ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для обработки результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03К 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k+1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[большее целое), и в выходной блок, содержащий к буферов с тремя состояниями с инверсным входом разрешения и k буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i=1, …, (m-1)) содержит (2i-1) буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц в упорядоченном двоичном числе, а не выявление диапазона единичных бит.

Известно устройство для упорядочения единиц (SU №1751746 А1, МПК G06F 7/38, 7/06, заявлено 26.11.1990, опубликовано 30.07.1992, Бюл. №28), содержащее по (n-1)-й группе элементов И и ИЛИ (где n - четное число, разрядность операнда, n=2К), две группы К-разрядных входов упорядоченных единиц и n-разрядный выход упорядоченных единиц.

Недостатком данного устройства является формирование на выходах упорядоченного кода, а не выявление диапазона единичных бит.

Известны система и способ подсчета начальных нулевых разрядов и подсчета начальных единичных разрядов в цифровом процессоре сигналов (RU №2409837 С2, МПК G06F 7/74, заявлен 27.07.2006, опубликовано 20.01.2011, Бюл. №2) в котором определяется количество разрядов для различных размеров слов данных. В устройстве проводится расширение входных данных знаком до временного шестидесятичетырехразрядного слова данных. При подсчете нулевых разрядов проводится инвертирование разрядов слова. Для подсчета начальных разрядов используется двоичный счетчик.

Недостатком данного устройства является низкое быстродействие, а также подсчет только начальных нулевых разрядов и начальных единичных разрядов в цифровом сигнале.

Известно устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, …, i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не выявление диапазона единичных бит.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для детектирования границ диапазона единичных бит (RU №2717934, МПК G06F 7/74, Н03К 21/00, заявлено 19.12.2019, опубликовано 27.03.2020, Бюл. №9), содержащее N разрядную входную шину D, выходную шину QR номера младшего разряда и выходную шину QL номера старшего разряда содержащие по М разрядов, где M=]log2 (N+1) [(большее целое), группу из (N-1) элементов ИЛИ 11, 12, …, 1(n-1), группу из (N-1) элементов ИЛИ-НЕ 21, 22, …, 2(n-1), первый 31 и второй 32 блоки счета младших упорядоченных единиц, а также внутреннюю шину SR сдвига вправо и внутреннюю шину SL сдвига влево, которые содержат по N разрядов.

Недостатком данного устройства является определение границ только для параллельно поступающего N разрядного входного двоичного числа.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является выявление номера старшего единичного бита и номера младшего единичного бита во входной бинарной последовательности данных.

При обработке результатов физических экспериментов устройство предназначено для выявления диапазона событий.

Техническим результатом изобретения является расширение функциональных возможностей в части возможности выявления границ и размерности диапазона единичных бит для бинарной последовательности.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство последовательного типа для детектирования границ диапазона единичных бит в бинарной последовательности, содержит

внешний вход DI данных N разрядной входной последовательности, выходную шину QUL номера младшего разряда, выходную шину QUM номера старшего разряда и выходную шину QUD диапазона, содержащие по М разрядов, где M=]log2(N+l) [(большее целое),

первый триггер пуска-останова TSS 1 и второй триггер единичных бит TU 2, первый элемент И 3, второй элемент И 4 с одним инверсным входом и элемент ИЛИ 5, первый счетчик бит СТВ 6 и второй счетчик диапазона CTD 7, первый регистр 8 номера старшего разряда, второй регистр 9 номера младшего разряда и третий регистр 10 диапазона,

а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый вход С,

причем вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого триггера пуска-останова TSS 1, первого счетчика бит СТВ 6 и второго счетчика диапазона CTD 7,

внешний тактовый вход устройства С соединен с соответствующими входами синхронизации С первого триггера 1 пуска-останова TSS, второго триггера 2 единичных бит TU, первого счетчика бит СТВ 6, второго счетчика диапазона CTD 7, первого регистра 8 номера старшего разряда, второго регистра 9 номера младшего разряда и третьего регистра 10 диапазона,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого триггера пуска-останова TSS 1, входами записи L первого счетчика бит СТВ 6 и второго счетчика диапазона CTD 7, а также с входами R синхронной установки в нулевое состояние второго триггера 2 единичных бит TU, первого регистра 8 номера старшего разряда, второго регистра 9 номера младшего разряда и третьего регистра 10 диапазона,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого триггера пуска-останова TSS 1,

причем выход первого триггера пуска-останова TSS 1 соединен с входом СЕ разрешения работы первого бит СТВ 6 и вторым входом первого элемента И 3,

внешний вход данных DI соединен с первыми входами первого элемента И 3, второго элемента И 4 с одним инверсным входом, элемента ИЛИ 5 и входом S синхронной установки в единичное состояние второго триггера 2 единичных бит TU, выход которого соединен со вторым инверсным входом второго элемента И 4 и вторым входом элемента ИЛИ 5, выход CED которого соединен с входом СЕ разрешения работы второго счетчика диапазона CTD 7,

выход СЕМ первого элемента И 3 соединен с входами СЕ разрешения работы первого регистра 8 номера старшего разряда и третьего регистра 10 диапазона, а выход CEL второго элемента И 4 с одним инверсным входом соединен с входом СЕ разрешения работы второго регистра 9 номера младшего разряда,

причем на группы информационных D-входов первого счетчика бит СТВ 6 и второго счетчика диапазона CTD 7 подано значение М разрядного двоичного кода «0…01»,

кроме того, выходы первого регистра 8 номера старшего разряда являются разрядами внешней шины QUM номера старшего разряда, выходы второго регистра 9 номера младшего разряда являются разрядами внешней шины QUL номера младшего разряда, а выходы третьего регистра 10 диапазона являются разрядами внешней шины QUD диапазона.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

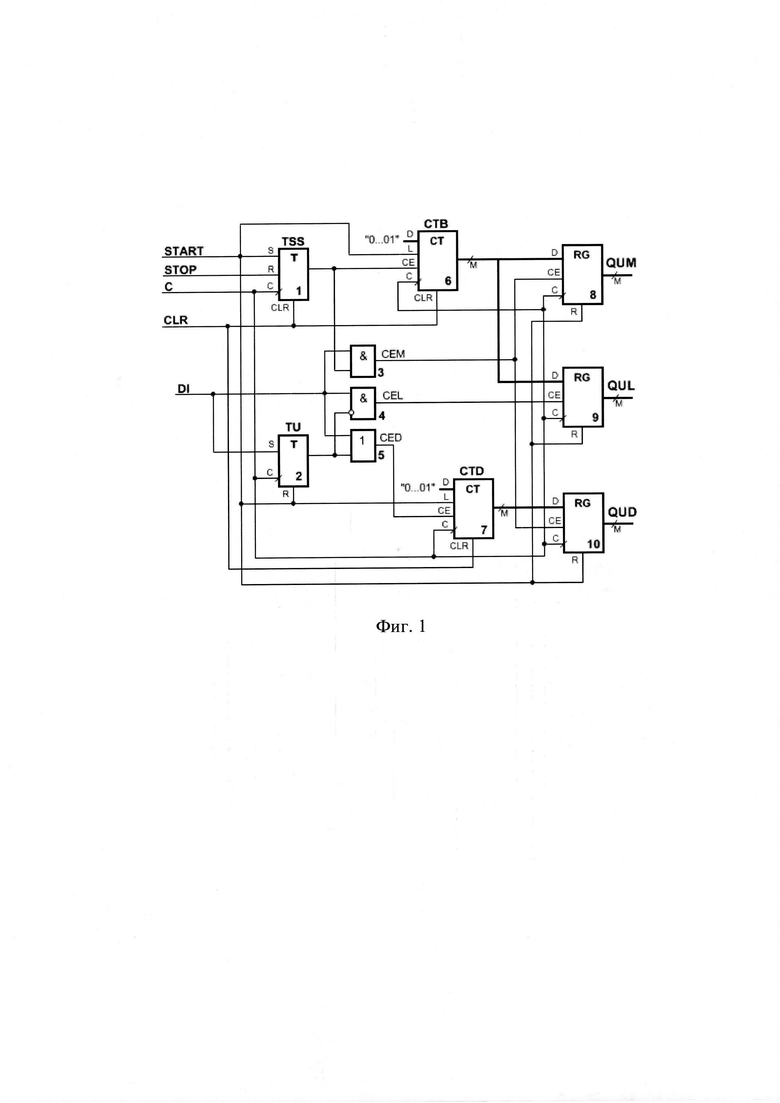

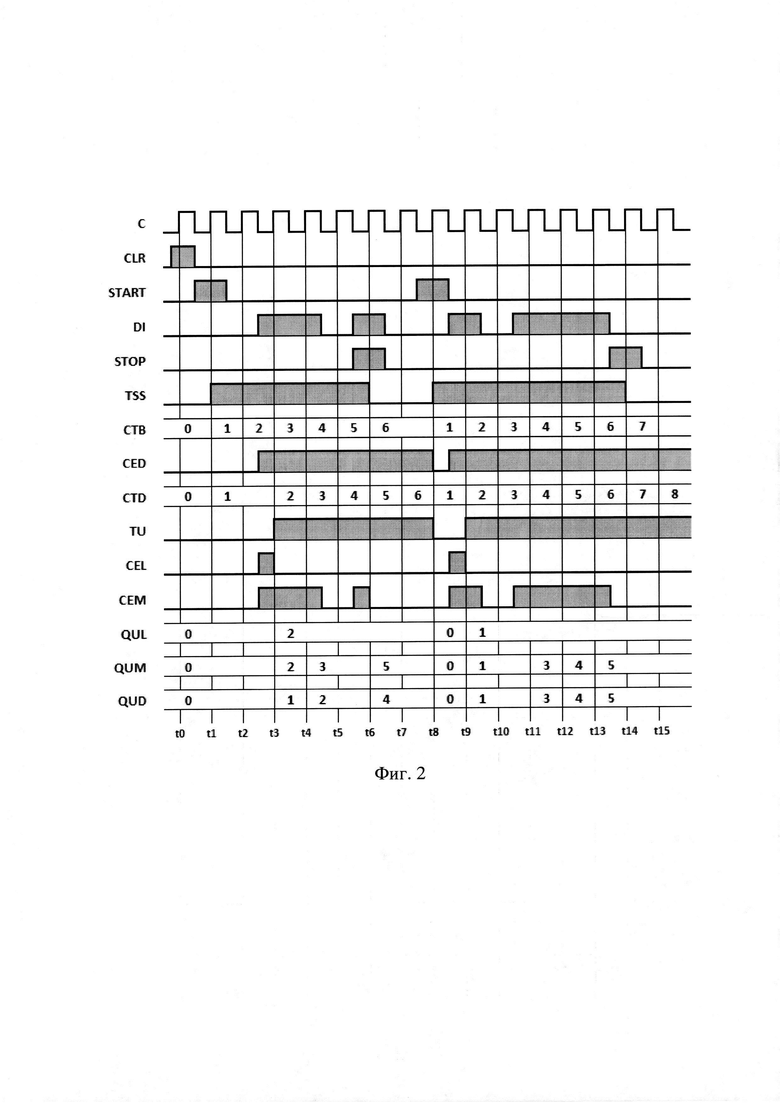

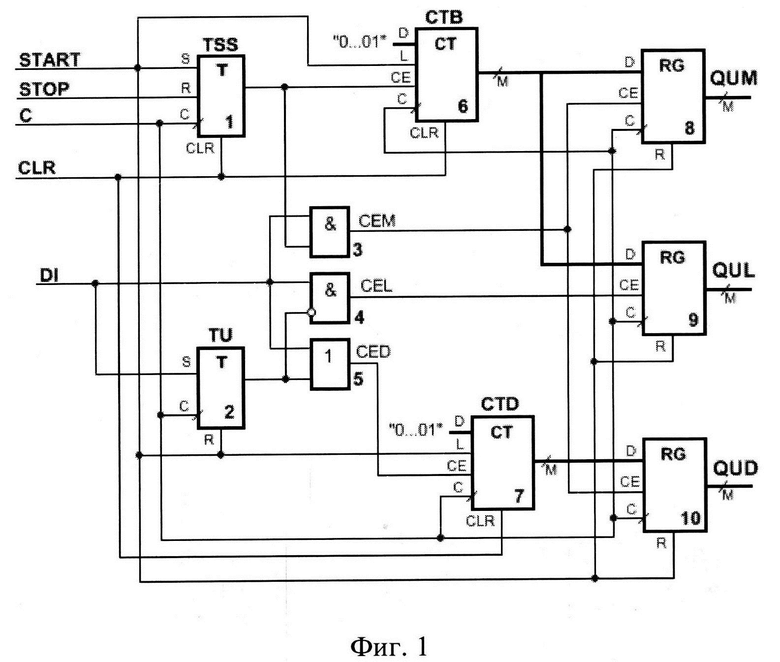

На фиг. 1 представлена функциональная схема предлагаемого устройства последовательного типа для детектирования границ диапазона единичных бит в бинарной последовательности. На фиг. 2 приведена временная диаграмма работы устройства

На фиг. 1-2 и в тексте введены следующие обозначения:

С - тактовый вход,

СЕ - вход разрешения работы,

CED - выход первого элемента И,

CEL - выход второго элемента И с одним инверсным входом,

СЕМ - выход элемента ИЛИ,

CLR - вход асинхронной установки в нулевое состояние,

СТ - счетчик,

СТВ - счетчик бит,

CTD - счетчик размерности диапазона,

D - информационные входы регистров и счетчиков,

DI - внешний вход данных,

L - вход разрешения записи (загрузки),

М - разрядность выходных шин, выходов счетчиков и регистров, где M=]log2(N+1) [(большее целое),

N - размерность (длина) входной последовательности данных,

QUD - внешняя выходная шина диапазона,

QUL - внешняя выходная шина номера младшего разряда,

QUM - внешняя выходная шина номера старшего разряда,

R - вход синхронной установки в нулевое состояние,

RG - регистр,

S - вход синхронной установки в единичное состояние,

START - внешний вход начала работы,

STOP - внешний вход останова,

Т - триггер,

TSS - триггер пуска-останова,

TU - триггер единичных бит,

1 - первый триггер пуска-останова TSS,

2 - второй триггер единичных бит TU,

3 - первый элемент И,

4 - второй элемент И с одним инверсным входом,

5 - элемент ИЛИ,

6 - первый счетчик бит СТВ,

7 - второй счетчик диапазона CTD,

8 - первый регистр номера старшего разряда,

9 - второй регистр номера младшего разряда,

10 - третий регистр диапазона.

Предлагаемое устройство последовательного типа для детектирования границ диапазона единичных бит в бинарной последовательности, содержит внешний вход DI данных N разрядной входной последовательности, выходную шину QUL номера младшего разряда, выходную шину QUM номера старшего разряда и выходную шину QUD диапазона, содержащие по М разрядов, где M=]log2(N+1) [(большее целое), первый триггер пуска-останова TSS 1 и второй триггер единичных бит TU 2, первый элемент И 3, второй элемент И 4 с одним инверсным входом и элемент ИЛИ 5, первый счетчик бит СТВ 6 и второй счетчик диапазона CTD 7, первый регистр 8 номера старшего разряда, второй регистр 9 номера младшего разряда и третий регистр 10 диапазона. Кроме того, введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый вход С.

Первый счетчик бит СТВ 6 предназначен для счета бит (разрядов) во входной бинарной последовательности входных данных DI. Второй счетчик диапазона CTD 7 предназначен для счета бит (разрядов) во входной бинарной последовательности входных данных DI после детектирования (выявления) первого (младшего) единичного бита.

Причем вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого триггера пуска-останова TSS, первого счетчика бит СТВ 6 и второго счетчика диапазона CTD 7. Единичное значение CLR=1 задается только в начале работы устройства.

Внешний тактовый вход устройства С соединен с соответствующими входами синхронизации С первого триггера 1 пуска-останова TSS, второго триггера 2 единичных бит TU, первого счетчика бит СТВ 6, второго счетчика диапазона CTD 7, первого регистра 8 номера старшего разряда, второго регистра 9 номера младшего разряда и третьего регистра 10 диапазона.

Внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого триггера пуска-останова TSS 1, входами записи L первого счетчика бит СТВ 6 и второго счетчика диапазона CTD 7, а также с входами R синхронной установки в нулевое состояние второго триггера 2 единичных бит TU, первого регистра 8 номера старшего разряда, второго регистра 9 номера младшего разряда и третьего регистра 10 диапазона. Единичное значение START=1 задается перед началом подачи очередной входной последовательности.

Внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого триггера пуска-останова TSS 1 и подается одновременно с последним N-м битом входной последовательности на вход DI данных.

Выход первого триггера пуска-останова TSS 1 соединен с входом СЕ разрешения работы первого бит СТВ 6 и вторым входом первого элемента И 3.

Внешний вход данных DI соединен с первыми входами первого элемента И 3, второго элемента И 4 с одним инверсным входом, элемента ИЛИ 5 и входом S синхронной установки в единичное состояние второго триггера 2 единичных бит TU, выход которого соединен со вторым инверсным входом второго элемента И 4 и вторым входом элемента ИЛИ 5, выход CED которого соединен с входом СЕ разрешения работы второго счетчика диапазона CTD 7.

Выход СЕМ первого элемента И 3 соединен с входами СЕ разрешения работы первого регистра 8 номера старшего разряда и третьего регистра 10 диапазона. Выход CEL второго элемента И 4 с одним инверсным входом соединен с входом СЕ разрешения работы второго регистра 9 номера младшего разряда.

Причем на группы информационных D-входов первого счетчика бит СТВ 6 и второго счетчика диапазона CTD 7 подано значение М разрядного двоичного кода «0…01».

Кроме того, выходы первого регистра 8 номера старшего разряда являются разрядами внешней шины QUM номера старшего разряда, выходы второго регистра 9 номера младшего разряда являются разрядами внешней шины QUL номера младшего разряда, а выходы третьего регистра 10 диапазона являются разрядами внешней шины QUD диапазона.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем. Предлагаемое устройство позволяет детектировать младший i разряд (где 1≤i≤N) и старший j разряд (где i≤j) в N разрядной входной последовательности данных, которые имеют единичное значение, и сформировать на выходах устройства номера младшего QUL и старшего QUM единичных разрядов, а также на выходах устройства QUD размерность диапазона между старшим и младшим единичными разрядами. При отсутствии единичных значений в разрядах входной последовательности на выходах номеров QUL и QUM границ диапазона и размерности диапазона QUD устанавливаются нулевые значения.

На внешний вход данных DI последовательно разряд за разрядом поступают биты входной бинарной последовательности данных размерностью N. Устройство начинает работать после подачи единичного сигнала START, при котором по фронту тактового сигнала С в единичное состояние устанавливается первый триггер пуска-останова TSS 1, в нулевое состояние устанавливаются второй триггер единичных бит TU 2, а также нулевые значения устанавливаются в первом регистре 8 номера старшего разряда, втором регистре 9 номера младшего разряда и третьем регистре 10 диапазона. Кроме того, по сигналу START=1 двоичные М разрядные коды «0…01» записываются в первый счетчик бит СТВ 6 и второй счетчик диапазона CTD 7 (единичное значение записывается в младшие разряды), что обеспечивает подготовку текущего значения счетчиков на номер первого бита входной последовательности.

Первый счетчик бит СТВ 6 осуществляет счет бит (разрядов) во входной бинарной последовательности входных данных DI. Второй счетчик диапазона CTD 7 осуществляет счет бит (разрядов) во входной бинарной последовательности входных данных DI после детектирования (выявления) первого единичного бита (младшего i-ro разряда).

Первый счетчик бит СТВ 6 осуществляет счет бит при единичном значении TSS=1 первого триггера пуска-останова 1 по фронтам тактового сигнала С.

При детектировании первого единичного бита, когда DI=1, по фронту тактового сигнала С в единичное состояние TU=1 устанавливается второй триггер единичных бит 2. При этом единичное значение CED=1 формируется на выходе элемента ИЛИ 5, по которому далее разрешается счет последующих бит вторым счетчиком диапазона CTD 7.

Кроме того, при детектировании первого i-го единичного бита, когда DI=1, единичное значение CEL=1 формируется на выходе второго элемента И 4 с одним инверсным выходом, по которому осуществляется запись текущего номера бита (соответствующего i-му разряду) с выхода первого счетчика бит СТВ 6 во второй регистр номера младшего разряда 9.

Одновременно единичное значение СЕМ=1 формируется на выходе первого элемента И 3, по которому осуществляется запись текущего номера бита (j-ro разряда) с выхода первого счетчика бит СТВ 6 в первый регистр номера старшего разряда 8 и запись значения размерности диапазона с выхода второго счетчика CTD 7 в третий регистр диапазона 10.

Если следующие биты входной последовательности имеют нулевое значение DI=0, то не осуществляется запись в первый 8, второй 9 и третий 10 регистры.

При детектировании следующего входного единичного бита DI=1 вновь формируется единичное значение СЕМ=1 на выходе первого элемента И 3, по которому аналогично осуществляется запись текущего номера бита (j-го разряда) с выхода первого счетчика бит СТВ 6 в первый регистр номера старшего разряда 8 и запись значения размерности диапазона с выхода второго счетчика CTD 7 в третий регистр диапазона 10.

Значения с выходов первого 8, второго 9 и третьего 10 регистров передаются соответственно на соответствующие разряды внешней шины QUM номера старшего разряда, внешней шины QUL номера младшего разряда и внешней шины QUD диапазона.

Предлагаемое устройство работает следующим образом.

При подаче сигнала на вход CLR (момент времени t0) асинхронной установки в нулевое состояние устанавливается первый триггер пуска-останова TSS 1 и нулевые коды устанавливаются в первый счетчик бит СТВ 6 и во второй счетчик диапазона CTD 7. Тактовые сигналы с входа С постоянно поступают на входы синхронизации всех триггеров, регистров и счетчиков, режимы работы которых задаются сигналами на соответствующих входах управления, а исполняются по фронтам тактовых сигналов С.

На временной диаграмме на фиг. 2 приведена работа предлагаемого устройства. В моменты времени t2-t6 на внешний вход данных DI подана последовательность «01101» содержащая N=5 бит, а в моменты времени t9-t14 подана последовательность «101110» содержащая N=6 бит (слева указаны младшие разряды, которые поступают первыми), которые отражают основные особенности работы устройства.

Работа устройства начинается после подачи сигнала START=1. При этом по фронту первого тактового сигнала С (моменты времени t1 и t8 на фиг. 2) в единичное состояние устанавливается первый триггер пуска-останова TSS 1, в нулевое состояние устанавливаются второй триггер единичных бит TU 2, а также нулевые значения устанавливаются в первом регистре 8 номера старшего разряда, втором регистре 9 номера младшего разряда и третьем регистре 10 диапазона. Кроме того, по единичному сигналу START=1, который поступает на входы L разрешения загрузки, М разрядные двоичные коды «0…01», установленные на информационных входах D, записываются в первый счетчик бит СТВ 6 и второй счетчик диапазона CTD 7 (единичное значение записывается в младшие разряды - моменты времени t1 и t8).

Далее на внешний вход данных DI последовательно разряд за разрядом поступают биты входной бинарной последовательности данных размерностью N. В момент времени t2 (фиг. 2) на вход данных поступает нулевое значение первого бита входной последовательности DI=0, по которому также нулевые значения устанавливаются на выходах первого и второго элементов И и третьего элемента ИЛИ - СЕМ=0, CEL=0 и CED=0 и далее нулевые значения установливаются на входах СЕ разрешения работы регистров 8, 9 и 10, поэтому по фронту тактового сигнала С в момент времени t2 не выполняется загрузка в регистры 8, 9 и 10. Но осуществляется счет в первом счетчике бит 6 (СТВ=2) - настройка на второй бит последовательности и сохраняется значение во втором счетчике диапазона CTD 7.

Между моментами времени t2 и t3 на вход данных DI поступает единичное значение DI=1 второго бита входной последовательности, по которому формируются единичные значения на выходах первого и второго элементов И и третьего элемента ИЛИ - СЕМ=1, CEL=1 и CED=1, по которым разрешается загрузка в регистры 8, 9 и 10. Поэтому в момент времени t3 по фронту тактового сигнала С в единичное состояние переключается второй триггер единичных бит 2 TU=1, запись значения кода СТВ=2 с выхода первого счетчика бит 6 в первый регистр номера старшего разряда 8 (QUM=2) и во второй регистр номера младшего разряда 9 (QUL=2), а также запись значения кода CTD=1 с выхода второго счетчика 7 в третий регистр диапазона 10 (QUD=1). Так как был выявлен (детектирован) только первый единичный бит DI=1 во входной последовательности, поэтому значения регистров младшего 9 и старшего 8 регистров совпадают и фиксируют, что это второй бит во входной последовательности, а также значение QUD=1 на выходе третьего регистра 10 указывает, что детектирован диапазон из одного единичного бита.

Кроме того, одновременно в момент времени t3 по фронту тактового сигнала С вновь увеличивается значение первого счетчика бит 6 (СТВ=3) и так как установлено единичное значение CED=1 увеличивается значение второго счетчика диапазона 7 (CTD=2). При этом единичное значение TU=1 с выхода второго триггера единичных бит 2 передается на выход CED=1 элемента ИЛИ 5, разрешая дальнейший счет бит в последовательности. Кроме того, единичное значение TU=1 с выхода второго триггера единичных бит 2 поступает на инверсный вход второго элемента И 4 и запрещает дальнейшее формирование единичных значений на выходе второго элемента И 5 (далее CEL=0) и, следовательно, запрещает запись во второй регистр номера младшего разряда 9.

Далее в моменты времени t4, t5, t6 по фронту тактовых сигналов С осуществляется счет бит во входной последовательности в первом счетчике бит СТВ 6 и во втором счетчике диапазона CTD 7. В момент времени t4 по фронту тактового сигнала С при единичном входном сигнале DI=1 и соответственно сформированном значении СЕМ=1 осуществляется запись значения кода СТВ=3 с выхода первого счетчика бит 6 в первый регистр номера старшего разряда 8 (QUM=3) и запись значения кода CTD=2 с выхода второго счетчика 7 в третий регистр диапазона 10 (QUD=2), которое указывает на размерность диапазона единичных бит равную двум.

В момент времени t5 по фронту тактового сигнала С при нулевом входном сигнале DI=0 и соответственно сформированном значении СЕМ=0 не проводится запись в регистры.

В момент времени t6 по фронту тактового сигнала С при единичном входном сигнале DI=1 и соответственно сформированном значении СЕМ=1 осуществляется запись значения кода СТВ=5 с выхода первого счетчика бит 6 в первый регистр номера старшего разряда 8 (QUM=5) и запись значения кода CTD=4 с выхода второго счетчика 7 в третий регистр диапазона 10 (QUD=4), которое указывает на размерность диапазона единичных бит равную четырем.

Кроме того, между моментами времени t5 и tl одновременно с входным сигналом DI=1 поступает сигнал STOP, по которому в момент времени t6 по фронту тактового сигнала С в нулевое состояние переходит первый триггер пуска-останова 1 TSS=0, который запрещает дальнейший счет бит в первом счетчике бит СТВ 6 и формирует нулевое значение СЕМ=0 на выходе первого элемента И 3.

Таким образом, для входной последовательности «01101» (слева указаны младшие разряды, которые поступают первыми), сформированы следующие значения, которые передаются на соответствующие выходные шины: номер младшего разряда QUL=2, номер старшего разряда QUM=5 и размерность диапазона единичных бит QUD=4.

На временной диаграмме на фиг. 2 после второго единичного сигнала START=1 в моменты времени t9-t14 подана вторая входная последовательность «101110» содержащая N=6 бит (слева указаны младшие разряды, которые поступают первыми). В отличие от первой последовательности входных данных «01101» первый бит, подаваемый на вход DI, имеет единичное значение (DI=1 в интервале времени между t8 и t10). Поэтому одновременно с подачей единичного бита на вход DI=1 формируются единичные значения на выходах первого и второго элементов И и третьего элемента ИЛИ - СЕМ=1, CEL=1 и CED=1, по которым разрешается загрузка в регистры 8, 9 и 10. Поэтому в момент времени t9 по фронту тактового сигнала С в единичное состояние переключается второй триггер единичных бит 2 TU=1, запись значения кода СТВ=1 с выхода первого счетчика бит 6 в первый регистр номера старшего разряда 8 (QUM=1) и во второй регистр номера младшего разряда 9 (QUL=1), а также запись значения кода CTD=1 с выхода второго счетчика 7 в третий регистр диапазона 10 (QUD=1).

В момент времени t10 входной сигнал имеет нулевое значение DI=0 поэтому запись новых значений в регистры не выполняется.

Далее по фронту тактовых сигналов С в моменты времени t11, t12, t13, аналогично рассмотренным режимам для первой последовательности проводится детектирование входных единичных бит DI=1 и запись значений кодов СТВ с выхода первого счетчика бит 6 в первый регистр номера старшего разряда 8 и запись значений кодов CTD с выхода второго счетчика 7 в третий регистр диапазона 10, при этом сохраняется значение во втором регистре 9 номера младшего разряда (QUL=1).

В момент времени t14 по фронту тактового сигнала С для нулевого входного сигнала DI=0 сохраняются значения регистров 8, 9 и 10 и при подаче единичного сигнала останова STOP=1 в нулевое состояние переходит первый триггер пуска-останова 1 TSS=0. При этом завершается цикл распознавания бит второй входной последовательности «101110», для которой будут сформированы следующие значения, которые передаются на соответствующие выходные шины: номер младшего разряда QUL=1, номер старшего разряда QUM=5 и размерность диапазона единичных бит QUD=5.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату -детектирование границ и размерности диапазона единичных бит для входной бинарной последовательности.

Изобретение относится к области вычислительной техники. Техническим результатом является обеспечение возможности выявления границ и размерности диапазона единичных бит для бинарной последовательности. Раскрыто устройство последовательного типа для детектирования границ диапазона единичных бит в бинарной последовательности, содержащее внешний вход DI данных N разрядной входной последовательности, выходную шину QUL номера младшего разряда, выходную шину QUM номера старшего разряда и выходную шину QUD диапазона, содержащие по М разрядов, где M=]log2(N+1)[ (большее целое), первый триггер пуска-останова TSS 1 и второй триггер единичных бит TU 2, первый элемент И 3, второй элемент И 4 с одним инверсным входом и элемент ИЛИ 5, первый счетчик бит СТВ 6 и второй счетчик диапазона CTD 7, первый регистр 8 номера старшего разряда, второй регистр 9 номера младшего разряда и третий регистр 10 диапазона, а также внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый вход С. 2 ил.

Устройство последовательного типа для детектирования границ диапазона единичных бит в бинарной последовательности содержит внешний вход DI данных N разрядной входной последовательности, выходную шину QUL номера младшего разряда, выходную шину QUM номера старшего разряда и выходную шину QUD диапазона, содержащие по М разрядов, где M=]log2(N+1)[ (большее целое),

первый триггер пуска-останова TSS 1 и второй триггер единичных бит TU 2, первый элемент И 3, второй элемент И 4 с одним инверсным входом и элемент ИЛИ 5, первый счетчик бит СТВ 6 и второй счетчик диапазона CTD 7, первый регистр 8 номера старшего разряда, второй регистр 9 номера младшего разряда и третий регистр 10 диапазона,

а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый вход С,

причем вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого триггера пуска-останова TSS 1, первого счетчика бит СТВ 6 и второго счетчика диапазона CTD 7,

внешний тактовый вход устройства С соединен с соответствующими входами синхронизации С первого триггера 1 пуска-останова TSS, второго триггера 2 единичных бит TU, первого счетчика бит СТВ 6, второго счетчика диапазона CTD 7, первого регистра 8 номера старшего разряда, второго регистра 9 номера младшего разряда и третьего регистра 10 диапазона,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого триггера пуска-останова TSS 1, входами записи L первого счетчика бит СТВ 6 и второго счетчика диапазона CTD 7, а также с входами R синхронной установки в нулевое состояние второго триггера 2 единичных бит TU, первого регистра 8 номера старшего разряда, второго регистра 9 номера младшего разряда и третьего регистра 10 диапазона,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого триггера пуска-останова TSS 1,

причем выход первого триггера пуска-останова TSS 1 соединен с входом СЕ разрешения работы первого бит СТВ 6 и вторым входом первого элемента И 3,

внешний вход данных DI соединен с первыми входами первого элемента И 3, второго элемента И 4 с одним инверсным входом, элемента ИЛИ 5 и входом S синхронной установки в единичное состояние второго триггера 2 единичных бит TU, выход которого соединен со вторым инверсным входом второго элемента И 4 и вторым входом элемента ИЛИ 5, выход CED которого соединен с входом СЕ разрешения работы второго счетчика диапазона CTD 7,

выход СЕМ первого элемента И 3 соединен с входами СЕ разрешения работы первого регистра 8 номера старшего разряда и третьего регистра 10 диапазона, а выход CEL второго элемента И 4 с одним инверсным входом соединен с входом СЕ разрешения работы второго регистра 9 номера младшего разряда,

причем на группы информационных D-входов первого счетчика бит СТВ 6 и второго счетчика диапазона СТD 7 подано значение М разрядного двоичного кода «0…01»,

кроме того, выходы первого регистра 8 номера старшего разряда являются разрядами внешней шины QUM номера старшего разряда, выходы второго регистра 9 номера младшего разряда являются разрядами внешней шины QUL номера младшего разряда, а выходы третьего регистра 10 диапазона являются разрядами внешней шины QUD диапазона.

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРАНИЦ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ | 2019 |

|

RU2717934C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680762C1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2021-06-07—Публикация

2020-10-26—Подача