Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны параллельные счетчики единичных сигналов входного кортежа (x1,..., x8), где хq∈{0,1} (см., например, рис.8.12 на стр.479 в книге Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. М.: Радио и связь, 1990.).

К причине, препятствующей достижению указанного ниже технического результата при использовании известных параллельных счетчиков единичных сигналов, относятся большие аппаратурные затраты.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, параллельный счетчик единичных сигналов (см. рис.2 в статье Новиков Л.Г. Преобразователи синхронного унитарного импульсного сигнала// Приборы и системы. Управление, контроль, диагностика. 2002. №8. С.34-35.), который содержит элементы «исключающее ИЛИ», элементы «И» и определяет число единичных сигналов входного кортежа (x1,..., x7), где хq∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, поскольку не допускается обработка кортежа (x1,..., x8), и большие аппаратурные затраты.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения определения числа единичных сигналов входного кортежа (x1,...,x8)(хq∈{0,1}) и уменьшение аппаратурных затрат.

Указанный технический результат при осуществлении изобретения достигается тем, что в параллельном счетчике единичных сигналов, содержащем семнадцать элементов «исключающее ИЛИ» и тринадцать элементов «И», первый и второй входы r-го  элемента «исключающее ИЛИ» соединены соответственно с первым и вторым входами r-го элемента «И», подключенного первым входом к (r+1)-му входу параллельного счетчика единичных сигналов, первые выход и вход которого соединены соответственно с выходом седьмого элемента «исключающее ИЛИ» и вторым входом первого элемента «И», подключенного выходом к второму входу восьмого элемента «исключающее ИЛИ», выходы первого - пятого и шестого элементов «исключающее ИЛИ» соединены соответственно с вторыми входами второго - шестого и седьмого элементов «И», подключенных выходами соответственно к первым входам восьмого - двенадцатого и тринадцатого элементов «исключающее ИЛИ», выходы которых соединены соответственно с вторыми входами девятого - тринадцатого элементов «И» и вторым выходом параллельного счетчика единичных сигналов, первый и второй входы r-го

элемента «исключающее ИЛИ» соединены соответственно с первым и вторым входами r-го элемента «И», подключенного первым входом к (r+1)-му входу параллельного счетчика единичных сигналов, первые выход и вход которого соединены соответственно с выходом седьмого элемента «исключающее ИЛИ» и вторым входом первого элемента «И», подключенного выходом к второму входу восьмого элемента «исключающее ИЛИ», выходы первого - пятого и шестого элементов «исключающее ИЛИ» соединены соответственно с вторыми входами второго - шестого и седьмого элементов «И», подключенных выходами соответственно к первым входам восьмого - двенадцатого и тринадцатого элементов «исключающее ИЛИ», выходы которых соединены соответственно с вторыми входами девятого - тринадцатого элементов «И» и вторым выходом параллельного счетчика единичных сигналов, первый и второй входы r-го  элемента «исключающее ИЛИ» соединены соответственно с первым и вторым входами r-го элемента «И», а выходы десятого-двенадцатого и тринадцатого элементов «И» подключены соответственно к первым входам четырнадцатого - шестнадцатого и семнадцатого элементов «исключающее ИЛИ», подсоединенных выходами соответственно к вторым входам пятнадцатого - семнадцатого элементов «исключающее ИЛИ» и третьему выходу параллельного счетчика единичных сигналов, особенность заключается в том, что второй вход четырнадцатого элемента; «исключающее ИЛИ» соединен с выходом девятого элемента «И», а первый, второй входы и выход восьмого элемента «И» подключены соответственно к первому, второму входам семнадцатого элемента «исключающее ИЛИ» и четвертому выходу параллельного счетчика единичных сигналов.

элемента «исключающее ИЛИ» соединены соответственно с первым и вторым входами r-го элемента «И», а выходы десятого-двенадцатого и тринадцатого элементов «И» подключены соответственно к первым входам четырнадцатого - шестнадцатого и семнадцатого элементов «исключающее ИЛИ», подсоединенных выходами соответственно к вторым входам пятнадцатого - семнадцатого элементов «исключающее ИЛИ» и третьему выходу параллельного счетчика единичных сигналов, особенность заключается в том, что второй вход четырнадцатого элемента; «исключающее ИЛИ» соединен с выходом девятого элемента «И», а первый, второй входы и выход восьмого элемента «И» подключены соответственно к первому, второму входам семнадцатого элемента «исключающее ИЛИ» и четвертому выходу параллельного счетчика единичных сигналов.

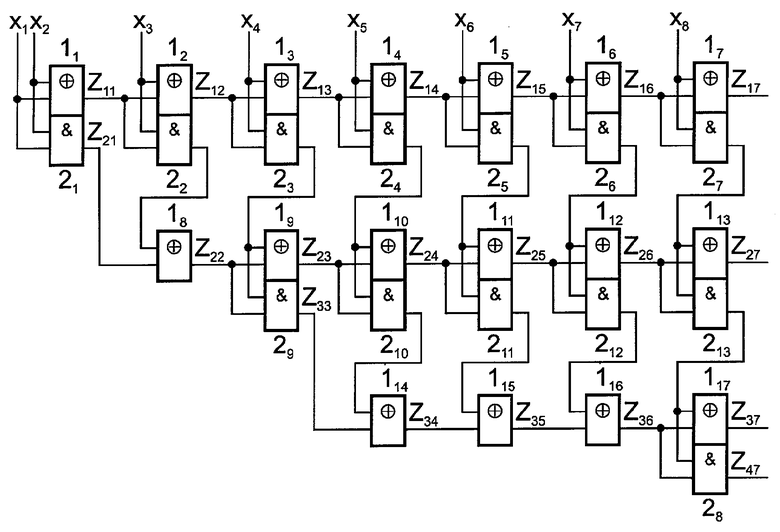

На чертеже представлена схема предлагаемого параллельного счетчика единичных сигналов.

Параллельный счетчик единичных сигналов содержит элементы «исключающее ИЛИ» 11,..., 117 и элементы «И» 21,..., 213, причем первый и второй входы элемента 1r соединены соответственно с первым и вторым входами элемента 2r, подключенного первым входом к (r+1)-му входу параллельного счетчика единичных сигналов, первые выход и вход которого соединены соответственно с выходом элемента 17 и вторым входом элемента 21, подключенного выходом к второму входу элемента 18, выходы элементов 11-15 и 16 соединены соответственно с вторыми входами элементов 22-26 и 27, подключенных выходами соответственно к первым входам элементов 18-112 и 113, выходы которых соединены соответственно с вторыми входами элементов 29-213 и вторым выходом параллельного счетчика единичных сигналов, первый и второй входы элемента 1r

соединены соответственно с первым и вторым входами элемента 2r, подключенного первым входом к (r+1)-му входу параллельного счетчика единичных сигналов, первые выход и вход которого соединены соответственно с выходом элемента 17 и вторым входом элемента 21, подключенного выходом к второму входу элемента 18, выходы элементов 11-15 и 16 соединены соответственно с вторыми входами элементов 22-26 и 27, подключенных выходами соответственно к первым входам элементов 18-112 и 113, выходы которых соединены соответственно с вторыми входами элементов 29-213 и вторым выходом параллельного счетчика единичных сигналов, первый и второй входы элемента 1r соединены соответственно с первым и вторым входами элемента 2r, а выходы элементов 210-212 и 213 подключены соответственно к первым входам элементов 114-116 и 117, подсоединенных выходами соответственно к вторым входам элементов 115-117 и третьему выходу параллельного счетчика единичных сигналов, второй вход элемента 114 соединен с выходом элемента 29, а первый, второй входы и выход элемента 28 подключены соответственно к первому, второму входам элемента 117 и четвертому выходу параллельного счетчика единичных сигналов.

соединены соответственно с первым и вторым входами элемента 2r, а выходы элементов 210-212 и 213 подключены соответственно к первым входам элементов 114-116 и 117, подсоединенных выходами соответственно к вторым входам элементов 115-117 и третьему выходу параллельного счетчика единичных сигналов, второй вход элемента 114 соединен с выходом элемента 29, а первый, второй входы и выход элемента 28 подключены соответственно к первому, второму входам элемента 117 и четвертому выходу параллельного счетчика единичных сигналов.

Работа предлагаемого параллельного счетчика единичных сигналов осуществляется следующим образом. На его первый,..., восьмой входы подаются соответственно подлежащие обработке сигналы x1,..., x8∈{0,1}. Тогда сигналы Zij (см. чертеж) будут определяться выражением  где символами ⊕ и & обозначены соответственно операции «исключающее ИЛИ» («сложение по модулю 2») и «И»; m=2i-1; хk1,..., хkm∈{x1,..., xj+1}, 1≤k1<...<km≤j+1; N=Cm j+1 есть количество неповторяющихся конъюнкций хk1&...&хkm, определяемое как число сочетаний из j+1 по m. В частности имеем Z13=х1⊕х2⊕х3⊕х4, Z23=x1&x2&⊕x1&x3⊕x1&x4⊕x2&x3⊕x2&x4⊕x3&x4, Z33=x1&x2&x3&x4. Таким образом, на выходах предлагаемого счетчика получим Z17=τ0, Z27=τ1 Z37=τ2 и Z47=τ3, где τ3τ2τ1τ0 есть двоичный код числа единичных сигналов в кортеже (x1,..., x8).

где символами ⊕ и & обозначены соответственно операции «исключающее ИЛИ» («сложение по модулю 2») и «И»; m=2i-1; хk1,..., хkm∈{x1,..., xj+1}, 1≤k1<...<km≤j+1; N=Cm j+1 есть количество неповторяющихся конъюнкций хk1&...&хkm, определяемое как число сочетаний из j+1 по m. В частности имеем Z13=х1⊕х2⊕х3⊕х4, Z23=x1&x2&⊕x1&x3⊕x1&x4⊕x2&x3⊕x2&x4⊕x3&x4, Z33=x1&x2&x3&x4. Таким образом, на выходах предлагаемого счетчика получим Z17=τ0, Z27=τ1 Z37=τ2 и Z47=τ3, где τ3τ2τ1τ0 есть двоичный код числа единичных сигналов в кортеже (x1,..., x8).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый параллельный счетчик единичных сигналов обладает более широкими по сравнению с прототипом функциональными возможностями и меньшими аппаратурными затратами, так как определяет число единичных сигналов входного кортежа (x1,..., x8) и содержит 17 элементов «исключающее ИЛИ» и 13 элементов «И» (прототип содержит 18 элементов «исключающее ИЛИ» и 13 элементов «И»).

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2013 |

|

RU2518641C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2256211C1 |

| МАЖОРИТАЛЬНЫЙ МОДУЛЬ | 2021 |

|

RU2778677C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2019 |

|

RU2710872C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2003 |

|

RU2251141C1 |

| Устройство для умножения элементов поля Галуа GF(2 @ ) при образующем полиноме F(х)=х @ +Х @ +х @ +х @ +1 | 1989 |

|

SU1716504A1 |

| Устройство для выдачи сообщений | 1989 |

|

SU1709367A1 |

| Многофункциональный модуль | 1988 |

|

SU1552168A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОТКАЗОВ В ШАГОВОМ ЭЛЕКТРОПРИВОДЕ | 2012 |

|

RU2523047C2 |

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1835542A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом является расширение функциональных возможностей за счет обеспечения определения числа единичных сигналов входного кортежа (x1,..., x8) (xq∈{0,1}) и уменьшение аппаратурных затрат. Устройство содержит семнадцать элементов "исключающее ИЛИ" и тринадцать элементов "И". 1 ил.

Параллельный счетчик единичных сигналов, содержащий семнадцать элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и тринадцать элементов И, причем первый и второй входы r-го  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами r-го элемента И, подключенного первым входом к (r+1)-му входу параллельного счетчика единичных сигналов, первые выход и вход которого соединены соответственно с выходом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом первого элемента И, подключенного выходом к второму входу восьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы первого - пятого и шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с вторыми входами второго - шестого и седьмого элементов И, подключенных выходами соответственно к первым входам восьмого - двенадцатого и тринадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены соответственно с вторыми входами девятого - тринадцатого элементов И и вторым выходом параллельного счетчика единичных сигналов, первый и второй входы r-го

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами r-го элемента И, подключенного первым входом к (r+1)-му входу параллельного счетчика единичных сигналов, первые выход и вход которого соединены соответственно с выходом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом первого элемента И, подключенного выходом к второму входу восьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы первого - пятого и шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с вторыми входами второго - шестого и седьмого элементов И, подключенных выходами соответственно к первым входам восьмого - двенадцатого и тринадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены соответственно с вторыми входами девятого - тринадцатого элементов И и вторым выходом параллельного счетчика единичных сигналов, первый и второй входы r-го  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами r-го элемента И, а выходы десятого - двенадцатого и тринадцатого элементов И подключены соответственно к первым входам четырнадцатого - шестнадцатого и семнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенных выходами соответственно к вторым входам пятнадцатого - семнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и третьему выходу параллельного счетчика единичных сигналов, отличающийся тем, что второй вход четырнадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом девятого элемента И, а первый, второй входы и выход восьмого элемента И подключены соответственно к первому, второму входам семнадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертому выходу параллельного счетчика единичных сигналов.

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами r-го элемента И, а выходы десятого - двенадцатого и тринадцатого элементов И подключены соответственно к первым входам четырнадцатого - шестнадцатого и семнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенных выходами соответственно к вторым входам пятнадцатого - семнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и третьему выходу параллельного счетчика единичных сигналов, отличающийся тем, что второй вход четырнадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом девятого элемента И, а первый, второй входы и выход восьмого элемента И подключены соответственно к первому, второму входам семнадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертому выходу параллельного счетчика единичных сигналов.

| НОВИКОВ Л.Г | |||

| Преобразователи синхронного унитарного импульсного сигнала | |||

| Приборы и системы | |||

| Управление, контроль, диагностика | |||

| ЩИТОВОЙ ДЛЯ ВОДОЕМОВ ЗАТВОР | 1922 |

|

SU2000A1 |

| СУММАТОР КОДОВ "1 ИЗ N" | 1997 |

|

RU2129730C1 |

| Устройство для параллельного счета количества единиц(нулей)в двоичном числе | 1972 |

|

SU450160A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1837280A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797111A1 |

| Параллельный счетчик по модулю @ -дешифратор количества единиц в @ -разрядном двоичном коде | 1986 |

|

SU1420666A1 |

| Двоичный счетчик | 1984 |

|

SU1261107A1 |

| DE 3716551 А, 23.02.1989. | |||

Авторы

Даты

2005-09-10—Публикация

2004-05-11—Подача