ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел и для обработки результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03К 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k+1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[большее целое), и в выходной блок, содержащий к буферов с тремя состояниями с инверсным входом разрешения и к буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i=1, (m-1)) содержит (2i-1) буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц только в одной группе упорядоченного двоичного числа, а не в группах единичных разрядов.

Известно устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, …, i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не по группам единичных разрядов.

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств для выделения групп и определения количества единичных разрядов в группах, и определение количества групп.

Известно устройство последовательного типа для детектирования групп нулевых и единичных бит и определение их количества (RU №2680759, МПК G06F 7/74, заявлено 16.02.2018, опубликовано 26.02.2019, Бюл. №6), содержащее внешний вход данных DI, группу внешних выходов данных QO, группу внешних выходов количества групп QG, группу внешних выходов количества нулей QZ, группу внешних выходов количества единиц QU, группу внешних выходов «разность единиц и нулей» QZU, первый RS-триггер пуска-останова TSS 1, блок детектора единиц и нулей 2, третий D-триггер разрешения счета групп ТСЕ 7, третий элемент И 8, первый счетчик групп CG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, четвертый 12, пятый 13 и шестой 14 элементы И, третий счетчик нулей CZ 15, четвертый счетчик единиц CU 16, пятый реверсивный счетчик нулей-единиц CZU 17 и блок преобразователя кода разности 18, причем блок детектора единиц и нулей 2 состоит из первого 3 и второго 4 элементов И с одним инверсным входом, элемента ИЛИ 5 и второго D-триггера управления битами TU 6 и содержит три выхода, а блок преобразователя кода разности 18 содержит группу из (М-2) элементов ИЛИ 19, группу из (М-1) элементов И 20 и группу из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 21, где M=[log2N]+l (меньшее целое), а N - размерность длина входной последовательности данных, причем первый счетчик групп CG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, третий счетчик нулей CZ 15 и четвертый счетчик единиц CU 16 имеют разрядность М, а пятый реверсивный счетчик нулей-единиц CZU 17 имеет разрядность (М+1), а также введены внешние флаги готовности результата FE, «Буфер заполнен» FF, «Буфер пуст» FZ и флаг «нулей больше единиц» F01. При этом в выходном буфере ОВ 11 в четных адресах, начиная с нулевого адреса, указывается количество нулевых бит в группах, а в нечетных адресах, начиная с первого адреса, указывается количество единичных бит в группах.

Недостатком данного устройства является выявление групп единичных бит произвольной размерности.

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств для сравнения ширины детектируемых групп с границами заданного диапазона групп.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для детектирования групп в бинарной последовательности (RU №2728957, МПК G06F 7/74, Н03К 21/00 заявлено 15.01.2020, опубликовано 03.08.2020, Бюл. №22), содержащее внешний вход данных DI, группу внешних выходов данных QO, группу внешних выходов количества групп QG, группу внешних выходов количества нулей QZ, группу внешних выходов количества единиц QU, группу внешних выходов «разность единиц и нулей» QZU, группы внешних выходов количества единиц в максимальной группе MU, количества нулей в максимальной группе MZ, номера группы максимальной группы единиц NGMU, номера группы максимальной группы нулей NGMZ, номера начала максимальной группы единичных бит NMU и номера начала максимальной группы нулевых бит NMZ, первый RS-триггер пуска-останова TSS 1, блок детектора единиц и нулей 2, третий D-триггер разрешения счета групп ТСЕ 7, третий элемент И 8, первый сумматор SMG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, четвертый 12, пятый 13 и шестой 14 элементы И, третий счетчик нулей CZ 15, четвертый счетчик единиц CU 16, пятый реверсивный счетчик нулей-единиц CZU 17 и блок преобразователя кода разности 18, первый счетчик CNB 22, первый регистр RNM 23, второй сумматор SNM 24, второй 25, третий 26, четвертый 27, пятый 28, шестой 29, седьмой 32 и восьмой 35 регистры, первый компаратор 30 сравнения количества единичных бит, седьмой элемент И 31, второй компаратор 33 сравнения количества нулевых бит, восьмой элемент И с одним инверсным входом 34, а также введены внешние флаги готовности результата FE, «Буфер заполнен» FF, «Буфер пуст» FZ и флаг «нулей больше единиц» F01.

В данном устройстве осуществляется выявление максимальных групп единичных и нулевых бит и определение общего количества групп, номеров групп и начала групп в бинарной последовательности. Недостатком данного устройства является отсутствие средств для сравнения ширины детектируемых групп с границами заданного диапазона групп.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является разработка аппаратных средств для исследования свойств генераторов псевдослучайных последовательностей двоичных чисел, а также для обработки результатов физических экспериментов.

При анализе генераторов псевдослучайных последовательностей двоичных чисел устройство предназначено для выявления заданных групп (рядов) подряд идущих единичных бит и определение количества таких групп единичных бит.

При обработке результатов физических экспериментов устройство предназначено для выявления событий (областей) заданной ширины диапазона, координат событий и определение количества событий.

Техническим результатом изобретения является расширение арсенала средств того же назначения, в части возможности выявления единичных групп заданной размерности, определение количества групп и их расположение во входной последовательности данных.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для детектирования единичных групп бит в бинарной последовательности содержит внешний вход данных DI, группу внешних выходов данных QB, группу внешних выходов количества групп QG, первый RS-триггер пуска-останова TSS 1, первый счетчик бит СТВ 2, регистр номера первого бита группы RGB 3, первый элемент И 4, первый элемент ИЛИ 5 с одним инверсным входом, второй триггер единичных бит TR1 6, второй элемент И 7 с одним инверсным входом, второй счетчик единиц CTU 8, блок равенства нижней границе 9, блок равенства верхней границе 10, третий триггер нижней границы TRL 11, четвертый триггер верхней границы TRM 12, третий 13 и четвертый 14 элементы И с двумя инверсными входами, второй элемент ИЛИ 15, выходной буфер ОВ 16 и третий счетчик количества групп CTG 17,

а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ,

причем внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1 и первого счетчика бит СТВ 2,

внешний тактовый вход устройства С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, первого счетчика бит СТВ 2, регистра номера первого бита группы RGB 3, второго триггера единичных бит TR1 6, второго счетчика единиц CTU 8, третьего триггера нижней границы TRL 11, четвертого триггера верхней границы TRM 12, выходного буфера ОВ 16 и третьего счетчика количества групп CTG 17,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1, с входом L разрешения записи первого счетчика бит СТВ 2, с входами R синхронной установки в нулевое состояние регистра номера первого бита группы RGB 3, выходного буфера ОВ 16 и третьего счетчика количества групп CTG 17, и соединен с первым прямым входом первого элемента ИЛИ 5 с одним инверсным входом, выход которого соединен с входами R синхронной установки в нулевое состояние второго триггера единичных бит TR1 6, второго счетчика единиц CTU 8, третьего триггера нижней границы TRL 11 и четвертого триггера верхней границы TRM 12,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с входом СЕ разрешения работы первого счетчика бит СТВ 2 и с первым входом первого элемента И 4, второй вход которого соединен с внешним входом данных DI,

на группу информационных D-входов первого счетчика бит СТВ 2 подано значение двоичного кода «0…01», а группа выходов первого счетчика бит СТВ 2 подключена к группе информационных D-входов регистра номера первого бита группы RGB 3, у которого группа выходов соединена с первой группой информационных D-входов выходного буфера ОВ 16, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 16 являются группой внешних выходов данных QB и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

причем выход первого элемента И 4 соединен с входом S синхронной установки в единичное состояние второго триггера единичных бит TR1 6, со вторым инверсным входом первого элемента ИЛИ 5 с одним инверсным входом, с входом СЕ разрешения работы второго счетчика единиц CTU 8, первыми инверсными входами третьего 13 и четвертого 14 элементов И с двумя инверсными входами и с первым прямым входом второго элемента И 7 с одним инверсным входом, у которого второй инверсный вход соединен с выходом второго триггера единичных бит TR1 6, а выход второго элемента И 7 с одним инверсным входом соединен с входом СЕ разрешения работы регистра номера первого бита группы RGB 3,

внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит соединены с первыми группами входов соответственно блока равенства нижней границы 9 и блока равенства верхней границы 10, вторые группы входов которых соединены между собой, соединены со второй группой информационных D-входов регистра номера первого бита группы RGB 3 и подключены к группе выходов второго счетчика единиц CTU 8,

причем выход блока равенства нижней границы 9 соединен с входом S синхронной установки в единичное состояние третьего триггера нижней границы TRL 11 и со вторым прямым входом третьего 13 элемента И с двумя инверсными входами, выход которого соединен с первым входом второго элемента ИЛИ 15,

выход блока равенства верхней границы 10 соединен с входом S синхронной установки в единичное состояние четвертого триггера верхней границы TRM 12, выход которого соединен с третьими инверсными входами третьего 13 и четвертого 14 элементов И с двумя инверсными входами,

кроме того выход третьего триггера нижней границы TRL 11 соединен со вторым прямым входом четвертого 14 элемента И с двумя инверсными входами, выход которого соединен со вторым входом второго элемента ИЛИ 15, выход которого соединен с входом СЕ разрешения работы выходного буфера ОВ 11 и третьего счетчика количества групп CTG 17, группа выходов которого является группой внешних выходов количества групп QG.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

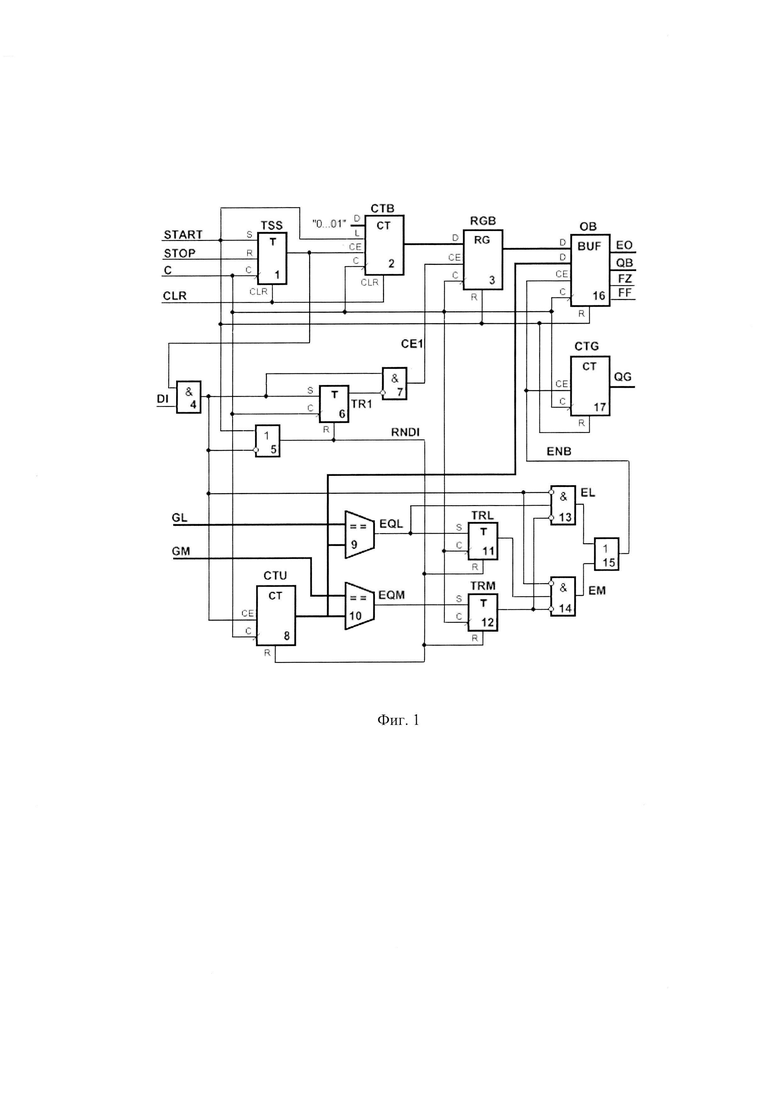

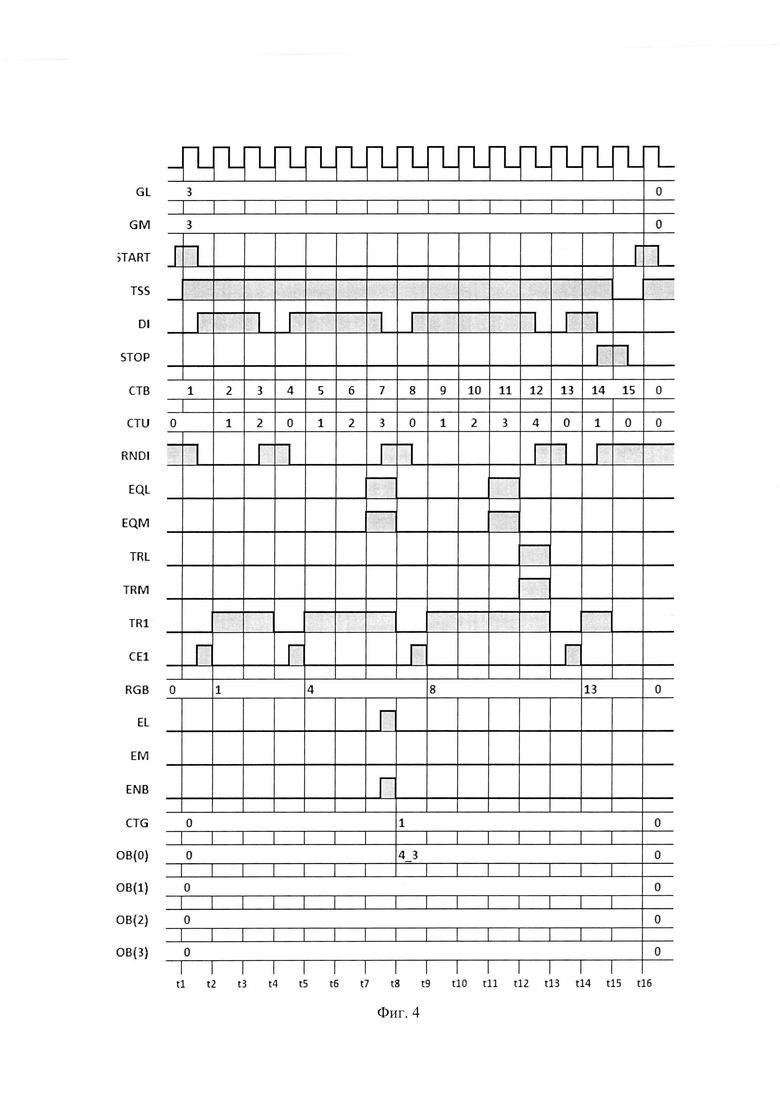

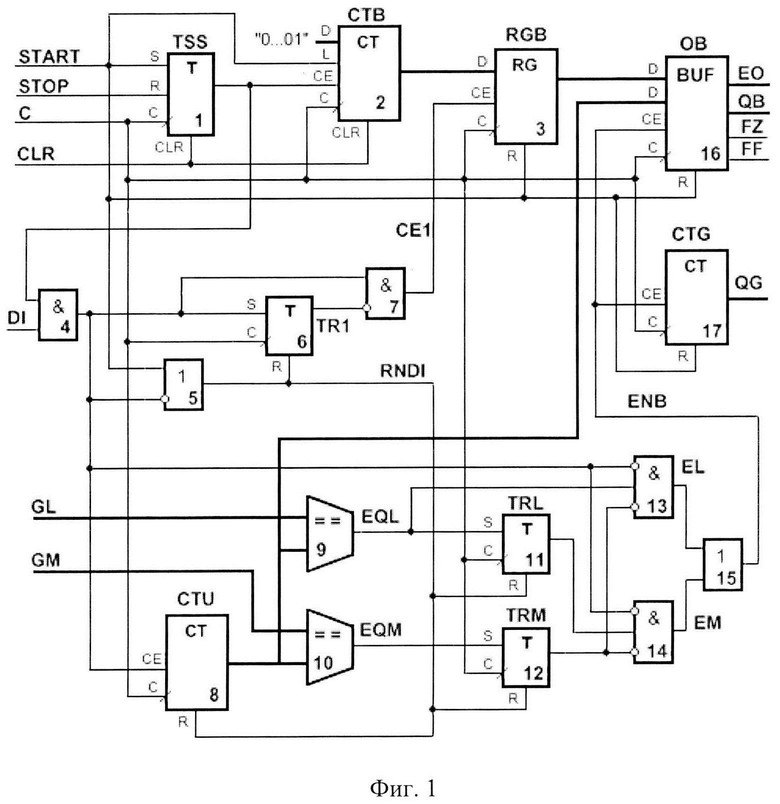

На фиг. 1 представлена схема предлагаемого устройства. На фиг. 2, фиг. 3 и фиг. 4 приведены временные диаграммы работы устройства.

На фиг. 1 - 4 и в тексте приняты следующие обозначения:

BUF - буфер с дисциплиной обслуживания FIFO,

С - тактовый вход,

СЕ - вход разрешения работы,

СЕ1 - флаг первого единичного бита в группе,

CLR - вход асинхронной установки в нулевое состояние,

СТВ - счетчик бит,

CTG - счетчик групп,

CTU - счетчик единиц,

D - информационные входы,

DI - внешний вход данных,

ЕО - внешняя шина управления обменом с выходным буфером ОВ,

EQL - флаг равенства нижней границы,

EQM - флаг равенства верхней границы,

EL - флаг нижней границы диапазона,

ED - флаг группы диапазона,

ENB - флаг записи в выходной буфер,

FF - внешний флаг «Буфер заполнен»,

FZ - внешний флаг «Буфер пуст»,

GL - входная шина нижней границы диапазона единичных бит,

GM - входная шина верхней границы диапазона единичных бит,

L - вход разрешения записи,

N - размерность (длина) входной последовательности данных,

ОВ - выходной буфер,

QG - группа внешних выходов количества групп,

QB - группа внешних выходов данных,

RG - регистр,

RGB - регистр номера первого бита группы,

RNDI - синхронный сброс при нулевом бите,

R - вход синхронной установки в нулевое состояние,

S - вход синхронной установки в единичное состояние,

START - внешний вход пуска,

STOP - внешний вход останова,

Т - триггер,

TR1 - триггер единичных бит,

TRL - триггер нижней границы,

TRM - триггер верхней границы,

TSS - триггер пуска-останова,

1 - первый RS-триггер пуска-останова TSS,

2 - первый счетчик бит СТВ,

3 - регистр номера первого бита группы RGB,

4 - первый элемент И,

5 - первый элемент ИЛИ с одним инверсным входом,

6 - второй триггер единичных бит TR1,

7 - второй элемент И с одним инверсным входом,

8 - второй счетчик единиц CTU,

9 - блок равенства нижней границе,

10 - блок равенства верхней границе,

11 - третий триггер нижней границы TRL,

12 - четвертый триггер верхней границы TRM,

13 - третий элемент И с двумя инверсными входами,

14 - четвертый элемент И с двумя инверсными входами,

15 - второй элемент ИЛИ,

16 - выходной буфер ОВ,

17 - третий счетчик количества групп CTG.

Предлагаемое устройство содержит внешний вход данных DI, группу внешних выходов данных QB, группу внешних выходов количества групп QG, первый RS-триггер пуска-останова TSS 1, первый счетчик бит СТВ 2, регистр номера первого бита группы RGB 3, первый элемент И 4, первый элемент ИЛИ 5 с одним инверсным входом, второй триггер единичных бит TR1 6, второй элемент И 7 с одним инверсным входом, второй счетчик единиц CTU 8, блок равенства нижней границе 9, блок равенства верхней границе 10, третий триггер нижней границы TRL 11, четвертый триггер верхней границы TRM 12, третий 13 и четвертый 14 элементы И с двумя инверсными входами, второй элемент ИЛИ 15, выходной буфер ОВ 16 и третий счетчик количества групп CTG 17.

В предлагаемое устройство также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

Внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1 и первого счетчика бит СТВ 2.

Внешний тактовый вход устройства С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, первого счетчика бит СТВ 2, регистра номера первого бита группы RGB 3, второго триггера единичных бит TR1 6, второго счетчика единиц CTU 8, третьего триггера нижней границы TRL 11, четвертого триггера верхней границы TRM 12, выходного буфера ОВ 16 и третьего счетчика количества групп CTG 17.

Внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1, с входом L разрешения записи первого счетчика бит СТВ 2, с входами R синхронной установки в нулевое состояние регистра номера первого бита группы RGB 3, выходного буфера ОВ 16 и третьего счетчика количества групп CTG 17, и соединен с первым прямым входом первого элемента ИЛИ 5 с одним инверсным входом, выход которого соединен с входами R синхронной установки в нулевое состояние второго триггера единичных бит TR1 6, второго счетчика единиц CTU 8, третьего триггера нижней границы TRL 11 и четвертого триггера верхней границы TRM 12.

Внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1.

Первый RS-триггер пуска-останова TSS 1 предназначен для выделения цикла работы предлагаемого устройства, между сигналами START и STOP, для входной последовательности данных DI размерности N. Причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с входом СЕ разрешения работы первого счетчика бит СТВ 2 и с первым входом первого элемента И 4, второй вход которого соединен с внешним входом данных DI.

Первый счетчик бит СТВ 2 предназначен для определения номера текущего разряда (бита) входной последовательности данных DI размерности N.

На группу информационных D-входов первого счетчика бит СТВ 2 подано значение двоичного кода «0…01», а группа выходов первого счетчика бит СТВ 2 подключена к группе информационных D-входов регистра номера первого бита группы RGB 3, у которого группа выходов соединена с первой группой информационных D-входов выходного буфера ОВ 16, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 16 являются группой внешних выходов данных QB и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

Выходной буфер ОВ 16 предназначен для накопления номеров первых бит единичных групп во входной последовательности и размерности этих групп, в пределах заданных нижней GL и верхней GM границами диапазона единичных бит.

Выход первого элемента И 4 соединен с входом S синхронной установки в единичное состояние второго триггера единичных бит TR1 6, со вторым инверсным входом первого элемента ИЛИ 5 с одним инверсным входом, с входом СЕ разрешения работы второго счетчика единиц CTU 8, первыми инверсными входами третьего 13 и четвертого 14 элементов И с двумя инверсными входами и с первым прямым входом второго элемента И 7 с одним инверсным входом, у которого второй инверсный вход соединен с выходом второго триггера единичных бит TR1 6, а выход второго элемента И 7 с одним инверсным входом соединен с входом СЕ разрешения работы регистра номера первого бита группы RGB 3.

Внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит соединены с первыми группами входов соответственно блока равенства нижней границы 9 и блока равенства верхней границы 10, вторые группы входов которых соединены между собой, соединены со второй группой информационных D-входов регистра номера первого бита группы RGB 3 и подключены к группе выходов второго счетчика единиц CTU 8.

Блок равенства нижней границы 9 и блок равенства верхней границы 10 формируют на выходах единичные значения при равенства количества единичных бит в текущей группе с заданными соответственно нижней GL и верхней GM границами диапазона единичных бит.

Причем выход блока равенства нижней границы 9 соединен с входом S синхронной установки в единичное состояние третьего триггера нижней границы TRL 11 и со вторым прямым входом третьего 13 элемента И с двумя инверсными входами, выход которого соединен с первым входом второго элемента ИЛИ 15.

Выход блока равенства верхней границы 10 соединен с входом S синхронной установки в единичное состояние четвертого триггера верхней границы TRM 12, выход которого соединен с третьими инверсными входами третьего 13 и четвертого 14 элементов И с двумя инверсными входами.

Кроме того выход третьего триггера нижней границы TRL 11 соединен со вторым прямым входом четвертого 14 элемента И с двумя инверсными входами, выход которого соединен со вторым входом второго элемента ИЛИ 15, выход которого соединен с входом СЕ разрешения работы выходного буфера ОВ 11 и третьего счетчика количества групп CTG 17, группа выходов которого является группой внешних выходов количества групп QG.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

На внешний вход данных DI последовательно разряд за разрядом поступают биты входной последовательности данных размерностью N. На входных шинах нижней границы GL и верхней границы GM устанавливаются значения границ диапазона единичных бит.

Устройство начинает работать после подачи единичного сигнала START=1, при котором по фронту тактового сигнала С в единичное состояние устанавливается первый RS триггер 1 пуска-останова TSS и в нулевое состояние устанавливаются регистр 3 номера первого бита группы RGB, выходной буфер ОВ 16, третий счетчик 17 количества групп CTG, а также загружается код «0…01» в первый счетчик бит СТВ 2 - выполняется настройка на первый бит в последовательности входных данных DI.

При этом одновременно единичное значение RNDI=1 также устанавливается на выходе первого элемента ИЛИ 5 с одним инверсным входом, при котором по фронту тактового сигнала С в нулевое состояние устанавливаются второй триггер 6 единичных бит TR1, второй счетчик 8 единиц CTU, третий триггер 11 нижней границы TRL и четвертый триггер 12 верхней границы TRM.

Единичное значение с выхода первого триггера 1 пуска-останова TSS=1 также разрешает на следующих тактах работать в счетном режиме первому счетчику бит СТВ 2, на котором устанавливается код номера текущего разряда входной последовательности.

При единичном значении на выходе первого триггера 1 пуска-останова TSS=1 входные данные DI передаются на элементы устройства.

Устройство определяет единичную группу бит следующим образом. При появлении единичного значения на входе данных DI=1, по фронту тактового сигнала С второй триггер 6 единичных бит TR1 переключается в единичное состояние TR1=1 и одновременно считает второй счетчик 8 единиц CTU. Одновременно единичное значение с входа данных DI=1 поступает на прямой вход второго элемента И 7, на инверсном входе которого установлено нулевое значение с выхода второго триггере 6 единичных бит TR1. Далее единичное значение флага первого единичного бита в группе СЕ 1=1 с выхода второго элемента И 7 передается на вход разрешения СЕ регистра 3 номера первого бита группы RGB и по фронту тактового сигнала С текущее значение кода номера бита во входной последовательности с первого счетчика бит СТВ 2 записывается в регистр 3 номера первого бита группы RGB. На следующих тактах при единичных значениях на входе данных DI=1 на выходе второго элемента И 7 устанавливается нулевое значение флага первого единичного бита в группе СЕ 1=0, так как на единичное значение установлено на выходе второго триггере 6 единичных бит TR1=1.

Значение кода с выхода второго счетчика 8 единиц CTU сравнивается с кодами границ диапазона единичных бит в блоках равенства нижней 9 и верхней 10 границ. При равенстве соответствующих кодов формируются соответственно единичный флаг равенства нижней границы EQL=1 или единичный флаг равенства верхней границы EQM=1, которые далее передаются на входы S синхронной установки в единичное состояние соответственно третьего триггера 11 нижней границы TRL или четвертого триггера 12 верхней границы TRM.

При единичном значении флага равенства нижней границы EQL=1, нулевом значении третьего триггера 11 нижней границы TRL=0, нулевом значении четвертого триггера 12 верхней границы TRM=0 и появлении нулевого значения бита на входе данных DI=0, когда количество единичных бит в группе равно нижней границы GL, меньше верхней границы GM и детектировании нулевого бита после группы единичных бит, устанавливается единичное значение флага нижней границы диапазона EL=1 на выходе третьего элемента И 13, далее устанавливается единичное значение флага записи в выходной буфер ENB=1 на выходе второго элемента ИЛИ 15, которое передается на входы разрешения СЕ выходного буфера ОВ 16 и третьего счетчика 17 количества групп CTG. При этом значения кода с выхода регистра 3 номера первого бита группы RGB и кода с выхода второго счетчика 8 единиц CTU записываются в выходной буфер ОВ 16, а также увеличивается на единицу значение в третьем счетчике 17 количества групп CTG.

При единичном значении на выходе третьего триггера 11 нижней границы TRL=1, нулевом значении на выходе четвертого триггера 12 верхней границы TRM=0 и появлении нулевого значения бита на входе данных DI=0, когда количество единичных бит в группе больше нижней границы GL, меньше или равно верхней границы GM и детектировании нулевого бита после группы единичных бит, устанавливается единичное значение флага диапазона ED=1 на выходе четвертого элемента И 14, далее устанавливается единичное значение флага записи в выходной буфер ENB=1 на выходе второго элемента ИЛИ 15, которое передается на вход разрешения СЕ выходного буфера ОВ 16 и третьего счетчика 17 количества групп CTG. При этом значения кода с выхода регистра 3 номера первого бита группы RGB и кода с выхода второго счетчика 8 единиц CTU записываются в выходной буфер ОВ 16, а также увеличивается на единицу значение в третьем счетчике 17 количества групп CTG.

При единичном значении на выходе третьего триггера 11 нижней границы TRL=1, единичном значении на выходе четвертого триггера 12 верхней границы TRM=1 и появлении нулевого значения бита на входе данных DI=0, когда количество единичных бит в группе больше нижней границы GL, больше верхней границы GM и детектировании нулевого бита после группы единичных бит, устанавливаются нулевые значения флага нижней границы диапазона EL=0 и флага диапазона ED=0, поэтому не выполняется запись в выходной буфер ОВ 16 и третий счетчик 17 количества групп CTG.

Кроме того, при детектировании нулевого значения бита на входе данных DI=0 устанавливается единичное значение сигнала синхронного сброса RNDI=1 на выходе первого элемента ИЛИ 5 с одним инверсным входом, по которому в нулевое состояние устанавливаются второй триггер 6 единичных бит TR1=0, второй счетчик 8 единиц CTU=0, третий триггер 11 нижней границы TRL=0 и четвертый триггер 12 верхней границы TRM=0. Таким образом, устройство настроено на выявление следующих групп единичных бит.

При заполнении выходного буфера ОВ 11 формируется флаг «Буфер заполнен» FF=1. Считывание данных из выходного буфера ОВ 11 осуществляется по сигналам с внешней шины управления обменом ЕО и при достижении нулевого адреса формируется флаг «Буфер пуст» FZ=1.

При единичном значении сигнала STOP по фронту тактового сигнала С в нулевое состояние устанавливается первый RS-триггер пуска-останова TSS 1 и запрещается передача входных данных DI в устройство.

Предлагаемое устройство работает следующим образом.

При подаче сигнала на вход CLR асинхронной установки в нулевое состояние устанавливается первый RS-триггер пуска-останова TSS 1 и первый счетчик бит СТВ 2. Тактовые сигналы с входа С постоянно поступают на входы синхронизации всех триггеров и счетчиков, режимы работы которых задаются сигналами на соответствующих входах управления, а исполняются по фронтам тактовых сигналов С.

На временных диаграммах на фиг. 2-4 приведены временные диаграммы работы предлагаемого устройства, отражающие основные особенности работы устройства. На фиг. 2 заданы нижняя GL=2 и верхняя GM=4 границы диапазона единичных бит, а на внешний вход данных DI для N=13 подана первая последовательность «0111011011110» содержащая три группы единичных бит. На фиг. 3 заданы нижняя GL=2 и верхняя GM=4 границы диапазона единичных бит, а на внешний вход данных DI для N=14 подана вторая последовательность «11011111001110» содержащая также три группы единичных бит. На фиг. 4 заданы равные нижняя GL=3 и верхняя GM=3 границы диапазона единичных бит, а на внешний вход данных DI для N=14 подана третья последовательность «11011101111010» содержащая четыре группы единичных бит.

Работа устройства для каждой входной последовательности начинается после подачи единичного сигнала START=1. При этом по фронту первого тактового сигнала С (моменты времени t1 на фиг. 2-4) в единичное состояние устанавливается первый RS-триггер 1 пуска-останова TSS=1, в нулевое состояние устанавливаются регистр 3 номера первого бита группы RGB=0, второй триггер 6 единичных бит TR1=0, второй счетчик 8 единиц CTU=0, третий триггер 11 нижней границы TRL=0, четвертый триггер 12 верхней границы TRM=0 и третий счетчик 17 количества групп CTG, а также загружается код «0…01» в первый счетчик бит 2 СТВ=1 и устанавливается начальный нулевой адрес в выходном буфере ОВ 16.

Единичное значение с выхода первого RS-триггера 1 пуска-останова TSS=1 также разрешает на следующих тактах работать в счетном режиме первому счетчику бит СТВ 2, на котором устанавливается код номера текущего разряда входной последовательности.

На внешний вход данных DI последовательно разряд за разрядом поступают биты входной последовательности данных размерностью N. В момент времени t2 (фиг. 2) на вход данных DI поступает нулевое значение первого бита входной последовательности DI=0. При этом выполняется только счет бит в первом 2 счетчике бит СТВ=2, а другие элементы устройства сохраняют свои значения.

Между моментами времени t2 - t3 на вход данных DI поступает единичное значение второго бита входной последовательности DI=1, по которому формируется единичное значение на выходе первого элемента И 4 и далее передается на вход S синхронной установки в единичное состояние второго триггера 6 единичных бит TR1 и на вход разрешения работы СЕ второго счетчика 8 единиц CTU, а также формируется единичное значение флага первого единичного бита в группе СЕ1=1 на выходе второго элемента И 7, которое передается на вход разрешения работы СЕ регистра 3 номера первого бита группы RGB.

В момент времени t3 (фиг. 2) по фронту тактового сигнала С в единичное состояние переключается второй триггер 6 единичных бит TR1=1, осуществляется счет во втором счетчике 8 единиц CTU=1, значение кода номера текущего бит СТВ=2 (номер первого бита первой единичной группы) с первого счетчика бит 2 записывается в регистр 3 номера первого бита группы RGB=2, а также формируется значение кода номера следующего бита СТВ=3 входной последовательности. При этом одновременно в единичное состояние устанавливается второй триггер 6 единичных бит TR1=1, по которому устанавливается нулевое значение флага первого единичного бита в группе СЕ 1=0 на выходе второго элемента И 7, запрещая прием на следующих тактах (моменты времени t4 и t5) в регистр 3 номера первого бита группы RGB для первой группы единичных бит.

Между моментами времени t3 - t4 и t4 - t5 на вход данных DI поступают единичные значения третьего и четвертого бит входной последовательности DI=1. В момент времени t4 (фиг. 2) по фронту тактового сигнала С осуществляется счет второго единичного бита во втором счетчике 8 единиц CTU=2, значение которого сравнивается с кодом нижней границы GL=2 в блоке равенства нижней границе 9 и на выходе формируется единичный флаг равенства нижней границы EQL=1, по которому в момент времени t5 в единичное состояние переключается третий триггер 11 нижней границы TRL=1. Кроме того в момент времени t5 (фиг. 2) по фронту тактового сигнала С также осуществляется счет третьего единичного бита первой группы во втором счетчике 8 единиц CTU=3.

Между моментами времени t5 - t6 на вход данных DI поступает нулевое значение пятого бита входной последовательности DI=0, по которому формируется единичное значение флага диапазона ED=1 на выходе четвертого элемента И 14, далее устанавливается единичное значение флага записи в выходной буфер ENB=1 на выходе второго элемента ИЛИ 15, которое далее передается на входы разрешения СЕ выходного буфера ОВ 16 и третьего счетчика 17 количества групп CTG. Поэтому в момент времени t6 значения кода с выхода регистра 3 номера первого бита группы RGB=2 и кода с выхода второго счетчика 8 единиц CTU=3 записываются в выходной буфер 16 по нулевому адресу ОВ(0)=2_3. Также в момент времени t6 увеличивается на единицу значение в третьем счетчике 17 количества групп CTG=1.

Таким образом, детектируется первая единичная группа, содержащая три единичных бита с номером первого бита равным двум (при заданных нижней GL=2 и верхней GM=4 границах диапазона единичных бит), содержащая количество бит CTU=3 больше нижней границы (CTU=3)>(GL=2) и меньше верхней (CTU=3)<(GM=4) границы.

Одновременно между моментами времени t5 - t6 при нулевом значении на входе данных DI=0 устанавливается единичное значение сигнала синхронного сброса RNDI=1 на выходе первого элемента ИЛИ 5 с одним инверсным входом, по которому в момент времени t6 по фронту тактового сигнала С в нулевое состояние устанавливаются второй триггер 6 единичных бит TR1=0, второй счетчик 8 единиц CTU=0, третий триггер 11 нижней границы TRL=0 и четвертый триггер 12 верхней границы TRM=0. Таким образом, устройство настроено на выявление второй группы единичных бит во входной последовательности.

Между моментами времени t6 - t7 (фиг. 2) на вход данных DI поступает единичное значение шестого разряда последовательности DI=1, по которому формируется единичное значение на выходе первого элемента И 4 и далее передается на вход S синхронной установки в единичное состояние второго триггера 6 единичных бит TR1 и на вход разрешения работы СЕ второго счетчика 8 единиц CTU, а также формируется единичное значение флага первого единичного бита в группе СЕ1=1 на выходе второго элемента И 7, которое передается на вход разрешения работы СЕ регистра 3 номера первого бита группы RGB.

В момент времени t7 (фиг. 2) по фронту тактового сигнала С в единичное состояние переключается второй триггер 6 единичных бит TR1=1, осуществляется счет во втором счетчике 8 единиц CTU=1, значение кода номера текущего бит СТВ=6 (номер первого бита второй единичной группы) с первого счетчика бит 2 записывается в регистр 3 номера первого бита группы RGB=6, а также формируется значение кода номера следующего бита СТВ=7 входной последовательности.

Между моментами времени t7 - t8 на вход данных DI поступает единичное значение седьмого бита входной последовательности DI=1. В момент времени t8 (фиг. 2) по фронту тактового сигнала С осуществляется счет второго единичного бита во втором счетчике 8 единиц CTU=2, значение которого сравнивается с кодом нижней границы GL=2 в блоке равенства нижней границе 9 и на выходе формируется единичный флаг равенства нижней границы EQL=1. Кроме того в момент времени t8 (фиг. 2) по фронту тактового сигнала С также осуществляется счет второго единичного бита второй группы во втором счетчике 8 единиц CTU=2.

Между моментами времени t8 - t9 на вход данных DI поступает нулевое значение восьмого бита входной последовательности DI=0, по которому формируется единичное значение флага нижней границы диапазона EL=1 на выходе третьего элемента И 13 и далее устанавливается единичное значение флага записи в выходной буфер ENB=1 на выходе второго элемента ИЛИ 15, по которому в момент времени t9 значения кода с выхода регистра 3 номера первого бита группы RGB=6 и кода с выхода второго счетчика 8 единиц CTU=2 записываются в выходной буфер 16 по первому адресу ОВ(1)=6_2. Также в момент времени t9 увеличивается на единицу значение в третьем счетчике 17 количества групп CTG=2.

Таким образом, детектируется вторая единичная группа, содержащая два единичных бита с номером первого бита равным шести (при заданных нижней GL=2 и верхней GM=4 границах диапазона единичных бит), содержащая количество бит CTU=2 равное нижней границе (CTU=2)=(GL=2) и меньше верхней (CTU=2)<(GM=4) границы.

В моменты времени t10, t11 и t12 (фиг. 2) детектируются единичные значения девятого, десятого и одиннадцатого бит третьей единичной группы аналогично моментам времени t3, t4 и t5 первой единичной группы. При этом будут установлены следующие значения RGB=9, СТВ=12, CTU=3,TRL=1.

Между моментами времени t12 - t13 на вход данных DI поступает единичное значение двенадцатого бита входной последовательности DI=1. В момент времени t13 (фиг. 2) по фронту тактового сигнала С осуществляется счет четвертого единичного бита третьей группы во втором счетчике 8 единиц CTU=4, значение которого сравнивается с кодом верхней границы GM=4 в блоке равенства верхней границе 10 и на выходе формируется единичный флаг равенства верхней границы EQM=1.

Между моментами времени t13 - t14 на вход данных DI поступает нулевое значение тринадцатого бита входной последовательности DI=0, по которому формируется единичное значение флага диапазона Е2 ED=1 на выходе четвертого элемента И 14, далее устанавливается единичное значение флага записи в выходной буфер ENB=1 на выходе второго элемента ИЛИ 15, по которому в момент времени t14 значения кода с выхода регистра 3 номера первого бита группы RGB=9 и кода с выхода второго счетчика 8 единиц CTU=4 записываются в выходной буфер 16 по второму адресу ОВ(2)=9_4. Также в момент времени t14 увеличивается на единицу значение в третьем счетчике 17 количества групп CTG=3.

Таким образом, детектируется третья единичная группа, содержащая четыре единичных бита с номером первого бита равным девяти (при заданных нижней GL=2 и верхней GM=4 границах диапазона единичных бит), содержащая количество бит CTU=4, которое больше нижней границы (CTU=4)>(GL=2) и равное верхней (CTU=4)=(GM=4) границе.

При подаче единичного сигнала STOP=l между моментами t13 - t14 по фронту тактового сигнала С в момент времени tl4 в нулевое состояние устанавливается первый RS-триггер 1 пуска-останова TSS=0.

Таким образом, для первой последовательности «0111011011110» сформированы следующие значения: номера первого бита и количество единичных бит в группах записанные в выходной буфер ОВ(0)=2_3, ОВ(1)=6_2, ОВ(2)=9_4 и количество групп QG=3.

Считывание результатов из выходного буфера ВО 16 выполняется под управлением по внешней шине управления ЕО. При реализации выходного буфера ВО 16 в виде двухпортовой памяти FIFO, обмен можно выполнять в процессе детектирования единичных групп с учетом значений флагов «Буфер пуст» FZ и «Буфер заполнен» FF.

Обработка следующей входной последовательности начинается после подачи единичного сигнала START=1 (например, на фиг.2 в момент времени t16).

На фиг. 3 во второй входной последовательности, в отличие от первой входной последовательности на фиг. 2, первая единичная группа начинается с первого бита последовательности и содержит два единичных бита. Поэтому для первой группы в момент времени t4 формируются следующие значения: RGB=1, CTU=2, ОВ(0)=1_2, CTG=1, CTB=4.

Вторая единичная группа начинается с четвертого бита и содержит пять единичных бит. В момент времени t6 (фиг. 3) по фронту тактового сигнала С осуществляется счет второго единичного бита второй группы во втором счетчике 8 единиц CTU=2, значение которого далее сравнивается с кодом нижней границы GL=2 в блоке равенства нижней границе 9 и на выходе формируется единичный флаг равенства нижней границы EQL=1, по которому в момент времени t7 в единичное состояние переключается третий триггер 11 нижней границы TRL=1. Кроме того в моменты времени t7 и t8 осуществляется подсчет третьего и четвертого единичных бит второй группы во втором счетчике 8 единиц и устанавливается значение CTU=4, которое сравнивается с кодом верхней границы GM=4 в блоке равенства верхней границе 10 и на выходе формируется единичный флаг равенства верхней границы EQM=1, по которому в момент времени t9 в единичное состояние переключается четвертый триггер 12 верхней границы TRM=1. При этом в момент времени t9 в устройстве будут сформированы следующие значения: RGB=4, СТВ=9, TRL=1, TRM=1, TR1=1, CTU=5.

Далее между моментами времени t9 - t10 на вход данных DI поступает нулевое значение девятого бита входной последовательности DI=0, но так как в единичное состояние установлен четвертый триггер 12 верхней границы TRM=1, т.е. количество единичных бит во второй группе превышает верхнюю границу диапазона GM=4, то формируется нулевое значение флага записи в выходной буфер ENB=0 на выходе второго элемента ИЛИ 15, и поэтому в момент времени t10 не выполняются запись в выходной буфер ОВ и счет групп в третьем счетчике 17 CTG.

В момент времени t11 на вход данных DI также поступает нулевое значение десятого бита входной последовательности, по которому не проводятся запись в выходной буфер ОВ 16 и счет групп в третьем счетчике 17 количества групп CTG.

Далее в моменты времени t12, t13 и t14 поступают единичные значения одиннадцатого, двенадцатого и тринадцатого бит третьей единичной группы входной последовательности, для которой в момент времени t15 формируются следующие значения: RGB=11, CTU=3, ОВ(1)=11_3, CTG=2, СТВ=14.

Таким образом, для второй последовательности «11011111001110» сформированы следующие значения: номера первого бита и количество единичных бит в группах записанные в выходной буфер ОВ(0)=1_2, ОВ(1)=11_3 и количество групп QG=2. Количество единичных групп QG=2, так как вторая единичная группа в последовательности содержит пять единичных бит, что превышает верхнюю границу диапазона.

На фиг. 4 для третьей входной последовательности заданы равные нижняя GL=3 и верхняя GM=3 границы диапазона единичных бит, а на внешний вход данных DI для N=14 подана третья последовательность «11011101111010» содержащая четыре группы единичных бит.

Первая единичная группа входной последовательности содержит первый и второй единичные биты. При этом количество (сумма) единичных бит в группе CTU=2 не равно границам заданного диапазона, поэтому не проводятся запись в выходной буфер ОВ 16 и счет групп в третьем счетчике 17 количества групп CTG.

Вторая единичная группа входной последовательности содержит три единичных бита: четвертый, пятый и шестой. При подсчете единичных бит в момент времени t7 во втором счетчике 8 единиц будет установлен код CTU=3, который сравнивается с кодами нижней GL=3 и верхней GM=3 границами диапазона в блоках равенства нижней 9 и верхней 10 границ и формируются единичные значения флага равенства нижней границы EQL=1 и флага равенства верхней границы EQM=1.

Далее между моментами времени t7 - t8 (фиг. 4) на вход данных DI поступает нулевое значение седьмого бита входной последовательности DI=0 и так как в нулевое состояние установлен четвертый триггер 12 верхней границы TRM=0 и при единичном значении флага равенства нижней границы EQL=1 формируется единичное значение флага нижней границы диапазона EL=1 на выходе третьего элемента И 13, далее устанавливается единичное значение флага записи в выходной буфер ENB=1 на выходе второго элемента ИЛИ 15, которое далее передается на входы разрешения СЕ выходного буфера ОВ 16 и третьего счетчика 17 количества групп CTG. Поэтому в момент времени t8 значения кода с выхода регистра 3 номера первого бита группы RGB=4 и кода с выхода второго счетчика 8 единиц CTU=3 записываются в выходной буфер 16 по нулевому адресу ОВ(0)=4_3, а также в момент времени t8 увеличивается на единицу значение в третьем счетчике 17 количества групп CTG=1.

Третья единичная группа входной последовательности содержит четыре единичных бита: восьмой, девятый, десятый и одиннадцатый. При подсчете единичных бит в момент времени t11 во втором счетчике 8 единиц будет установлен код CTU=3, который сравнивается с равными кодами нижней GL=3 и верхней GM=3 границами диапазона в блоках равенства нижней 9 и верхней 10 границ и формируются единичные значения флага равенства нижней границы EQL=1 и флага равенства верхней границы EQM=1, по которым в момент времени t12 в единичное состояние устанавливаются третий триггера 11 нижней границы TRL=1 и четвертый триггер 12 верхней границы TRM=T.

Далее между моментами времени t12 - t13 (фиг. 4) на вход данных DI поступает нулевое значение двенадцатого бита входной последовательности DI=0 и так как в единичное состояние установлен четвертый триггер 12 верхней границы TRM=1, то формируется нулевое значение флага записи в выходной буфер ENB=0. При этом количество (сумма) единичных бит в третьей группе CTU=4 больше границ заданного диапазона, поэтому не проводятся запись в выходной буфер ОВ 16 и счет групп в третьем счетчике 17 количества групп CTG.

Четвертая единичная группа входной последовательности содержит только один единичный тринадцатый бит. При этом количество (сумма) единичных бит в группе CTU=1 не равно границам заданного диапазона, поэтому не проводятся запись в выходной буфер ОВ 16 и счет групп в третьем счетчике 17 количества групп CTG.

Таким образом, для третьей последовательности «11011101111010» (фиг. 4) сформированы значения только для одной группы: номер первого бит и количество единичных бит в группе записанные в нулевой адрес выходного буфера ОВ(0)=4_3 и количество групп QG=1.

Таким образом, в предлагаемом устройстве для входных последовательностей данных размерностью N, поступающих на внешний вход данных DI, на соответствующих внешних выходах групп устройства формируются двоичные коды QB, содержащие номер первого бит и количество единичных бит в группе, и двоичный код QG количества групп заданной размерности, а также формируются флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату - выявление групп единичных бит заданной размерности, определение количества групп во входной последовательности данных и их расположение во входной последовательности.

Изобретение относится к области вычислительной техники. Технический результат - возможность выявления единичных групп заданной размерности, определение количества групп и их расположение во входной последовательности данных. Указанный результат достигается за счет того, что устройство содержит внешний вход данных DI, группу внешних выходов данных QB, группу внешних выходов количества групп QG, первый RS-триггер пуска-останова TSS 1, первый счетчик бит СТВ 2, регистр номера первого бита группы RGB 3, первый элемент И 4, первый элемент ИЛИ 5 с одним инверсным входом, второй триггер единичных бит TR1 6, второй элемент И 7 с одним инверсным входом, второй счетчик единиц CTU 8, блок равенства нижней границе 9, блок равенства верхней границе 10, третий триггер нижней границы TRL 11, четвертый триггер верхней границы TRM 12, третий 13 и четвертый 14 элементы И с двумя инверсными входами, второй элемент ИЛИ 15, выходной буфер ОВ 16 и третий счетчик количества групп CTG 17, а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ. 4 ил.

Устройство для детектирования единичных групп бит в бинарной последовательности, содержащее внешний вход данных DI, группу внешних выходов данных QB, группу внешних выходов количества групп QG, первый RS-триггер пуска-останова TSS 1, первый счетчик бит СТВ 2, регистр номера первого бита группы RGB 3, первый элемент И 4, первый элемент ИЛИ 5 с одним инверсным входом, второй триггер единичных бит TR1 6, второй элемент И 7 с одним инверсным входом, второй счетчик единиц CTU 8, блок равенства нижней границе 9, блок равенства верхней границе 10, третий триггер нижней границы TRL 11, четвертый триггер верхней границы TRM 12, третий 13 и четвертый 14 элементы И с двумя инверсными входами, второй элемент ИЛИ 15, выходной буфер ОВ 16 и третий счетчик количества групп CTG 17,

а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ,

причем внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующими входами асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1 и первого счетчика бит СТВ 2,

внешний тактовый вход устройства С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, первого счетчика бит СТВ 2, регистра номера первого бита группы RGB 3, второго триггера единичных бит TR1 6, второго счетчика единиц CTU 8, третьего триггера нижней границы TRL 11, четвертого триггера верхней границы TRM 12, выходного буфера ОВ 16 и третьего счетчика количества групп CTG 17,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1, с входом L разрешения записи первого счетчика бит СТВ 2, с входами R синхронной установки в нулевое состояние регистра номера первого бита группы RGB 3, выходного буфера ОВ 16 и третьего счетчика количества групп CTG 17 и соединен с первым прямым входом первого элемента ИЛИ 5 с одним инверсным входом, выход которого соединен с входами R синхронной установки в нулевое состояние второго триггера единичных бит TR1 6, второго счетчика единиц CTU 8, третьего триггера нижней границы TRL 11 и четвертого триггера верхней границы TRM 12,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с входом СЕ разрешения работы первого счетчика бит СТВ 2 и с первым входом первого элемента И 4, второй вход которого соединен с внешним входом данных DI,

на группу информационных D-входов первого счетчика бит СТВ 2 подано значение двоичного кода «0…01», а группа выходов первого счетчика бит СТВ 2 подключена к группе информационных D-входов регистра номера первого бита группы RGB 3, у которого группа выходов соединена с первой группой информационных D-входов выходного буфера ОВ 16, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 16 являются группой внешних выходов данных QB и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

причем выход первого элемента И 4 соединен с входом S синхронной установки в единичное состояние второго триггера единичных бит TR1 6, со вторым инверсным входом первого элемента ИЛИ 5 с одним инверсным входом, с входом СЕ разрешения работы второго счетчика единиц CTU 8, первыми инверсными входами третьего 13 и четвертого 14 элементов И с двумя инверсными входами и с первым прямым входом второго элемента И 7 с одним инверсным входом, у которого второй инверсный вход соединен с выходом второго триггера единичных бит TR1 6, а выход второго элемента И 7 с одним инверсным входом соединен с входом СЕ разрешения работы регистра номера первого бита группы RGB 3,

внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит соединены с первыми группами входов соответственно блока равенства нижней границы 9 и блока равенства верхней границы 10, вторые группы входов которых соединены между собой, соединены со второй группой информационных D-входов регистра номера первого бита группы RGB 3 и подключены к группе выходов второго счетчика единиц CTU 8,

причем выход блока равенства нижней границы 9 соединен с входом S синхронной установки в единичное состояние третьего триггера нижней границы TRL 11 и со вторым прямым входом третьего 13 элемента И с двумя инверсными входами, выход которого соединен с первым входом второго элемента ИЛИ 15,

выход блока равенства верхней границы 10 соединен с входом S синхронной установки в единичное состояние четвертого триггера верхней границы TRM 12, выход которого соединен с третьими инверсными входами третьего 13 и четвертого 14 элементов И с двумя инверсными входами,

кроме того, выход третьего триггера нижней границы TRL 11 соединен со вторым прямым входом четвертого 14 элемента И с двумя инверсными входами, выход которого соединен со вторым входом второго элемента ИЛИ 15, выход которого соединен с входом СЕ разрешения работы выходного буфера ОВ 11 и третьего счетчика количества групп CTG 17, группа выходов которого является группой внешних выходов количества групп QG.

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680759C1 |

| US 7584233 B2, 01.09.2009 | |||

| US 6938061 B1, 30.08.2005 | |||

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2022-01-11—Публикация

2021-04-29—Подача