Предлагаемое изобретение относится к области вычислительной техники, в частности к способам парирования ошибок при передаче, хранении, чтении и восстановлении цифровых данных.

Известен способ кодирования видео [RU 2551207, С2, H04N 19/105, 20.05.2015], который содержит этапы, на которых кодируют блок В пикселей с использованием опорного режима и одного или более опорных изображений и тем самым предоставляют закодированный блок Ве, получают одиночный синтаксический элемент, идентифицирующий опорный режим и одно или более опорных изображений, причем одиночный синтаксический элемент представляет запись в первом предопределенном опорном списке, и причем первый список содержит одну или более записей, идентифицирующих, по меньшей мере, одно из множества опорных изображений и одиночного опорного изображения, предоставляют одиночный синтаксический элемент декодеру блока Ве, а особенностью способа является то, что синтаксический элемент получается посредством того, что используемый опорный режим и одно или более опорных изображений отображают на синтаксический элемент в соответствии с предопределенной схемой отображения, каждая запись в первом списке дополнительно идентифицирует опорный режим, одиночный синтаксический элемент дополнительно представляет опорный режим и запись во втором предопределенном опорном списке.

Недостатком этого технического решения является относительно узкая область применения, поскольку способ предназначен преимущественно для кодирования изображений.

Способ кодирования и декодирования блокового кода с использованием алгоритма Витерби [RU 2608872, C1, Н03М 13/41, 24.09.2015], являющийся способом-прототипом, содержит алгоритм, в соответствии с которым кодируемые информационные последовательности разбивают на блоки, и помещают в регистры кодера, причем все регистры свертывают циклически соединением выходов последних ячеек каждого их этих регистров с их входами, после чего выполняют синхронные сдвиги всех получившихся циклических регистров, во время которых формируют кодовые подблоки и затем подают их на вход декодера Витерби, причем после приема декодером всех кодовых подблоков в декодер подают вновь эти же кодовые подблоки в том же порядке еще несколько раз, после чего процесс декодирования прерывается и на выжившем пути минимального веса выбираются решения декодера Витерби.

Недостатком этого технического решения является невозможность применения при условии высокой вероятности возникновения ошибок в кодере. При использовании кодера на основе данного способа в космических бортовых системах, в нем возможно появление ошибок из-за радиационных эффектов, что не позволит достоверно восстановить исходную информацию.

Технический результат - повышение устойчивости цифровых данных к ошибкам, возникающим на этапе информационного обмена и на этапе кодирования.

Технический результат достигается тем, что в способе кодирования и декодирования блокового кода, включающем запись каждого символа исходного сообщения в одну из k0 переменных длиной K разрядов каждая, формирование k0 кодовых слов по n0 символов с помощью линейной комбинации значений разрядов переменной, декодирование по средствам анализа не менее d0 наборов кодовых слов, сформированных из новых исходных сообщений, причем d0 >= 2, формирование всех возможных состояний переменной для каждого кодового слова и соответствующего ей кодового слова, которые можно получить из переменной, сохраненной на предыдущем такте путем ее модификации, и вычисление для каждого варианта кодового слова расстояния, равного числу позиций, в которых соответствующие символы варианта кодового слова и кодового слова, сформированного из символа исходного сообщения, различны, расчет аналогичных расстояний для всех вариантов d0 наборов кодовых слов, объединение взаимозависимых друг от друга вариантов в пути, формирование  вероятных путей, из которых путь, имеющий минимальное суммарное расстояние за d0 кодовых слов признается достоверным, а значения, записываемые в разряд переменной при модификации на каждом такте, соответствуют исходному сообщению, в отличие от известного способа, к исходному сообщению длинной k0 разрядов добавляют избыточный символ, значение которого инвертируют после каждого обнуления адреса, несущего номер модифицируемого разряда переменной, имеющего длину T=log2K разрядов, округленную до целого значения в большую сторону, каждый такт адрес изменяют на единицу, циклически перебирая К<2Т возможных комбинаций, далее переменную длинной К разрядов потактово модифицируют путем записи избыточного символа в разряд соответствующего адреса, а выходное кодовое выражение длинной

вероятных путей, из которых путь, имеющий минимальное суммарное расстояние за d0 кодовых слов признается достоверным, а значения, записываемые в разряд переменной при модификации на каждом такте, соответствуют исходному сообщению, в отличие от известного способа, к исходному сообщению длинной k0 разрядов добавляют избыточный символ, значение которого инвертируют после каждого обнуления адреса, несущего номер модифицируемого разряда переменной, имеющего длину T=log2K разрядов, округленную до целого значения в большую сторону, каждый такт адрес изменяют на единицу, циклически перебирая К<2Т возможных комбинаций, далее переменную длинной К разрядов потактово модифицируют путем записи избыточного символа в разряд соответствующего адреса, а выходное кодовое выражение длинной  символов, формируют из

символов, формируют из  линейных комбинаций разрядов переменной длинной К разрядов, запись символов исходного сообщения в соответствующие им переменные производят по тому же адресу что и избыточный символ, при декодировании на основе сохраненных на предыдущем такте значений адреса и значений переменной перебирают все возможные модификации переменной при условии достоверного адреса и формируют кодовые слова длинной

линейных комбинаций разрядов переменной длинной К разрядов, запись символов исходного сообщения в соответствующие им переменные производят по тому же адресу что и избыточный символ, при декодировании на основе сохраненных на предыдущем такте значений адреса и значений переменной перебирают все возможные модификации переменной при условии достоверного адреса и формируют кодовые слова длинной  символов для каждой возможной модификации, путем

символов для каждой возможной модификации, путем  линейных комбинаций разрядов модифицированной переменной, и далее проверяют неравенство кодового слова сформированного на данном такте из избыточного символа и сформированного на предыдущем такте, а также равенство одного из кодовых слов, сформированных из модифицированной переменной, и кодового слова, сформированного на данном такте из избыточного символа, при выполнении обоих условий, значение адреса принимается как достоверное, в ином случае, в зависимости от того, какое из условий выполняется, производят модификацию сохраняемых значений адреса и переменной, а следующие d0 тактов анализируют новые кодовые выражения, сформированные из новых значений избыточных символов, при этом на каждом такте перебирая все возможные модификации переменной при соответствующем адресе, формируют все варианты кодовых слов и вычисляют расстояния между кодовыми словами из каждого модифицированного значения и кодовым словом из избыточного символа, формируя пути, по линейной комбинации расстояний каждого пути определяют достоверные адреса разрядов переменной, в которые записывались символы исходного сообщения.

линейных комбинаций разрядов модифицированной переменной, и далее проверяют неравенство кодового слова сформированного на данном такте из избыточного символа и сформированного на предыдущем такте, а также равенство одного из кодовых слов, сформированных из модифицированной переменной, и кодового слова, сформированного на данном такте из избыточного символа, при выполнении обоих условий, значение адреса принимается как достоверное, в ином случае, в зависимости от того, какое из условий выполняется, производят модификацию сохраняемых значений адреса и переменной, а следующие d0 тактов анализируют новые кодовые выражения, сформированные из новых значений избыточных символов, при этом на каждом такте перебирая все возможные модификации переменной при соответствующем адресе, формируют все варианты кодовых слов и вычисляют расстояния между кодовыми словами из каждого модифицированного значения и кодовым словом из избыточного символа, формируя пути, по линейной комбинации расстояний каждого пути определяют достоверные адреса разрядов переменной, в которые записывались символы исходного сообщения.

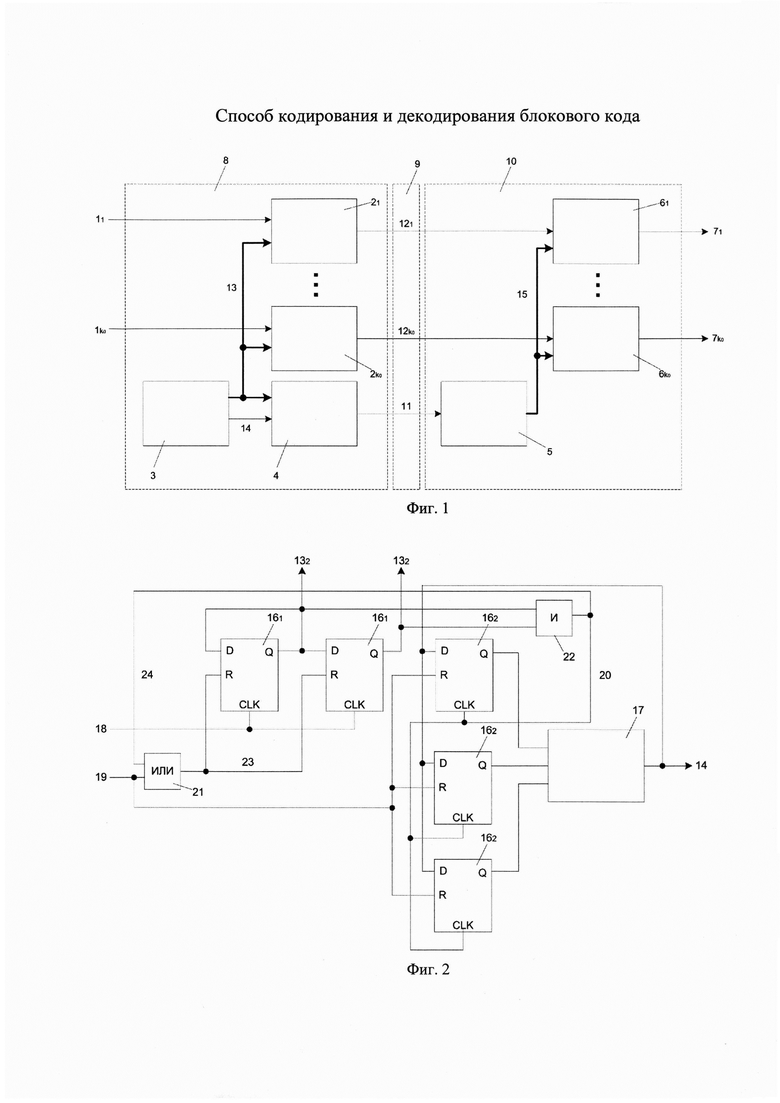

На фиг. 1 представлена функциональная схема реализации способа кодирования и декодирования блокового кода.

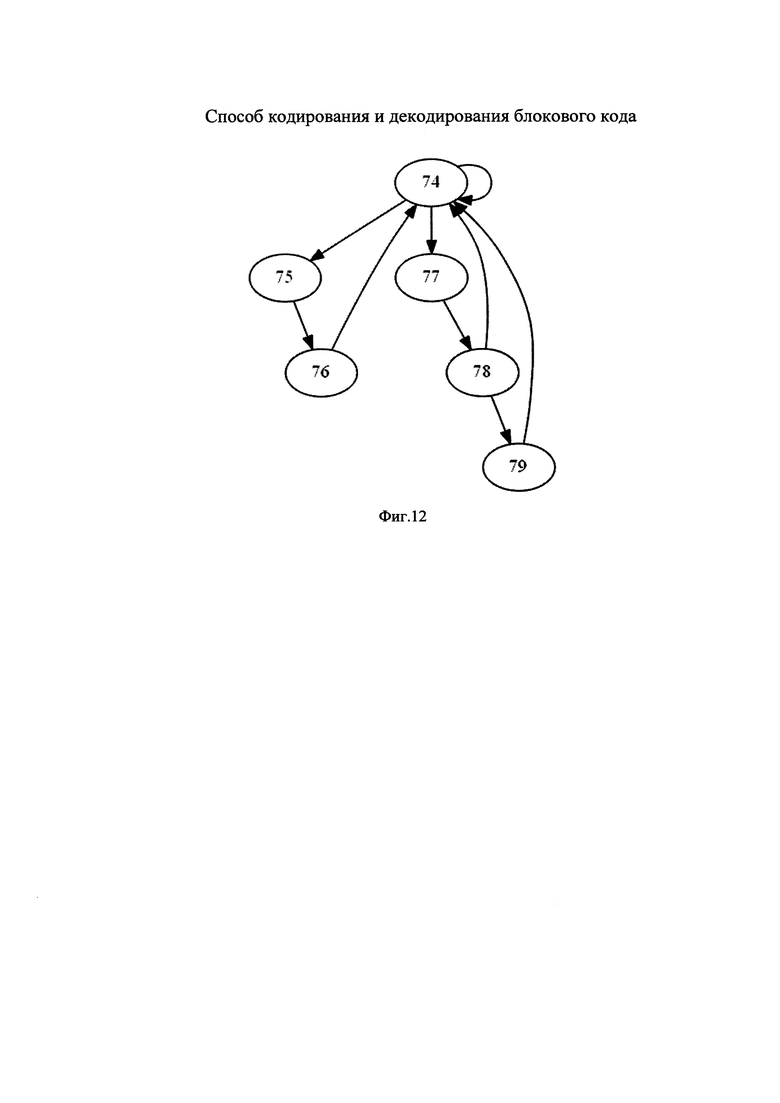

На фиг. 2 представлен счетчик для формирования символа избыточности.

На фиг. 3 представлены временные диаграммы сигналов счетчика.

На фиг. 4 представлена функциональная схема формирования выходного кодового слова.

На фиг. 5 представлена схема комбинаторной логики, формирующей выходное кодовое слово.

На фиг. 6 показан переход из состояния «0»;

На фиг. 7 показан переход из состояния «1»;

На фиг. 8 показан переход из состояния «2»;

На фиг. 9 показан переход из состояния «3»;

На фиг. 10 показан переход из состояния «4»;

На фиг. 11 показан переход из состояния «5».

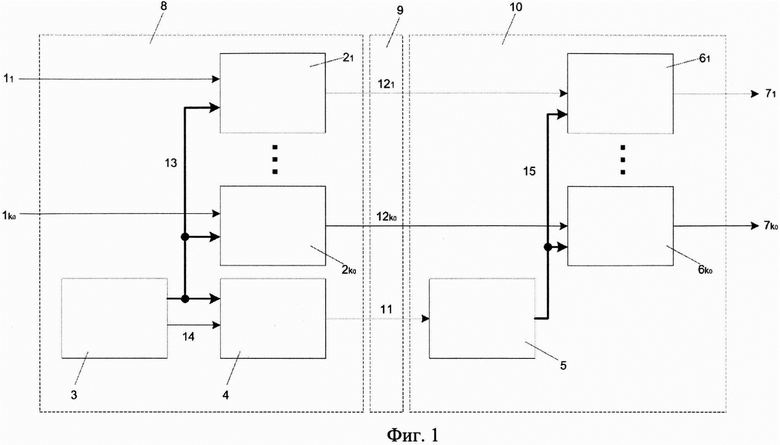

На фиг. 12 представлен граф переходов конечного автомата, на основе которого строится декодер.

1 - исходное сообщение,

2 - блоки формирования выходных кодовых слов исходного сообщения, далее, по тексту - блок 2,

3 - счетчик,

4 - блок формирования выходного кодового слова избыточности, далее, по тексту - блок 4,

5 - блок исправления ошибок избыточности, далее, по тексту - блок 5,

6 - блоки исправления ошибок исходного сообщения, далее, по тексту - блок 6,

7 - символы выходного сообщения,

8 - кодер,

9 - канал передачи кодовых сообщений,

10 - декодер,

11 - кодовое слово, сформированное из избыточности, далее, по тексту - кодовое слово 11,

12 - кодовые слова, сформированные из исходного сообщения, далее, по тексту - кодовое слово 12,

13 - адресная шина кодера,

14 - избыточный символ,

15 - адресная шина декодера,

16 - триггеры,

17 - схема мажорирования,

18 - входной тактовый сигнал,

19 - входной сигнал сброса,

20 - тактовый сигнал,

21 - элемент ИЛИ,

22 - элемент И,

23 - внутренний сигнал сброса,

24 - дополнительный сигнал сброса,

25 - дешифратор,

26 - буферы,

27 - шифратор,

28 - комбинаторная логика,

29 - разряд циклически перезаписываемого регистра,

30 - сумматор по mod2,

31 - схема сравнения,

32 - схема формирования сходных воздействий,

33 - сигнал выбора буфера,

34 - блок записи исходных значений дополнения №3 при состоянии 3, далее, по тексту - блок 34,

35 - блок записи исходных значений без дополнений при состоянии 5, далее, по тексту - блок 35,

36 - вывод достоверных значений в A2, A3, далее, по тексту - блок 36,

37 - блок сравнения кодовых слов 12, далее, по тексту - блок 37,

38 - блок вычисления расстояний Хемминга для одинаковых кодовых слов 12, далее, по тексту - блок 38,

39 - блок сравнения расстояний Хемминга для одинаковых кодовых слов 12, далее, по тексту - блок 39,

40 - блок перехода к состоянию 1, далее, по тексту - блок 40,

41 - блок записи исходных значений без дополнений при состоянии 0, далее, по тексту - блок 41,

42 - блок расчета исходных значений по дополнению №1 при состоянии 0, далее, по тексту - блок 42,

43 - блок записи исходных значений дополнения №1 при состоянии 0, далее, по тексту - блок 43,

44 - блок перехода к состоянию 0, далее, по тексту - блок 44,

45 - блок записи исходных значений без ошибок, далее, по тексту - блок 45,

46 - вывод достоверного значения в А3, далее, по тексту - блок 46,

47 - блок перехода к состоянию 3, далее, по тексту - блок 47,

48 - блок расчета исходных значений по дополнению №2 при состоянии 0, далее, по тексту - блок 48,

49 - блок расчета исходных значений по дополнению №3 при состоянии 0, далее, по тексту - блок 49,

50 - блок записи исходных значений дополнения №2 и дополнения №3 при состоянии 0, далее, по тексту - блок 50,

51 - блок расчета исходных значений без дополнений при состоянии 1, далее, по тексту - блок 51,

52 - блок записи исходных значений без дополнений при состоянии 1, далее, по тексту - блок 52,

53 - блок перехода к состоянию 2, далее, по тексту - блок 53,

54 - блок расчета исходных значений по дополнению №1 при состоянии 1, далее, по тексту - блок 54,

55 - блок записи исходных значений дополнения №1 при состоянии 1, далее, по тексту - блок 55,

56 - блок расчета исходных значений по дополнению №2 при состоянии 3, далее, по тексту - блок 56,

57 - блок расчета исходных значений без дополнений при состоянии 2, далее, по тексту - блок 57,

58 - блок записи исходных значений без дополнений при состоянии 2, далее, по тексту - блок 58,

59 - вывод достоверных значений в A1, A2, A3, далее, по тексту - блок 59,

60 - блок записи исходных значений дополнения №2 при состоянии 3, далее, по тексту - блок 60,

61 - блок расчета исходных значений по дополнению №1 при состоянии 2, далее, по тексту - блок 61,

62 - блок записи исходных значений дополнения №1 при состоянии 2, далее, по тексту - блок 62,

63 - вывод достоверных значений в A1, A2, далее, по тексту - блок 63,

64 - блок расчета исходных значений по дополнению №2 при состоянии 2, далее, по тексту - блок 64,

65 - блок записи исходных значений дополнения №2 при состоянии 2, далее, по тексту - блок 65,

66 - блок перехода к состоянию 4, далее, по тексту - блок 66,

67 - блок расчета исходных значений по дополнению №3 при состоянии 2, далее, по тексту - блок 67,

68 - блок записи исходных значений дополнения №3 при состоянии 2, далее, по тексту - блок 68,

69 - блок перехода к состоянию 5, далее, по тексту - блок 69,

70 - блок формирования сигнала ошибки в решении дополнения №3, далее, по тексту - блок 70,

71 - блок проверки ошибки в решении дополнения №3, далее, по тексту - блок 71,

72 - блок расчета исходных значений по дополнению №3 при состоянии 3, далее, по тексту - блок 72,

73 - блок расчета исходных значений по без дополнений при состоянии 5, далее, по тексту - блок 73,

74 - вершина состояния «0» графа переходов,

75 - вершина состояния «1» графа переходов,

76 - вершина состояния «2» графа переходов,

77 - вершина состояния «3» графа переходов,

78 - вершина состояния «4» графа переходов,

79 - вершина состояния «5» графа переходов,

Функциональная схема реализации способа кодирования и декодирования блокового кода, представленная на фиг. 1 может быть построена следующим образом. Блок 4 соединен со счетчиком 3 с помощью адресной шины 13 кодера, и с помощью линии избыточного символа 14. Блок 4 соединен с линией кодового слова 11 которая в свою очередь подключена к блоку 5. Счетчик 3 также соединен с блоком 2, к которым подключены линии символов исходного сообщения 1. Блоки 2 соединены соответствующими линиями кодовых слов 12 к соответствующим блокам 6, которые подключены к линиям символов исходного сообщения 7 и адресной шине 15 декодера 10.

Счетчик 3 представленный на фиг. 2 может быть выполнен следующим образом. Входной тактовый сигнал 18 и внутренний сигнал сброса 23 подключенный к элементу ИЛИ 21 соединен с триггерами 161, которые соединены последовательно между собой, а к их входу подключен первый разряд 131 адресной шины 13, выходы этих триггеров соединены с разрядами адресной шины 13 кодера (131 - первый разряд и 132 - второй разряд) и соединены с элементом И 22 выход которого соединен с элементом ИЛИ 21, а на его второй вход подключена линия сигнала внешнего сброса 19, но выход элемента И 22 так же подключен к триггеру 162, к которому так же подключен внешний сигнал сброса 19 и линия выходного избыточного символа 14, которая соединена со схемой мажорирования 17.

Блок формирования выходного кодового слова избыточности 4 представленный на фиг. 4 может быть построен по следующей схеме. Дешифратор 25 подключен к адресной шине кодера 13, к линии избыточного символа 14 и к обоим буферам 26. Шифратор 27 соединен с обоими буферами 26, а также с линией сигнала выбора буфера 33 и комбинаторной логикой 28, которая подключена к линии кодового слова 11.

Вариант логики функционирования блока формирования выходного кодового слова исходного сообщения представленный на фиг. 5 может быть построен по следующей схеме. Ко всем разрядам циклически перезаписываемого регистра 26 подключена линия избыточного символа и определенный для каждого разряда набор сумматоров по mod2, которые в свою очередь соединены с линиями кодовых слов 11.

Показанный на фиг. 6 переход из состояния «0» построен следующим образом. Блок 37 соединен с блоками 47 и 38. Блок 38 соединен с блоком 39. Блок 39 соединен с блоками 40 и 44. Блок 40 соединен с блоком 41, который подключен к блоку 42. Блок 42 соединен с блоком 43, который подключен к блокам 46 и 50. Блок 44 соединен с блоком 45, который подключен к блоку 46. Блок 47 соединен с блоком 48, который подключен к блоку 49. А блок 49 соединен с блоком 50.

Показанный на фиг. 7 переход из состояния «1» построен следующим образом. Блок 51 соединен с блоками 54 и 52. Блок 52 соединен с блоками 53 и 54. А блоки 54 и 55 соединены между собой.

Показанный на фиг. 8 переход из состояния «2» построен следующим образом. Блок 37 соединен с блоками 57 и 61. Блоки 57, 58 и 59 соединены последовательно, аналогично блокам 61, 62 и 59. А блоки 59 и 44 соединены между собой.

Показанный на фиг. 9 переход из состояния «3» построен следующим образом. Блоки 64 и 67 соединены между собой. Блок 64 подключен к блоку 65, который в свою очередь соединен с блоками 66, 70 и 39. Блоки 67, 68, 39 и 70 соединены последовательно.

Показанный на фиг. 10 переход из состояния «4» построен следующим образом. Блоки 71, 72, 39, 74, 59 и 44 соединены последовательно. Блок 71 дополнительно соединен с блоками 56 и 39. Блоки 56, 39, 60, 63, 69 соединены последовательно, аналогично блокам 39, 60, 59, 44. Блоки 44 и 69 соединены между собой.

Показанный на фиг. 11 переход из состояния «5» построен следующим образом, блоки 73, 75, 76 и 44 соединены последовательно.

Представленный на фиг. 12 граф переходов конечного автомата строится следующим образом. Вершина состояния «0» 74 соединена сама с собой, с вершиной состояния «1» 75 и вершиной состояния «3» 77. Вершина состояния «1» 75 соединена с вершиной состояния «2» 76, которая соединена с вершиной состояния «0» 74. Вершина состояния «3» 77 соединена с вершиной состояния «4» 78, которая соединена с вершиной состояния «0» 74 и вершиной состояния «5» 79 подключенной к вершине состояния «0» 74.

Пример реализации кодера для заявляемого способа кодирования и декодирования блокового кода представляется на фиг. 1, 2, 4, 5 и работает следующим образом. Собранный на базе триггеров 161 двоичный синхронный счетчик за счет обратной связи, реализованной с помощью логического умножения выходных сигналов этих триггеров, с помощью элемента И 22, и последующей выдачей в качестве одного из вариантов сигнала сброса, формируемого элементом ИЛИ 21, подключенной на вход сброса, как видно из временных диаграмм представленных на фиг. 3, формирует в разрядах 131 и 132 адресной шины кодера значения от 0 до 2. Сигнал, являющийся логическим произведением 131 и 132, так же является тактовым сигналом, одноразрядного троированного двоичного счетчика, построенного на триггерах 162, входным сигналом для которых является выход схемы мажорирования 17 реализуемой по схеме «два из трех», сделано это для того, чтобы символ избыточности 14 был защищен от единичных сбоев и таким образом был достоверным в любой момент времени. Как видно из временной диаграммы сигнала U14 на фиг. 3, детерминированным алгоритмом вычисления символа избыточности 14 является инвертирование его значения каждый полный такт работы счетчика на триггерах 161. Далее дешифратор 25 каждый такт записывает значение избыточного символа 14 параллельно только в один разряда (291, 292, 293) обоих буферов 26, выполненных на основе циклически перезаписываемых регистров 29, адрес определяется значением, установленным на адресной шине 13 кодера. Шифратор 27 по сигналу выбора буфера 33 выдает в блок комбинаторной логики 28 значения только одного, активного в данном такте, буфера. В блоке комбинаторной логики каждый из трех сумматоров по mod2 30, как показано на фиг. 5, производит суммирование двух определенных разрядов циклически перезаписываемого регистра 29, выбранного шифратором 27, и результат логической операции выводится в виде кодового слова 11 сформированного из избыточности. Блок формирования выходного кодового слов исходного сообщения 2 строится по схеме, идентичной блоку формирования выходного кодового слова избыточности 4, но вместо сигнала избыточности 14 на вход подается один из k0 символов исходного сообщения 1, а первые три разряда выходных кодовых слов 12 сформированных из исходного сообщения формируются полностью идентично кодовому слову 11 сформированному из избыточности, но с добавлением четвертого разряда хранящего в себе значение одного из k0 символов исходного сообщения 1.

В качестве метода реализации блока исправления ошибок избыточности 5 лучше всего подходит конечный автомат, представленный на фиг. 12, а на фиг. 6…11 представлены блок-схемы выбора следующего состояния.

Суть реализации конечного автомата блока 5 заключается в следующем. Состояние «0» означает, что на предыдущем такте было определено достоверное значение адреса, а переход к состояниям «1» и «3» возможен только в случае обнаружения ошибок в кодовом слове 11, при этом для определения достоверного значения на такте состояния «0» необходимо пройти одну из двух ветвей:

- Состояние «0» - состояние «1» - состояние «2»;

- Состояние «0» - состояние «3» - состояние «4»;

Состояние 5 является дополнительным для второй ветви и помогает определять достоверное значение в кодовых словах 11 для состояния 4.

Из этого можно сделать вывод, что восстановление достоверного значения адреса блоком исправления ошибок избыточности 5, происходит с максимальной задержкой в 2 такта. Поэтому в нем реализуется сдвиговый регистр из трех переменных A1, A2 и A3 хранящих состояния адреса во время тактов t0, t0+1 и t0+2 и независимо от состояния конечного автомата в данном такте происходит запись A1 в A2 и A2 в A3, параллельно с выводом нового значения A1 в адресную шину 15 декодера. Количество записанных новых значений в переменные A1, A2 и A3 может варьироваться в зависимости от состояния конечного автомата в настоящем такте.

Алгоритмы декодирования строятся на основе алгоритма Витерби, однако для поиска ошибок в него вводятся три дополнения:

- Первое дополнение - ошибка, приводящая к компрометации адреса в адресной шине кодера 13;

- Второе дополнение - ошибка, приводящая к «залипанию» адреса в адресной шине кодера 13;

- Третье дополнение - ошибка в буфере 26.

Принципа работы блока 5 описывается блок-схемами перехода конечного автомата между всеми состояниями и работает следующим образом. При состоянии «0» блок 37 сравнивает кодовое слово 11 полученное в данном такте и сохраненное на прошлом такте, их равенство свидетельствует о наличии ошибки кодера или в адресной шине кодера 13, или при записи нового значения в буфер 26. При обнаружении ошибки данного типа блок 47 формирует вектор на переход к новому состоянию «3» при следующем такте, однако перед переходом к новому состоянию блок 48 в соответствии со вторым дополнением производит инверсию бита буфера, значение которого было сохранено на прошлом такте, по адресу, следующему за определенным на прошлом такте, и на его основе формирует комбинаторной логикой, идентичной комбинаторной логике 28, предполагаемое слово, сохраняя его, новый адрес и сформированный буфер с помощью блок 50 в память. Блок 49 действует аналогично блоку 48, с той разницей, что значения адреса, состояние буфера и новое значение будут идентичны значениям предыдущего такта, но запись производится аналогично блоком 50. Если блок 37 выдал отрицательный результат, то производится расчет расстояний Хемминга по классической схеме алгоритма Витерби блоком 38, а именно в два идентичных буфера по одному адресу записываются два разных значения, на их основе комбинаторной логикой формируются кодовые слова, для которых считается расстояние Хемминга от входного кодового слова 11. Рассчитанные расстояния проверяются блоком 39 и нулевое значение принимается достоверным, новые значения адреса, записываемое значение, буфер и выходное слово блоком 45 записываются в память, при этом блок 44 определяет вектор перехода в состояние «0», а блок 46 выводит достоверное значение адреса в адресную шину декодера 15. В случае если блок 39 выдал отрицательный результат, то значит была ошибка или в адресной шине кодера 13, или в кодовом слове 11. Для данного случая вектор перехода устанавливается блоком 40 в состояние «1». Блок 41 сохраняет два набора данных полученных от блока 38. Блок 42 перебирает все возможные сочетания адресов и значений записываемых бит для определения расстояния Хемминга равного нулю и это значение, а именно адрес, буфер и записанное значение бита, сохраняются блоком 43.

Если вектор переходы был задан равным состоянию «1», то производится расчет двух параллельных ветвей без дополнений и по первому дополнению. Блок 51 производит расчет четырех значений, по два для каждого из сохраненных блоком 41 значений и определяет значение для которого расстояние Хемминга будет нулевым, это значение и записывается блоком 52. Параллельно этому производится расчет блоком 54 идентичный логике блока 38, но из исходных данных сохраненных блоком 43 и так же как и в ветви без дополнений, путь с расстоянием Хемминга равным нулю сохраняется блоком 55. А в дальнейшем осуществляется формирование вектора перехода к состоянию «2», блоком 53.

Если вектор перехода был установлен в состояние «2», то как и для состояния «0» производится сравнение блоком 37 кодового слова 11 полученного в данном такте и сохраненного на прошлом такте, если условие выполняется, то верным было решение по первому дополнению, для которого аналогично состоянию «1», блоком 61 рассчитываются значения аналогично блоку 54, но из данных, сохраненных блоком 43, а блоком 62 сохраняются достоверные значения для следующего состояния. В дальнейшем блок 59 производит вывод достоверных значений (A1, А2 и А3) для всех предыдущих состояний, начиная с нулевого. Если блок 37 выдал отрицательный результат, то верным было решение по алгоритму без дополнений, для которого аналогично состоянию «0», блоком 57 рассчитываются значения, аналогично блоку 38, но на основе данных сохраненных блоком 52, а блоком 58 сохраняются достоверные значения для следующего состояния, после чего аналогично первому дополнению блоком 59 производится вывод достоверных значений А1, А2 и A3. Не зависимо от выбранной ветви блок 44 выставляет вектор перехода к состоянию 0.

Если вектор перехода был установлен в состояние «3», то производится расчет двух параллельных ветвей по второму дополнения и по третьему дополнению. Для второго дополнения выполняется расчет новых значений блоком 64, аналогично блоку 38, но из данных сохраненных блоком 50 для второго дополнения и их сохранение блоком 65. Параллельно этому для третьего дополнения выполняется расчет новых значений блоком 67, аналогично блоку 38, но из данных сохраненных блоком 50 для третьего дополнения и их сохранение блоком 68, но с дополнительной проверкой блоком 39 наличия решения блока 38 и в случае отсутствия выставление флага ошибки для третьего дополнения блоком 70. Обе ветви данного состояния приводят к установке вектора перехода блоком 66 в состояние «4».

Если вектор перехода был установлен в состояние «4», то блоком 71 анализируется наличие флага ошибки третьего дополнения и в случае наличия переходят к ветви решения по второму дополнению, в которой блоком 56, аналогично блоку 38, рассчитывают новые значения, но на основе решений блока 65, а далее блоком 39 определяется ветвь выбора вектора перехода или к состоянию «0» блоком 44, с выводом блоком 59 достоверных значений A1, А2 и А3, и сохранение новых значений блоком 60, или переход к состоянию «5» блоком 69 с выводом блоком 63 достоверных значений A1, и А2, и сохранение новых значений блоком 60. Если блок 71 установил что ошибки нет, то производится расчет новых значений по ветви третьего дополнения блоком 72 аналогично блоку 38, но для исходных данных блока 68 и в случае отсутствия решений блоком 39 переходит к уже описанной ранее ветви второго дополнения, в случае же наличия решения, сохраняются новые значения блоком 74, а блоком 59 выводятся достоверные значения А1, А2 и А3 с переходом вектором к состоянию «0» блоком 44.

Если вектор был установлен в состояние «5», то значит на прошлом такте уже были установлены значения A1, и A2 и данное решение должно определить последнее значение, осуществляется это за счет расчета блоком 73 аналогично 38 но из значений блока 60 расстояний Хемминга и сохранения новых значений адреса, записываемого значения, буфера и выходного слова блоком 35, с последующей выдачей значений А2 и А3 блоком 36, так как сохраненные значения блоком 63 были сдвинуты сдвиговым регистром на единицу. По окончании вывода осуществляется установка вектора перехода к состоянию 0 и все расчеты начинаются с начала.

Блоки с 61 по  реализуются аналогично блоку 5, но без дополнений и строго в соответствии с адресом A1 рассчитанным в данном такте блоком 5.

реализуются аналогично блоку 5, но без дополнений и строго в соответствии с адресом A1 рассчитанным в данном такте блоком 5.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| СПОСОБ ПЕРЕДАЧИ СООБЩЕНИЙ В СИСТЕМАХ С ОБРАТНОЙ СВЯЗЬЮ И ГИБРИДНЫМ АВТОМАТИЧЕСКИМ ЗАПРОСОМ НА ПОВТОРЕНИЕ | 2022 |

|

RU2786023C1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ | 1995 |

|

RU2117388C1 |

| АДАПТИВНЫЙ КОДЕР ГИПЕРКОДА РАЗМЕРНОСТИ 3D | 2011 |

|

RU2480918C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| СПОСОБ РАСПРОСТРАНЕНИЯ ИНФОРМАЦИИ В МНОГОАБОНЕНТНОЙ СИСТЕМЕ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2155451C2 |

| Способ кодирования и декодирования блокового кода с использованием алгоритма Витерби | 2015 |

|

RU2608872C1 |

| СПОСОБ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ В СИСТЕМАХ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2310273C2 |

| СПОСОБ ПЕРЕДАЧИ СООБЩЕНИЙ В ПОЛУДУПЛЕКСНОМ КАНАЛЕ СВЯЗИ | 1996 |

|

RU2127953C1 |

Изобретение относится к способам парирования ошибок при передаче, хранении, чтении и восстановлении цифровых данных. Технический результат заключается в повышении устойчивости цифровых данных к ошибкам, возникающим на этапе информационного обмена и на этапе кодирования. В способе кодирования и декодирования блокового кода записывают каждый символ исходного сообщения в одну из k0 переменных длиной K разрядов каждая, формируют k0 кодовых слов по n0 символов с помощью линейной комбинации значений разрядов переменной. Декодируют по средствам анализа не менее d0 наборов кодовых слов, сформированных из новых исходных сообщений, записывают значения в разряд переменной при модификации на каждом такте, соответствующие исходному сообщению. К исходному сообщению длиной k0 разрядов добавляют избыточный символ. Формируют все варианты кодовых слов и вычисляют расстояния между кодовыми словами из каждого модифицированного значения и кодовым словом из избыточного символа, формируя пути. Определяют достоверные адреса разрядов переменной, в которые записывались символы исходного сообщения, по линейной комбинации расстояний каждого пути. 12 ил.

Способ кодирования и декодирования блокового кода, включающий запись каждого символа исходного сообщения в одну из k0 переменных длиной K разрядов каждая, формирование k0 кодовых слов по n0 символов с помощью линейной комбинации значений разрядов переменной, декодирование по средствам анализа не менее d0 наборов кодовых слов, сформированных из новых исходных сообщений, причем d0>=2, формирование всех возможных состояний переменной для каждого кодового слова и соответствующего ей кодового слова, которые можно получить из переменной, сохраненной на предыдущем такте путем ее модификации, и вычисление для каждого варианта кодового слова расстояния, равного числу позиций, в которых соответствующие символы варианта кодового слова и кодового слова, сформированного из символа исходного сообщения, различны, расчет аналогичных расстояний для всех вариантов d0 наборов кодовых слов, объединение взаимозависимых друг от друга вариантов в пути, формирование 2d0 вероятных путей, из которых путь, имеющий минимальное суммарное расстояние за d0 кодовых слов, признается достоверным, а значения, записываемые в разряд переменной при модификации на каждом такте, соответствуют исходному сообщению, отличающийся тем, что к исходному сообщению длиной k0 разрядов добавляют избыточный символ, значение которого инвертируют после каждого обнуления адреса, несущего номер модифицируемого разряда переменной, имеющего длину T=log2K разрядов, округленную до целого значения в большую сторону, каждый такт адрес изменяют на единицу, циклически перебирая К<2Т возможных комбинаций, далее переменную длиной К разрядов потактово модифицируют путем записи избыточного символа в разряд соответствующего адреса, а выходное кодовое выражение длиной n0 символов формируют из n0 линейных комбинаций разрядов переменной длиной К разрядов, запись символов исходного сообщения в соответствующие им переменные производят по тому же адресу, что и избыточный символ, при декодировании на основе сохраненных на предыдущем такте значений адреса и значений переменной перебирают все возможные модификации переменной при условии достоверного адреса и формируют кодовые слова длиной n0 символов для каждой возможной модификации путем n0 линейных комбинаций разрядов модифицированной переменной и далее проверяют неравенство кодового слова, сформированного на данном такте из избыточного символа и сформированного на предыдущем такте, а также равенство одного из кодовых слов, сформированных из модифицированной переменной, и кодового слова, сформированного на данном такте из избыточного символа, при выполнении обоих условий значение адреса принимается как достоверное, в ином случае в зависимости от того, какое из условий выполняется, производят модификацию сохраняемых значений адреса и переменной, а следующие d0 тактов анализируют новые кодовые выражения, сформированные из новых значений избыточных символов, при этом на каждом такте, перебирая все возможные модификации переменной при соответствующем адресе, формируют все варианты кодовых слов и вычисляют расстояния между кодовыми словами из каждого модифицированного значения и кодовым словом из избыточного символа, формируя пути, по линейной комбинации расстояний каждого пути определяют достоверные адреса разрядов переменной, в которые записывались символы исходного сообщения.

| Токарный резец | 1924 |

|

SU2016A1 |

| Способ кодирования и декодирования блокового кода с использованием алгоритма Витерби | 2015 |

|

RU2608872C1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ СЛОВ ДАННЫХ | 2008 |

|

RU2485584C2 |

| СПОСОБ АДАПТИВНОЙ КОРРЕКЦИИ ПАРАМЕТРОВ ПЕРЕДАЧИ СООБЩЕНИЙ | 2006 |

|

RU2331987C1 |

Авторы

Даты

2019-03-12—Публикация

2018-04-09—Подача