Изобретение относится к технике связи и может быть использовано при разработке систем полудуплексной связи для передачи сообщений, закодированных каскадным кодом, с подтверждением правильного приема путем передачи квитанции.

Известен способ передачи информации кодограммами [1, стр. 136], по которому кодограмму разбивают на блоки, каждый блок кодируют корректирующим ошибки кодом, запоминают и передают в канал связи. На приеме комбинации декодируют, запоминают адреса комбинаций, принятых с ошибками, по окончании приема кодограммы корреспонденту передается либо квитанция, если все комбинации приняты без ошибок, либо адреса комбинаций, которые требуется повторить. На передающей стороне по принятым адресам осуществляется повторная передача комбинаций. При неприеме квитанции в заданное время осуществляется повторная передача кодограммы.

Недостаток известного способа заключается в низкой пропускной способности канала связи из-за отсутствия динамического согласования корректирующей способности кода с изменяющимся качеством канала связи.

Кроме того, в случае неприема квитанции из-за ошибок в канале связи кодограмма передается повторно и поэтому еще раз может быть выведена абоненту. При передаче команд управления, например, оружием, это недопустимо, так как приведет к повторному выполнению этой команды.

Известен способ передачи информации [2] по полудуплексному каналу связи, выбранный в качестве прототипа, по которому на передающей стороне формируют блоки, содержащие информационную и служебную части.

В служебной части передается номер блока и признак повторения блока. Блок кодируют корректирующим ошибки кодом, передают по каналу связи. На приемной стороне блок декодируют, при отсутствии ошибок передают в сторону передающей стороны сигнала квитанции, сравнивают номера принимаемого блока и номер последнего выданного получателю блока. При отличии этих номеров выдают принимаемый блок получателю. При неприеме передающей стороной сигнала квитанции в заданное время повторяют блок информации.

В этом способе отбраковка блоков по номерам устраняет возможность выдачи повторной команды управления получателю.

Недостаток известного способа заключается в плохом использовании пропускной способности канала связи вследствие необходимости квитирования каждого блока информации, что приводит к дополнительным затратам времени на переключение каналообразующих средств с приема на передачу и обратно. Особенно велики эти затраты при работе через радиостанции, время переключения которых зачастую соизмеримо с длительностью передаваемых сообщений.

Кроме того, хотя по известному способу один и тот же блок может повторяться несколько раз, предыдущие передачи не используются для повышения достоверности приема информации, что также приводит к плохому использованию канала связи.

В дополнение к сказанному, в известном способе не оговорена процедура определения начала сообщения. Как правило, для этой цели перед сообщением передается сигнал фазового пуска, что также снижает пропускную способность канала связи.

Задачей изобретения является повышение пропускной способности канала связи.

Технический результат, достигаемый предлагаемым способом, заключается в увеличении вероятности приема за счет быстрого наращивания мощности кода (увеличения кодового расстояния) путем организации передач дополнительных символов только к недоведенным блокам и формирования из основных и дополнительных символов умощненного блока, подлежащего последующему декодированию.

Дополнительный технический результат, достигаемый без введения дополнительной избыточности заключается в уменьшении времени передачи информации за счет исключения из состава сообщения сигнала фазового пуска и определения начала передачи информации по номерам кодовых комбинаций, что уменьшает длительность сообщения.

Признаками предлагаемого способа, общими с прототипом являются: передача информации в полудуплексных системах связи с подтверждением правильного приема квитанцией, передача информации блоками, содержащими информационную и служебную части, при этом последняя включает в себя номер блока, кодирование блоков каскадным кодом, состоящим из комбинаций внутреннего и внешнего кодов, декодирование блоков на приемной стороне, при положительном результате декодирования блока выдача его получателю, при неприеме квитанции в заданное время повторение предыдущей передачи.

Признаками предлагаемого способа отличительными от прототипа являются: передача информации циклами, содержащими произвольное число блоков, в состав служебной части которых введена информация о длине цикла; формирование дополнительных символов в процессе кодирования внешним кодом и запоминание их вместе с основными; перед передачей блоков в канал связи нумерация комбинаций внутреннего кода каждого блока одним из двух типов системы нумерации; кодирование каждого номера корректирующим ошибки кодом, формирование суммарных кодовых комбинаций путем сложения каждой комбинации внутреннего кода с комбинацией соответствующего номера; на приемной стороне, на каждом такте частоты приема, проверка принимаемой последовательности на соответствие закону построения суммарных кодовых комбинаций; при выделении соответствия-фиксация границ суммарных кодовых комбинаций; определение типа системы нумерации и номеров комбинаций внутреннего кода, по которым фиксируют границы внешнего кода; формирование комбинаций внутреннего кода путем вычитания из суммарных комбинаций комбинаций номеров; при декодировании комбинаций внутреннего кода формирование оценки их надежности и запоминание комбинаций внутреннего кода вместе с оценкой их надежности; перед декодированием внешнего кода из основных и дополнительных символов предыдущих и текущей передач формирование умощненного блока, причем в случае повторного приема какой-либо части этого блока используют метод синхронного накопления; выделение из служебной части блока информации о длине цикла при положительном результате декодирования блока; по результатам декодирования всех блоков цикла формирование квитанции с указанием номеров недекодированных блоков, запоминание ее и выдача на передающую сторону.

На передающей стороне в соответствии с принимаемой квитанцией передают дополнительные символы недекодированных блоков, при этом нумеруют комбинации внутреннего кода другим типом нумерации, а при неприеме квитанции в заданное время сохраняют то же количество блоков в цикле и тот же тип нумерации комбинаций внутреннего кода, что и в предыдущей передаче, причем при неприеме квитанции на первый цикл сеанса осуществляют повторную передачу этого цикла, а при неприеме квитанции на любой другой цикл передают очередные дополнительные символы к непринятым блокам, зафиксированным в последней принятой квитанции, при обнаружении приемной стороной другого типа нумерации фиксируют факт приема квитанции передающей стороной и осуществляют прием текущего цикла с номерами неприятных блоков, зафиксированными в этой квитанции, при этом, как при приеме, так и при неприеме квитанции символы, участвующие в образовании умощненного блока, определяются по номеру цикла, а также по номеру блока, который вычисляется до декодирования блока, причем для блока, на котором произошло фазирование - по моменту приема блока и по квитанции, а для последующих блоков в цикле - по квитанции, при невыделении приемной стороной в ожидаемое время того или другого типа нумерации отслеживаются номера блоков и длины двух циклов: цикла, на который передавалась последняя квитанция, и цикла, на который прием квитанции подтвержден.

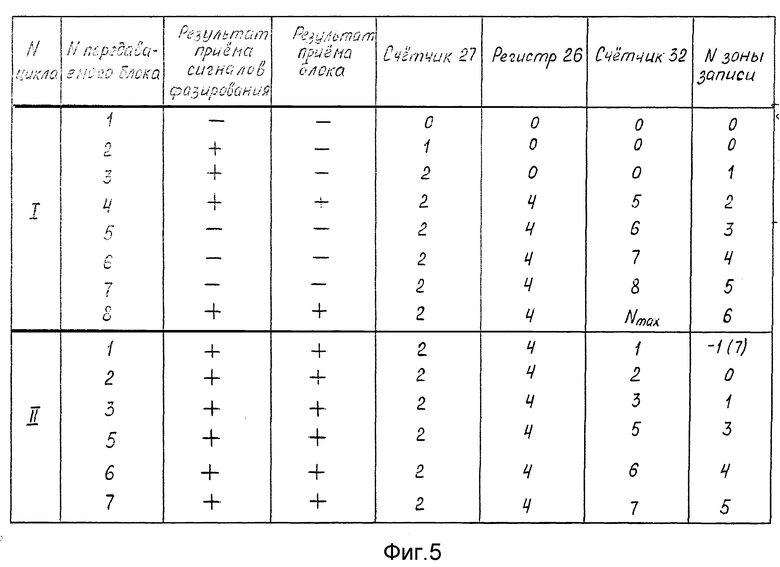

Поставленная задача решается при передаче информации каскадным кодом [3, стр. 228], состоящим из комбинаций внутреннего (n1; K1) и внешнего (n2; K2) кодов, где n1(n2) и K1(K2) общее число и число информационных символов соответственно.

В качестве внутреннего кода используют двоичные короткие коды, в качестве внешнего - недвоичные коды, например, несистематические коды Рида-Соломона (РС) над полем GF(2m), где m - расширение двоичного поля. Так например, в предлагаемом способе может быть использован в качестве внутреннего расширенный (24, 12) код Голея с образующим полиномом

g(x)=X11+X9+X7+X6+X5+X+1

и одним битом проверки на четность, используемый в режиме исправления трехкратных ошибок и обнаружения четырехкратных и части ошибок большей кратности.

В качестве внешнего кода может быть использован расширенный код РС (64, 28) над полем GF(2b) с образующим многочленом поля

F(x) = X6+X+1,

с примитивным элементом поля L = 000010.

В качестве кода нумерации может быть использован код (12, 6), проверочная часть которого является инверсией информационной части.

Передача квитанции также осуществляется корректирующим кодом, например упомянутым выше кодом Голея.

На фиг. 1 представлена структура цикла передачи информации;

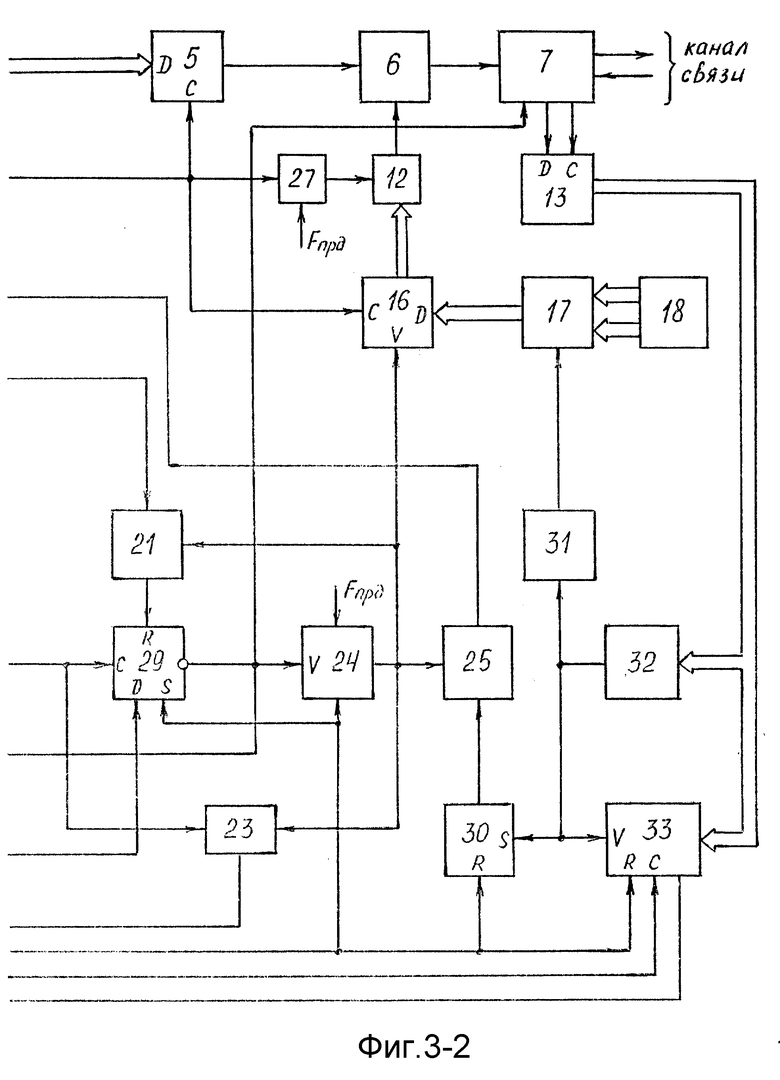

на фиг. 2 - временная диаграмма процесса формирования умощненного кода, на фиг. 3-1, 3-2 - функциональная схема примера реализации передающей части устройства;

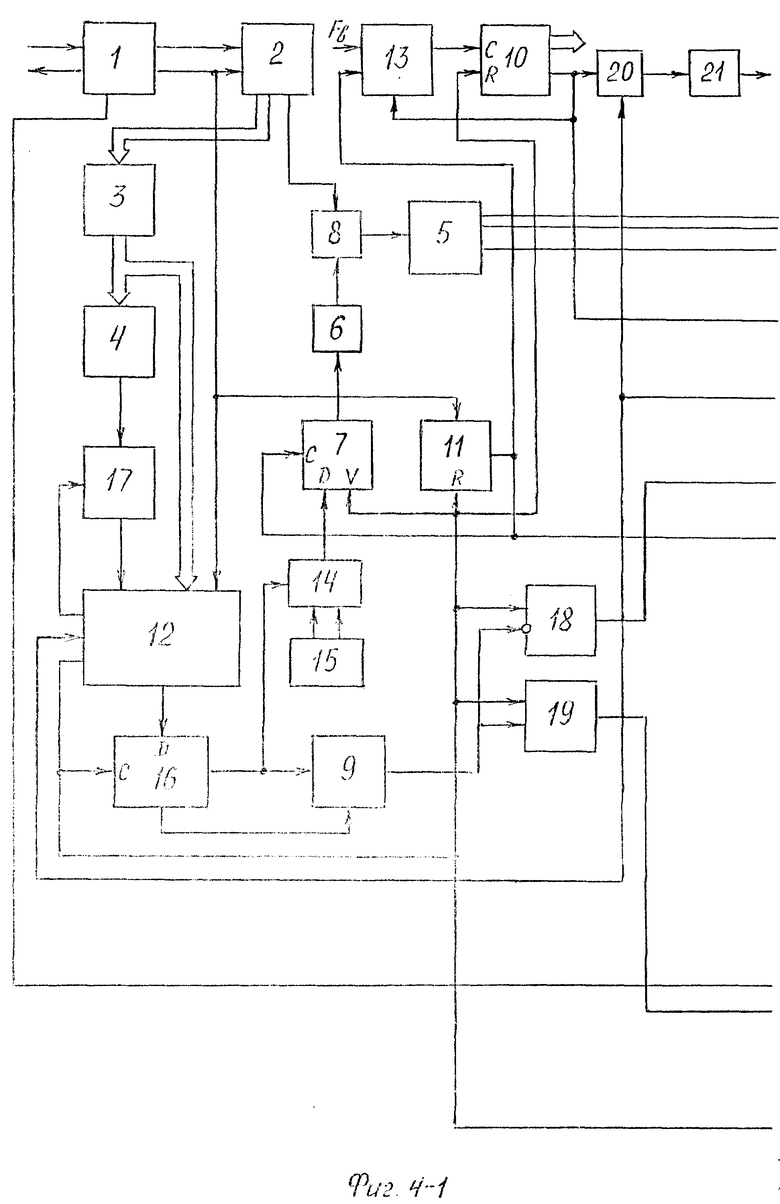

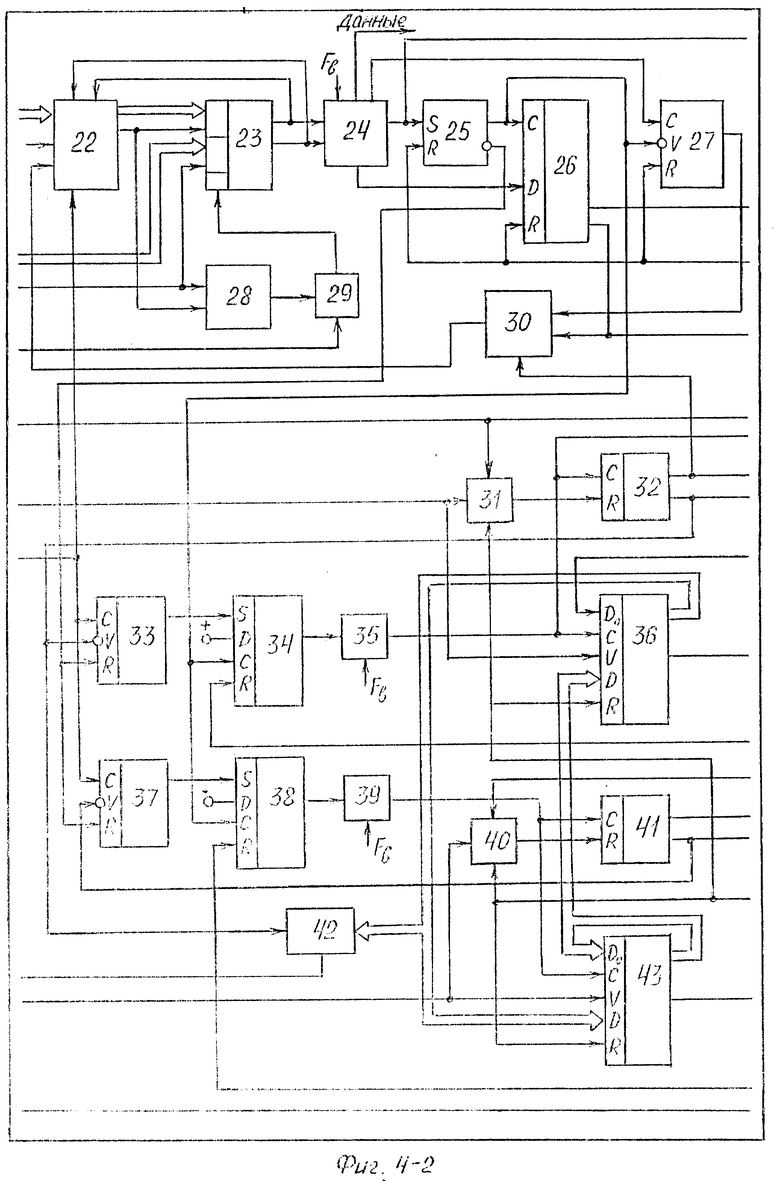

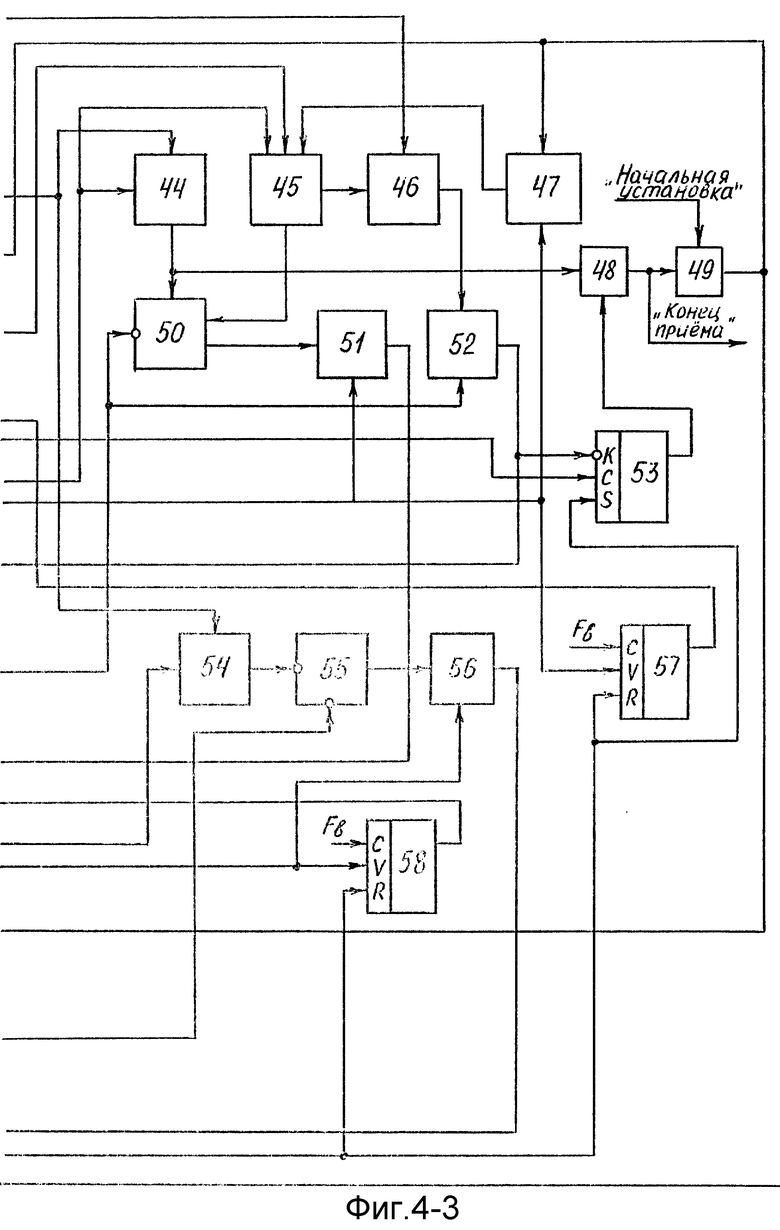

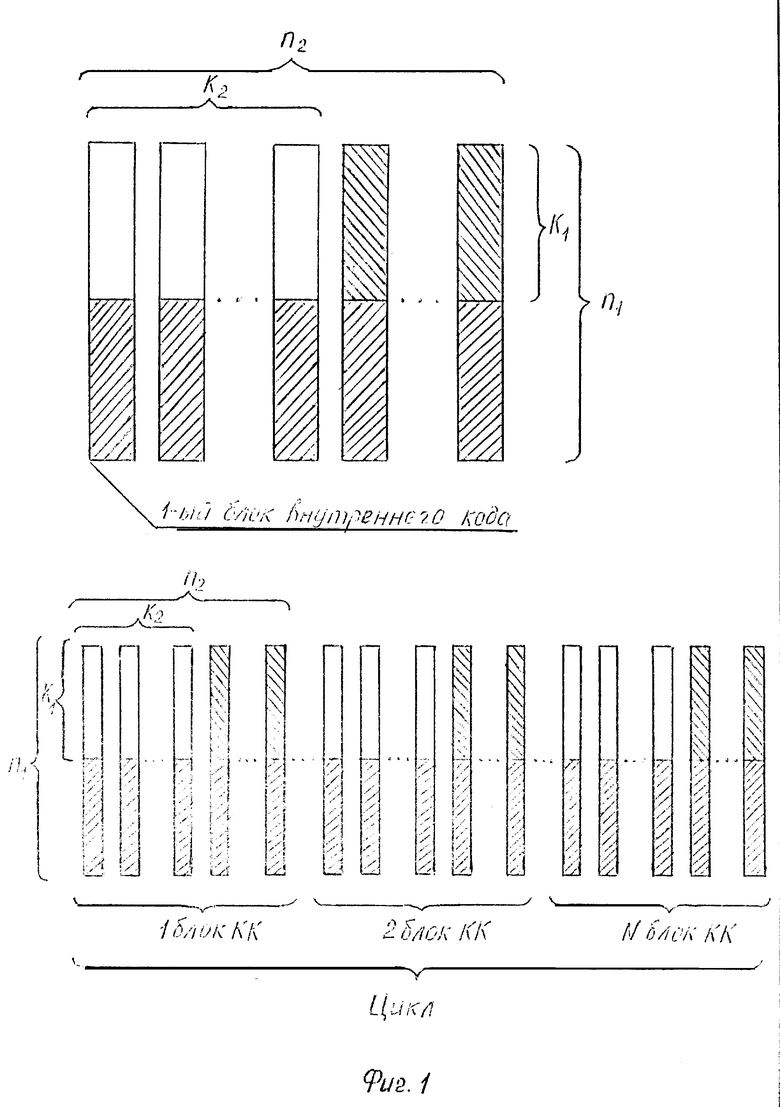

на фиг. 4-1, 4-2, 4-3 - функциональная схема примера реализации приемной части устройства, на фиг. 5 - диаграмма состояний узлов устройства, на фиг. 6 - функциональная схема примера реализации блока синхронизации.

Передача информации по предлагаемому способу осуществляют следующим образом. Информация от корреспондента поступает блоками, содержащими информационную и служебную части, при этом последняя состоит из номера блока и числа блоков в цикле. Поступающий блок кодируют каскадным кодом [3, стр. 228]. Закодированные каскадным кодом N блоков, образующие цикл, последовательно друг за другом без изменения направления передачи передают в канал связи. О неприеме всех или некоторых блоков цикла приемная сторона сообщает передающей стороне в квитанции. Передающая сторона в следующем цикле передает дополнительные символы к этим блокам. Последовательность передач, начинающаяся от момента передачи первого блока и заканчивающаяся моментом приема последнего из N блоков образует сеанс связи.

В отличие от прототипа, в котором передача осуществляется по одному блоку и на каждый блок принимающей стороной передается квитанция и, следовательно, тратится время на переключение каналообразующих средств, по предлагаемому способу квитанция передается на весь цикл с существенно меньшими затратами времени (в пересчете на 1 блок).

В [1] также квитируется все сообщение, однако там при неприеме квитанции это сообщение все повторяется. По предлагаемому способу в квитанции запрашиваются только недоведенные блоки. Для этого квитанция формируется в виде последовательности "1" и "0", где 1 означает правильный прием, а "0" - ошибочный прием блока, причем расположение этих символов по длине квитанции соответствует номеру блока. Для повышения помехоустойчивости квитанции ее кодируют корректирующим ошибки кодом, например (1) и несколько раз повторяют.

Запрос в квитанции сразу нескольких ошибочно принятых блоков позволяет более эффективно использовать пропускную способность канала, чем в известных технических решениях.

При кодировании блока внешним (n2; K2) кодом формируют основные и дополнительные символы. Например, если выбран код РС (64, 28), то число основных символов равно 32 и дополнительных тоже 32. Если выбран более мощный код, например (n2; K2) (96, 28) над GF(27), то число дополнительных может быть равно 64. Дополнительные символы могут передаваться как все сразу в следующем цикле, так и порциями, например, по 32 символа в каждой, передаваемые в двух циклах для кода РС (96, 28).

Деление символов на основные и дополнительные - чисто условное, так как при ухудшении качества канала связи, когда будут исчерпаны все дополнительные символы, осуществляется повторная передача всех символов, начиная с основных, которые будут использоваться при декодировании внешнего кода в дополнение к переданным, и в этом смысле являются также дополнительными.

Основные и дополнительные символы на передающей стороне запоминают. В первом цикле сеанса передают только основные символы. При неполучении в заданное время квитанции на первый цикл его полностью повторяют. При неполучении квитанции на любой другой цикл сеанса передают очередные дополнительные символы к неприятным блокам, зафиксированные в последней принятой квитанции.

При получении квитанции с номерами ошибочных блоков передают дополнительные символы этих блоков. На приемной стороне основные и дополнительные символы образуют умощненный внешний код. Так, например, если после 1-го цикла имеем код РС (32, 28), позволяющий исправить 4 ошибочно принятых (стертых символа внешнего кода, то после второй передачи имеем код РС (64, 28) после третьей - (96, 28) и так далее, которые позволяют уже исправить соответственно 36, 68 и так далее ошибок во внешнем коде.

Таким образом, резко наращивается мощность кода и осуществляется адаптация к качеству канала связи, при этом при декодировании, как это будет показано дальше, используются как предыдущие передачи так и текущая.

Как говорилось выше, при ухудшении качества канала связи повторно передают все символы, начиная с основных. Благодаря этому на приемной стороне будет уже не одно, а два или более повторения одних и тех же символов, поэтому становится возможным использование на приемной стороне синхронного накопления, о чем будет сказано ниже.

Для определения при приеме информации границ блоков комбинации внутреннего кода в пределах блока нумеруются, например, для вышеупомянутого кода РС (32, 28) номерами от 0 до 31. Для повышения достоверности передачи номера кодируются путем дополнения информационной части служебной, которая представляет собой инверсию информационной. Код нумерации, для приведенного примера (12, 6), используется в режиме обнаружения ошибок.

По предлагаемому способу предусмотрен, кроме первого также и второй вид нумерации комбинаций внутреннего кода, например, от 32 до 63. Смена вида нумерации происходит при получении передающей стороной квитанции. Благодаря смене вида нумерации приемная сторона получает подтверждение о приеме квитанции передающей стороной.

Отличительной чертой предлагаемого способа является передача обоих видов номеров без затраты пропускной способности канала связи, для чего формируют суммарные кодовые комбинации путем сложения каждой комбинации внутреннего кода с комбинацией соответствующего ей номера. Например для внутреннего кода (24, 12) осуществляют сложение проверочной части этого кода с 12-ти разрядной комбинацией номера.

Прием информации осуществляется следующим образом. Принимаемую информацию на каждом такте частоты приема проверяют на соответствие закону построения суммарных кодовых комбинаций. Данная операция необходима для определения границ внутреннего кода. Для осуществления этой операции на каждом такте вычисляются последовательно два синдрома: синдром внутреннего кода и синдром кода нумерации. Если проверяемая последовательность соответствует закону построения суммарных кодовых комбинаций, то при отсутствии ошибок в канале связи синдром кода нумерации будет равен 0 и будет выделяться периодически через n1 тактов. Для повышения помехоустойчивости и уменьшения времени синхронизации по комбинациям внутреннего кода проверку на соответствие целесообразно осуществлять сразу на нескольких позициях, о чем подробно будет сказано при описании примера реализации способа.

Определение синдромов может осуществляться, например, путем умножения принятого слова соответствующей разрядности на проверочную матрицу кода. Результатом вычисления первого синдрома будет являться номер комбинации внутреннего кода, который фиксируется в момент выделения "нулевого" синдрома кода нумерации.

По известному номеру определяются границы блока внешнего кода, тип системы нумерации (первый или второй). Комбинации внутреннего кода формируют путем вычитания из суммарных комбинаций выделенных комбинаций номеров, после чего комбинации внутреннего кода декодируют. В процессе декодирования комбинаций осуществляется оценка их качества. Например, в простейшем случае при обнаружении ошибки фиксируется "плохая" комбинация, при отсутствии ошибок "хорошая".

Но возможна и более детальная оценка качества (надежности) комбинации тремя, четырьмя и так далее градациями, например, по количеству искаженных символов в комбинации: нулевая - отсутствие ошибок, первая - наличие однократных ошибок, вторая - двухкратных ошибок и так далее. Комбинации с оценками надежности запоминаются и декодируются в декодере внешнего кода по известным алгоритмам [4], [5].

В случае положительного результата декодирования блока он выдается получателю. В случае отрицательного результата декодирования номера недекодированных блоков цикла сообщаются в квитанции на передающую сторону, которая в ответ на квитанцию передает дополнительные символы, которые вместе с основными образуют умощненный код, обладающий большим кодовым расстоянием, о чем говорилось выше.

Если блок не декодирован после передачи основных и дополнительных символом, то осуществляется повторная их передача. При этом проявляется возможность выбора методом синхронного накопления более надежных символов внешнего кода из разных передач, используя оценки надежности этих символов.

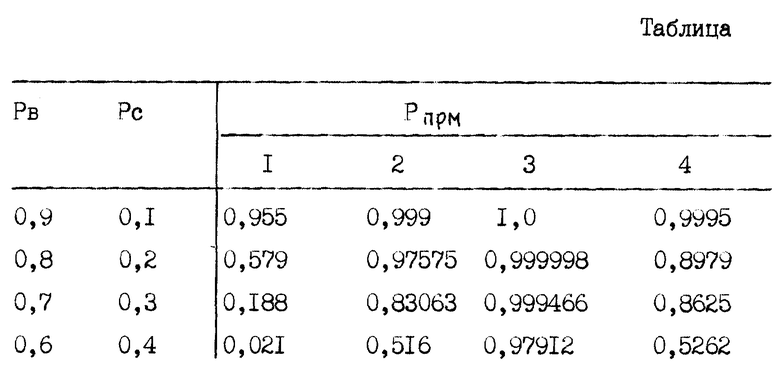

На фиг. 2 представлена временная диаграмма процесса формирования умощненного кода с использованием метода синхронного накопления для варианта, когда передается только один блок дополнительных символов.

На передаче формируются основные (A) и дополнительные (B) символы. Предполагается, что до начала приема в памяти ОЗУ на приемной стороне хранятся N блоков по n2 символов внешнего кода каждый с наинизшими оценками качества по сравнению с поступающими из канала связи (стертые символы, обозначаемые X). В процессе приема ОЗУ заполняется символами внешнего кода, образованными методом синхронного накопления из хранящихся в ОЗУ и приходящих из канала связи. По существу, пока не будет повторных передач, ОЗУ заполняется канальными символами.

Происходит это следующим образом (см. фиг. 2). В первом цикле передаются основные символы A, а в декодер внешнего кода на приемной стороне вводится умощненный блок из 2n2 (фиг. 2a) символов. Первые n2 символов - это хранящиеся в памяти приемного ОЗУ (X1), а вторые - результат синхронного накопления следующих n2 символов X2, хранящихся в ОЗУ и n2 символов принятого A1 блока. С учетом приоритета по качеству канальных символов в первом цикле в декодер внешнего кода поступят символы A1. Второй блок, вводимый в декодер (A1* X2), где * - символ операции синхронного накопления, запоминается в ОЗУ по адресу блока, участвовавшего в синхронном накоплении (X2). Декодер внешнего кода осуществляет декодирование умощненного блока. Если блок не декодируется, то после приема всего цикла в квитанции будет сообщен результат декодирования этого и других недекодированных блоков.

Предположим, что блок A1 не декодирован и во втором цикле передан блок B дополнительных символов. При этом в декодер поступят блок A1 * X2 = A1 и блок B1 * X1 = B1 (приоритет опять отдан канальным символам). По существу в декодер поступит умощненный блок A1B1 (фиг. 2б). Если и в этот раз блок будет недекодирован, то в третьем цикле второй раз (A2) будут переданы основные символы, и в декодер поступят блоки B1 * X1 = B1 и (A1 * X2) * A2 = A1 * A2 (фиг. 2б). Таким образом, в нашем примере, начиная с третьего цикла, проявляется эффект синхронного накопления, при котором выбираются наиболее надежные символы из двух одинаковых блоков, принадлежащих разным передачам. Аналогичный процесс формирования умощненного блока будет происходить при необходимости в четвертом, пятом цикле и так далее, до тех пор, пока блок не будет декодирован.

При положительном результате декодирования хотя бы одного блока из его служебной части выделяют информацию о длине цикла (числе блоков в цикле) и по результатам декодирования остальных блоков цикла формируют квитанцию с указанием номеров недекодированых блоков, запоминают ее и выдают на передающую сторону. Знание на приемной стороне длительности цикла необходимо для определения момента приема повторной передачи цикла. При передаче квитанции возможны два варианта: первый - квитанция принята и второй - квитанция не принята. В первом варианте передается новый цикл в соответствии с квитанцией, во втором варианте передается предыдущий цикл. Поэтому на приемной стороне необходимо знать оба цикла, чтобы их отсчитывать. Кроме того, на приемной стороне необходима информация о том, какой цикл поступает в конкретный момент. Для извещения приемной стороны о факте неприема квитанции в заданное время передающая сторона организует передачу предыдущего цикла, то есть с прежней системой нумерации комбинаций внутреннего кода. При приеме квитанции передающая сторона передает новый цикл в соответствии с номерами блоков, запрошенных в квитанции, при этом меняется тип нумерации комбинаций внутреннего кода.

При обнаружении приемной стороной смены типа нумерации фиксируется факт приема квитанции передающей стороной и осуществляется прием нового (текущего) цикла в соответствии с номерами повторяемых блоков и длиной цикла, зафиксированными в квитанции текущего цикла. Фазирование может быть проведено на любом блоке КК цикла. Номер этого блока определяется по времени приема и последовательности некодированных блоков, зафиксированной в квитанции.

При обнаружении приемной стороной того же типа нумерации фиксируется факт неприема квитанции передающей стороной и осуществляется прием предыдущего цикла в соответствии с номерами повторяемых блоков и длиной цикла, зафиксированными в последней доведенной квитанции.

Если приемная сторона в ожидаемое время не выделяет ни тот, ни другой тип нумерации, то отслеживаются (отсчитываются) длины циклов и номера блоков внешнего кода двух циклов: цикла, на который передавалась последняя квитанция и цикла, на который прием квитанции подтвержден.

Возможность реализации предлагаемого способа поясняется функциональными схемами передающей и приемной части.

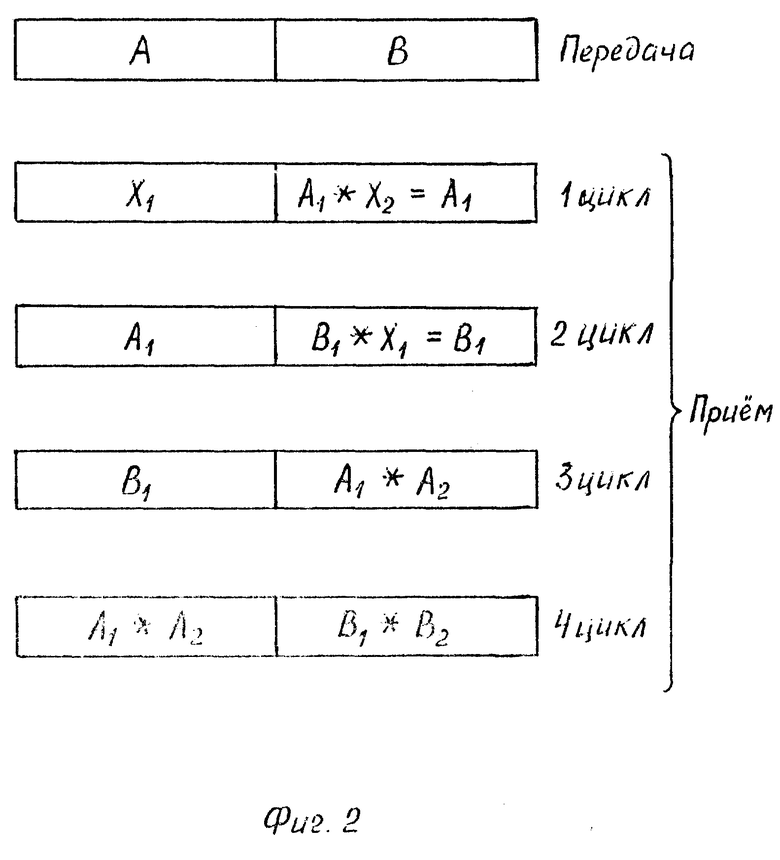

На фиг. 3-1 и 3-2 представлена функциональная схема передающей части устройства (пример), реализующая прелагаемый способ. Устройство содержит следующие блоки:

датчик адресов записи 1,

коммутатор 2,

кодер внешнего кода 3,

оперативное запоминающее устройство (ОЗУ) 4,

кодер внутреннего кода 5.

сумматор 6,

устройство преобразования сигналов 7,

счетчик блоков 8,

первый 9, второй 10, третий 11 датчик и счетчики адресов считывания,

кодер кода нумерации 12,

входной регистр квитанции 13

регистр числа блоков 14,

блок сравнения 15,

датчик номеров 16,

коммутатор вида нумерации 17,

датчик вида нумерации 18,

счетчик длины внутреннего кода 19,

счетчик длины внешнего кода 20,

первый 21, второй 22 и третий 23 элементы ИЛИ,

счетчик ожидания квитанции 24

первый 25, второй 26, третий 27 элементы И,

первый 28, второй 29, третий 30, четвертый 31 триггеры,

декодер кода квитанции 32,

кольцевой регистр квитанции 33.

Устройство работает следующим образом.

Информация, подлежащая передаче, поступает в параллельном коде, разрядность которого определяется разрядностью используемой шины, в сопровождении частоты ввода FВВ и сигнала "Начало блока". Служебная часть блока, которая несет информацию о числе блоков цикла, записывается в регистр числа блоков 14, а информационная - через коммутатор 2, устанавливаемый сигналом "Начало блока", в кодер внешнего кода 3. Сигнал "Начало блока" поступает также в счетчик блоков 8, который фиксирует номер текущего блока. После окончания ввода блока снимается сигнал "Начало блока" и коммутатор 2 устанавливается в состояние, при котором во внешний кодер 3 поступают служебная часть блока: номер текущего блока с основного выхода счетчика блоков 8 и число блоков в цикле с выхода регистра числа блоков 14. Кодер внешнего кода 3 кодирует блоки внешним кодом. Закодированные блоки данных из кодера 3 в сопровождении импульса записи поступают в ОЗУ4, где записываются по адресу, формируемому из импульсов записи датчиком адресов записи 1.

После поступления второго блока на вход передатчика начинается передача информации в канал связи. Для этого счетчик блоков 8 по дополнительному выходу выдает сигнал "Начало передачи", который устанавливает второй 10 датчик адреса считывания в нулевое состояние. При этом датчик 10 формирует адрес зоны, в которой хранятся основные символы внешнего кода. При поступлении на второй (счетный) вход импульса датчик 10 сформирует адрес зоны, в которой хранятся дополнительные символы внешнего кода.

Сигнал с дополнительного выхода счетчика блоков 8 через первый 21 элемент ИЛИ устанавливает второй 29 триггер в состояние "О", при этом сигналом с инверсного выхода его УПС 7 устанавливается в режим передачи и разрешается работа счетчика ожидания квитанции 24, счетчика длины внутреннего кода 19, счетчика длины внешнего кода 20 и третьего 11 датчика адресов считывания. Счетчик 19 через n1 тактов частоты передачи Fпрд выдает импульс считывания в ОЗУ 4, на счетный вход счетчика 9, задающего младшие разряды адреса считывания, на управляющий вход кодера 5 внутреннего кода, разрешая его работу. Третий датчик 11 адресов считывания задает старшие разряды адреса считывания из ОЗУ 4 (номер зоны, в которой записан текущий блок).

Из ОЗУ 4 K1 - разрядные комбинации поступают в кодер 5 внутреннего (n1; K1) кода. Из кодера 5 информации в последовательности коде поступает в сумматор 6 по модулю два.

Сигнал с выхода счетчика 19 поступает также на счетный вход датчика номеров 16, при этом последний выдает текущий номер кодовой комбинации внутреннего кода одной из двух используемых систем нумерации. Система нумерации задается датчиком вида нумерации 18 и счетным триггером 31. Исходные номера одной из 2-х систем нумерации через коммутатор 17 записываются в счетчик 16. Последний в параллельном виде выдает номер комбинации внутреннего кода, который в кодере 12 кодируется корректирующим ошибки кодом. Этот номер в сумматоре 6 накладывается на проверочную часть комбинации внутреннего кода, и результат суммирования через УПС 7 поступает в канал связи.

Работа кодера 12 осуществляется под действием частоты передачи Fпрд, поступающей через третий 27 элемент И, в свою очередь открываемый сигналом с выхода счетчика 19.

Смена номера считываемого из ОЗУ 4 блока внешнего кода происходит по сигналу с выхода счетчика 20 длины внешнего кода, который отсчитывает n2 символов внешнего кода (комбинаций внутреннего кода) и через третий 23 элемент ИЛИ выдает сигнал на установку первого 28 триггера в состояние "1", при этом второй 26 элемент И открывается и импульс высокой частоты Fвыс проходит на счетный вход третьего 11 датчика адресов считывания, увеличивая его состояние на 1.

Номер считываемого из ОЗУ текущего блока, выдаваемый третьим 11 датчиком адресов считывания, сравнивается с числом блоков в сообщении, хранящимся в регистре 14 числа блоков, с помощью блока сравнения 15, который выдает сигнал в том числе, когда показания регистра 14 будут больше показаний датчика 11. При этом импульс с выхода блока сравнения 15 через второй 22 элемент ИЛИ поступает на сброс первого 28 триггера, закрывая тем самым второй 26 элемент И, и состояние датчика 11 не изменится до тех пор, пока не будут сосчитаны все комбинации внутреннего кода текущего блока.

После считывания последнего блока сообщения блок сравнения 15 не выдает импульс сброса на триггер 28 и в течение некоторого времени на вход датчика 11 будут поступать импульсы частоты Fвыс. После того, как датчик 11 отсчитает максимально возможное число Nmax блоков в сообщении, по второму выходу он выдает сигнал, закрывающий элемент И26, а также на второй 29 триггер, при этом счетчики 19 и 20 и датчик 11 устанавливаются в исходное состояние. УПС 7 переключается на прием, запускается счетчик ожидания квитанции 24. Входные символы поступают в приемное УПС 7 и в сопровождении тактовой частоты приема записываются во входном регистре квитанции 13. С выхода регистра 13 символы в параллельном коде поступают в декодер 32 кода квитанции и в кольцевой регистр 33 квитанции. Декодер 32 на каждом такте проверяет принятую последовательность на соответствие корректирующему ошибки коду и при соответствии выдает сигнал, фиксирующий квитанцию в регистре 33, переключающий четвертый 32 триггер в противоположное состояние, благодаря чему в датчик 16 через коммутатор 17 записываются исходные данные второй системы нумерации.

Кроме того, сигнал с выхода декодера 32 устанавливает третий 30 триггер в состояние "1". При этом открывается первый 25 элемент И и после окончания отсчета счетчиком 24 времени ожидания квитанции устанавливается режим передачи недоведенных блоков, а именно: в датчике номеров 16 фиксируется новая система нумерации комбинаций внутреннего кода и сигналом с выхода элемента И25 в счетчике 10 устанавливается адрес зоны ОЗУ 4, в которой хранятся дополнительные символы переданных блоков внешнего кода.

Кроме того, сигналом с выхода счетчика 24 через первый 21 элемент ИЛИ триггер 29 и УПС 7 устанавливаются в режим передачи, а через элемент ИЛИ 23 триггер 28 устанавливается в состояние "1". При этом, если на ходе кольцевого регистра квитанции 33 присутствует "0" (непринятый блок), то с выхода элемента ИЛИ 22 поступит сигнал сброса триггера 28, в результате чего импульс частоты Fвыс не пройдет через элемент И 26 и счетчик 1 не сменит адрес считывания. При этом с приходом очередного импульса частоты Fпрд сигналом с выхода счетчика 19 произойдет считывание из ОЗУ 4 дополнительных символов непринятого блока по адресу, указанному датчиками 9, 10 и 11.

Если же на выходе регистра 33 присутствует "1" (блок принят), то с выхода элемента И 26 будет выдан импульс который продвинет регистр 33 и счетчик 11 на один такт, при этом на выходе счетчика установится адрес проверочных символов следующего блока. Если и следующий блок был принят, то счетчик 11 и регистр 33 продвинутся еще на один шаг. Так будет происходить до тех пор, пока на выходе регистра 33 не появится "0", при этом опять произойдет считывание дополнительных символов следующего неприятного блока. Описанное выше будет происходить до тех пор, пока счетчик 11 не отсчитает максимальное число блоков Nmax, в результате чего триггер 29 переключится в режим приема.

Регистр 33 выполнен кольцевым, то есть его выход подключен ко входу (на фиг. 3 эта цепь не показана). Благодаря этому квитанция циркулирует в нем, что необходимо для организации повторной передачи дополнительных символов в случае, если предыдущая передача их была неуспешной.

При этом, в случае неполучения квитанции в заданное время, на триггер 31 не поступит импульс и при повторной передаче система нумерации не будет сменена, что позволяет приемной стороне определить факт неприема квитанции передающей стороной.

В случае неприема квитанции вообще декодер кода квитанции 32 не сработает ни разу и в кольцевом регистре квитанции 33 останутся записанными все "0", смены нумерации комбинаций внутреннего кода в датчике 16 не произойдет, и сигналом с выхода счетчика ожидания квитанции 24 через элемент ИЛИ 23, триггер 28, элемент И 26 будет запущен счетчик 11, при этом из ОЗУ 4 будут вновь сосчитаны все блоки первого цикла.

На фиг. 4-1, 4-2 и 4-3 представлена функциональная схема приемной части устройства (пример), реализующей предлагаемый способ.

Устройство содержит блоки:

устройство преобразования сигналов 1,

приемный регистр 2,

вычислитель синдрома внутреннего кода 3,

вычислитель синдрома кода нумерации 4,

декодер внутреннего кода 5,

кодер кода нумерации 6,

датчик кода нумерации 7

первый 8 и второй 9 сумматоры по модулю два,

счетчик удвоенной длины внешнего кода 10,

счетчик длины внутреннего кода 11,

блок синхронизации 12,

первый 13, второй 14, третий 23 коммутаторы,

датчик вида нумерации 15,

регистр вида нумерации 16,

первый 17, второй 18, третий 19, четвертый 29

пятый 35, шестой 39, седьмой 46, восьмой 48

девятый 50, десятый 55 элементы И,

первый 20, второй 31, третий 40, четвертый 49,

пятый 51, шестой 52, седьмой 56 элементы ИЛИ

первый 21, второй 25, третий 34, четвертый 38,

пятый 47, шестой 53 триггеры,

оперативное запоминающее устройство (ОЗУ) 22,

декодер внешнего кода 24,

первый 26, второй 26, третий 43 регистры сдвига,

счетчик отрицательных результатов декодирования 27,

первый 28, второй 44, третий 45, четвертый 54,

блоки сравнения,

арифметическое устройство (АУ) 30,

первый 32, второй 41 счетчики блоков,

первый 33 и второй 37 счетчики длины внешнего кода,

кодер квитанции 42,

первый 57 и второй 58 счетчики квитанции:

Устройство работает следующим образом.

Инстформация из канала связи поступает в УПС 1, которое обеспечивает согласование с каналом связи и преобразование сигналов в двоичную форму. Двоичные сигналы в сопровождении тактовой частоты поступают в приемный регистр 2, длиной n1-n2. С выхода приемного регистра 2 n1 -разрядные комбинации поступают в вычислитель синдромов внутреннего кода 3, а с выхода последнего - в вычислитель синдромов кода нумерации 4. При отсутствии помех в канале связи через n1 тактов частоты приема на выходе вычислителя 4 будут выделяться "0". Этот сигнал, проходя через первый 17 элемент И, фиксирует в блоке синхронизации 12 номер комбинации внутреннего кода, поступающий в него с выхода вычислителя 3. В блоке синхронизации по этим номерам выделяется сигнал фазирования, соответствующий приему последнего бита блока каскадного кода. Более подробно работа блока синхронизации будет описана ниже. Сигнал фазирования разрешает работу датчика 7 кода нумерации, устанавливает в исходное состояние счетчик длины внутреннего кода 11, счетчик удвоенной длины внешнего кода 10, а также открывает второй 18-и и третий 19 элементы И.

По второму выходу блок синхронизации выдает старший разряд номера, который определяет вид нумерации ("0" - первый вид нумерации, "1" - второй). Этот старший разряд фиксируется в 2-разрядном регистре сдвига 16 сигналом фазирования. С выхода регистра 16 сигнал вида нумерации поступает на управляющий вход второго 14 коммутатора, при этом в датчик 7 записываются исходные данные с датчика вида нумерации (N1 или N2) 15. На тактовый вход датчика 7 через n1 тактов приемной частоты Fпрм поступают сигналы, вырабатываемые счетчиком 11. Таким образом датчик 7 вырабатывает последовательно n2 номеров, которые поступают в кодер кода нумерации 6, который колирует номера корректирующим ошибки кодом, например, кодом (12,6), о чем говорилось выше. На первом 8 сумматоре происходит сложение по модулю два проверочной части принятых, n1 - разрядных комбинаций и выше упомянутых номеров, то есть снятие системы нумерации. В декодере внутреннего кода 5 комбинации внутреннего кода декодируются, при этом декодер формирует дополнительно характеристику качества комбинации, например, при отсутствии ошибок - хорошее качество ("1), а при наличии ошибок - плохое качество ("0").

Информационные комбинации с их характеристикой с выхода декодера 5 через третий коммутатор 23 поступают в декодер внешнего кода 24 и в ОЗУ 22. Запись осуществляется по адресу, формируемому счетчиком 10, первым триггером 21 и АУ 30. При этом последнее задает номер зоны, в которую осуществляется запись блока. АУ 30 вычисляет разность между показаниями счетчиков 26 и 32. До первого положительного результата декодирования эта разность равна 0. Поэтому запись первого блока, на котором выделен сигнал фазирования осуществляется в нулевую зону. Счетчик 10 задает младшие разряды адреса ячеек ОЗУ, в которые записываются комбинации внутреннего кода с их характеристиками. Триггер 21 задает адреса первой или второй части, из n2 символов каждая, одного умощенного блока внешнего кода.

В рассматриваемом примере реализации умощненный блок содержит 2 части, первая - основные и вторая - дополнительные символы, поэтому и счетчик 10 выбран двойной длины, а в качестве датчика номеров зон, где хранятся основные и дополнительные символы, выбран счетный триггер 21. Если бы дополнительных символов была бы не одна часть, а больше, например 3, то счетчик 10 был бы длины 4n2, а вместо счетного триггера 21 необходимо было бы использовать счетчик на 4, задающий номера 4-х зон.

После установки счетчика 10 сигналов фазирования на управляющем выходе счетчика сигнал отсутствует и на его счетный вход в течение n2 тактов коммутируется высокая частота Fb. При этом из ОЗУ 22 сосчитываются n2 комбинаций внутреннего кода, которые при первом приеме имеют низкую характеристику качества. Эти комбинации через коммутатор 23 поступают в декодер 24 внешнего кода. Через n2 тактов сигнал со второго выхода счетчика 10 открывает элемент И 29, меняет состояние триггера 21 на противоположное и устанавливает коммутатор 13 в состояние, при котором на счетный вход счетчика 10 поступают сигналы с выхода счетчика 11. Блок сравнения 28 сравнивает характеристики комбинаций, выдаваемых декодером 5 и ОЗУ 22. При первоначальном приеме характеристика, выдаваемая декодером выше, поэтому блок сравнения в течение n2 тактов выдает сигнал, который через элемент И29 удерживает коммутатор 23 в состоянии, при котором на вход декодера 24 коммутируются комбинации и характеристики их, выдаваемые декодером 5, которые одновременно записываются в ОЗУ 22 по сигналу записи, выдаваемому счетчиком 11.

Таким образом, в декодер 24 поступает умощненный блок, как это изображено на фиг. 2. По существу в 1-ом цикле приема декодер принимает решение только по вторым n2 символам, принятым из канала связи, так как первые n2 символов - это стертые символы внешнего кода с низшими оценками качества.

После ввода в декодер 24 умощненного блока декодер вырабатывает результат декодирования. Отрицательные результаты декодирования, выдаваемые декодером по первому выходу, подсчитываются счетчиком отрицательных результатов 27.

Если первый блок, на котором был выделен сигнал фазирования, не будет декодирован, то состояние счетчика 27 будет равно 1. Это число с выхода счетчика 27 поступит в АУ 30, которое задает зону 1 для записи следующего блока. Если и этот блок будет с отрицательным результатом декодирования, то счетчик 27 и АУ 30 зададут зону 2 для записи третьего блока и так далее. Первый положительный результат декодирования, выдаваемый декодером 24 по второму выходу, устанавливают триггер 25 в состояние "1", при этом в счетчике 27 фиксируется число блоков с отрицательным результатом декодирования. По третьему выходу декодер 24 выдает служебную часть декодированного блока, содержащую номер декодированного блока и число блоков в сообщении, которые записываются в регистре 26. Сам декодированный блок выдается получателю по четвертому выходу. Так как в составе блока выдается и номер его, то получатель имеет возможность сам отбраковывать повторно принятый блок, хотя в принципе эта задача может быть решена декодером 24.

Сигнал с прямого выхода триггера 25 устанавливает в состояние "1" триггеры 34 и 38, при этом открываются элементы И 35 и 39. Сигнал с инверсного выхода триггера 25 разблокирует первый 33 и второй 37 счетчики длины внешнего кода.

Предположим, что в первом цикле нумерация комбинаций внутреннего кода такова, что на выходе второго сумматора 9 сигнал отсутствует (смены нумерации не произошло). Тогда будет открыт элемент И 18 и сигнал фазирования, пройдя через него, разрешит работу второго 36 регистра сдвига, а через элемент ИЛИ 31 установит первый 32 счетчик блоков в "0" состояние.

Импульс высокой частоты Fв через элемент "И" 35 проходит на вход счетчика 32, при этом на выходе последнего устанавливается число, равное "1", которое поступает в третий бок 45 блок сравнения. Работа последнего разрешается сигналом с выхода пятого 47 триггера, в свою очередь установленного в состояние "1" через элемент ИЛИ 49 сигналом "Начальная установка". Блок сравнения 45 сравнивает состояния счетчика 32 (в данном случае число "1") и регистра 26, который по первому выходу выдает номер первого блока с положительным результатом декодирования. Если перед первым положительным результатом декодирования декодер 24 выдавал отрицательные результаты декодирования, то показания регистра 26 будут больше показаний счетчика 32, блок сравнения 45 выдает "0", элемент И 46 будет закрыт. При этом сигнал "0" с выхода регистра 36 через элемент ИЛИ 52 сбросит триггера 53 в состояние "0" и запишется в регистр 36 по входу D0. Описанным образом в регистре 36 запишется столько "0", сколько будет отрицательных результатов декодирования, при этом счетчик 32 увеличит свое состояние до номера блока, записанного в регистре 26. Как только показания регистра 26 и счетчика 32 сравнятся, блок сравнения 45 сработает, по первому выходу выдаст сигнал на элемент И 46, при этом положительный результат декодирования, выдаваемый декодером 24 пройдет через элемент И 46, элемент ИЛИ 52 и запишется в регистр 36 в виде "1". Следующий такт частоты Fв увеличить показания счетчика 32 на единицу, при этом разность между показаниями регистра 26 и счетчика 32 будет равна "1". Арифметическое устройство 30 по показаниям счетчика 27, регистра 26 и счетчика 32 задает номер зоны для записи следующего принимаемого блока. При этом блок сравнения 45 по второму выходу выдаст сигнал "больше", который через элемент И 50, элемент ИЛИ 51 сбросит триггер 34 в состояние "0", закрывая элемент И 35 до прихода следующего блока. Следующий блок запишется в зону, заданную АУ 30, и поступит в декодер 24. В случае отрицательного результата декодирования на выходе элемента И 46 будет "0", который через элемент ИЛИ 52 поступит на вход D0 регистра 36.

Положительный результат декодирования пройдет через элемент И 46, ИЛИ 52 и запишется в виде "1" в регистр 36. После поступления последней комбинации внутреннего кода сработает первый 33 счетчик длины внешнего кода и выдаст сигнал, устанавливающий триггер 34 в состояние "1", при этом открывается элемент И 35 и импульс высокой частоты Fв увеличит показания счетчика 32 на единицу, а также зафиксирует в регистре 36 результат декодирования. Так как показания счетчика 32 будут больше показаний регистра сдвига 26, то блок сравнения 45 выдаст сигнал по второму выходу, который, пройдя через элементы И 50, ИЛИ 51 сбросит триггер 34. Устройство готово к приему следующего сообщения, который начнется опять с выдачи результата декодирования и срабатывания через n2 символов внешнего кода счетчика 33. После приема последнего блока сообщения, когда в регистре 36 будет записана последовательность "1" и "0", причем "1" будет означать принятый блок, а "0" - непринятый, число блоков в сообщении, выдаваемое по второму выходу регистра 26, и показания счетчика 32 сравняются, при этом сработает блок сравнения 44, и если триггер 53 не сброшен, что будет только в том случае, когда все блоки будут декодированы, то на выходе элемента И 48 будет сформирован сигнал "Конец приема" , устанавливающий устройство в исходное состояние. Сигнал с выхода блока сравнения 44 закрывает элемент И 50, поэтому сигнал с выхода блока сравнения 45 не пройдет через элементы И 50 и ИЛИ 51, в результате чего триггер 34 не будет сброшен до тех пор, пока счетчик 32 не выдаст сигнал по второму выходу, который соответствует максимально возможному числу Nm блоков в сообщении. Этим сигналом триггер 47 устанавливается в состояние "0", сбрасывается триггер 34, запускается счетчик 57, отсчитывающий время передачи квитанции, блокируется работа счетчика 33 и разрешается работа кодера квитанции 42, в котором записана квитанция, выдаваемая регистром 36 по параллельному выходу.

Закодированная корректирующим ошибки кодом квитанция через УПС 1 передается в канал связи.

После отсчета времени передачи квитанции сигналом с выхода счетчика квитанции 57, счетчик 32 через элемент ИЛИ 31 сбрасывается в состояние "0", триггер 21 через элемент ИЛИ 20 - в противоположное состояние. Устройство готово к приему повторной передачи.

В следующем цикле приема возможны два варианта приема сообщения. Первый вариант - прием сообщения в случае неприема передающей стороной квитанции и второй - в случае приема квитанции.

В первом варианте, если не была получена квитанция на первый цикл, то он будет повторен передающей стороной в неизменном виде, то есть будут переданы основные символы блоков, если же не была получена квитанция на любой другой цикл, то будут переданы очередные дополнительные символы. Так как в первом варианте вид нумерации комбинаций внутреннего кода остается неизменным, то в регистре вида нумерации 16 будут записаны либо два "0" либо две "1". При этом на выходе второго 9 сумматора сигнал будет отсутствовать, и потому будет открыт элемент И 18. При этом сигнал фазирования пройдет через элемент И 18 на вход V регистра 36, разрешая тем самым перепись в него старой квитанции из регистра 43 (в случае второго цикла это будут все "0"). Кроме того, через элемент ИЛИ 31 обнуляется счетчик 32. Во втором варианте вид нумерации изменится, в регистре 16 будет записана комбинация "01" или "10" и сигнал фазирования пройдет через элемент И 19 на вход V регистра 43, разрешая в него перепись квитанции из регистра 36, а также через элемент ИЛИ 40 - на вход R счетчика 41, устанавливая его в состояние "0". Регистр 43 выполняет роль хранения доведенной квитанции. Во втором варианте приема устройство работает аналогично описанному с тем лишь отличием, что после приема каждого блока через элемент И 35 пройдет столько импульсов частоты FB, чтобы в старшем разряде регистра 36 оказался "0", а в счетчике 32-номер следующего непринятого блока.

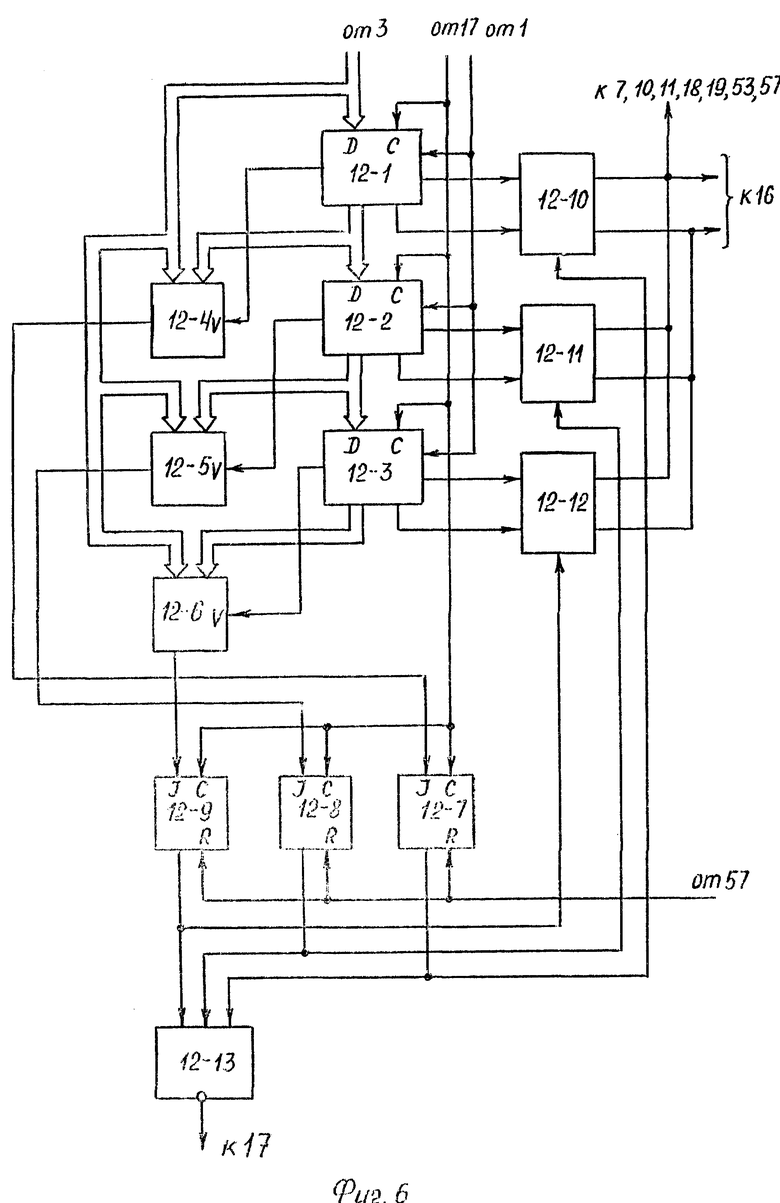

В качестве примера на фиг. 5 представлена диаграмма состояний узлов устройства (счетчика отрицательных результатов 27, регистра 26 и счетчика 32) и номер зоны, в которую записывается принимаемый блок для второго варианта приема в зависимости от результата приема сигнала фазирования и результата приема блока. Номер зоны определяется следующим образом:

Nз = Nсч.32 + (Nсч.27 - Nрг.26) - 1,

в первом цикле и

Nз = Nсч.32 + (Nсч.27 - Nрг.26)

во втором и последующих циклах,

где Nз - номер зоны записи,

Nсч.32 - показания счетчика 32

Nсч.27 - показания счетчика 27

Nрг.26 - показания регистра 26.

По результатам приема блоков формируется квитанция, которая имеет вид 00010001, т.е. должны быть запрошены все блоки, кроме четвертого и восьмого.

В результате положительного декодирования всех блоков сообщения в регистре 36 будут записаны все "1", которые через элемент ИЛИ 52 поддерживают триггер 53 в состоянии "1". При этом после приема последнего блока блок сравнения 44 через элемент И 48 формирует сигнал "Конец приема", устанавливающий устройство в исходное состояние.

Возможна ситуация, когда на каком-либо цикле или нескольких циклах подряд сигналы фазирования вообще не выделяются. Тогда верхняя (узлы 31-36, 44-46, 50-52) и нижняя (узлы 37-43, 54-56) схемы управления независимо друг от друга отслеживают новый и старый временные циклы приема. При этом после отсчета времени передачи квитанции счетчиками 57 и 58 счетчики 32 и 41 устанавливаются в состояние "0" и начинается цикл приема по последней переданной квитанции, зафиксированной в регистре 36 или по последней квитанции, прием которой подтвержден (в регистре 43).

На фиг.6 представлен пример реализации функциональной схемы блока синхронизации 12. Блок синхронизации содержит:

первый 12-1, второй 12-2 и третий 12-3 счетчики,

первый 12-4, второй 12-5 и третий 12-6 блоки сравнения,

первый 12-7, второй 12-8 и третий 12-9 триггеры,

первый 12-10, второй 12-11 и третий 12-12 ключи,

элемент ИЛИ 12-13.

Блок синхронизации работает следующим образом.

Номера комбинаций внутреннего кода, поступающие от вычислителя синдрома 3, фиксируются в первом 12-1 счетчике сигналом, поступающим на вход C счетчика с выхода элемента И 17 (фиг.4-1). При этом ранее выделенные номера с первого 12-1 счетчика переписываются во второй 12-2, а со второго - в третий 12-3 счетчик. Таким образом в счетчиках 12-1, 12-2, 12-3 отслеживается три версии фазирования. Через каждые n1 тактов частоты приема Fпрм на выходе этих счетчиков формируется следующий, на единицу больший номер. Блоки сравнения 12-4, 12-5 и 12-6 сравнивают номер, поступающий на вход блока синхронизации с номером, выдаваемым соответственно счетчиками 12-1, 12-2, 12-3. В течение (n1-1) тактов частоты Fпрм счетчики 12-1, 12-2, 12-3 по первому дополнительному выходу выдают сигналы, запрещающие работу блоков сравнения, а каждый n1-ый такт - разрешающий. Если какой-либо увеличивающий номер в счетчиках 12-1, 12-2, 12-3 через число тактов, кратное n1, совпадает с номером комбинации внутреннего кода, поступающим на вход блока синхронизации, то сигналом с блоком сравнения 12-4, 12-5, 12-6 включится какой-либо из триггеров 12-7, 12-8, 12-9, которые в свою очередь выдадут управляющий сигнал на ключи 12-10, 12-11, 12-12 и сформируют сигнал на выходе схемы ИЛИ 12-13, который закроет элемент И 17 (фиг.4-1). После окончания счета источником, номер в котором совпадал с номером вводимым в блок синхронизации, сигнал со второго дополнительного выхода проходит через открытый ключ на выход блока синхронизации как сигнал фазирования, соответствующий приему последнего блока каскадного кода. Кроме того, через открытый ключ проходит также значение старшего разряда номера, выдаваемого по третьему дополнительному выходу счетчика. Этот старший разряд определяет вид системы нумерации комбинаций внутреннего кода ("0" - один вид, "1" - другой вид).

Таким образом, предложенный способ позволяет решить поставленную задачу: повышением пропускной способности канала связи путем повышения вероятности приема информации и уменьшения времени передачи ее.

Повышение вероятности приема обеспечивается за счет передачи в циклах повторения дополнительных символов, используемых на приемной стороне совместно с основными, и достижения благодаря этому большей исправляющей способности каскадного кода, а также за счет формирования методом синхронного накопления из наиболее надежных комбинаций внутреннего кода результирующих блоков каскадного кода перед декодированием последних. Именно совместное использование синхронного накопления и наращивания исправляющей способности кода при повторных передачах обусловили более значительное повышение вероятности приема информации по сравнению с общепринятым независимым приемом блоков [2] или синхронным накоплением [1 стр.77]

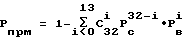

Проведем сравнительный анализ вероятности приема блока каскадного кода для трех вариантов приема:

независимый прием блоков,

синхронное накопление

предлагаемый способ.

Пусть блок каскадного кода состоит из 16 блоков внутреннего кода, 14 из которых являются полезной информацией. Код используется в режиме исправления двух и менее стираний.

Найдем вероятность правильного приема блока при условии двухкратной передачи его (для третьего варианта передаются один раз дополнительные символы, количество которых равно количеству основных).

Для первого варианта

Pпрм = 1-(1-Pкк)2,

где Pкк = P

Для второго варианта

Pпрм = P

где Pв2 = 1-(1-Pв)2

Для предлагаемого способа

где Pв - вероятность приема блока внутреннего кода

Pс - вероятность стирания блока внутреннего кода

Результаты расчетов приведены в таблице.

Эти результаты свидетельствуют о существенном выигрыше предлагаемого способа по сравнению с первым или вторым. Даже если предположить, что существует гипотетический (четвертый) способ, объединяющий первый и второй варианты, то вероятность правильного приема блока по этому способу определится как

Pпрм4 = 1 - (1-Pпрм1) х (1 - Pпрм2)

Результаты расчетов свидетельствуют о преимуществе предлагаемого способа по сравнению с гипотетическим, особенно при ухудшении качества канала связи.

Уменьшение времени передачи информации, помимо того, что оно достигается за счет увеличения вероятности приема блоков, обусловлено сокращением длительности повторных циклов, так как в них передаются не все блоки цикла, а только недоведенные. Таким образом, если на каком-то i-ом цикле обеспечивается вероятность приема блока каскадного кода, Pпрмi то в (i+1)-ом цикле передается (1-Pпрм) часть блоков от общего количества в сообщении. Например, при вероятности приема блока, равной 0,8, длительности следующего цикла сокращается в 1/1-0,8 = 5 раз.

Уменьшение времени передачи информации достигается также за счет совмещения передачи сигнала фазового пуска и информации, благодаря чему уменьшается длительность сообщения. В известных технических решениях сигнал фазового пуска, необходимый для определения начала передачи сообщения, передается как правило перед самим сообщением. По предлагаемому способу начало блока определяется по нумерации комбинаций внутреннего кода, при этом передача номера совмещена с передачей информации. Кроме того, благодаря смене вида нумерации достигается передача сигнала подтверждения приема квитанции без дополнительных затрат пропускной способности канала связи.

Дополнительный технический результат, достигаемый за счет совмещения передачи сигнала фазового пуска и информации заключается в большей скрытности передачи по сравнению с техническими решениями с раздельной передачей фазового пуска и информации, что важно для работы в условиях воздействия преднамеренных помех, когда благодаря выделению сигнала фазового пуска, передаваемому перед информацией имеется возможность подавить первые блоки и все сообщение в целом.

Источники информации.

1. Мартынов Ю. М. Обработка информации в системах передачи данных. М. "Связь" 1969.

2. Заявка на патент N 3423217, H 04 L 1/16, ФРГ. Способ надежной передачи информации между станциями данных.

3. Блейхут Р. Теория и практика кодов, контролирующих ошибки. М. Мир., 1986.

4. Форни Д. Каскадные коды. М. Мир. 1970.

5. Стальнов В. Н. , Личидов Ю. Я. , Волков А.С. Фомин А.Ю. Заявка N 94039139/09 от 13.10.94 г. Устройство кодирования-декодирования информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО СОЕДИНЕНИЯ ДЛЯ ВЕДЕНИЯ СЕКРЕТНЫХ ТЕЛЕФОННЫХ ПЕРЕГОВОРОВ | 1999 |

|

RU2191481C2 |

| СИСТЕМА СЕАНСНОЙ СВЯЗИ | 1992 |

|

RU2027312C1 |

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

| УСТРОЙСТВО ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2001 |

|

RU2206957C2 |

| ДЕКОДЕР | 1993 |

|

RU2088044C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1988 |

|

SU1578825A2 |

| СПОСОБ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2015 |

|

RU2581770C1 |

| УСТРОЙСТВО ДЛЯ ПОРОГОВОГО ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 1993 |

|

RU2081513C1 |

Изобретение относится к технике связи и может быть использовано при разработке систем полудуплексной связи для передачи сообщений, закодированных каскадным кодом, с подтверждением правильного приема путем передачи квитанции. Согласно предлагаемому способу передачу информации осуществляют циклами, состоящими из блоков каскадного кода, в состав служебной части которых введены номер блока и число блоков в цикле. Номера непринятых блоков в цикле сообщаются на передающую сторону в квитанции. Передающая сторона передает к этим блокам дополнительные символы, которые совместно с основными образуют умощненный код, благодаря чему повышается исправляющая способность кода и соответственно увеличивается вероятность приема информации и уменьшается время передачи ее, что является достигаемым техническим результатом. При исчерпании дополнительных символов вновь передают основные, при этом используют принцип синхронного накопления символов из нескольких одинаковых передач, что дополнительно увеличивает вероятность приема информации, образование умощненного блока осуществляется до декодирования, когда служебная часть блока еще неизвестна, для чего на приемной стороне хранятся последняя доведенная квитанция и последняя квитанция, прием которой подтвержден передающей стороной за счет смены вида нумерации комбинаций внутреннего кода по сравнению с нумерацией в предыдущем цикле. При этом, если вид нумерации не изменяется, то используется доведенная квитанция, а если изменяется - то последняя квитанция. Используемая квитанция показывает порядок следования дополнительных символов блоков, прием которых не подтвержден. Номер блока, от которого начинается отсчет блоков, принимаемых в цикле, определяется по моменту фазирования относительно момента окончания приема квитанции. В случае пропуска произвольного количества циклов приема из-за длительных искажений в канале связи отсчитываются оба варианта длительности циклов, что позволяет при фазировании на любом блоке в любом цикле определить номер блока каскадного кода. Передача номеров комбинаций внутреннего кода, используемых также для определения границ блоков, совмещена с передачей самих комбинаций внутреннего кода, благодаря чему устраняется необходимость передачи специального сигнала синхронизации (сигнала фазового пуска) и тем самым достигается уменьшение времени передачи сообщений. 6 ил., 1 табл.

Способ передачи информации в полудуплексных системах связи с подтверждением правильного приема путем передачи в обратном направлении квитанции, по которому информацию передают блоками, содержащими информационную и служебную части, при этом последняя включает в себя номер блока, блоки кодируют каскадным кодом, состоящим из комбинаций внутреннего и внешнего кодов, на приемной стороне блоки декодируют, при положительном результате декодирования блока его выдают получателю, при неприеме квитанции в заданное время повторяют предыдущую передачу, отличающийся тем, что на передающей стороне передачу осуществляют циклами, содержащими произвольное число блоков, при этом в состав служебной части блока вводят информацию о длине цикла, при кодировании блока внешним кодом формируют дополнительные символы и запоминают их вместе с основными, перед передачей блоков в канал связи нумеруют комбинации внутреннего кода каждого блока одним из двух типов системы нумерации, кодируют каждый номер корректирующим ошибки кодом, формируют суммарные кодовые комбинации путем сложения каждой комбинации внутреннего кода с комбинацией соответствующего ей номера, а на приемной стороне на каждом такте частоты приема вычисляют последовательно синдром внутреннего кода и синдром кода нумерации, в момент равенства нулю синдрома кода нумерации фиксируют границы суммарных кодовых комбинаций, определяют тип системы нумерации и номера комбинаций внутреннего кода, по которым фиксируют границы внешнего кода, формируют комбинации внутреннего кода путем вычитания из суммарных комбинаций комбинаций номеров, при декодировании комбинаций внутреннего кода выявляют в них ошибки и по их числу оценивают надежность декодированных комбинаций внутреннего кода, запоминают их вместе с оценкой их надежности, перед декодированием внешнего кода из основных и дополнительных символов предыдущих и текущей передачи формируют умощненный блок, причем в случае повторного приема какой-либо части этого блока используют метод синхронного накопления, при первом положительном результате декодирования блока в сеансе из служебной части его выделяют информацию о длине цикла и по результатам декодирования остальных блоков цикла формируют квитанцию с указанием номеров недекодированных блоков, запоминают ее и выдают на передающую сторону, на которой в соответствии с принимаемой квитанцией передают дополнительные символы недекодированных блоков, при этом нумеруют комбинации внутреннего кода другим типом нумерации, а при неприеме квитанции в заданное время сохраняют то же количество блоков в цикле и тот же тип нумерации комбинаций внутреннего кода, что и в предыдущей передаче, причем при неприеме квитанции на первый цикл сеанса осуществляют повторную передачу этого цикла, а при неприеме квитанции на любой другой цикл передают очередные дополнительные символы к непринятым блокам, зафиксированным в последней принятой квитанции, при обнаружении приемной стороной того же типа нумерации фиксируют факт неприема квитанции передающей стороной и осуществляют прием цикла с номерами блоков, соответствующим номерам непринятых блоков в последней квитанции, прием которой подтвержден, при обнаружении приемной стороной другого типа нумерации фиксируют факт приема квитанции передающей стороной и осуществляют прием текущего цикла с номерами непринятых блоков, зафиксированными в этой квитанции, при этом, как при приеме, так и при неприеме квитанции символы, участвующие в образовании умощненного блока, определяются по номеру цикла, а также по номеру блока, который вычисляется до декодирования блока, причем для блока, на котором произошло фазирование - по моменту приема блока и по квитанции, а для последующих блоков в цикле - по квитанции, при невыделении приемной стороной того или другого типа нумерации отслеживаются номера блоков и длины двух циклов: цикла, на который передавалась последняя квитанция, и цикла, на который прием квитанции подтвержден.

| DE, 3423217 A, 05.05.1986 | |||

| US, 5257270 A, 26.10.1993 | |||

| GB, 2244593 A, 11.11.1992. |

Авторы

Даты

1999-03-20—Публикация

1996-05-06—Подача