Изобретение относится к технике связи и может использоваться при проектировании новых и модернизации существующих систем передачи дискретной информации.

Известны устройства формирования кодов-произведений (см. Р.Морелос-Сарагоса. Искусство помехоустойчивого кодирования. Методы, алгоритмы, применение. М.: Техносфера, 2005, с.183, …, 191; а также Питерсон У. Коды, исправляющие ошибки. / У.Питерсон, Э.Уэлдон; пер. с англ. / Под редакцией Р.Л.Добрушина и С.Н.Самойленко. - М.: Мир, 1976. - 594 с.; а также Форни Д. Каскадные коды. / Д.Форни. - М.: Мир, 1970. - 207 с.).

Кроме того, известны методы использования гиперкодов (см. Hunt A., "Hyper-Codes: High-Performance Low-Complexity Error-Correcting Codes", Master's Thesis, Carleton University, Ottawa, Canada, defended March 25, 1998; a также Hunt A., Crozier S., Falconer D., "Hyper-Codes: High-performance Low-Complexity Error-Correcting Codes", 19-th Biennial Symposium on Communications, Kingston, Ontario, Canada, pp.263-267, May 31 - June 3, 1998).

Наиболее близким устройством такого же назначения является кодер кода-произведения (см. Р.Морелос-Сарагоса. Искусство помехоустойчивого кодирования. Методы, алгоритмы, применение. М.: Техносфера, 2005, с.183), содержащий последовательно соединенные кодер проверки четности k-разрядной комбинации и счетчик распределитель, (k+1) выход которого подключен к одноименным входам регистра вертикальных проверок, при этом выход регистра вертикальных проверок соединен с входом схемы перфорации символа проверки проверок.

К недостаткам работы аналогов, в том числе и прототипа, предлагаемой системы следует отнести негативное влияние избыточности, не только сформированной за счет проверки проверочных разрядов, но и той избыточности, в которой нет необходимости при хорошем состоянии канала связи. Неизменяемые параметры вводимой в код кодером избыточности приводят к увеличению длины кодового вектора и, как следствие, к потерям скорости передачи данных. Для каналов с переменными параметрами подобный подход не пригоден, и, как правило, задача повышения достоверности в таких системах решается с помощью адаптивных кодеков.

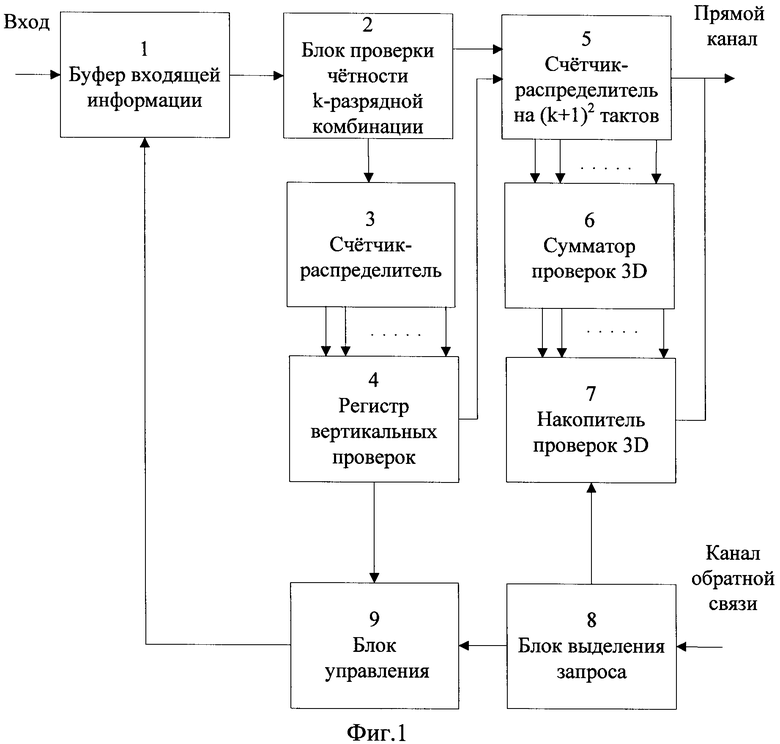

Технический результат - повышение достоверности и скорости передачи информации. Для достижения технического результата в адаптивный кодер гиперкода размерности 3D, содержащий блок проверки четности k-разрядной комбинации, первый выход которого подключен к входу счетчика-распределителя, a (k+1) выход этого счетчика-распределителя подключен к одноименным входам регистра вертикальных проверок, отличающийся тем, что введены буфер входящей информации, счетчик-распределитель на (k+1)2 тактов, сумматор проверок 3D, накопитель проверок 3D, блок выделения запроса и блок управления, при этом выход буфера входящей информации соединен с входом блока проверки четности k-разрядной комбинации, второй выход которого подключен к одноименному входу счетчика-распределителя на (k+1)2 тактов, а первый выход регистра вертикальных проверок подключен к одному входу блока управления, тогда как второй выход регистра вертикальных проверок подключен к первому входу счетчика-распределителя на (k+1)2 тактов и (k+1)2 выходов этого счетчика-распределителя подключены к одноименным входам сумматора проверок 3D и в свою очередь его (k+1)2 выходов подключены к одноименным входам накопителя проверок 3D, выход которого, объединенный с главным выходом счетчика-распределителя на (k+1)2 тактов, подключен к прямому каналу связи, тогда как обратный канал связи подключен к входу блока выделения запроса, первый выход которого соединен с управляющим входом накопителя проверок 3D, а второй выход подключен к другому входу блока управления, выход которого соединен с управляющим входом буфера входящей информации.

Структурная схема адаптивного кодера гиперкода размерности 3D представлена на фиг.1.

Адаптивный кодер гиперкода размерности 3D содержит буфер 1 входящей информации, выход которого подключен к входу блока 2 проверки четности k-разрядной комбинации, при этом первый выход блока 2 проверки четности k-разрядной комбинации соединен с входом счетчика-распределителя 3, а второй выход блока 2 проверки четности k-разрядной комбинации подключен к одноименному входу счетчика-распределителя 5 на (k+1)2 тактов, при этом (k+1) выход счетчика-распределителя 3 подключен к одноименным входам регистра 4 вертикальных проверок, при этом первый выход регистра 4 вертикальных проверок соединен с одним из входов блока 9 управления, тогда как второй выход регистра 4 вертикальных проверок подключен к первому входу счетчика-распределителя 5 на (k+1)2 тактов и (k+1)2 выходов счетчика-распределителя 5 на (k+1)2 тактов подключены к одноименным входам сумматора 6 проверок 3D, при этом в свою очередь (k+1)2 выходов сумматора 6 проверок 3D подключены к одноименным входам накопителя 7 проверок 3D, выход которого, объединенный с главным выходом счетчика-распределителя 5 на (k+1)2 тактов, подключен к прямому каналу связи, тогда как обратный канал связи подключен к входу блока 8 выделения запроса, первый вход которого соединен с управляющим входом накопителя 7 проверок 3D, а второй выход подключен к другому входу блока 9 управления, выход которого соединен с управляющим входом буфера 1 входящей информации.

Назначения отдельных блоков адаптивного кодера и их совместная работа рассматриваются на примере обработки комбинаций с k=3.

Буфер 1 входящей информации предназначен для регулирования потока последовательности информационных символов и служит для обеспечения согласованной работы элементов адаптивного кодера. Вход этого блока является информационным входом устройства, а управляющий вход буфера 1 входящей информации обеспечивает регулирование входящего информационного потока символов. Управляющий вход буфера 1 входящей информации подключен к выходу блока 9 управления, при этом буфера 1 входящей информации соединен с входом блока 2 проверки четности k-разрядной комбинации. Буфер 1 входящей информации имеет три режима работы. В первом режиме буфер 1 входящей информации принимает поток данных от источника информации, выделяет k-разрядные комбинации информационных символов и передает их в блок 2 проверки четности k-разрядной комбинации. Во втором режиме буфер 1 входящей информации осуществляет задержку и накопление потока данных от источника информации на время, равное k тактам. В третьем режиме буфер 1 входящей информации задерживает и накапливает входящий поток информации на время, равное (k+1)2 тактов.

Блок 2 проверки четности k-разрядной комбинации предназначен для выполнения проверки четности в группе k двоичных символов, поступающих с выхода буфера 1 входящей информации. После выполнения процедуры проверки четности комбинация в (k+1) символ в последовательном коде поступает одновременно на первый и второй выходы блока 2 проверки четности k-разрядной комбинации. При этом первый выход подключен к входу счетчика-распределителя 3, а второй выход блока 2 проверки четности k-разрядной комбинации подключен ко второму входу счетчика-распределителя 5 на (k+1)2 тактов. Информация, передаваемая через второй выход блока 2 проверки четности k-разрядной комбинации без изменений и задержек, передается через блок 5 в прямой канал связи.

Счетчик-распределитель 3 предназначен для распределения значений (k+1) разрядной комбинации по (k+1) сумматорам, при передаче ровно (k+1)-й комбинаций сумматоры определяют четность информационных и проверочных символов на одноименных позициях этих комбинаций. Состояние сумматоров после обработки k комбинаций соответствует проверкам на четность по вертикали в традиционной системе двух кодов произведений. Для получения подобных проверок счетчик-распределитель 3 связан с регистром 4 вертикальных проверок ровно (k+1) выходами.

Регистр 4 вертикальных проверок предназначен для фиксации через каждые k×(k+1) тактов работы адаптивного кодера проверок четности по вертикали. Этот блок имеет 2 выхода. Первый выход предназначен для передачи сигнала управления в блок 9 управления, который блокирует выход буфера 1 входящей информации на (k+1) такт (режим 2). За время блокировки буфера 1 входящей информации регистр 4 вертикальных проверок через второй выход и первый вход счетчика-распределителя 5 на (k+1)2 тактов передает проверочные символы по вертикали в прямой канал связи.

Счетчик-распределитель 5 на (k+1)2 тактов предназначен для трансляции (k+1)2 разрядной комбинации, получаемой с первого или со второго входов через главный выход в прямой канал связи, а также для распределения значений этой последовательности по (k+1)2 сумматорам. При передаче (k+1) комбинаций сумматоры определяют четность информационных и проверочных символов на одноименных позициях в этих комбинациях. Состояние сумматоров после обработки k комбинаций соответствует проверкам на четность размерности 3D в системе гиперкода. Для получения подобных проверок счетчик-распределитель 5 на (k+1)2 тактов связан с сумматором 6 проверок 3D (k+1)2 параллельными выходами.

Сумматор 6 проверок 3D предназначен для суммирования и фиксации по завершении k×(k+1)2 тактов работы кодера окончательного итога проверок четности размерности 3D. Этот блок имеет (k+1)2 выходов, занумерованных от 1 до (k+1)2, подключенных к одноименным входам накопителя 7 проверок 3D. После сброса информации из сумматора 6 проверок 3D в накопитель 7 проверок 3D сумматор 6 проверок 3D готов к обработке очередной последовательности битов.

Накопитель 7 проверок 3D предназначен для хранения символов проверки размерности 3D и передачи их последовательным кодом в прямой канал связи только в случае поступления запроса по каналу обратной связи. Накопитель 7 проверок 3D имеет (k+1)2 входов и один управляющий вход. Управляющий вход подключен к первому выходу блока 8 выделения запроса. Выход накопителя 7 проверок 3D объединен с главным выходом счетчика-распределителя 5 на (k+1)2 тактов и подключен к прямому каналу связи. Если через установленное число тактов работы кодера после передачи кодового слова запроса на передачу дополнительной избыточности не поступило, накопитель 7 проверок 3D обнуляет накопитель проверок 3D, относящихся к переданному кодовому слову. Число установленных тактов работы кодера является переменным и зависит от параметров обратного канала связи. Процесс обнуления накопителя носит циклический характер.

Блок 8 выделения запроса предназначен для выделения комбинации запроса из канала обратной связи и управления передачей дополнительной избыточности из накопителя 7 проверок 3D в прямой канал связи. Данный блок имеет два выхода. Второй выход предназначен для передачи сигнала управления в блок 9 управления, который блокирует выход буфера 1 входящей информации на (k+1)2 такт. В это же время управляющая команда передается по первому выходу на управляющий вход накопителя 7 проверки 3D, который за время блокировки буфера 1 входящей информации передает проверочные символы размерности 3D из накопителя 7 проверки 3D в прямой канал связи.

Блок 9 управления предназначен для управления последовательностями передаваемой информации. Данный блок имеет выход, подключенный к управляющему входу буфера 1 входящей информации. Блок 9 управления имеет два входа. Один из них подключен к первому выходу регистра 4 вертикальных проверок. При поступлении команды с этого выхода блок 9 управления блокирует выход буфера 1 входящей информации на (k+1) такт. Другой вход блока 9 управления подключен к второму выходу блока 8 выделения запроса. При поступлении управляющей команды с этого входа блок 9 управления блокирует выход буфера 1 входящей информации на (k+1)2 такт.

Работа адаптивного кодера гиперкода размерности 3D рассматривается на примере передачи информации при k=3.

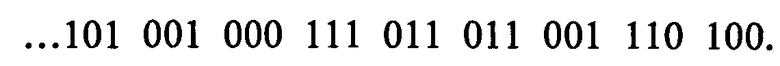

На вход буфера 1 входящей информации от источника информации поступает некоторая последовательность двоичных символов вида:

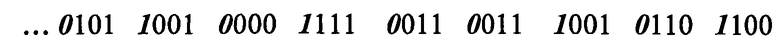

Пробелы между группами двоичных символов приведены только для удобства анализа работы последующих блоков кодера. Первоначально буфер 1 входящей информации 1 работает в первом режиме. Тогда с выхода буфера 1 входящей информации указанная последовательность посимвольно передается на вход блока 2 проверки четности А-разрядной комбинации, где при поступлении k символов исходной последовательности формируется (k+1) разрядов кода с проверкой четности по горизонтали. В таком случае входная последовательность при записи проверочного разряда слева (показаны жирным курсивом) приобретает вид:

Полученные таким образом символы последовательным кодом через первый выход блока 2 проверки четности А-разрядной комбинации поступают на вход счетчика-распределителя 3 и одновременно через второй выход блока 2 проверки четности А-разрядной комбинации и второй вход счетчика-распределителя 5 на (k+1)2 тактов в прямой канал связи.

Счетчик-распределитель 3 предназначен для распределения значений (k+1) разрядной комбинации по (k+1) сумматорам. При завершении передачи k-й комбинаций сумматоры определяют четность информационных и проверочных символов на одноименных позициях в этих комбинациях. Состояние сумматоров после обработки k комбинаций соответствует проверкам на четность по вертикали в традиционной системе кодов произведений. Для получения подобных проверок счетчик-распределитель 3 связан с регистром 4 вертикальных проверок ровно (k+1) выходами.

Регистр 4 вертикальных проверок предназначен для фиксации через k×(k+1) тактов работы кодера проверок четности по вертикали. При обработке k комбинаций в регистре вертикальных проверок фиксируется последовательность проверок четности по вертикали для первых k переданных комбинаций.

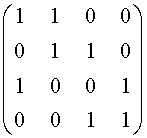

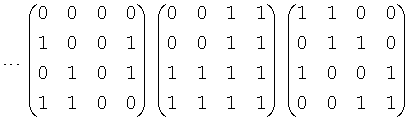

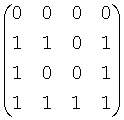

При этом формирование проверок четности по вертикали на основе первых k×(k+1) бит можно представить массивом данных вида:

Указанный массив в регистре 4 вертикальных проверок не формируется. В этом блоке образуется только нижняя строка матрицы: 0011. Для передачи этой строки в канал связи через второй выход регистра 4 вертикальных проверок необходимо задержать входящий поток информационных бит ровно на (k+1) такт. С этой целью через каждые k×(k+1) тактов работы кодера из регистра 4 вертикальных проверок на его первый выход передается сигнала управления на один вход блок 9 управления, который переводит буфер 1 входящей информации во второй режим работы. За время блокировки буфера 1 входящей информации, регистр 4 вертикальных проверок через второй выход и первый вход счетчика-распределителя 5 на (k+1)2 тактов передает проверочные символы по вертикали (в нашем примере 0011) в прямой канал связи.

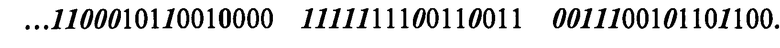

Таким образом, поочередно через второй и первый входы счетчика-распределителя 5 на (k+1)2 тактов и его главный выход в прямой канал связи транслируется последовательность:

Разрывы между группами символов показаны только для удобства восприятия текста и в реальной системе они отсутствуют. Эту последовательность образно можно представить в виде трех массивов (матриц), каждый из которых назовем слоем гиперкода размерности 3D:

Продвигаясь по счетчику-распределителю 5 на (k+1)2 тактов, передаваемая последовательность подвергается анализу, в ходе которого символы из каждого слоя с номерами xij оцениваются сумматором 6 проверок 3D. Также в счетчике на (k+1)2 тактов символы новой последовательности распределяются по (k+1)2 сумматорам. При передаче k слоев сумматоры определяют четность информационных и проверочных символов на одноименных позициях в этих комбинациях. Состояние сумматоров после обработки k слоев соответствует проверкам на четность 3D в системе гиперкода. Для получения подобных проверок счетчик-распределитель 5 на (k+1)2 тактов связан с сумматором 6 проверок 3D (k+1)2 выходами.

Сумматор 6 проверок 3D предназначен для фиксации через k×(k+1)2 тактов проверок четности 3D. Сумматор 6 проверок 3D имеет (k+1)2 выходов, занумерованных от 1 до (k+1)2 и подключенных к входам накопителя 7 проверок 3D. Проверка четности 3D представляет собой (k+1) слой гиперкода, который можно представить в виде матрицы:

Этот слой не передается в канал связи без специальной команды.

Накопитель 7 проверок 3D предназначен для сохранения символов проверки 3D и передачи их последовательным кодом в прямой канал связи только при поступлении запроса. Данный блок имеет (k+1)2 входов и 1 управляющий вход. Управляющий вход подключен к первому выходу блока 8 выделения запроса. Выход накопителя 7 проверок 3D объединен с главным выходом счетчика-распределителя 5 на (k+1)2 тактов и подключен к прямому каналу связи. При поступлении сигнала запроса из блока 8 выделения запроса в накопитель 7 проверок 3D через второй выход блока выделения запроса 8 и другой вход блока 9 управления подается команда в буфер 1 входящей информации о переводе кодера в режим три.

Таким образом, основная скорость представленного в примере кода R=0,56. При необходимости передачи добавленной по запросу избыточности скорость кода принимает значение R=0,42. Представленная конструкция кодера способствует поддержанию синхронизации кодера и декодера системы обмена данными, поскольку добавляемая избыточность в точности соответствует одному слою данных и требует специальных указателей для выделения добавленной избыточности.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР ПРОИЗВЕДЕНИЯ КОДОВ РАЗМЕРНОСТИ 3D С ЗАПРОСАМИ | 2014 |

|

RU2562415C1 |

| АДАПТИВНЫЙ ДЕКОДЕР ПРОИЗВЕДЕНИЯ КОДОВ РАЗМЕРНОСТИ 3D | 2012 |

|

RU2500073C1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| Устройство для декодирования корректирующих кодов | 1987 |

|

SU1441487A1 |

| Кодер | 1990 |

|

SU1783623A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

| Устройство для определения местоположения ошибок в строке матричного накопителя | 1980 |

|

SU896691A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

Изобретение относится к технике связи, а именно к системам помехоустойчивого кодирования с параметрической адаптацией. Техническим результатом является повышение достоверности и скорости передачи информации. Технический результат достигается тем, что в адаптивный кодер гиперкода размерности 3D, содержащий блок проверки четности k-разрядной комбинации, первый выход которого подключен к входу счетчика-распределителя, а (k+1) выход этого счетчика-распределителя подключен к одноименным входам регистра вертикальных проверок, дополнительно введены буфер входящей информации, счетчик-распределитель на (k+1)2 тактов, сумматор проверок 3D, накопитель проверок 3D, блок выделения запроса и блок управления. В случае хороших условий передачи избыточность, относящаяся к проверкам 3D, не передается и хранится в памяти кодера. При поступлении запроса от приемника на введение дополнительной избыточности проверки 3D доставляются приемнику для декодирования ранее принятого кодового вектора в условиях повышения корректирующей способности кода. 1 ил.

Адаптивный кодер гиперкода размерности 3D, содержащий блок проверки четности k-разрядной комбинации, первый выход которого подключен к входу счетчика-распределителя, а (k+1) выход этого счетчика-распределителя подключен к одноименным входам регистра вертикальных проверок, отличающийся тем, что введены буфер входящей информации, счетчик-распределитель на (k+1)2 тактов, сумматор проверок 3D, накопитель проверок 3D, блок выделения запроса и блок управления, при этом выход буфера входящей информации соединен с входом блока проверки четности k-разрядной комбинации, второй выход которого подключен к одноименному входу счетчика-распределителя на (k+1)2 тактов, а первый выход регистра вертикальных проверок подключен к одному входу блока управления, тогда как второй выход регистра вертикальных проверок подключен к первому входу счетчика-распределителя на (k+1)2 тактов, и (k+1)2 выходов этого счетчика-распределителя подключены к одноименным входам сумматора проверок 3D, и, в свою очередь, его (k+1)2 выходов подключены к одноименным входам накопителя проверок 3D, выход которого, объединенный с главным выходом счетчика-распределителя на (k+1)2 тактов, подключен к прямому каналу связи, тогда как обратный канал связи подключен к входу блока выделения запроса, первый выход которого соединен с управляющим входом накопителя проверок 3D, а второй выход подключен к другому входу блока управления, выход которого соединен с управляющим входом буфера входящей информации.

| RU 2008122352 A, 20.12.2009 | |||

| КОДИРОВАНИЕ КОДОВ ПЕРЕМЕННОЙ ДЛИНЫ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ ПАМЯТИ | 2007 |

|

RU2426227C2 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| EP 1443725 A1, 04.08.2004 | |||

| FR 2850500 A1, 30.07.2004 | |||

| US 6154489 A, 28.11.2000 | |||

| US 5369652 A, 29.11.1994. | |||

Авторы

Даты

2013-04-27—Публикация

2011-11-18—Подача