1. Область техники, к которой относится изобретение

Изобретение относится к области устройств цифровой обработки данных, предназначенных для вычисления значений функций приближенными методами, в особенности экстраполяцией. Изобретение может быть использовано в системах различного назначения, выполняющих в процессе работы операцию предсказания новых значений изменяющихся во времени математических функций по имеющимся ранее известным их значениям.

2. Уровень техники

В настоящее время известно большое количество разнообразных устройств, предназначенных для предсказания значений изменяющихся во времени случайных величин по их ранее известным значениям.

Среди устройств цифровой обработки данных, выполняющих указанную задачу, известен такой аналог предлагаемого устройства, как «Цифровое прогнозирующее устройство» (Патент РФ RU 2477887, от 27.10.2011, МПК G06G 7/30), в состав которого, помимо прочих элементов, входят блок сглаживания, блок прогноза и узел управления динамикой прогноза, причем блок сглаживания содержит сумматор, первый и второй реверсивный счетчики, а также ряд субблоков, содержащих регистры, сумматоры, вычитатели, регистр сдвига, а также различные комбинационные логические элементы, блок прогноза содержит, среди прочих элементов, первый и второй вычитатели, сумматор и ряд субблоков, также имеющих в своем составе различные комбинационные и последовательностные элементы.

Очевидным недостатком столь сложной конструкции является ее аппаратная избыточность, а также неизбежные для нее низкая скорость и надежность работы.

Устройством, близким к предлагаемому в достаточной степени, чтобы быть использованным в качестве прототипа, является устройство «Экстраполятор» (патент СССР SU 1529245, МПК G06F 15/353). Указанное устройство содержит линию задержки, первый, второй, третий и четвертый регистры, первый, второй, третий и четвертый сумматоры, первый и второй умножители, а также преобразователь «код-частота» и счетчик с возможностью переключения между инкрементирующим и декрементирующим режимами счета по сигналу внешнего управления.

Недостатками данного устройства является значительная задержка вычисления прогнозируемого значения, связанная с тем, что корректировка спрогнозированного значения осуществляется путем инкрементации или декрементации счетчика, осуществляемой по единице за один такт сигнала тактовой частоты работы устройства. Кроме того, размещение указанного счетчика в выходном каскаде устройства приводит к появлению на выходе устройства сигналов, соответствующих нерелевантным промежуточным результатам расчета прогнозируемых значений.

3. Раскрытие изобретения

Технический результат, достигаемый при осуществлении предлагаемого изобретения, заключается в ускорении вычисления прогнозируемого значения, исключении вероятности возникновения на выходе устройства сигналов, соответствующих нерелевантным результатам расчета прогнозируемых значений, а также приобретении свойства многоскоростной обработки данных, при которой скорость поступления значений сигнала, подлежащего прогнозированию, может существенно отличаться от скорости следования импульсов сигнала тактовой частоты работы устройства, а также от скорости считывания прогнозируемых значений сигнала.

Достижение указанного технического результата осуществляется за счет того, что предлагаемое устройство содержит первый, второй и третий элементы памяти, первый и второй узлы вычитания, первый и второй узлы суммирования, первый и второй масштабирующий блоки, а также интегратор, причем вход первого элемента памяти подключен ко входу предлагаемого устройства, выход первого элемента памяти подключен ко входу второго элемента памяти, входам вычитаемого первого и второго узлов вычитания, а также первому входу второго узла суммирования, выход упомянутого второго элемента памяти подключен ко входу вычитателя первого узла вычитания, выход которого, соответственно, подключен ко входу первого масштабирующего блока, сигнал с выхода которого подается на первый вход первого узла суммирования, сигнал с выхода первого узла суммирования подается на вход интегратора, в то время как сигнал с выхода интегратора подается на второй вход второго узла суммирования, сигнал с выхода которого подается на выход предлагаемого устройства, а также на вход третьего элемента памяти, выход которого подключен ко входу вычитателя вышеупомянутого второго узла вычитания, сигнал с выхода которого подается вход второго масштабирующего блока, сигнал с выхода которого подается на второй вход упомянутого первого узла суммирования.

Первое и второе запоминающие устройства содержат последнее и предпоследнее полученные значения программируемого сигнала, αn и αn-1 соответственно. На выходе первого узла вычитания формируется значение разности, которая, будучи поделенной в первом масштабирующем блоке на значение периода следования значений прогнозируемого сигнала Т, представляет собой скорость изменения значения прогнозируемого сигнала на предыдущем такте.

Параллельно с этим осуществляется вычисление значения ошибки экстраполяции путем вычисления с помощью упомянутого второго узла вычитания разности между значением  , спрогнозированным на предыдущей итерации работы предлагаемого устройства и фактическим значением прогнозируемого сигнала αn, полученным на текущей итерации. Указанное значение разности умножается на μ/Т с помощью второго масштабирующего блока, где μ - весовой коэффициент ошибки экстраполяции. Причем допускается варьирование значения указанного весового коэффициента ошибки экстраполяции таким образом, чтобы осуществлять подстройку работы предлагаемого цифрового многоскоростного экстраполятора непосредственно в процессе функционирования.

, спрогнозированным на предыдущей итерации работы предлагаемого устройства и фактическим значением прогнозируемого сигнала αn, полученным на текущей итерации. Указанное значение разности умножается на μ/Т с помощью второго масштабирующего блока, где μ - весовой коэффициент ошибки экстраполяции. Причем допускается варьирование значения указанного весового коэффициента ошибки экстраполяции таким образом, чтобы осуществлять подстройку работы предлагаемого цифрового многоскоростного экстраполятора непосредственно в процессе функционирования.

Указанные значения ошибки экстраполяции и скорости изменения прогнозируемого сигнала суммируются с помощью первого сумматора. Полученное значение рассматривается как значение скорости изменения прогнозируемого сигнала, интегрируемое по времени с помощью интегратора, после чего полученное интегрированное значение суммируется с последним полученным фактическим значением прогнозируемого сигнала. Таким образом формируется прогнозный номинал следующего значения прогнозируемого сигнала, подаваемый на выход предлагаемого устройства.

Математическое описание работы предлагаемого устройства можно представить в виде формулы 1.

где: τ - временной шаг работы экстраполятора (τ<<Т).

4. Краткое описание чертежей

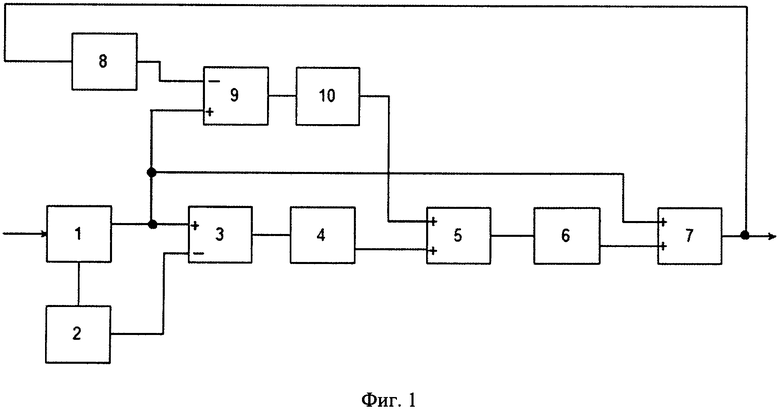

Изобретение поясняется чертежами где:

Фиг. 1. - Структура предлагаемого многоскоростного цифрового экстраполятора.

На фигуре представлены:

1 - первый регистр;

2 - второй регистр;

3 - первый вычитатель;

4 - первый масштабирующий блок;

5 - первый сумматор;

6 - интегратор;

7 - второй сумматор;

8 - третий регистр;

9 - второй вычитатель;

10 - второй масштабирующий блок.

5. Осуществление изобретения

Предлагаемое изобретение может быть осуществлено различными способами, как аппаратными, так и программными или смешанными. Рассмотрим способ осуществления устройства в виде цифровой схемы на основе цифровых логических элементов различной степени сложности. При таком способе осуществления функции элементов памяти могут быть осуществлены путем использования регистров, функции узлов вычитания и суммирования могут быть осуществлены цифровыми вычитателями и сумматорами, соответственно, функции интегратора могут быть осуществлены устройством суммирования с накоплением, а функции масштабирования могут быть осуществлены цифровым устройством, реализующим операцию деления на значение периода времени считывания значений прогнозируемого сигнала.

Структурная схема предлагаемого устройства при таком варианте осуществления представлена на фиг. 1.

Работа предлагаемого устройства осуществляется следующим образом. При поступлении очередного значения прогнозируемого сигнала, указанное значение фиксируется на первом регистре 1, одновременно с этим, значение, ранее хранившееся в указанном первом регистре 1, фиксируется на втором регистре 2. На выходе первого вычитателя 3 формируется значение разности указанных значений, которое подается на вход первого масштабирующего блока 4 вычисляющего на его основе значение скорости изменения значения прогнозируемого сигнала.

Параллельно с этим осуществляется вычисление значения ошибки экстраполяции для чего на положительный вход второго вычитателя 9 подается упомянутое очередное фактическое значение прогнозируемого сигнала, а на отрицательный вход второго вычитателя 9 - значение прогнозируемого сигнала спрогнозированное на предыдущей итерации работы предлагаемого устройства, сохраненное с помощью третьего регистра 8.

Полученное на выходе второго вычитателя 9 значение разности умножается на весовой коэффициент ошибки экстраполяции и масштабируется по времени с помощью второго масштабирующего блока 10.

Сигналы с выходов первого масштабирующего блока 4 и второго масштабирующего блока 10 подаются на вход первого сумматора 5, сигнал с выхода указанного первого сумматора 5 - на вход интегратора 6.

Значение с выхода указанного интегратора 6 подается на первый вход второго сумматора 7, на второй вход которого подается последнее полученное фактическое значение прогнозируемого сигнала, сохраненное с помощью первого регистра 1.

Сигнал или сигналы, кодирующие вычисленную с помощью второго сумматора 7 сумму, подаются на выход предлагаемого устройства и одновременно фиксируются на третьем регистре 8.

Все вышеупомянутые значения могут передаваться в виде совокупности электрических сигналов (при параллельном кодировании цифровых значений), либо одного электрического сигнала (при последовательном кодировании цифровых значений).

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1986 |

|

SU1478978A1 |

| ПРОГНОЗАТОР | 1996 |

|

RU2113006C1 |

| Экстраполятор | 1979 |

|

SU842855A1 |

| Устройство для прогнозирования длительности производственных операций | 1990 |

|

SU1781685A1 |

| Устройство для прогноза мощности потребления энергосистем | 1982 |

|

SU1070591A1 |

| Экстраполятор | 1987 |

|

SU1439620A1 |

| ТЕЛЕВИЗИОННЫЙ АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1988 |

|

SU1623536A1 |

| Экстраполятор | 1974 |

|

SU531167A1 |

| Ступенчато-линейный экстраполятор | 1977 |

|

SU739559A1 |

| Цифровой экстраполятор | 1990 |

|

SU1772805A1 |

Изобретение относится к области цифровой техники для обработки данных, предназначенных для вычисления значений функций приближенными методами, в особенности экстраполяцией. Технический результат заключается в ускорении вычисления прогнозируемого значения, исключении вероятности возникновения на выходе устройства сигналов, соответствующих нерелевантным результатам расчета прогнозируемых значений. Технический результат достигается за счет многоскоростного цифрового экстраполятора, который содержит первый, второй и третий элементы памяти, первый и второй узлы вычитания, первый и второй узлы суммирования, первый и второй масштабирующий блоки, а также интегратор, причем масштабирующий блок осуществляет, помимо операции масштабирования, операцию умножения подаваемого на вход значения на весовой коэффициент ошибки экстраполяции. 3 з.п. ф-лы, 1 ил.

1. Многоскоростной цифровой экстраполятор, содержащий первый, второй и третий элементы памяти, первый и второй узлы вычитания, первый и второй узлы суммирования, отличающийся тем, что содержит первый и второй масштабирующий блоки, а также интегратор, причем выход первого узла вычитания подключен ко входу первого масштабирующего блока, сигнал с выхода которого подается на первый вход первого узла суммирования, сигнал с выхода первого узла суммирования подается на вход интегратора, в то время как сигнал с выхода интегратора подается на второй вход второго узла суммирования, сигнал с выхода второго узла вычитания подается на вход второго масштабирующего блока, сигнал с выхода которого подается на второй вход упомянутого первого узла суммирования, кроме того второй масштабирующий блок осуществляет, помимо операции масштабирования, операцию умножения подаваемого на вход значения на весовой коэффициент ошибки экстраполяции.

2. Многоскоростной цифровой экстраполятор по п. 1, отличающийся тем, что упомянутая операция масштабирования осуществляется путем математического деления получаемых на входе значений на величину периода получения значений прогнозируемого сигнала, причем указанная величина хранится в запоминающих устройствах первого и второго масштабирующих блоков с возможностью варьирования его номинала в процессе работы устройства.

3. Многоскоростной цифровой экстраполятор по п. 1, отличающийся тем, что упомянутое значение весового коэффициента ошибки экстраполяции хранится в запоминающем устройстве второго масштабирующего блока с возможностью варьирования его номинала в процессе работы устройства.

4. Многоскоростной цифровой экстраполятор по п. 1, отличающийся тем, что все значения, передаваемые между структурными элементами цифрового многоскоростного экстраполятора, передаются либо в виде совокупности электрических сигналов (при параллельном кодировании цифровых значений), либо одного электрического сигнала (при последовательном кодировании цифровых значений).

| US 5689449 A, 18.11.1997 | |||

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| US 5841681 A, 24.11.1998 | |||

| Цифровой экстраполятор | 1978 |

|

SU694865A1 |

Авторы

Даты

2019-04-04—Публикация

2018-05-18—Подача