Изобретение относится к микроэлектронике и может быть использовано в интегральных схемах запоминающих устройств с произвольной выборкой на МДП-транзисторах.

Цель изобретения - повышение быстродействия и надежности устройства.

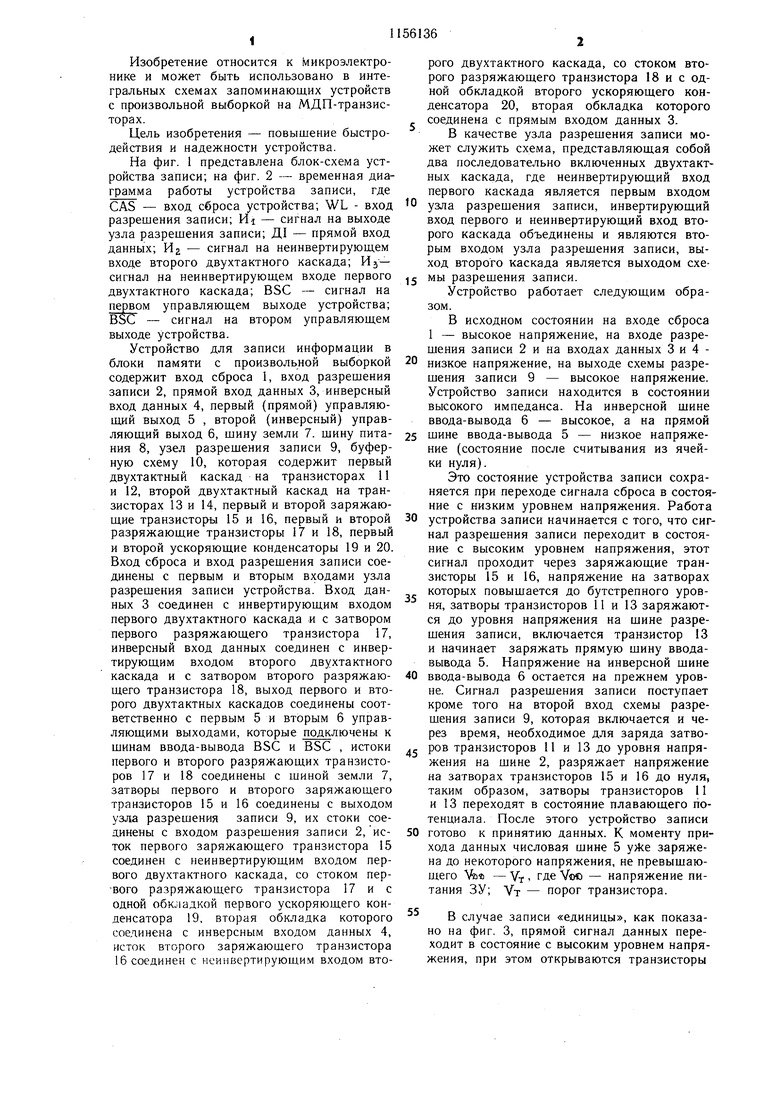

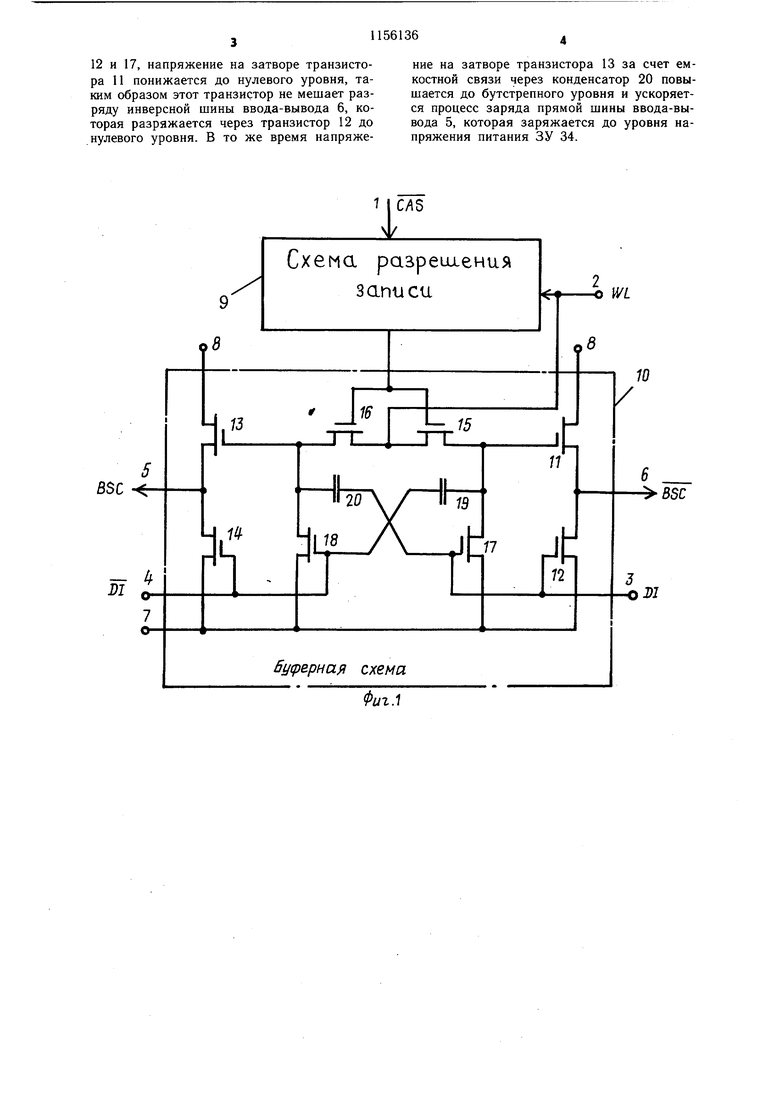

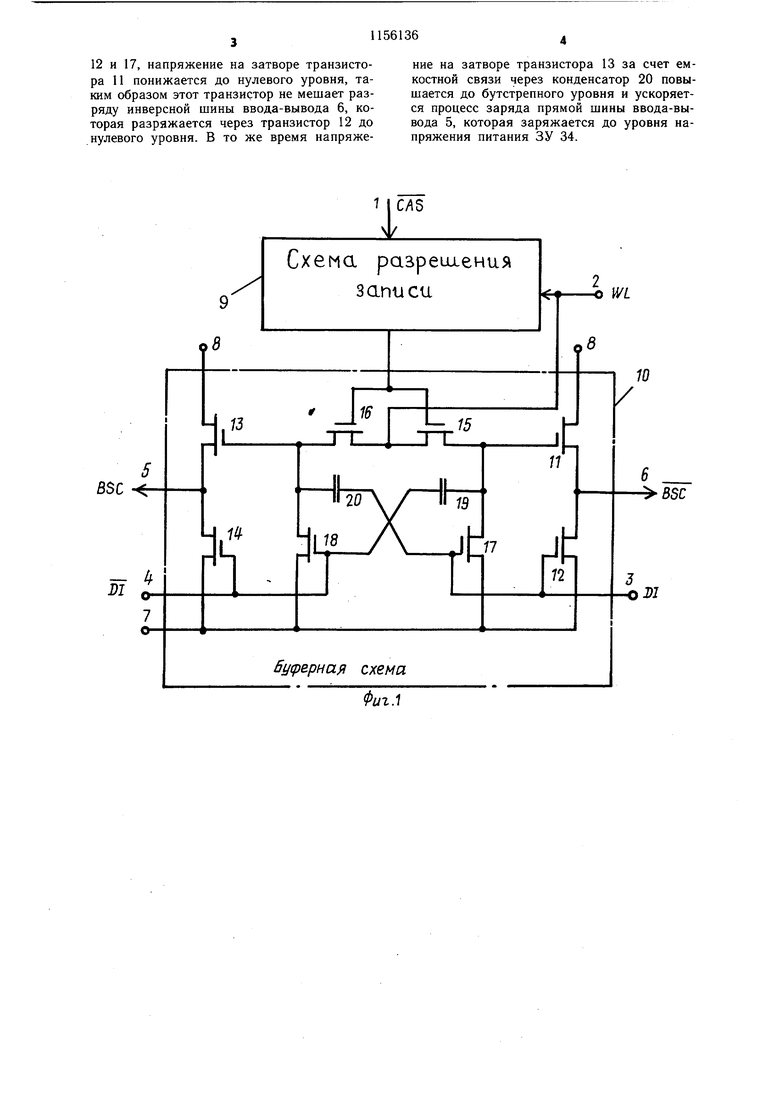

На фиг. 1 представлена блок-схема устройства записи; на фиг. 2 - временная диаграмма работы устройства записи, где CAS - вход сброса устройства; WL - вход разрешения записи; HI - сигнал на выходе узла разрешения записи; Д1 - прямой вход данных; Иг - сигнал на неинвертируюш.ем входе второго двухтактного каскада; Из- сигнал на неинвертируюш,ем входе первого двухтактного каскада; BSC - сигнал на первом управляюш,ем выходе устройства; BSC - сигнал на втором управляющем выходе устройства.

Устройство для записи информации в блоки памяти с произвольной выборкой содержит вход сброса 1, вход разрешения записи 2, прямой вход данных 3, инверсный вход данных 4, первый (прямой) управляющий выход 5 , второй (инверсный) управляющий выход 6, шину земли 7. щину питания 8, узел разрешения записи 9, буферную схему 10, которая содержит первый двухтактный каскад на транзисторах 11 и 12, второй двухтактный каскад на транзисторах 13 и 14, первый и второй заряжающие транзисторы 15 и 16, первый и второй разряжаюшие транзисторы 17 и 18, первый и второй ускоряющие конденсаторы 19 и 20. Вход сброса и вход разрешения записи соединены с первым и вторым входами узла разрешения записи устройства. Вход данных 3 соединен с инвертирующим входом первого двухтактного каскада и с затвором первого разряжающего транзистора 17, инверсный вход данных соединен с инвертирующим входом второго двухтактного каскада и с затвором второго разряжающего транзистора 18, выход первого и второго двухтактных каскадов соединены соответственно с первым 5 и вторым 6 управляющими выходами, которые подключены к шинам ввода-вывода BSC и BSC , истоки первого и второго разряжающих транзисторов 17 и 18 соединены с шиной земли 7, затворы первого и второго заряжающего транзисторов 15 и 16 соединены с выходом узла разрешения записи 9, их стоки соединены с входом разрешения записи 2, исток первого заряжающего транзистора 15 соединен с неинвертирующим входом первого двухтактного каскада, со стоком первого разряжающего транзистора 17 и с одной обкладкой первого ускоряющего конденсатора 19, вторая обкладка которого соединена с инверсным входо.м данных 4, исток второго заряжающего транзистора 16 соединен с ноинвертирующим входом второго двухтактного каскада, со стоком второго разряжающего транзистора 18 и с одной обкладкой второго ускоряющего конденсатора 20, вторая обкладка которого соединена с прямым входом данных 3.

В качестве узла разрешения записи может служить схема, представляющая собой два последовательно включенных двухтактных каскада, где неинвертирующий вход первого каскада является первым входом

узла разрешения записи, инвертирующий вход первого и неинвертирующий вход второго каскада объединены и являются вторым входом узла разрешения записи, выход второго каскада является выходом схе5 мы разрешения записи.

Устройство работает следующим образом.

В исходном состоянии на входе сброса 1 - высокое напряжение, на входе разрещения записи 2 и на входах данных 3 и 4 0низкое напряжение, на выходе схемы разрешения записи 9 - высокое напряжение. Устройство записи находится в состоянии высокого импеданса. На инверсной шине ввода-вывода 6 - высокое, а на прямой

5 шине ввода-вывода 5 - низкое напряжение (состояние после считывания из ячейки нуля).

Это состояние устройства записи сохраняется при переходе сигнала сброса в состояние с низким уровнем напряжения. Работа

0 устройства записи начинается с того, что сигнал разрешения записи переходит в состояние с высоким уровнем напряжения, этот сигнал проходит через заряжающие транзисторы 15 и 16, напряжение на затворах которых повышается до бутстрепного уров5ня, затворы транзисторов 11 и 13 заряжаются до уровня напряжения на шине разрешения записи, включается транзистор 13 и начинает заряжать прямую шину вводавывода 5. Напряжение на инверсной шине

0 ввода-вывода 6 остается на прежнем уровне. Сигнал разрешения записи поступает кроме того на второй вход схемы разрешения записи 9, которая включается и через время, необходимое для заряда затвос ров транзисторов 11 и 13 до уровня напряжения на щине 2, разряжает напряжение на затворах транзисторов 15 и 16 до нуля, таким образом, затворы транзисторов 11 и 13 переходят в состояние плавающего потенциала. После этого устройство записи

0 готово к принятию данных. К моменту прихода данных числовая шине 5 уЖе заряжена до некоторого напряжения, не превышающего - VT . где Voo - напряжение питания ЗУ; VT - порог транзистора.

В случае записи «единицы, как показано на фиг. 3, прямой сигнал данных переходит в состояние с высоким уровнем напряжения, при этом открываются транзисторы

12 и 17, напряжение на затворе транзистора И понижается до нулевого уровня, таким образом этот транзистор не мешает разряду инверсной шины ввода-вывода 6, которая разряжается через транзистор 12 до нулевого уровня. В то же время напряжение на затворе транзистора 13 за счет емкостной связи через конденсатор 20 повышается до бутстрепного уровня и ускоряется процесс заряда прямой шины ввода-вывода 5, которая заряжается до уровня напряжения питания ЗУ 34.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Дешифратор | 1989 |

|

SU1644222A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

| Формирователь импульсов | 1985 |

|

SU1374417A1 |

| Формирователь импульсов | 1980 |

|

SU919062A1 |

УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В БЛОКИ ПАМЯТИ С ПРОИЗВОЛЬНОЙ ВЫБОРКОЙ, содержащее узел расширения записи и буферный узел, состоящий из двух двухтактных каскадов на МДП-транзисторах обогащенного типа, первый вход узла разрешения записи является входом сброса устройства, второй вход является входом разрешения записи, инвертирующий вход первого двухтактного буферного каскада является прямым входом устройства, инвертирующий вход второго двухтактного буферного каскада является инверсным входом устройства, выходы двухтактных буферных каскадов являются первым и вторым управляющими выходами устройства, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит элементы заряда на транзисторах, элементы разряда на транзисторах и форсирующие элементы на конденсаторах, причем затворы транзисторов элементов заряда соединены с выходом узла разрешения записи, их стоки - с шиной разрешения записи, исток первого транзистора элемента заряда соединен с неинвергирующим входом первого двухтактного буферного каскада, со стоком первого транзистора элемента разряда и с одной обкладкой конденсатора первого форсирующего элемента. Вторая обкладка которого соединена с инверсным входом устройства, исток транзистора второго элемента заряда соединен с неинвер- § тирующим входом второго двухтактного буферного каскада, со стоком транзистора L// второго элемента разряда и с одной обкладкой конденсатора второго форсирующего элемента, вторая обкладка которого соединена с прямым входом устройства, истоки транзисторов элементов разряда соединены с шиной нулевого потенциала, а их затворы - соответственно с прямым и инверсным входами устройства.Wl 00 О5

7 ICAS

I

| Патент США № 4123799, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Патент США № 4202045, кл | |||

| Насос | 1917 |

|

SU13A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1985-05-15—Публикация

1984-04-09—Подача