(54) ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления четырехфазным двигателем переменного тока | 1980 |

|

SU886182A1 |

| Устройство для моделированияиМпульСНОгО дАТчиКА чАСТОТы ВРАщЕНия | 1979 |

|

SU849245A1 |

| Аналоговое запоминающее устройство | 1974 |

|

SU510752A1 |

| Стабилизатор двуполярных импульсов тока | 1977 |

|

SU661526A1 |

| Устройство для автоматизации рентгеновской съемки органов грудной клетки | 1981 |

|

SU1039481A2 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Аналого-цифровой преобразователь компенсационного интегрирования | 1974 |

|

SU764126A1 |

| Интегратор | 1979 |

|

SU847330A1 |

| ФОТОДАТЧИК ИМПУЛЬСНОГО ИЗЛУЧЕНИЯ | 2018 |

|

RU2673989C1 |

| Устройство для управления четырехфазным двигателем переменного тока | 1983 |

|

SU1138918A2 |

Изобретение относится к области автоматики и электроизмерительной техники и может быть использовано п построении устройств измерения сигналов низкого уровня в присутствии помех. Известен интегратор, содержащий операционныйусилитель, и интегрирующую цепь, состоящую из резистора и конденсатора 1, Известный интегратор имеет низкую точность интегрирования, так как его выходной сигнал является функцией не только входного сигнала, но и напряжения дрейфа нуля one рационного усилителя. Наиболее близким к предлагаемому устройству по технической сущности является интегратор, содержащий -интегрирующий и корректирующий операционные усилители, интегрирующую цепь, состоящую из резистора и конденсатора, конденсатор запоминания напряжения коррекции дрейфа нул устройства и МОП-к 1ЮЧи управления процессом интегрирования,коррекцией дрейфа и разрядом интегрирующего ко денсатора 2 . У Недостатком этого интегратора яв .ляется наличие погрешности ичтёгрирования от влияния сопротивления открытого МОП-ключа, управляющего процессом интегрирования, а также сравнительно большая погрешность из-за влияния дрейфа нуля операционных усилителей. Целью изобретения является повышение точности интегрирования. Поставленная цель достигается тем, что в интегратор, содержащий интегрирующий усилитель, выход которого соединен с инвертирующим входом корректирующего операционного усилителя, масштабный резистор, один вывод которого является входом интегратора, интегрирующий конденсатор, подк.шоченный одной обкладкой к выходу интегрирующего усилителя, запоминающий конденсатор, включённый между шиной нулевого потенциала и неинвертирующим входом интегрирующего усилителя, и два ключа, каяудай из которых выполнен на МОП-транзисторе, цепь стокисток МОП-транзистора первого ключа включена параллельно интегрируюадему конденсатору, второго - между выходом корректирующего операционного усилителя и неинвертирующим входЬм интегрирукицего усилителя, а затворы- МОП-транзисторов ключей соедияены с входом сброса интегратора, введены дополнительные ключи, выполненные на МОП-транзисторах,дополнительный масштабный резистор и инвертор, причем цепь сток-исток МОПтранзистора первого дополнительного ключа включена между шиной нулевого потенциала и инвертирующим входом интегрирующего усилителя, цепь стокисток МОП-транзистора второго дополнительного ключа подключена между вторыми выводами масштабного резистора и интегрирующего конденсатора, соединенными через цепь сток-исток МОП-транзисторов соответственно третьего и .четвертого допрлнительных ключей с инвертирующим входом интегрирующего усилителя и с первым выводом дополнительного масштабного резистора, второй вывод которого подключен к инвертирующем) входу интегрирующего усилителя, затворы МОПтранзисторов второго и третьего дополнительных ключей Соединены, со входом управления процессоминтегрирования, затвор МОП-транзистора первого доп олнительного ключа подключен ко входу сброса интегратора, соединенному через инвертор с затвором МОП-транзистора четвертого дополнительного ключа.

Это позволяет значительно уменьшить влияние на точность интегрирования сопротивления Г ОП-ключей, . управляющих процессом интегрирования, а также дрейфа нуля корректирующего операционного усилителя.

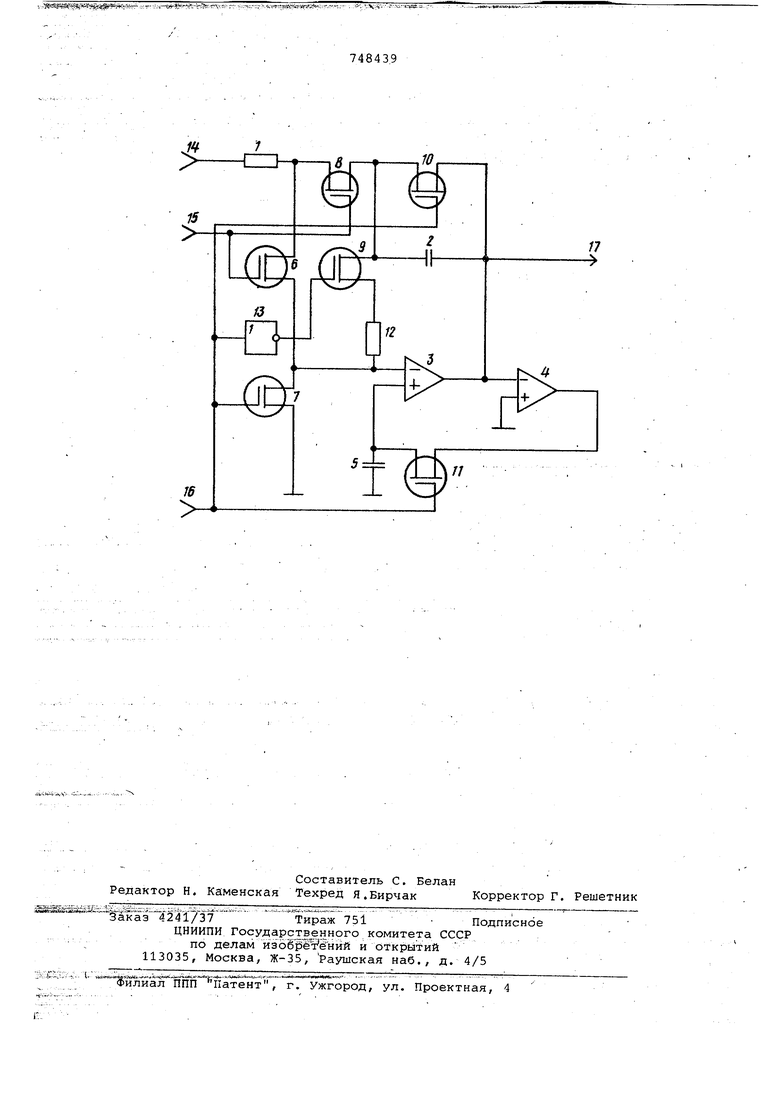

На чертеже показана схема интегратора, на которой обозначеньа масштабный резиЪтор 1, интегрирующий конденсатор 2, интегрирующий 3, и корректирующий 4 операционные усилители, запоминающий конденсатор 5, ключи 6-11, выполненные на МОП-транзисторах, дополнительный резистор 12, инвертор 13, вход интегратора 14, вход управления процессом интегрирования 15, вход сброса интегратора 16, выход интегратора 17.

Интегратор работает следующим образом.

С поступлением импульса сбросапо входу 16 интегратора открываются клйчй 10, 11 и 7 и закрывается ключ 9. С помощью ключа 10 осуществляется разряд интегрирующего конденсатора 2, ключом 11 подключается выход корректирующего операционного ус|1лителя к запоминающему конденсатору 5 и к неинвертирующему входу интегрирующего операционного усилителя 3. Ключ 7 замыкает инвертирующий вход интегрирующего операционног усилителя 3 на шину нулевого потенциала, а ключ 9 разрывает цепь отрицательной обратной связи интегратора. Одновременно с разрядом интегрирующего конденсатора, начинается процесс .коррекции дрейфа нуля

операционных усилителей. При этом напряжение на выходе корректирующего операционного усилителя будет равно

).,

(1)

и

где .Uj - входное напряжение и напряжение дрейфа нуля этого yc литeля,

Kj- коэффициент усиления этого

усилителя. .

Так как выход корректирующего операционного усилителя соединен с инвертирующим входом интегрирующего операционного усилителя, цепь отрицательной обратной связипоследнего разомкнута, и его инвертирующий вход подключен к шине нулевого потенциала, выходное напряжение интегрирующего усилителя можно записать

(2)

,,)

где uU - напряжение дрейфа нуля интегрирующего операционного усилителя,

к/, - его коэффициент усиления. Решая совместно уравнение (1) и (2) , получим

.,

и .K,

8Ь|Х

ПОСКОЛЬКУК 1 ,1

и выражение для выходного напряжения корректирунэщего операционного улителя, а соответственно и напряжения на запоминанйцем конденсаторе примет вид

ди, , Ugb,c;-Kf;Ab,.

После окончания импульса сброса открывается ключ 9, замыкая цепь отрицательной обратной связи интегрирующего операционного ус14лиТеля 3 через интегрирующий конденсатор 2. -,-,„,-«....

С поступлением на вход управления процессом интегрирования устройства 15 сигнала, разрешающего интегрирование, замыкаются ключи б и 8. Начинается интегрирование входного напряжения, подаваемого по входу 14

После окончания процесса интегривания (при включении ключей 6 и 8) интегратор входит в режим хранения проинтегрированного входного сигнала.

Выходное напряжение интегратора будет иметь вид

. t

:1

-2л.

v.)POlнeния (

(R+R,a-)

где к - сопротивление.масштабного

резистора,

R/)g- эквивалентное сопротивление, МОП-тра:нзисторов. Применение предлагаемого интегр тора в измерительных устройствах позволяет значительно повысить их точность. Так, дрейф нуля интегратора по сравнению с прототипом уме шается в к раз, где К, коэффициент усиления интегрирующего усилителя. Использование дополнительных кл чей и дополнительного резистора в цепи коммутации масштабного резистора уменьшает влияние сопротивления этих ключей на точность интегрирования. Так, если даже сопротивление дополнительного резистора равно нулю, точность интегрирования возрастает в два раза по сравнению с прототипом. При превышении сопротивления дополнительного резистора над сопротивлением открыто го ключа в 100 раз, влияние сопротивления открытого ключа на точнос интегрирования уменьшается в 100 р по сравнению с прототипом. Формула изобретения Интегратор, содержащий интегрирующий усилитель, выход которого соединен с инвертирующим входом корректирующего операционного усилителя, масштабный резистор, один вывод которого является входом инте гратора, интегрирующий конденсатор подключенный одной обкладкой к выходу интегрирующего усилителя, запоминающий конденсатор, включенный между шиной нулевого.потенциала и неинвертирующем входом интегрирующего усилителя, и два ключа, каждый из которых выполнен на МОП-транзисторе, цепь сток-исток МОП-транзистора первого ключа, включена паралле но интегрирующему конденсатору, вто рого - между выходом .корректирующег :операционн6го усилителя и неинверти ющим входом интегрирующего усилител а затворы МОП-транзисторов ключей соединены с входом сброса интегратора, отличающийся тем, что, с целью повышения точности интегрирования, в него введены дополнительные ключи, выполненные на МОПтранзисторах, дополнительный масштабный резистор и инвертор, причем цепь сток-исток МОП-транзистора первого дополнительного ключа включена между шиной нулевого потенциала и инвертирующим входом интегрирующего усилителя, цепь сток-исток МОПтранзистора второго дополнительного ключа подключена между вторыми выводами масштабного резистора и интегрирующего конденсатора, соединенными через цепь сток-исток МОП-транзисторов соответственно третьего и четвертого дополнительных ключей с инвертирующим входом интегрирующего усилителя и с первым выводом дополнительного масштабного резистора, второй вывод которого подключен к инвертирующему входу интегрирующего усилителя, затворы МОП-транзисторов второго и третьего дополнительных ключей соединены со входом управдения процессом интегрирования, затвор МОП-,транзистора первого дополнительного ключа подключен ко входу сброса интегратора, соединенному через инвертор с затвором МОП-транзистора четвертого дополнительного ключа. Источники информации, принятые во внимание при экспертизе 1.Ж. Марше. Операционные усилители и их применение, Энергия, М., 1974, с. 70. . 2.А. И. Наконечный. Интегра тор на микросхеме с автоматической компенсацией дрейфа нуля. Контрольно-измерит,ельная техника. Республиканский межведомственный научнотехнический сборник, Киев, 1975, вып. 18 (прототип).

748439

70

Авторы

Даты

1980-07-15—Публикация

1978-05-04—Подача