Изобретение относится к вычислительной технике и может быть использовано при цифровой обработке сигналов для преобразования напряжения в цифровой двоичный код с повышенным быстродействием и минимальным объемом оборудования.

Известен последовательный аналого-цифровой преобразователь напряжение-код, реализующий метод последовательного приближения (Зиатдинов С.И., Суетина Т.А., Поваренкин Н.В. Схемотехника телекоммуникационных устройств. Учебник. М: Академия, 2016. С. 218, рис. 8.3).

Устройство предназначено для преобразования напряжения в двоичный код. Преобразователь содержит n триггеров; n-разрядный сдвигающий регистр; n-разрядный параллельный цифроаналоговый преобразователь; генератор тактовых импульсов и компаратор. Управляющие входы триггеров соединены с соответствующими выходами сдвигающего регистра; выходы триггеров соединены с соответствующими входами параллельного цифроаналогового преобразователя, выход которого соединен с одним из входов компаратора; выход компаратора соединен с управляющим входом сдвигающего регистра и выход генератора тактовых импульсов соединен со входом подачи импульсов сдвига сдвигающего регистра.

Недостатком данного устройства является сложность схемы управления триггерами и большое количество оборудования.

Известен последовательный преобразователь напряжение-код следящего типа (Микропроцессорные системы автоматического управления. Под общей ред. В.А. Бесекерского. Л.: Машиностроение, 1998. С. 300, рис. 12.6). В состав преобразователя входят реверсивный n-разрядный счетчик; n-разрядный параллельный цифроаналоговый преобразователь; генератор импульсов тактовой частоты; компаратор и логические двухвходовые конъюнкторы управления направлением счета. В преобразователе выходы реверсивного счетчика соединены с одноименными входами цифроаналогового преобразователя; выход цифроаналогового преобразователя подключен к одному из входом компаратора, на второй вход которого подается преобразуемое напряжение; выход компаратора через логические элементы подключен к управляющим входам суммировании и вычитания реверсивного счетчика, вход которого соединен с выходом генератора тактовой частоты.

Недостатком устройства является наличие сложного и дорогого реверсивного счетчика, а также большое время начальной установки режима слежения.

Наиболее близким по технической сущности к предлагаемому изобретению является преобразователь напряжение-код, построенный по методу последовательного счета со ступенчатым пилообразным напряжением (Гитис Э.И., Пискунов Е.А. Аналого-цифровые преобразователи. М.: Энергоиздат, 1981. С. 218, рис. 6.4)

Устройство состоит из n-разрядного двоичного суммирующего счетчика; n-разрядного параллельного цифроаналогового преобразователя; компаратора; генератора импульсов тактовой частоты; триггера запуска счета; двухвходового конъюнктора подачи счетных импульсов; выходы двоичного суммирующего счетчика соединены с одноименными входами параллельного цифроаналогового преобразователя, выход которого подключен к одному из входов компаратора; на другой вход компаратора подается преобразуемое напряжение; выход компаратора соединен со входом сброса триггера запуска счета; выход триггера запуска счета подключен к одному из входов конъюнктора подачи счетных импульсов; другой вход конъюнктора подачи счетных импульсов соединен с выходом генератора импульсов тактовой частоты; выход конъюнктора подачи счетных импульсов подключен ко входу поступления тактовых импульсов двоичного суммирующего счетчика.

Недостатком устройства является большое время преобразования напряжения в код.

Основная задача, на решение которой направлено заявляемое изобретение, состоит в разработке последовательного преобразователя напряжение-код со ступенчатым пилообразным напряжением, обладающего повышенным быстродействием при минимальном количестве оборудования.

Техническим результатом, достигаемым при осуществлении заявляемого изобретения, является повышение быстродействия цифровых устройств обработки меняющихся во времени сигналов.

Указанный технический результат достигается тем, что последовательный преобразователь напряжение-код со ступенчатым пилообразным напряжением, включающий n-разрядный двоичный суммирующий счетчик; n-разрядный параллельный цифроаналоговый преобразователь; компаратор; генератор импульсов тактовой частоты; триггер запуска счета; двухвходовой конъюнктор подачи счетных импульсов, при этом выход генератора импульсов тактовой частоты соединен с первым входом двухвходового конъюнктора подачи счетных импульсов; выход двухвходового конъюнктора подачи счетных импульсов соединен со входом С поступления тактовых импульсов двоичного суммирующего счетчика; выходы dn-2, … ,d0 n-разрядного двоичного суммирующего счетчика соединены с одноименными входами n-разрядного параллельного цифроаналогового преобразователя; выход n-разрядного параллельного цифроаналогового преобразователя соединен со вторым входом компаратора; выход компаратора соединен со входом сброса R триггера запуска счета, выход которого соединен со вторым входом двухвходового конъюнктора подачи счетных импульсов; вход сброса R n-разрядного двоичного суммирующего счетчика служит для подачи импульса сброса; первый вход компаратора служит для подачи преобразуемого напряжения; вход S триггера запуска счета служит для подачи импульса начала преобразования, дополнительно содержит триггер установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; линию задержки; двухвходовой конъюнктор управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя и двухвходовой дизъюнктор; выход старшего разряда dn-1 n-разрядного двоичного суммирующего счетчика соединен со вторым входом двухвходового дизъюнктора, первый вход которого подключен к выходу триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; выход двухвходового дизъюнктора соединен со входом старшего разряда dn-1 n-разрядного параллельного цифроаналогового преобразователя; выход n-разрядного параллельного цифроаналогового преобразователя соединен со вторым входом компаратора; выход компаратора одновременно соединен со входом сброса R триггера запуска счета и первым входом двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; выход двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя соединен со входом сброса R триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; выход линии задержки соединен со вторым входом двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; вход сброса R n-разрядного двоичного суммирующего счетчика одновременно соединен со входом линии задержки и входом S триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя.

Поставленный технический результат достигается за счет введения дополнительных блоков и связей между ними, что позволяет весь диапазон возможных изменений преобразуемого напряжения разбить на два равных поддиапазона. При этом последовательное преобразование напряжения в код методом ступенчатого пилообразного напряжения осуществляется в пределах лишь того поддиапазона, в котором находится текущее значение напряжения, что позволяет в среднем практически в два раза повысит скорость преобразования без существенных дополнительных затрат на оборудование.

Проведенный заявителем анализ уровня техники установил, что у аналогов отсутствует совокупность признаков, тождественных признакам заявляемого устройства «Последовательный преобразователь напряжение-код со ступенчатым пилообразным напряжением». Следовательно, заявляемое устройство соответствует условию «новизна».

Результаты поиска известных технических решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявляемого устройства, показали, что они не следуют явным образом из уровня техники.

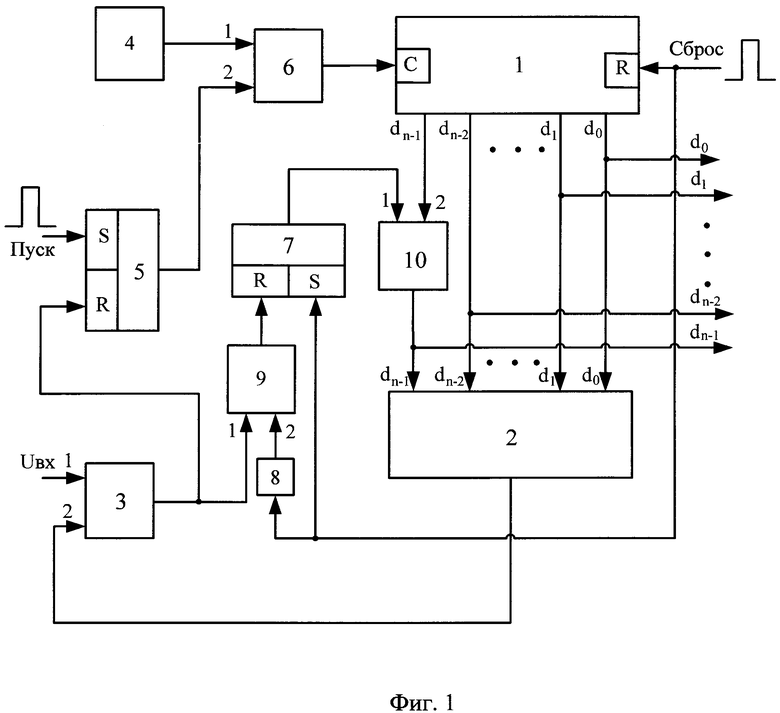

Сущность изобретения поясняется чертежом, представленным на фиг. 1. Последовательный преобразователь напряжение-код со ступенчатым пилообразным напряжением включает n-разрядный двоичный суммирующий счетчик 1; n-разрядный параллельный цифроаналоговый преобразователь 2; компаратор 3; генератор импульсов тактовой частоты 4; триггер запуска счета 5; двухвходовой конъюнктор подачи счетных импульсов 6; триггер установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя 7; линию задержки 8; двухвходовой конъюнктор управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя 9 и двухвходовой дизъюнктор 10; выходы dn-2, … ,d0 n-разрядного двоичного суммирующего счетчика 1 соединены с одноименными входами n-разрядного параллельного цифроаналогового преобразователя 2; выход старшего разряда dn-1 n-разрядного двоичного суммирующего счетчика 1 соединен со вторым входом двухвходового дизъюнктора 10, первый вход которого подключен к выходу триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя 7; выход двухвходового дизъюнктора 10 соединен со входом старшего разряда dn-1 n-разрядного параллельного цифроаналогового преобразователя 2; выход n-разрядного параллельного цифроаналогового преобразователя 2 соединен со вторым входом компаратора 3; выход компаратора 3 одновременно соединен со входом сброса R триггера запуска счета 5 и первым входом двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя 9; выход двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя 9 соединен со входом сброса R триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя 7; выход линии задержки 8 соединен со вторым входом двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя 9; вход сброса R n-разрядного двоичного суммирующего счетчика 1 соединен одновременно со входом линии задержки 8 и входом S триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя 7; вход сброса R n-разрядного двоичного суммирующего счетчика служит для подачи импульса сброса; первый вход компаратора служит для подачи преобразуемого напряжения; вход S триггера запуска счета служит для подачи импульса начала преобразования.

В качестве генератора импульсов тактовой частоты можно использовать, например, автогенератор, в качестве триггера - микросхему К555ТР2, в качестве компаратора - микросхему - AD8564AD, в качестве двухвходового конъюнктора - микросхему К1555ЛИ1, в качестве линии задержки -последовательно соединенные буферные элементы К155ЛН4, в качестве двоичного суммирующего счетчика - микросхему К155ИЕ4, в качестве двухвходового дизъюнктора - микросхему К155 ЛЛ1, в качестве параллельного цифроаналогового преобразователя - микросхему К572ПА1 [1], [2].

Последовательный преобразователь напряжение-код со ступенчатым пилообразным напряжением работает следующим образом.

Импульсом «сброс», подаваемым на вход сброса R двоичного суммирующего счетчика 1, обнуляется содержимое счетчика 1. Одновременно импульс «сброс» поступает на вход S триггера 7 и в триггер 7 записывается логическая единица, которая через дизъюнктор 10 поступает в старший разряд параллельного цифроаналогового преобразователя 2. В результате на выходе параллельного цифроаналогового преобразователя 2 устанавливается напряжение, соответствующее коду 100 … 002, которое делит весь диапазон возможных значений преобразуемого напряжения Uвx на два равных поддиапазона. Данное напряжение поступает на второй вход компаратора 3, в котором сравнивается с преобразуемым напряжением Uвх, поступающим на первый вход компаратора 3. Если преобразуемое напряжение Uвх меньше напряжения, поступающего на второй вход компаратора 3, то компаратор 3 срабатывает, на его выходе устанавливается напряжение логической единицы, которое поступает на первый вход двухвходового конъюнктора 9. Одновременно с выхода линии задержки 8 задержанный импульс сброса поступает на второй вход двухвходового конъюнктора 9. При этом на выходе двухвходового конъюнктора 9 устанавливается уровень логической единицы, которым по входу сброса R сбрасывается триггер 7 и на выходе параллельного цифроаналогового преобразователя 2 формируется нулевое напряжение. Это означает, что преобразование входного напряжения Uвх будет вестись в нижнем поддиапазоне возможных значений преобразуемого напряжения.

В противном случае, когда преобразуемое напряжение Uвх больше напряжения, поступающего после сигнала сброса с параллельного цифроаналогового преобразователя 2, компаратор 3 не срабатывает. То на первом входе и выходе двухвходового конъюнктора 9 присутствует напряжение уровня логического нуля; триггер 7 не сбрасывается с уровня логической единицы. В результате в старшем разряде параллельного цифроаналогового преобразователя 2 присутствует логическая единица и напряжение на выходе параллельного цифроаналогового преобразователя 2 равняется половине уровня возможных значений преобразуемого напряжения Uвх. Это означает, что преобразование входного напряжения Uвх будет вестись в верхнем поддиапазоне возможных значений преобразуемого напряжения.

Далее на вход S триггера 5 поступает импульс запуска, на выходе триггера 5 устанавливается напряжения уровня логической единицы, которое поступает на второй вход двухвходового конъюнктора 6, тем самым разрешая прохождение счетных импульсов генератора импульсов тактовой частоты 4 на вход С n-разрядного двоичного суммирующего счетчика 1. В результате подсчета импульсов на выходе n-разрядного двоичного суммирующего счетчика 1 формируется линейно нарастающий двоичный код, который параллельным цифроаналоговым преобразователем 2 преобразуется в ступенчато нарастающее напряжение. Данное напряжение поступает на второй вход компаратора 3 и сравнивается с преобразуемым напряжением Uвх.

В момент времени, когда ступенчато нарастающее напряжение с выхода параллельного цифроаналогового преобразователя 2 становится больше преобразуемого напряжения Uвх, компаратор 3 срабатывает, на его выходе формируется напряжение уровня логической единицы, которое поступает на вход сброса R триггера 5. Триггер 5 сбрасывается и через двухвходовой конъюнктор 6 прекращается поступление счетных импульсов на n-разрядный двоичный суммирующий счетчик 1. На этом процесс преобразования заканчивается. Код, установившийся на входах n-разрядного параллельного цифроаналогового преобразователя 2 в момент прекращения счета, является цифровым аналогом преобразуемого напряжения.

В результате предложенный последовательный преобразователь напряжение-код со ступенчатым пилообразным напряжением позволяет повысить быстродействие аналого-цифрового преобразования напряжения в двоичный код по сравнению с прототипом при минимальном дополнительном оборудовании.

Увеличение скорости преобразования достигается за счет того, что весь диапазон возможных изменений преобразуемого напряжения разбивается на два равных поддиапазона. При этом последовательное преобразование напряжения в код методом ступенчатого пилообразного напряжения осуществляется в пределах лишь того поддиапазона, в котором находится текущее значение напряжения.

Сопоставление параметров, характеризующих заявляемое устройство и прототип, позволяют сделать вывод о том, что заявляемое устройство обеспечивает более высокую скорость преобразования напряжение-код.

Приведенные сведения доказывают, что при осуществлении заявленной модели выполняются следующие условия:

- средство, воплощающее предлагаемое устройство при его осуществлении, предназначено для использования в вычислительной технике, а именно в цифровых устройствах обработки сигналов;

- для заявленного устройства в том виде, как оно охарактеризовано в независимом пункте формулы изобретния, подтверждена возможность ее осуществления с помощью описанных до даты подачи заявки средств;

- средство, воплощающее заявленное устройство при его осуществлении, способно обеспечить получение указанного технического результата.

Следовательно, заявленное устройство соответствует условию «промышленная применимость».

Источник информации:

1. Зиатдинов С.И., Суетина Т.А., Поваренкин Н.В. Схемотехника телекоммуникационных устройств. Учебник. М: Академия, 2016.

2. Шило В.Л. Популярные цифровые микросхемы. М.: Радио и связь, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор выбросов и провалов напряжения | 1990 |

|

SU1837325A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| ИМИТАТОР УГЛА ПОВОРОТА АНТЕННЫ РЛС | 1987 |

|

SU1841003A1 |

| СПОСОБ АДАПТИВНОЙ АДРЕСНОЙ СИГНАЛИЗАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2209468C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ БЕЗЫЗБЫТОЧНОГОS-РАЗРЯДНОГО ДВОИЧНОГО КОДА В ДВОИЧНЫЙV-РАЗРЯДНЫЙ /С-ВЫЧЕТНЫЙ РАЗНОСТНЫЙ КОД | 1972 |

|

SU435518A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ В КОД | 1991 |

|

RU2019030C1 |

| Цифровая система измерения глубинного положения морской пьезосейсмографной косы | 1976 |

|

SU894640A1 |

| Устройство для вихретоковой дефектоскопии | 1986 |

|

SU1308885A1 |

| Вероятностный преобразователь аналог-код | 1984 |

|

SU1229950A1 |

Изобретение относится к вычислительной технике и может быть использовано при цифровой обработке сигналов для преобразования напряжения в цифровой двоичный код. Техническим результатом, достигаемым при осуществлении заявляемого изобретения, является повышение быстродействия цифровых устройств обработки меняющихся во времени сигналов. Устройство содержит n-разрядный двоичный суммирующий счетчик; n-разрядный параллельный цифроаналоговый преобразователь; компаратор; генератор импульсов тактовой частоты; триггер запуска счета; двухвходовой конъюнктор подачи счетных импульсов; триггер установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; линию задержки; двухвходовый конъюнктор управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя и двухвходовый дизъюнктор. 1 ил.

Последовательный преобразователь напряжение-код со ступенчатым пилообразным напряжением, включающий n-разрядный двоичный суммирующий счетчик; n-разрядный параллельный цифроаналоговый преобразователь; компаратор; генератор импульсов тактовой частоты; триггер запуска счета; двухвходовый конъюнктор подачи счетных импульсов, при этом выход генератора импульсов тактовой частоты соединен с первым входом двухвходового конъюнктора подачи счетных импульсов; выход двухвходового конъюнктора подачи счетных импульсов соединен со входом С поступления тактовых импульсов двоичного суммирующего счетчика; выходы dn-2,…, d0 n-разрядного двоичного суммирующего счетчика соединены с одноименными входами n-разрядного параллельного цифроаналогового преобразователя; выход n-разрядного параллельного цифроаналогового преобразователя соединен со вторым входом компаратора; выход компаратора соединен со входом сброса R триггера запуска счета, выход которого соединен со вторым входом двухвходового конъюнктора подачи счетных импульсов; вход сброса R n-разрядного двоичного суммирующего счетчика служит для подачи импульса сброса; первый вход компаратора служит для подачи преобразуемого напряжения; вход S триггера запуска счета служит для подачи импульса начала преобразования, отличающийся тем, что он дополнительно содержит триггер установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; линию задержки; двухвходовый конъюнктор управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя и двухвходовый дизъюнктор; выход старшего разряда dn-1 n-разрядного двоичного суммирующего счетчика соединен со вторым входом двухвходового дизъюнктора, первый вход которого подключен к выходу триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; выход двухвходового дизъюнктора соединен со входом старшего разряда dn-1 n-разрядного параллельного цифроаналогового преобразователя; выход n-разрядного параллельного цифроаналогового преобразователя соединен со вторым входом компаратора; выход компаратора одновременно соединен со входом сброса R триггера запуска счета и первым входом двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; выход двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя соединен со входом сброса R триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; выход линии задержки соединен со вторым входом двухвходового конъюнктора управления триггером установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя; вход сброса R n-разрядного двоичного суммирующего счетчика одновременно соединен со входом линии задержки и входом S триггера установки старшего разряда n-разрядного параллельного цифроаналогового преобразователя.

| ГИТИС Э.И | |||

| и др | |||

| Аналого-цифровые преобразователи, Москва, Энергоиздат, 1981, с | |||

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU834892A1 |

| US 7612702 B2, 03.11.2009 | |||

| US 20170111053 A1, 20.04.2017 | |||

| US 7982652 B2, 19.07.2011. | |||

Авторы

Даты

2019-06-24—Публикация

2018-01-09—Подача