Самосинхронный динамический однотактный D-триггер с нулевым спейсером относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен динамический асинхронный D-триггер [1], содержащий шесть элементов И-НЕ и обеспечивающий запись информации в триггер и блокирование информационного входа с после прихода активного фронта тактового входа.

Недостаток известного устройства - отсутствие средств индикации окончания переходных процессов в элементах триггера.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный однотактный D-триггер с высоким активным уровнем сигнала управления [2], в дальнейшем именуемый D-триггером, содержащий один инвертор и четыре элемента ИЛИ-И-НЕ. Триггер обеспечивает запись состояния информационного входа и переключение в рабочую фазу по высокому уровню входа управления, блокировку информационного входа и переключение в спейсерную фазу низким уровнем входа управления и контроль окончания переходных процессов при переключении в спейсерную и рабочую фазу.

Недостаток прототипа - большая длительность периода времени после появления высокого уровня на входе управления D-триггера, соответствующая длительности высокого уровня на входе управления, в течение которого состояние информационного входа не должно изменяться во избежание нарушения самосинхронной дисциплины формирования сигналов и взаимодействия самосинхронных устройств.

Задача, решаемая заявляемым изобретением, заключается в ускорении взаимодействия D-триггера с источником его информационного входа за счет сокращения времени, в течение которого состояние информационного входа D-триггера не должно изменяться после появления высокого уровня на его входе управления. Такое ускорение взаимодействия D-триггера с источником его информационного входа соответствует требованиям синхронных интерфейсов и обеспечивает возможность использования предлагаемого самосинхронного D-триггера в синхронном окружении.

Это достигается тем, что комбинационный индикаторный выход в самосинхронном однотактном D-триггере с нулевым спейсером (прототипе), преобразуется в последовательностный индикаторный выход (выход с памятью). Это преобразование реализуется введением дополнительного элемента НЕ между комбинационной частью индикаторного элемента и его внешним выводом и введением двух дополнительных связей. Первая связь обеспечивает подключение комбинационного индикаторного выхода к дополнительным входам триггера (бистабильной ячейке), что гарантирует невосприимчивость триггера к изменению состояния компонентов информационного входа. Вторая связь обеспечивает подключение дополнительного элемента НЕ к дополнительным входам индикаторного элемента, что переводит его из комбинационного класса в последовательностный класс и гарантирует невосприимчивость индикаторного выхода к изменению состояния компонентов информационного входа.

- Использование обратных связей в асинхронных триггерах известно, например, в Т-триггере [3]. Однако использование их в самосинхронном D-триггере с учетом специфики работы самосинхронных устройств позволило достичь эффекта, выраженного целью изобретения. Существенное отличие предлагаемой реализации обратных связей от аналогичных решений в асинхронной схемотехнике заключается в том, что в данном случае обратные связи используются для предотвращения нежелательного переключения триггера, а не для подготовки его к переключению в противоположное состояние. Это позволяет ускорить блокировку информационного входа триггера после прихода активного уровня сигнала управления, разрешающего запись состояния информационного входа в триггер, и обеспечить ее самосинхронность при использовании дополнительного инвертора, как описано ниже.

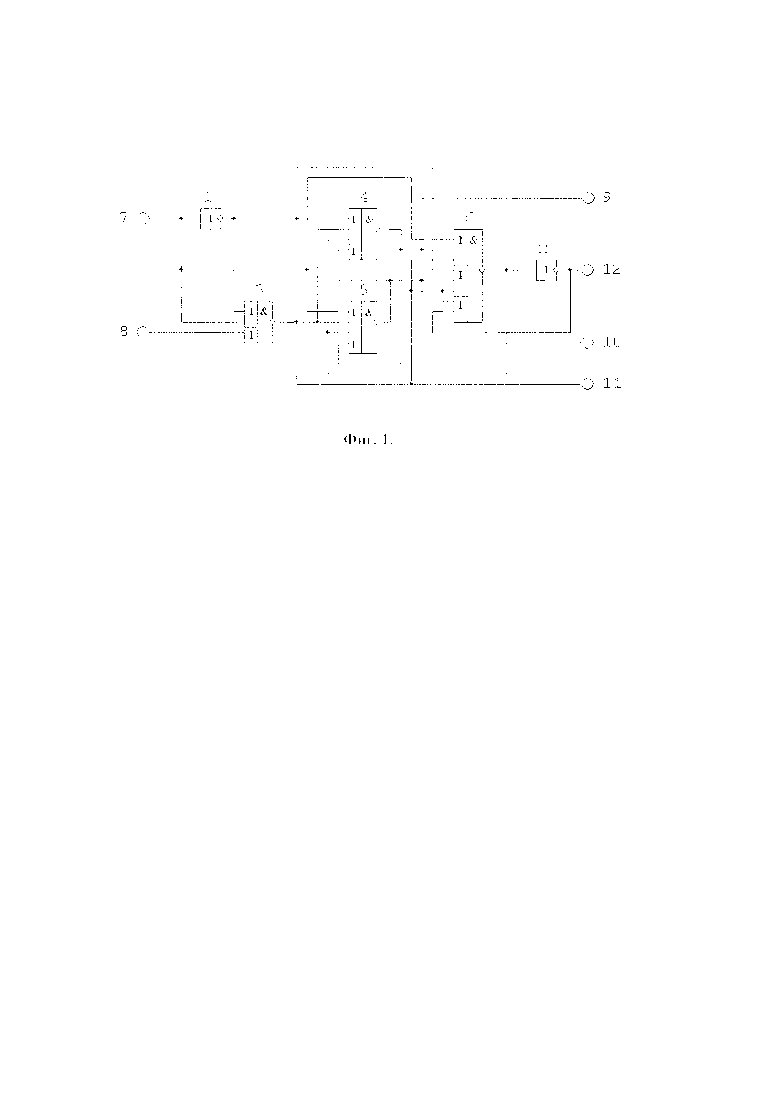

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны (не было известно ранее из опубликованных в мире источников информации), устройство может считаться отвечающим критерию новизны. Из уровня техники известны только объекты, которым присущи признаки, обепечивающие невосприимчивость триггера к изменению состояния компонентов информационного входа и описанные в формуле. Объекты же, обеспечивающие невосприимчивость индикатора окончания переходных процессов к изменению состояния компонентов информационного входа и описанные в формуле не известны, что отвечает критерию новизны изобретения. В тексте заявки описаны все средства и методы, необходимые для реализации решения, как оно представлено в формуле изобретения, что отвечает критерию промышленной применимости. На Фиг. 1 изображена схема самосинхронного динамического однотактного D-триггера с нулевым спейсером.

Схема содержит первый 1 и второй 2 инверторы и четыре элемента ИЛИ-И-НЕ 3 -6, однофазный информационный вход 7, вход управления 8, информационный бифазный выход 9 - 10, выход сигнала управления 11 и индикаторный выход 12, причем однофазный информационный вход 7 подключен к входу первого инвертора 1, ко второму входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 3, первому входу первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ 5 и к первому входу первой группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ 6, вход управления 8 триггера соединен с входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 3, выход первого инвертора 1 подключен к первым входам первых групп входов ИЛИ первого 3 и второго 4 элементов ИЛИ-И-НЕ и к первому входу второй группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ 6, выход первого элемента ИЛИ-И-НЕ 3 соединен со вторыми входами первых групп входов ИЛИ второго 4 и третьего 5 элементов ИЛИ-И-НЕ, с третьими входами первой и второй групп входов ИЛИ и первым входом третьей группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ 6 и выходом сигнала управления 11 триггера, выход второго элемента ИЛИ-И-НЕ 4 подключен к входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ 5, второму входу первой группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ 6 и прямой составляющей бифазного информационного выхода 9 триггера, выход третьего элемента ИЛИ-И-НЕ 5 подключен к входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ 4, второму входу второй группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ 6 и инверсной составляющей бифазного информационного выхода 10 триггера, третьи входы первых групп входов ИЛИ второго 4 и третьего 5 элементов ИЛИ-И-НЕ соединены с выходом четвертого элемента ИЛИ-И-НЕ 6 и входом второго инвертора 2, второй вход третьей группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ 6 подключен к выходу второго инвертора 2 и к индикаторному выходу 12 триггера.

Схема работает следующим образом. Запись состояния однофазного информационного входа 7 в триггер происходит при поступлении высокого (рабочего) уровня на вход управления 8 D-триггера. Окончание записи (завершение переключений всех элементов схемы триггера, инициированных в процессе записи) в бистабильную ячейку памяти на элементах ИЛИ-И-НЕ 4 и 5 фиксируется индикаторным элементом на элементе ИЛИ-И-НЕ 6, подтверждающим высоким уровнем на своем выходе соответствие состояния информационного бифазного выхода 9 - 10 триггера состоянию информационного входа 7. Выход индикаторного элемента 6 переключается в состояние логической единицы, обеспечивающее блокировку записи однофазного информационного входа 7 триггера в ячейку памяти на элементах 4 и 5. Одновременно переключается в состояние логического нуля инвертор 2, запрещая переключение индикаторного элемента 6 из-за возможного переключения информационного входа 7 триггера в состояние, не соответствующее состоянию ячейки памяти на элементах 4 и 5. Выход инвертора 2 формирует индикаторный выход 12, оповещающий подключенные к данному D-триггеру устройства о завершении записи в триггер и разрешающий источнику информационного входа 7 триггера больше не поддерживать текущее состояние информационного входа 7. Источник информационного входа данного D-триггера, получив это уведомление, инициирует переключение сигнала управления 8 триггера в неактивное (спейсерное) состояние логического нуля и одновременно с этим, не дожидаясь ответа от D-триггера, может начать формирование нового значения информационного входа 7. D-триггер принимает состояние логического нуля (спейсерное) входа управления 8, переводит выход сигнала управления в состояние логической единицы и инициирует переключение индикаторного элемента 6 в состояние логического нуля, снимающее блокировку записи информационного входа 7 в ячейку памяти на элементах 4 и 5 индикаторным элементом (сама блокировка остается, но реализуется уже входом управления) и запрещение изменения состояния индикаторного элемента 6 из-за несоответствия состояния информационного входа 7 состоянию ячейки памяти на элементах 4 и 5. После окончания переключения инвертора 2 в состояние логической единицы D-триггер готов к записи нового значения информационного входа 7, о чем он уведомляет источник информационного входа 7 высоким уровнем индикаторного выхода 12.

Особенности данной схемы по сравнению с прототипом следующие.

Триггер имеет обратные связи, обеспечивающие блокировку информационного входа триггера после записи его состояния в ячейку памяти триггера и блокировку индикаторного элемента до появления низкого уровня на входе управления триггера. Это позволяет источнику информационного входа триггера начать формирование нового значения информационного входа, не дожидаясь переключения в спейсер (низкий уровень) входа управления триггера, что в прототипе является обязательным условием для соблюдения самосинхронной дисциплины формирования сигналов в самосинхронной схеме.

Таким образом, предлагаемое устройство ускоряет взаимодействие D-триггера с источником его информационного входа и обеспечивает возможность использования предлагаемого самосинхронного D-триггера в синхронном окружении. Тем самым обеспечивается получение заявленного результата.

На практике D-триггер часто требует предустановки в определенное состояние перед началом (после включения питания) или в процессе работы схемы.

В качестве примеров покажем реализации самосинхронного динамического однотактного D-триггера с нулевым спейсером с асинхронными сбросом и установкой.

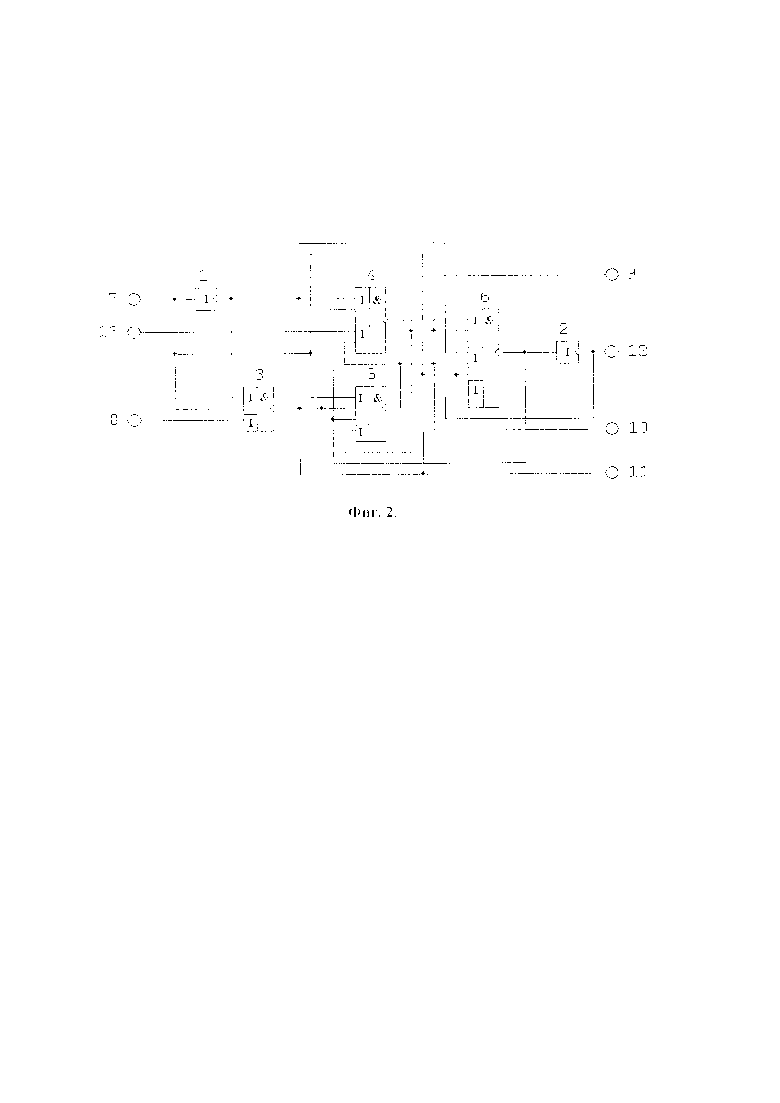

На Фиг. 2 представлена реализация самосинхронного динамического однотактного D-триггера с нулевым спейсером с асинхронным сбросом. Данная реализация отличается от реализации на Фиг. 1 тем, что во вторую группу входов ИЛИ второго элемента ИЛИ-И-НЕ 4 введен второй вход, подключенный к входу асинхронного сброса 13.

Сброс триггера в состояние с низким уровнем на прямой составляющей бифазного выхода 9 и высоким уровнем на инверсной составляющей бифазного выхода 10 осуществляется при спейсерном состоянии входа управления 8 триггера и происходит следующим образом. При низком уровне сигнала на входе управления 8 выход элемента ИЛИ-И-НЕ 3 своим высоким уровнем блокирует запись информационного входа 7 в бистабильную ячейку на элементах 4 и 5 и поддерживает выход индикаторного элемента ИЛИ-И-НЕ 6 в состоянии логического нуля. Подача в это время высокого уровня на вход асинхронного сброса 13 приводит к переключению выхода элемента ИЛИ-И-НЕ 4 и, соответственно, прямой составляющей бифазного выхода 9, в состояние логического нуля, что, в свою очередь, вызывает переключение элемента ИЛИ-И-НЕ 5 и инверсной составляющей бифазного выхода 10 в состояние логической единицы. Сброс триггера завершен.

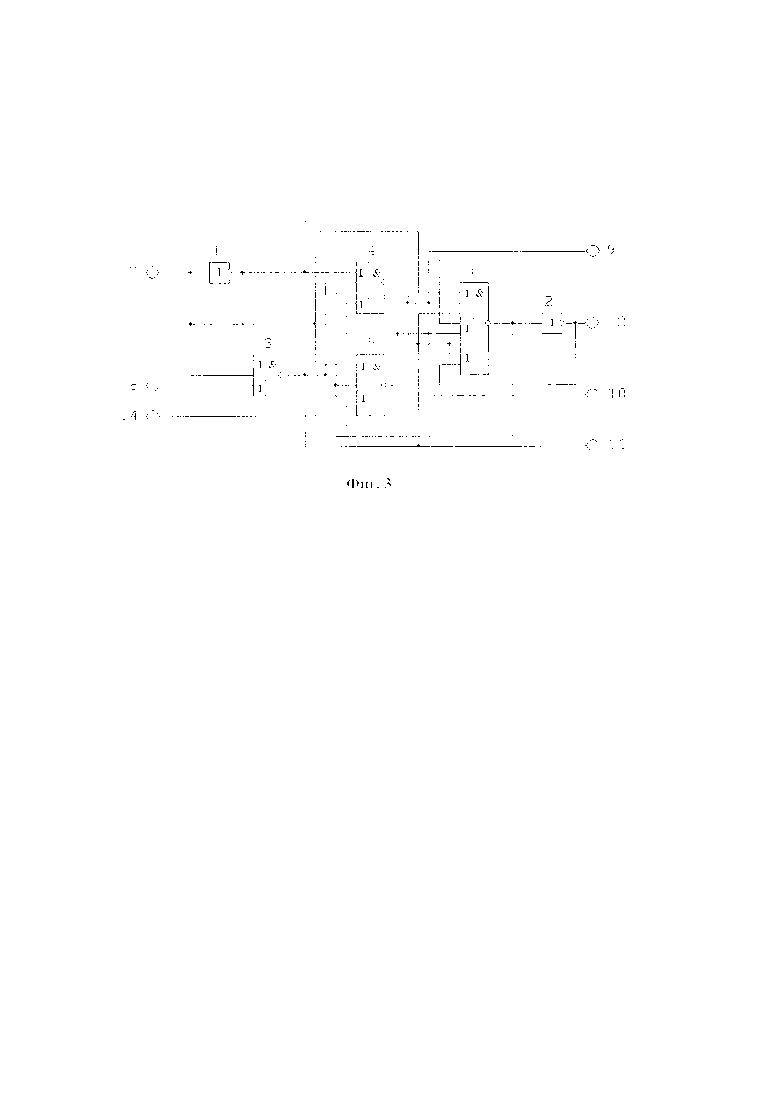

На Фиг. 3 представлена реализация самосинхронного динамического однотактного D-триггера с нулевым спейсером с асинхронной установкой. Данная реализация отличается от реализации на Фиг. 1 тем, что во вторую группу входов ИЛИ третьего элемента ИЛИ-И-НЕ 5 введен второй вход, подключенный к входу асинхронной установки 14.

Установка триггера в состояние с высоким уровнем на прямой составляющей бифазного выхода 9 и низким уровнем на инверсной составляющей бифазного выхода 10 осуществляется при спейсерном состоянии входа управления 8 триггера и происходит следующим образом. При низком уровне сигнала на входе управления 8 выход элемента ИЛИ-И-НЕ 3 своим высоким уровнем блокирует запись информационного входа 7 в бистабильную ячейку на элементах 4 и 5 и поддерживает выход индикаторного элемента ИЛИ-И-НЕ 6 в состоянии логического нуля. Подача в это время высокого уровня на вход асинхронной установки 14 приводит к переключению выхода элемента ИЛИ-И-НЕ 5 и, соответственно, инверсной составляющей бифазного выхода 10 в состояние логического нуля, что, в свою очередь, вызывает переключение элемента ИЛИ-И-НЕ 4 и прямой составляющей бифазного выхода 9 в состояние логической единицы. Установка триггера завершена.

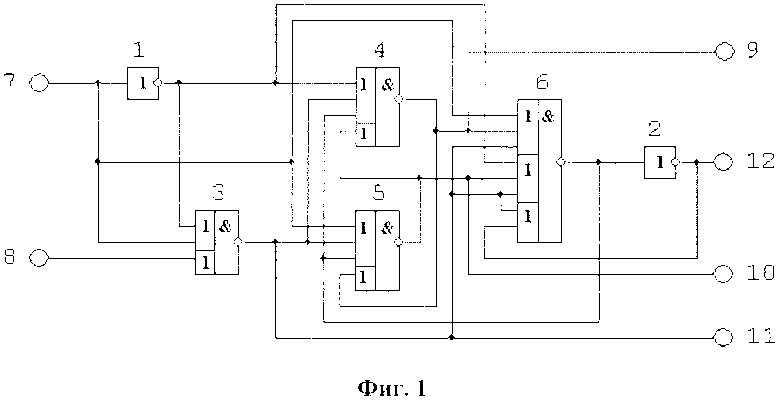

На Фиг. 4 представлена схема реализации самосинхронного динамического однотактного D-триггера с нулевым спейсером с асинхронными сбросом и установкой. Данная схема отличается от схемы на Фиг. 1 тем, что во вторые группы входов ИЛИ второго 4 и третьего 5 элементов ИЛИ-И-НЕ введен второй вход, подключенный к входам асинхронного сброса 13 и асинхронной установки 14 соответственно. Сброс и установка D-триггера выполняется при спейсерном состоянии входа управления 8 в соответствии с рассмотренными выше процедурами сброса и установки вариантов триггера, представленных на Фиг. 2 и 3.

Источники:

[1] Титце У., Шенк К. Полупроводниковая схемотехника: Справочное руководство. Пер. с нем. М: Мир, 1982. - 512 с, рис. 9.34.

[2] Соколов И.А., Степченков Ю.А., Дьяченко Ю.Г., Захаров В.Н. Самосинхронный однотактный D-триггер с высоким активным уровнем сигнала управления: пат. №2362266. Зарегистрирован 20.07.09. Опубл. в Б.И., 2009, №20. - 7 с.

[3] Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ - Санкт-Петербург, 2000. 528 с. ISBN 5-8206-0100-9, рис. 3.7(б).

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693318C1 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с нулевым спейсером | 2024 |

|

RU2835382C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693319C1 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с единичным спейсером | 2024 |

|

RU2834690C1 |

| ФОРМИРОВАТЕЛЬ ПАРАФАЗНОГО СИГНАЛА С НИЗКИМ АКТИВНЫМ УРОВНЕМ ВХОДА УПРАВЛЕНИЯ | 2011 |

|

RU2475952C1 |

| ФОРМИРОВАТЕЛЬ ПАРАФАЗНОГО СИГНАЛА С ВЫСОКИМ АКТИВНЫМ УРОВНЕМ ВХОДА УПРАВЛЕНИЯ | 2011 |

|

RU2469470C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С НУЛЕВЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693321C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ | 2008 |

|

RU2390092C1 |

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации. Технический результат заключается в ускорении взаимодействия D-триггера с источником его информационного входа за счет сокращения времени, в течение которого состояние информационного входа D-триггера не должно изменяться после появления высокого уровня на его входе управления. Для этого комбинационный индикаторный выход в самосинхронном однотактном D-триггере с нулевым спейсером преобразуется в последовательный индикаторный выход (выход с памятью). Это преобразование реализуется введением дополнительного элемента НЕ между комбинационной частью индикаторного элемента и его внешним выводом и введением двух дополнительных связей. Первая связь обеспечивает подключение комбинационного индикаторного выхода к дополнительным входам триггера (бистабильной ячейке). Вторая связь обеспечивает подключение дополнительного элемента НЕ к дополнительным входам индикаторного элемента, что переводит его из комбинационного класса в последовательный класс. 4 ил.

Самосинхронный динамический однотактный D-триггер с нулевым спейсером, содержащий один инвертор и четыре элемента ИЛИ-И-НЕ, вход управления, однофазный информационный вход, прямую и инверсную составляющие бифазного информационного выхода, выход сигнала управления и индикаторный выход, причем однофазный информационный вход подключен к входу инвертора, второму входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ, первому входу первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ и первому входу первой группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ, вход управления триггера соединен с входом второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ, выход инвертора подключен к первым входам первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ и к первому входу второй группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ соединен со вторыми входами первых групп входов ИЛИ второго и третьего элементов ИЛИ-И-НЕ, с третьими входами первой и второй групп входов ИЛИ четвертого элемента ИЛИ-И-НЕ и выходом сигнала управления триггера, выход второго элемента ИЛИ-И-НЕ подключен к входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, второму входу первой группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ и прямой составляющей бифазного информационного выхода триггера, выход третьего элемента ИЛИ-И-НЕ подключен к входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ, второму входу второй группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ и инверсной составляющей бифазного информационного выхода триггера, отличающийся тем, что в него введены второй инвертор, третьи входы в первые группы входов ИЛИ второго и третьего элементов ИЛИ-И-НЕ и третья группа входов ИЛИ в четвертый элемент ИЛИ-И-НЕ, причем третьи входы первых групп входов ИЛИ второго и третьего элементов ИЛИ-И-НЕ соединены с выходом четвертого элемента ИЛИ-И-НЕ и входом второго инвертора, первый и второй входы третьей группы входов ИЛИ четвертого элемента ИЛИ-И-НЕ подключены к выходам первого элемента ИЛИ-И-НЕ и второго инвертора соответственно, выход второго инвертора соединен с индикаторным выходом триггера.

| САМОСИНХРОННЫЙ ОДНОКРАТНЫЙ D-ТРИГГЕР С ВЫСОКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362266C1 |

| САМОСИНХРОННЫЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С НИЗКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362267C1 |

| САМОСИНХРОННЫЙ D-ТРИГГЕР С ИНДИКАЦИЕЙ ОТКАЗА | 2008 |

|

RU2391771C1 |

| US 6218878 B1, 17.04.2001. | |||

Авторы

Даты

2019-07-02—Публикация

2018-11-21—Подача