Изобретение относится к импульсной и вычислительной технике и может использоваться в качестве базовых элементов при построении самосинхронных триггерных, регистровых и других вычислительных устройств цифровой обработки информации.

Параметры базовых элементов определяют быстродействие, энергопотребление и массогабаритные характеристики устройства, построенного на их основе. Индикация отказа базовых элементов позволяет обнаружить и предотвратить его аппаратный сбой, на предельных режимах работы (ионизирующих излучений, напряжения питания, рабочей температуры).

Существующие в настоящее время самосинхронные D-триггеры обладают рядом недостатков, являющихся следствием их устройства и заключающихся в относительно большой по сравнению с синхронными D-триггерами площади, занимаемой на кристалле, низком быстродействии, связанном с большим временем прохождения сигналов и отсутствием индикации отказа.

Известно устройство «D-триггер с самосинхронной предустановкой» (патент РФ №2319297 от 09.08.2006) того же назначения, что и предлагаемое, но не имеющее с ним общих признаков и содержащее два инвертора, три элемента ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, прямой и инверсный информационные входы с парафазным кодированием, вход установки нуля, вход установки единицы, вход разрешения установки, управляющий вход, прямой информационный выход, инверсный информационный выход и индикаторный выход, инверсный информационный вход подключен к первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ и первому входу третьей группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, прямой информационный вход подключен к третьему входу первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ и третьему входу второй группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, управляющий вход подключен ко входу первого инвертора, выход которого соединен со вторыми входами первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ, вторыми входами вторых групп входов И первого и второго элементов И-ИЛИ-НЕ и вторыми входами второй, третьей и пятой групп входов ИЛИ третьего элемента ИЛИ-И-НЕ, вход установки нуля подключен к первому входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ, вход установки единицы подключен к третьему входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ, вход разрешения установки подключен ко вторым входам вторых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ, выход первого элемента ИЛИ-И-НЕ подключен к первому входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ, первому входу второй группы входов И первого элемента И-ИЛИ-НЕ и первым входам второй и четвертой групп входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход второго элемента ИЛИ-И-НЕ подключен к третьему входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ, первому входу второй группы входов И второго элемента И-ИЛИ-НЕ, второму входу первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ и третьему входу третьей группы входов ИЛИ третьего элемента ИЛИ-И-НЕ, выход второго элемента И-ИЛИ-НЕ подключен ко входу первой группы входов И первого элемента И-ИЛИ-НЕ, первому входу первой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ и прямому информационному выходу, выход первого элемента И-ИЛИ-НЕ подключен ко входу первой группы входов И второго элемента И-ИЛИ-НЕ, второму входу четвертой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ и инверсному информационному выходу, выход третьего элемента ИЛИ-И-НЕ соединен со входом второго инвертора, третьим входом первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ и первым входом первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ, выход второго инвертора подключен к индикаторному выходу и первому входу пятой группы входов ИЛИ третьего элемента ИЛИ-И-НЕ.

Основные недостатки данного устройства заключаются в отсутствии индикации отказа, позволяющей обнаружить и предотвратить аппаратный сбой на предельных режимах работы, относительно большой площади, занимаемой на кристалле, и наличии многоступенчатых цепей последовательной комбинационной логики, что существенно снижает границу быстродействия.

Сущностью изобретения является самосинхронный D-триггер, информационный вход которого содержит как парафазное со спейсером, так и бифазное представление и имеющий выход индикации отказа.

Достигаемый технический результат заключается в повышении надежности цифровых устройств на предельных режимах работы, построенных на базе предлагаемых триггерных элементов, благодаря наличию у последних функции индикации отказа; в снижении площади на кристалле при аппаратной реализации и увеличении быстродействия - за счет уменьшения длины последовательных связей между элементами комбинационной логики.

Сопоставительный анализ с прототипом показывает, что предлагаемое устройство отличается наличием группы новых признаков: первого и второго элементов 2И-4ИЛИ, элемента И, элемента ИЛИ, причем выход первого элемента 2И-4ИЛИ подсоединен к первому входу второй группы и к первому входу третьей группы входов И первого элемента 2И-4ИЛИ, к первому входу элемента И, к первому входу элемента ИЛИ, и является первым информационным выходом триггера; выход второго элемента 2И-4ИЛИ подключен ко второму входу второй группы и ко второму входу третьей группы входов И второго элемента 2И-4ИЛИ, ко второму входу элемента И, ко второму входу элемента ИЛИ и является инверсным информационным выходом триггера. Следовательно, устройство удовлетворяет критерию «новизна».

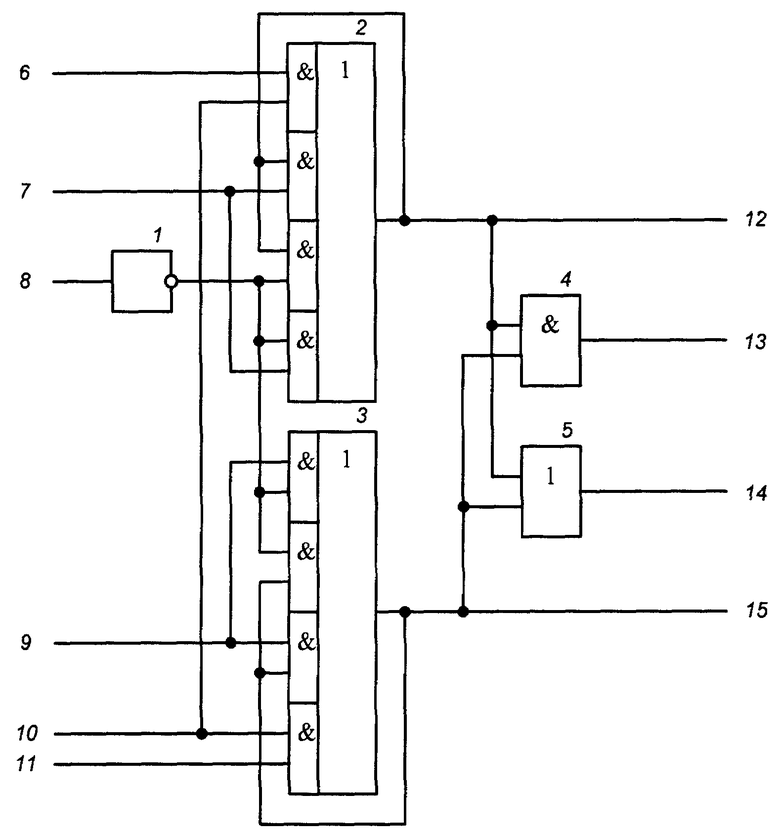

Изобретение поясняется следующими графическими материалами:

чертеж - структурная схема самосинхронного D-триггера с индикацией отказа.

Самосинхронный D-триггер с индикацией отказа состоит из инвертора 1, первого элемента 2И-4ИЛИ 2, второго элемента 2И-4ИЛИ 3, элемента И 4 и элемента ИЛИ 5; причем вход управления 8 триггера является входом инвертора 1, выход которого соединен со вторым входом третьей группы и с первым входом четвертой группы входов И первого элемента 2И-4ИЛИ 2, со вторым входом первой группы и с первым входом второй группы входов И второго элемента 2И-4ИЛИ 3, а выход первого элемента 2И-4ИЛИ 2 подсоединен к первому входу второй группы и к первому входу третьей группы входов И первого элемента 2И-4ИЛИ 2, к первому входу элемента И 4, к первому входу элемента ИЛИ 5 и является первым информационным выходом 12 триггера; выход второго элемента 2И-4ИЛИ 3 подсоединен ко второму входу второй группы и ко второму входу третьей группы входов И второго элемента 2И-4ИЛИ 3, ко второму входу элемента И 4, ко второму входу элемента ИЛИ 5 и является инверсным информационным выходом 15 триггера, причем вход установки единицы 6 триггера является первым входом первой группы входов И первого элемента 2И-4ИЛИ 2, прямой информационный вход 7 триггера является вторым входом второй группы и вторым входом четвертой группы входов И первого элемента 2И-4ИЛИ 2, инверсный информационный вход триггера 9 является первым входом первой группы и первым входом третьей группы входов И второго элемента 2И-4ИЛИ 3; вход разрешения установки 10 триггера является вторым входом первой группы входов И первого элемента 2И-4ИЛИ 2 и первым входом четвертой группы входов И второго элемента 2И-4ИЛИ 3; вход установки нуля 11 триггера является вторым входом четвертой группы входов И второго элемента 2И-4ИЛИ 3; выход элемента ИЛИ 5 является индикаторным выходом 14 триггера, а выход элемента И 4 является выходом индикации отказа 13 триггера.

Устройство работает следующим образом. При подаче на вход управления 8 триггера сигнала логический нуль на выходе инвертора 1 формируется сигнал логической единицы, который поступает на первый и второй элементы 2И-4ИЛИ 2 и 3 соответственно. При подаче данных на прямой 7 или инверсный 9 информационный вход триггера логическая единица поступает соответственно на четвертую группу И элемента 2И-4ИЛИ 2 или первую группу И элемента 2И-4ИЛИ 3, что приводит к появлению сигнала логической единицы на их выходах, а также соответственно на прямом 12 или инверсном 15 выходах триггера, что приводит к появлению сигнала логической единицы на выходе элемента ИЛИ 5 и выходе индикации 14 триггера, сигнализируя об окончании переходных процессов в схеме и появлении стабильного сигнала корректных данных на выходе триггера. При появлении логической единицы на выходе первого 2 и второго 3 элементов 2И-4ИЛИ одновременно происходит формирование сигнала логической единицы на выходе элемента И 4 и выходе индикации отказа 13 триггера, что свидетельствует об аппаратной неисправности схемы, так как при парафазном представлении сигнала такое состояние невозможно. При поступлении сигнала логический нуль на вход управления 8 триггера происходит переключение выходов первого 2 и второго 3 элементов 2И-4ИЛИ в состояние логического нуля, что соответствует сигналу «спейсер» при парафазном представлении сигналов.

Установка логических нуля и единицы триггера производится при подаче сигнала логический нуль на вход управления 8 и сигнала логической единицы на входе разрешения установки 10 триггера. При этом при помощи сигналов установки единицы на входе 6 и установки нуля - на входе 11 триггера возможна установка соответствующих состояний на информационных выходах 12 и 15.

В результате предлагаемое устройство помимо основной функции, выполняемой самосинхронным D-триггером, осуществляет индикацию отказа. Совокупность новых элементов и их соединений позволяет снизить площадь, занимаемую устройством на кристалле, и увеличить его быстродействие.

| название | год | авторы | номер документа |

|---|---|---|---|

| D-ТРИГГЕР С САМОСИНХРОННОЙ ПРЕДУСТАНОВКОЙ | 2006 |

|

RU2319297C1 |

| САМОСИНХРОННЫЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С НИЗКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362267C1 |

| САМОСИНХРОННЫЙ ТРИГГЕР С ОДНОФАЗНЫМ ИНФОРМАЦИОННЫМ ВХОДОМ | 2008 |

|

RU2405246C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ | 2008 |

|

RU2390092C1 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с нулевым спейсером | 2024 |

|

RU2835382C1 |

| САМОСИНХРОННЫЙ ОДНОКРАТНЫЙ D-ТРИГГЕР С ВЫСОКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362266C1 |

| КОМБИНИРОВАННЫЙ Г-ТРИГГЕР С НУЛЕВЫМ СПЕЙСЕРОМ | 2007 |

|

RU2368068C2 |

| ОДНОТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ И ВХОДОМ УПРАВЛЕНИЯ | 2008 |

|

RU2391772C2 |

Изобретение относится к импульсной и вычислительной технике, является базовым элементом цифровой техники и может использоваться при построении самосинхронных триггерных, регистровых и других вычислительных устройств, систем цифровой обработки информации. Достигаемый технический результат - обеспечение самосинхронной реализации D-триггера с индикацией отказа, с парафазным или бифазным представлением информационного входа и парафазным представлением информационного выхода. Самосинхронный D-триггер с индикацией отказа содержит два элемента 2И-4ИЛИ, элемент И, элемент ИЛИ и инвертор. 1 ил.

Самосинхронный D-триггер с индикацией отказа, состоящий из инвертора, первого и второго элементов 2И-4ИЛИ, элемента И, элемента ИЛИ; причем вход управления триггера является входом инвертора, выход которого соединен со вторым входом третьей группы и с первым входом четвертой группы входов И первого элемента 2И-4ИЛИ, со вторым входом первой группы и с первым входом второй группы входов И второго элемента 2И-4ИЛИ, причем вход установки единицы триггера является первым входом первой группы входов И первого элемента 2И-4ИЛИ, прямой информационный вход триггера является вторым входом второй группы и вторым входом четвертой группы входов И первого элемента 2И-4ИЛИ, инверсный информационный вход триггера является первым входом первой группы и первым входом третьей группы входов И второго элемента 2И-4ИЛИ; вход разрешения установки триггера является вторым входом первой группы входов И первого элемента 2И-4ИЛИ и первым входом четвертой группы входов И второго элемента 2И-4ИЛИ; вход установки нуля триггера является вторым входом четвертой группы входов И второго элемента 2И-4ИЛИ; выход элемента ИЛИ является индикаторным выходом триггера, а выход элемента И является выходом индикации отказа триггера, отличающийся тем, что выход первого элемента 2И-4ИЛИ соединен с первым входом второй группы и с первым входом третьей группы входов И первого элемента 2И-4ИЛИ, с первым входом элемента И, с первым входом элемента ИЛИ и является первым информационным выходом триггера; выход второго элемента 2И-4ИЛИ соединен с вторым входом второй группы и со вторым входом третьей группы входов И второго элемента 2И-4ИЛИ, со вторым входом элемента И, со вторым входом элемента ИЛИ и является инверсным информационным выходом триггера.

| D-ТРИГГЕР С САМОСИНХРОННОЙ ПРЕДУСТАНОВКОЙ | 2006 |

|

RU2319297C1 |

| РАЗРЯД САМОСИНХРОННОГО РЕГИСТРА СДВИГА | 2006 |

|

RU2319232C1 |

| Резервированный RS-триггер | 1989 |

|

SU1629962A1 |

| JP 11163686 A, 18.06.1999. | |||

Авторы

Даты

2010-06-10—Публикация

2008-12-04—Подача