Самосинхронный двухтактный триггер с парафазными с единичным спейсером входными и выходными сигналами относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных регистровых и вычислительных устройств, систем цифровой обработки информации.

Из уровня техники известен ряд аналогов заявляемого технического решения. Известен самосинхронный двухтактный триггер с бифазными входами [1, рис. 2.16(б)], содержащий пять элементов И-ИЛИ-НЕ. Недостаток данного триггера - отсутствие информационных выходов в парафазном коде с единичным спейсером.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный двухтактный триггер с парафазным информационным входом с единичным спейсером и бифазным информационным выходом [2, рис. 3.34], содержащий один элемент И-НЕ, один элемент ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, элемент И-ИЛИ-И-НЕ.

Недостаток прототипа - отсутствие парафазного информационного выхода, затрудняющее использование информации, хранимой триггером, его комбинационным окружением, формирующим информационный вход триггера.

Техническая задача, решаемая заявляемым изобретением, заключается в обеспечении возможности использования информации, хранимой триггером, его комбинационным окружением, формирующим информационный вход триггера, за счет ввода элементов, формирующих парафазный с единичным спейсером выход триггера и блокирования входов второй бистабильной ячейки триггера компонентами парафазного выхода в рабочей фазе триггера и его окружения.

Решение поставленной технической задачи достигается тем, что в самосинхронный двухтактный триггер с парафазным информационным входом с единичным спейсером, содержащий один элемент И-НЕ, один элемент ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, элемент И-ИЛИ-И-НЕ, парафазный информационный вход с единичным спейсером, вход асинхронного сброса и индикаторный выход, причем прямая компонента парафазного входа подключена к входу второй группы входов ИЛИ элемента ИЛИ-И-НЕ, ко второму входу первой группы входов И первого элемента И-ИЛИ-НЕ и первому входу третьей группы входов И элемента И-ИЛИ-И-НЕ, инверсная компонента парафазного входа подключена ко вторым входам элемента И-НЕ, первой группы входов И второго элемента И-ИЛИ-НЕ и первой группы входов И элемента И-ИЛИ-И-НЕ, вход асинхронного сброса соединен с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ, выход которого подключен к первым входам элемента И-НЕ и первой группы входов И первого элемента И-ИЛИ-НЕ, а также к входу второй группы входов И элемента И-ИЛИ-И-НЕ, выход элемента И-НЕ соединен со вторым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ, первым входом первой группы входов И второго элемента И-ИЛИ-НЕ и входом четвертой группы входов И элемента И-ИЛИ-И-НЕ, выход первого элемента И-ИЛИ-НЕ подключен к входу второй группы входов И второго элемента И-ИЛИ-НЕ и первому входу первой группы входов И элемента И-ИЛИ-И-НЕ, выход второго элемента И-ИЛИ-НЕ соединен с входом второй группы входов И первого элемента И-ИЛИ-НЕ и со вторым входом третьей группы входов И элемента И-ИЛИ-И-НЕ, выход которого подключен к индикаторному выходу триггера, первая и вторая группы входов И элемента И-ИЛИ-И-НЕ объединяются первой группой ИЛИ второго каскада элемента И-ИЛИ-И-НЕ, третья и четвертая группы входов И элемента И-ИЛИ-И-НЕ объединяются второй группой ИЛИ второго каскада элемента И-ИЛИ-И-НЕ, введены второй и третий элементы И-НЕ, парафазный информационный выход с единичным спейсером и вход управления фазой триггера, причем вход управления фазой подключен к первым входам второго и третьего элементов И-НЕ, второй вход второго элемента И-НЕ подключен к выходу первого элемента И-ИЛИ-НЕ, а его выход подключен к прямой компоненте парафазного выхода триггера и третьему входу первой группы входов И первого элемента И-ИЛИ-НЕ, второй вход третьего элемента И-НЕ подключен к выходу второго элемента И-ИЛИ-НЕ, а его выход подключен к инверсной компоненте парафазного выхода триггера и третьему входу первой группы входов И второго элемента И-ИЛИ-НЕ.

Предлагаемое устройство триггера обладает существенными признаками, отличающими его от прототипа и находящимися в причинно-следственной связи с достигаемым техническим результатом. Действительно, использование элементов И-НЕ для формирования парафазного сигнала с единичным спейсером известно, например, в [2, Fig. 3.13(a)]. Но простое подключение элементов И-НЕ к бифазным выходам триггера не обеспечивает самосинхронности использования парафазного информационного выхода триггера его комбинационным окружением. Только подключение третьих входов первых групп входов И первого и второго элементов И-ИЛИ-НЕ к выходам второго и третьего элементов И-НЕ позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные и функциональные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия и обладающим изобретательским уровнем.

Понятие "парафазный", используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя компонентами - парой переменных  которые в активной фазе имеют взаимоинверсные значения:

которые в активной фазе имеют взаимоинверсные значения:  Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ осуществления перехода парафазного сигнала между его состояниями предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если в качестве спейсерного используется состояние  то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние

то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние  то - парафазный сигнал с единичным спейсером. Спейсерное состояние - статическое состояние, переключение в которое в самосинхронной схемотехнике должно фиксироваться индикатором окончания переходного процесса, в данном случае - окончания переключения в спейсерное состояние. Традиционно парафазный сигнал со спейсером имеет только одно спейсерное состояние.

то - парафазный сигнал с единичным спейсером. Спейсерное состояние - статическое состояние, переключение в которое в самосинхронной схемотехнике должно фиксироваться индикатором окончания переходного процесса, в данном случае - окончания переключения в спейсерное состояние. Традиционно парафазный сигнал со спейсером имеет только одно спейсерное состояние.

Второй способ осуществления перехода парафазного сигнала между его состояниями предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние:  называемое транзитным состоянием.

называемое транзитным состоянием.

В материалах данной заявки речь идет об использовании в качестве информационного входа и информационного выхода триггера парафазного сигнала с единичным спейсером, в дальнейшем - просто парафазного сигнала. Именно использование в качестве информационного входа и информационного выхода триггера парафазного сигнала с единичным спейсером представляет собой существенный отличительный признак заявленного изобретения, который обеспечивает решение поставленной технической задачи.

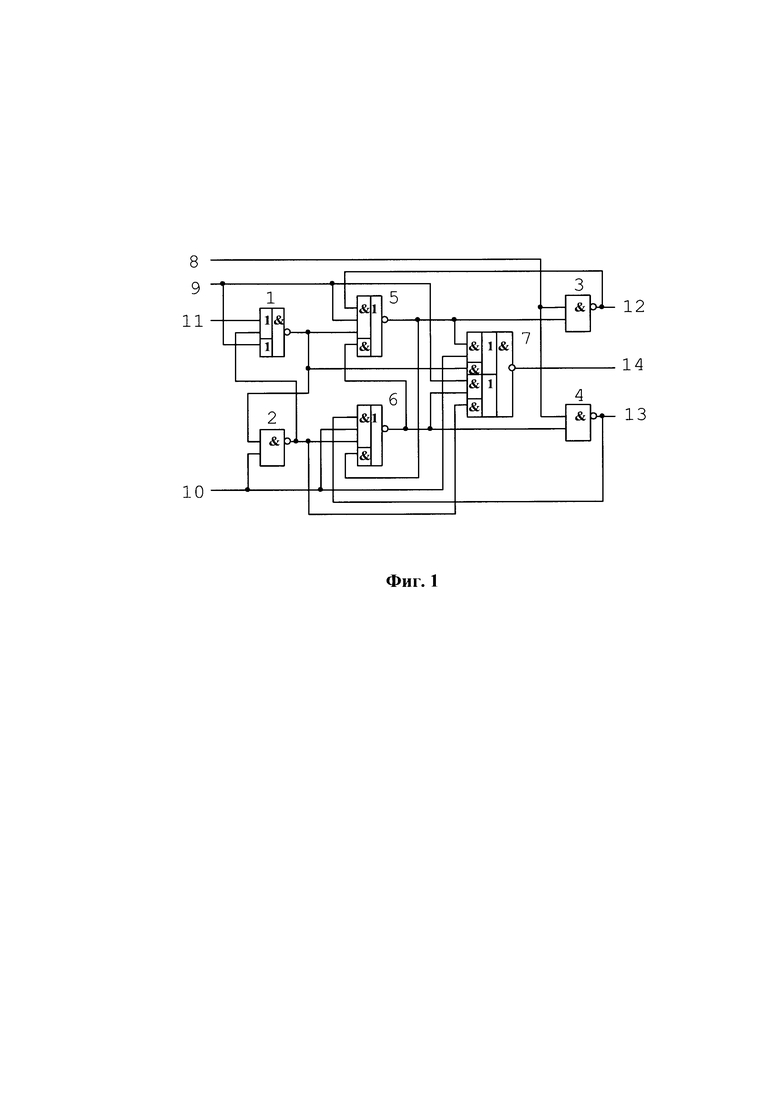

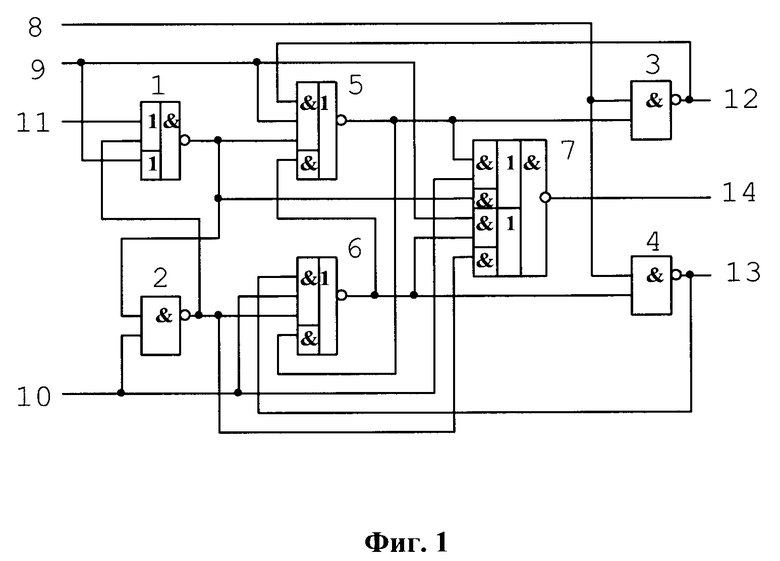

На Фиг. 1 представлена схема самосинхронного двухтактного триггера с парафазным выходом с единичным спейсером, содержащего элемент ИЛИ-И-НЕ 1, три элемента И-НЕ 2-4, два элемента И-ИЛИ-НЕ 5-6, элемент И-ИЛИ-И-НЕ 7, вход управления фазой триггера 8, прямую 9 и инверсную 10 компоненты парафазного информационного входа, вход асинхронного сброса 11, прямую 12 и инверсную 13 компоненты парафазного информационного выхода с единичным спейсером и индикаторный выход 14, причем прямая компонента парафазного входа 9 подключена к входу второй группы входов ИЛИ элемента ИЛИ-И-НЕ 1, ко второму входу первой группы входов И элемента И-ИЛИ-НЕ 5 и первому входу третьей группы входов И элемента И-ИЛИ-И-НЕ 7, инверсная компонента парафазного входа 10 подключена ко вторым входам элемента И-НЕ 2, первой группы входов И элемента И-ИЛИ-НЕ 6 и первой группы входов И элемента И-ИЛИ-И-НЕ 7, вход асинхронного сброса 11 соединен с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ 1, выход которого подключен к первому входу элемента И-НЕ 2, первому входу первой группы входов И элемента И-ИЛИ-НЕ 5 и входу второй группы входов И элемента И-ИЛИ-И-НЕ 7, выход элемента И-НЕ 2 соединен со вторым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ 1, первым входом первой группы входов И элемента И-ИЛИ-НЕ 6 и входом четвертой группы входов И элемента И-ИЛИ-И-НЕ 7, выход элемента И-ИЛИ-НЕ 5 подключен к входу второй группы входов И элемента И-ИЛИ-НЕ 6, первому входу первой группы входов И элемента И-ИЛИ-И-НЕ 7 и второму входу элемента И-НЕ 3, выход элемента И-ИЛИ-НЕ 6 соединен с входом второй группы входов И элемента И-ИЛИ-НЕ 5, со вторым входом третьей группы входов И элемента И-ИЛИ-И-НЕ 7 и вторым входом элемента И-НЕ 4, выход элемента И-ИЛИ-И-НЕ 7 подключен к индикаторному выходу 14 триггера, первая и вторая группы входов И элемента И-ИЛИ-И-НЕ 7 объединяются первой группой ИЛИ второго каскада элемента И-ИЛИ-И-НЕ 7, третья и четвертая группы входов И элемента И-ИЛИ-И-НЕ 7 объединяются второй группой ИЛИ второго каскада элемента И-ИЛИ-И-НЕ 7, вход управления фазой 8 подключен к первым входам элементов И-НЕ 3 и 4, выход элемента И-НЕ 3 подключен к третьему входу первой группы входов И элемента И-ИЛИ-НЕ 5 и прямой компоненте 12 парафазного выхода триггера, выход элемента И-НЕ 4 подключен к инверсной компоненте 13 парафазного выхода триггера и третьему входу первой группы входов И элемента И-ИЛИ-НЕ 6.

Парафазный вход и парафазный выход триггера имеют единичный спейсер.

Схема работает следующим образом. Пусть парафазный информационный вход триггера находится в рабочем состоянии, например, "10" (прямая компонента 9 в логической единице, а инверсная компонента 10 в логическом нуле), вход управления фазой 8 тоже имеет рабочее значение логической единицы, а бистабильная ячейка на элементах И-ИЛИ-НЕ 5-6 хранит предыдущее рабочее состояние триггера, например, "01" (на выходе элемента И-ИЛИ-НЕ 5 уровень логического нуля, на выходе элемента И-ИЛИ-НЕ 6 уровень логической единицы). Высокий уровень на входе 8 разрешает формирование рабочего состояния "10" на парафазном выходе 12-13, которое может использоваться комбинационным окружением триггера, в том числе и для формирования рабочего состояния его парафазного информационного входа 9-10. Индикаторный выход 14 высоким уровнем подтверждает пребывание триггера в рабочей фазе. Переключение входа управления 8 в логический нуль заставляет парафазный выход триггера 12-13 перейти в единичный спейсер, разрешая тем самым окружению переключить в спейсерное состояние парафазный вход 9-10, что, в свою очередь, разрешает запись состояния первой бистабильной ячейки триггера на элементах 1-2 во вторую бистабильную ячейку на элементах 5-6. Индикаторный выход 14 низким уровнем подтверждает переход триггера в спейсерную фазу.

Отличительные особенности данной схемы по сравнению с прототипом состоят в следующем.

Парафазный информационный выход триггера, формируемый элементами 3 и 4, за счет обратной связи на входы второй бистабильной ячейки, образованной элементами 5 и 6, разрешает изменение ее состояния только при своем спейсерном состоянии. Эти связи обеспечивают самосинхронность переключения триггера из одной фазы в противоположную и возможность использования парафазного выхода триггера его комбинационным окружением для формирования парафазного входа триггера без нарушения самосинхронности.

Таким образом, предлагаемое устройство обеспечивает самосинхронность переключения триггера из одной фазы в противоположную и возможность использования парафазного выхода триггера с единичным спейсером его комбинационным окружением для формирования парафазного входа триггера без нарушения самосинхронности. Тем самым обеспечивается решение поставленной технической задачи. Цель изобретения достигнута.

Источники:

[1] Астановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы / Под ред. В.И. Варшавского. - М.: Наука. Гл. ред. физ.-мат.лит., 1976. - 424 с.

[2] Степченков Ю.А., Денисов А.Н., Дьяченко Ю.Г., Гринфельд Ф.И., Филимоненко О.П., Морозов Н.В., Степченков Д.Ю., Плеханов Л.П. Библиотека функциональных ячеек для проектирования самосинхронных полузаказных БМК микросхем серий 5503/5507. М.: Техносфера. 2017. 367 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с нулевым спейсером | 2024 |

|

RU2835382C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693319C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| ДВУХТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ | 2008 |

|

RU2390923C1 |

| Формирователь парафазного сигнала с единичным спейсером | 2019 |

|

RU2718220C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693318C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С НУЛЕВЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693321C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С НУЛЕВЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693320C1 |

| Формирователь парафазного сигнала с нулевым спейсером | 2019 |

|

RU2718221C1 |

| ДВУХТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ И ВХОДОМ УПРАВЛЕНИЯ | 2008 |

|

RU2390093C1 |

Изобретение относится к импульсной и вычислительной технике. Технический результат - обеспечение самосинхронности переключения триггера из одной фазы в противоположную и возможность использования парафазного выхода триггера с единичным спейсером без нарушения самосинхронности. Для этого предложен самосинхронный двухтактный триггер с парафазным выходом с единичным спейсером, содержащий один элемент И-НЕ, один элемент ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, элемент И-ИЛИ-И-НЕ, парафазный информационный вход с единичным спейсером, вход асинхронного сброса и индикаторный выход. При этом в схему введены второй и третий элементы И-НЕ, парафазный информационный выход с единичным спейсером и вход управления фазой триггера, причем вход управления фазой подключен к первым входам второго и третьего элементов И-НЕ, второй вход второго элемента И-НЕ подключен к выходу первого элемента И-ИЛИ-НЕ, а его выход подключен к прямой компоненте парафазного выхода триггера и третьему входу первой группы входов И первого элемента И-ИЛИ-НЕ, второй вход третьего элемента И-НЕ подключен к выходу второго элемента И-ИЛИ-НЕ, а его выход подключен к инверсной компоненте парафазного выхода триггера и третьему входу первой группы входов И второго элемента И-ИЛИ-НЕ. 1 ил.

Самосинхронный двухтактный триггер с парафазным выходом с единичным спейсером, содержащий один элемент И-НЕ, один элемент ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, элемент И-ИЛИ-И-НЕ, парафазный информационный вход с единичным спейсером, вход асинхронного сброса и индикаторный выход, причем прямая компонента парафазного входа подключена к входу второй группы входов ИЛИ элемента ИЛИ-И-НЕ, ко второму входу первой группы входов И первого элемента И-ИЛИ-НЕ и первому входу третьей группы входов И элемента И-ИЛИ-И-НЕ, инверсная компонента парафазного входа подключена ко вторым входам элемента И-НЕ первой группы входов И второго элемента И-ИЛИ-НЕ и первой группы входов И элемента И-ИЛИ-И-НЕ, вход асинхронного сброса соединен с первым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ, выход которого подключен к первому входу элемента И-НЕ, первому входу первой группы входов И первого элемента И-ИЛИ-НЕ и входу второй группы входов И элемента И-ИЛИ-И-НЕ, выход элемента И-НЕ соединен со вторым входом первой группы входов ИЛИ элемента ИЛИ-И-НЕ, первым входом первой группы входов И второго элемента И-ИЛИ-НЕ и входом четвертой группы входов И элемента И-ИЛИ-И-НЕ, выход первого элемента И-ИЛИ-НЕ подключен к входу второй группы входов И второго элемента И-ИЛИ-НЕ и первому входу первой группы входов И элемента И-ИЛИ-И-НЕ, выход второго элемента И-ИЛИ-НЕ соединен с входом второй группы входов И первого элемента И-ИЛИ-НЕ и со вторым входом третьей группы входов И элемента И-ИЛИ-И-НЕ, выход которого подключен к индикаторному выходу триггера, первая и вторая группы входов И элемента И-ИЛИ-И-НЕ объединяются первой группой ИЛИ второго каскада элемента И-ИЛИ-И-НЕ, третья и четвертая группы входов И элемента И-ИЛИ-И-НЕ объединяются второй группой ИЛИ второго каскада элемента И-ИЛИ-И-НЕ, отличающийся тем, что в схему введены второй и третий элементы И-НЕ, парафазный информационный выход с единичным спейсером и вход управления фазой триггера, причем вход управления фазой подключен к первым входам второго и третьего элементов И-НЕ, второй вход второго элемента И-НЕ подключен к выходу первого элемента И-ИЛИ-НЕ, а его выход подключен к прямой компоненте парафазного выхода триггера и третьему входу первой группы входов И первого элемента И-ИЛИ-НЕ, второй вход третьего элемента И-НЕ подключен к выходу второго элемента И-ИЛИ-НЕ, а его выход подключен к инверсной компоненте парафазного выхода триггера и третьему входу первой группы входов И второго элемента И-ИЛИ-НЕ.

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| КОМБИНИРОВАННЫЙ Г-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2010 |

|

RU2434318C1 |

| САМОСИНХРОННЫЙ ТРИГГЕР С ОДНОФАЗНЫМ ИНФОРМАЦИОННЫМ ВХОДОМ | 2008 |

|

RU2405246C2 |

| Устройство для контроля магнитных сердечников | 1980 |

|

SU905892A1 |

Авторы

Даты

2025-02-12—Публикация

2024-09-13—Подача