Изобретение относится к цифровой технике в области обмена информацией и может быть использовано в космической, авиационной, кораблестроительной и др. отраслях в качестве интерфейса обмена информацией между контроллером и оконечным устройством (ОУ).

Асинхронный последовательный интерфейс обмена (ИО) предназначен для обмена информацией между контроллером и одним оконечным устройством (радиальным) или несколькими оконечными устройствами (магистральными с гальванической развязкой). Обмен информацией ведется 32-х разрядными словами, разделенными на байты и дополненными стартовым и стоповым битами. Инициализатором обмена всегда выступает контроллер, который выдает командное слово (КС) для ОУ. В КС передается код операции (КОП), адрес ОУ и количество слов для обмена. Получив КС, ОУ сравнивает адрес в КС с собственным адресом, после чего выполняет его (адрес совпадает) или игнорирует (чужой адрес). Если в КОП заложена операция приема, то ОУ принимает указанное в КС количество слов данных (СД), если операция выдачи, то ОУ выдает указанное количество СД.

Наиболее близкими аналогами способа являются радиальный интерфейс RS232 и магистральный интерфейс RS485 (А. Лапин, Интерфейсы. Выбор и реализация - М.: Техносфера, 2005, стр. 46-53). Данные интерфейсы универсальны, имеют набор стандартных скоростей обмена, при использовании гальванической развязки (RS485) возможно передавать информацию на расстояние до 1200 м. Недостатками данных интерфейсов являются малая скорость обмена на стандартном ряде частот, а также использование стандартного ряда частот не кратного 1 кГц, что существенно усложняет процесс синхронизации с тактовой частотой процессора, кратной 1 МГц.

Прототипом контроллера и оконечного устройства является контроллер для выдачи и приема информации по последовательному асинхронному интерфейсу, представленные в пособии к курсам «Микропроцессорная техника» и «Автоматизированные системы для научных исследований» Ершова Н.Ю., Ивашенков О.Н., Курсков С.Ю. «Микропроцессоры» (http://dfe.petrsu.ru/koi/posob/microcpu/index.html) на рис. 3.8 и 3.9. Недостатками аналогов является отсутствие возможности передачи информации с минимальным количеством сигналов между устройствами.

Задача изобретения - создание надежного асинхронного интерфейса и необходимых для его работы контроллера и ОУ, которые обеспечат обмен 32-х разрядными словами с высокой скоростью передачи информации с минимальным количеством сигналов между устройствами.

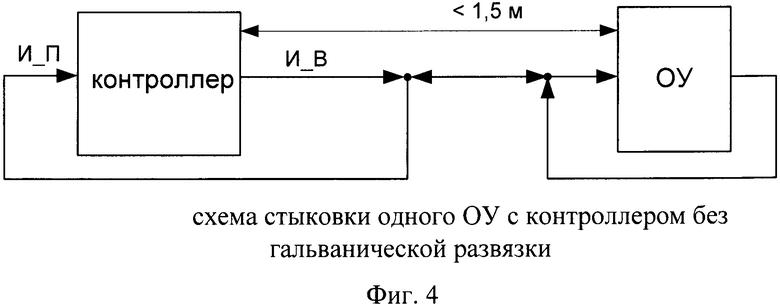

Для решения задачи был разработан способ и устройства (контроллер и ОУ), предназначенные для обмена информацией без гальванической развязки и расположенные на расстоянии до 1,5 метров. Возможно введение гальванической развязки, что увеличивает расстояние до 10 метров.

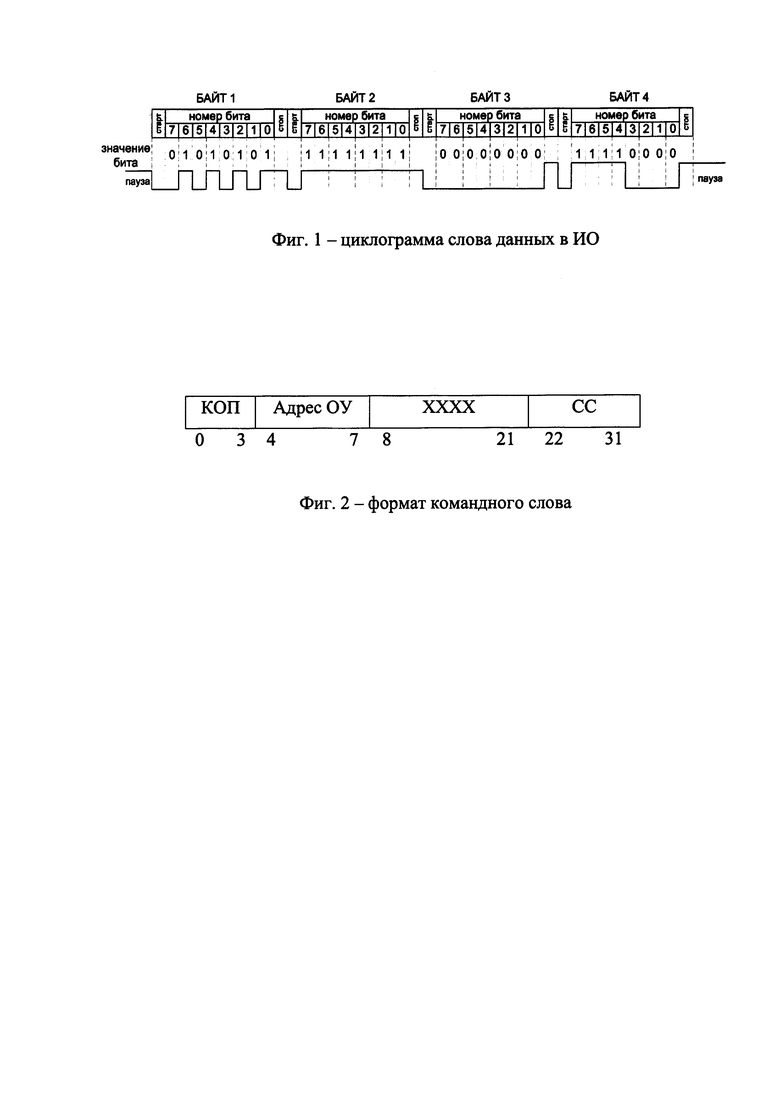

Асинхронный последовательный интерфейс обмена устанавливает следующие правила взаимодействия контроллера и ОУ: обмен всегда ведется 32-х разрядными словами, разделенными на байты, каждый байт сопровождается одним стартовым и одним стоповым битами и выдается последовательным кодом младшими разрядами вперед, начиная со старшего байта.

Информация передается на частоте 4 МГц. Скорость передачи одного информационного, стартового или стопового бита 0,25 мкс. Скорость обмена 4 Мбод. Стартовый бит всегда передается низким уровнем, стоповый - высоким уровнем. Отсутствие данных (пауза) передается высоким уровнем.

При использовании гальванической развязки, ИО работает как магистральный, т.е. к одному контроллеру можно подключить до 16 ОУ. Подключение двух контроллеров на одну магистраль не допускается, а каждому ОУ присваиваться персональный адрес в магистрали. Максимальное количество слов в одной посылке 1023.

На фигуре 1 представлена циклограмма одного СД в ИО.

Контроллер выполняет следующие основные функции:

- осуществляет сопряжение абонентов интерфейса с линией передачи информации (ЛПИ);

- управляет обменом информацией с помощью КС;

- осуществляет контроль принимаемой информации. ОУ выполняет следующие основные функции:

- осуществляет сопряжение абонентов интерфейса с ЛПИ;

- осуществляет контроль принимаемой информации;

- выполняет адресованные ему команды контроллером.

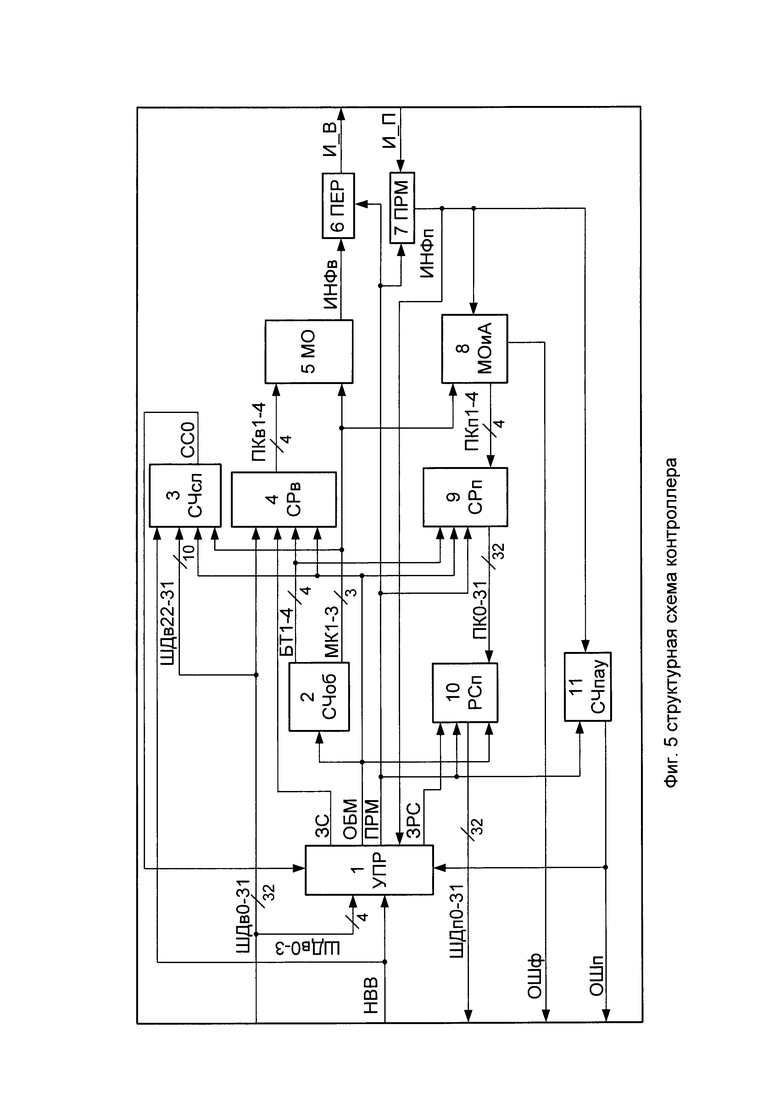

Контроллер всегда является инициатором обмена. После инициализации контроллера на обмен информацией, сначала контроллер выдает КС, затем без пауз выдает СД (операция выдачи), либо встает в ожидание СД от ОУ (операция приема). Время ожидания СД от ОУ<16 мкс. Отсутствие СД более 16 мкс расценивается контроллером как отсутствие ответа от ОУ, в этом случае контроллер заканчивает обмен с признаком ошибки. КС состоит из одного 32-х разрядного слова. Если контроллер или ОУ при приеме информации обнаруживают нарушение условия старт (низкий уровень), стоп (высокий уровень), то такой обмен маркируется признаком ошибки, но продолжается до полного приема информации.

Формат КС представлен на фигуре 2, где:

0-3 разряды - код выполняемой операции (КОП). «1010» - выдача, «1100» - прием.

4-7 разряды - персональный адрес ОУ в магистрали, к которому обращается контроллер.

8-21 разряды - резервные, могут быть использованы для конкретных задач, в соответствии с программным протоколом. «0» - отсутствие признака, «1» - наличие признака.

22-31 разряды - счетчик слов (СС). Количество 32-х разрядных слов подлежащих обмену (максимум 1023).

На фигуре 3 представлены временные диаграммы операций приема и выдачи информации.

На время приема информации выходные информационные сигналы контроллера и ОУ устанавливаются в третье состояние. Это дает возможность упростить схему стыковки одного ОУ с контроллером. Схема такой стыковки представлена на фигуре 4. Схема стыковки ИО с гальванической развязкой зависит от типа приемо-передающих устройств.

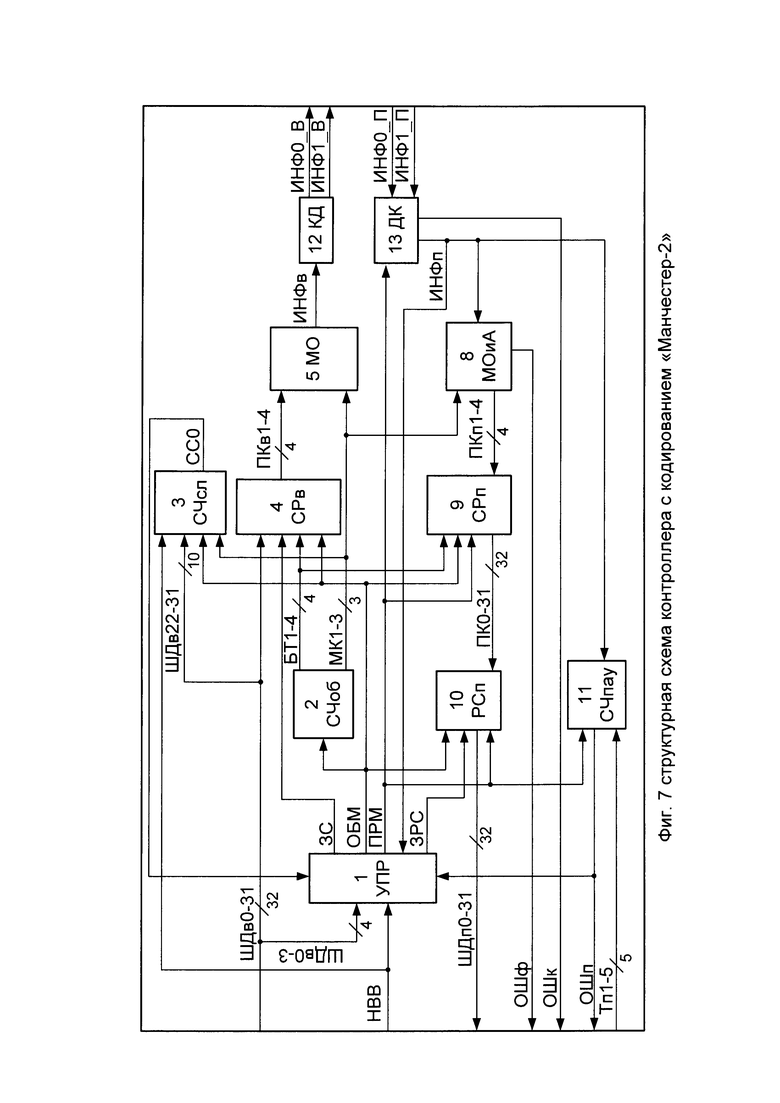

Поскольку, известные устройства не подходят для работы по ИО, был разработан контроллер, схема которого представлена на фигуре 5 и включает в себя следующие элементы:

1 - блок управления (УПР);

2 - счетчик обмена (СЧоб);

3 - счетчик слов (СЧсл);

4 -сдвиговый регистр выдачи (СРв);

5 - блок мультиплексирования обмена (МО);

6 - блок выходной информации с включением 3-го состояния (ПЕР);

7 - блок приема информации (ПРМ);

8 - блок мультиплексирования и анализа приема информации (МОиА);

9 - сдвиговый регистр приема (СРп);

10 - регистр принятого слова (РСп);

11 - счетчик паузы ожидания слова данных (СЧпау).

Элементы структурной схемы контроллера имеют следующие связи:

На контроллер поступают: сигнал начала ввода-вывода (НВВ), 32-х разрядный сигнал на выдачу информации (ШДв0-31), информация приема (И_П). На выход контроллера поступают: 32-х разрядный сигнал принятой информации (ШДп0-31), информация выдачи (И_В), признак ошибки формата обмена (ОШф) (старт - стоп) при приеме СД от ОУ, признак ошибки ожидания (ОШп) СД от ОУ (>16 мкс).

32-х разрядный сигнал ШДв0-31 поступает на СРв (4), его 0-3 разряды дополнительно поступают на УПР (1), а разряды 22-31 - на СЧсл (3).

Сигнал НВВ поступает на УПР (1) и СЧсл (3). Когда СЧсл (3) становится равным нулю, вырабатывается сигнал счетчик слов равен нулю (СС0), который поступает на УПР (1).

Из УПР (1) вырабатываются сигналы: загрузка слова (ЗС), который поступает на СРв (4); обмен (ОБМ), который поступает на СЧоб (2), СЧсл (3), СРв (4), СРп (9), РСп (10); прием (ПРМ), который поступает на ПЕР (6), ПРМ (7), СРп (9), РСп (10), СЧпау (11); загрузка регистра слова (ЗРС), который поступает на РСп (10).

СЧоб (2) связан: 4-х разрядным сигналом байт (БТ1-4) с СРв (4) и СРп (9); 3-х разрядным сигналом маркеров (МК1-3) с СЧсл (3), МО (5) и МОиА (8), который вырабатывает сигнал ОШф и связан 4-х разрядным сигналом последовательного кода приема (ПКп1-4) с СРп (9), который связан 32-х разрядным сигналом параллельного кода ПК0-31 с РСп (10), из которого на выход схемы поступает 32-х разрядный сигнал ШДп0-31.

СРв (4) связан с 4-х разрядным сигналом последовательного кода выдачи (ПКв1-4) с МО (5), связанный сигналом информации на выдачу (ИНФв) с ПЕР (6), который генерирует выходной сигнал И_В.

Сигнал И_П поступает на ПРМ (7), который вырабатывает сигнал информации на прием (ИНФп), поступающий на УПР (1), МОиА (8) и СЧпау (11), из которого вырабатывается выходной сигнал ОШп, также поступающий на УПР (1).

Принцип работы контроллера:

На фигуре 6 представлена блок схема работы контроллера. Все блоки контроллера работают на частоте 4 МГц, кроме блока ПРМ (7), который работает на частоте 16 МГц, из-за чего он не теряет принимаемую информацию.

Операция выдачи для контроллера:

По сигналу НВВ происходит инициализация контроллера на работу и в УПР (1) загружается код операции (0-3 разряды ШДв). Если эти разряды равны «1010», то УПР (1) настраивается на операцию вывода информации. Так же по сигналу НВВ в СЧсл (3) загружается количество слов для обмена (22-31 разряды ШДв), к количеству слов добавляется еще одно слово (КС).

Далее УПР (1) вырабатывает сигнал ОБМ - признак начала обмена, по которому начинает считать счетчик СЧоб (2), и снимается сброс с СРв (4) и СЧсл (3). Так же из УПР (1) вырабатывается сигнал ЗС, по которому происходит параллельная загрузка сдвигового регистра СРв (4).

После параллельной загрузки СРв (4), счетчик СЧоб (2) начинает считать байты информации - сигналы БТ1-4, которые подаются на сдвиговый регистр СРв (4). Сигналы БТ1-4 поочередно встают в высокий уровень на время выдачи нужного байта информации и поочередно выдвигают из СРв (4) информацию. Переключение сигналов БТ1-4 между собой разделены паузами в 2 бита (для формата старт - стоп). Таким образом на выходе СРв (4) мы имеем 4 сигнала ПКв1-4 на которых побайтно, в последовательном коде, младшими разрядами вперед выдвигается информация (КС).

Так же из СЧоб (2) вырабатывается 3 управляющих сигнала МК1-3, которые поступают на мультиплексор обмена МО (5). Эти сигналы в МО (5) мультиплексируют сигналы ПКв1-4 и добавляют стартовый (низкий уровень) и столовый (высокий уровень) биты. На выходе из МО (5) информация получается в последовательном коде в соответствии с фигурой 1 и 3.

Через блок ПЕР (6), в операциях выдачи, информация проходит без изменений и выходит из схемы по сигналу И_В.

По концу выдачи КС, по управляющим сигналам МК1-3 из СЧсл (3) вычитается единица. Если СЧсл (3) не равен нулю, после вычитания единицы, то начинается выдача первого СД аналогично выдачи КС и так до момента пока СЧсл (3) не досчитает до нуля.

Когда СЧсл (3) становится равным нулю, вырабатывается сигнал ССО, который поступает на УПР (1). После обработки этого сигнала УПР (1) снимает сигнал ОБМ и перестает вырабатывать сигнал ЗС. СЧоб (2), СРв (4), СЧсл (3) при снятии сигнала ОБМ сбрасываются и устанавливаются в начальное состояние. Выдача информации закончена.

Операция приема для контроллера:

Выдача КС при операциях обмена аналогична выдачи КС в операциях выдачи. Код при загрузке ШДв0-3 в УПР (1) должен быть «1100»

После выдачи КС вычитается единица из СЧсл (3) аналогично операции выдачи. Далее, если СЧсл (3) равен нулю, то обмен заканчивается аналогично операции выдачи.

Если СЧсл (3) не равен нулю, то после выдачи КС схема переходит к выполнению операции приема. УПР (1) вырабатывает сигнал ПРМ, по которому ПЕР (6) устанавливает выходной сигнал И_В в 3-е состояние. Блок ПРМ (7) по соответствующему сигналу ПРМ открывается на прием сигнала И_П. Так же снимается сброс с СРп (9), РСп (10) и начинает считать счетчик паузы СЧпау (11). Так же снимается сигнал ОБМ и перестает считать счетчик обмена СЧоб (2).

Информация на сигнале И_П в блоке ПРМ (7) переписывается частотой 16 МГц и выходит на сигнал ИНФп. Если СЧпау (11) отсчитал 16 мкс, а низкий уровень (стартовый бит) на сигнале ИНФп не появился, то СЧпау (11) вырабатывает сигнал ошибка приема (нет ответа от абонента) ОШп, который идет на выход схемы и в УПР (1). УПР (1) по сигналу ОШп сбрасывается и устанавливается в ожидание новой инициализации по сигналу НВВ. Сигнал ПРМ снимается, обмен закончен.

Если информация от ОУ поступает раньше 16 мкс, то СЧпау (11) сбрасывается по сигналу ИНФп, а УПР (1) вырабатывает сигнал ОБМ, по которому начинает считать счетчик СЧоб (2) и вырабатывать сигналы БТ1-4 и МК1-3 (аналогично операции выдачи). Сигнал ИНФп также поступает на МОиА (8), в котором с помощью управляющих сигналов МК1-3 параллельный код с ИНФп мультиплексируется в 4 сигнала в последовательном коде по одному байту (ПКп1-4). Так же с помощью сигналов МК1-3 в МОиА (8) анализируется наличие низкого уровня на стартовом и высокого на стоповом битах. Если формат старт (низкий уровень), стоп (высокий) не соблюдается, то МОиА (8) вырабатывает сигнал ошибка формата ОШф, который идет на выход схемы.

Не зависимо от того нарушен ли формат старт - стоп, прием продолжается до полного приема запрошенного количества слов.

Четыре принятые МОиА (8) байта, в параллельном коде ПКп1-4, загружаются в СРп (9) с помощью сигналов БТ1-4. Для сохранения принятого СД, на время приема следующего, информация в параллельном коде (сигнал ПК0-31) переписывается в РСп (10) по сигналу ЗРС. Из РСп (10) сигнал ШДп0-31 выходит из схемы.

После приема СД, по управляющим сигналам МК1-3 из СЧсл (3) вычитается единица. Если СЧсл (3) не равен нулю, после вычитания единицы, то продолжается прием следующего СД и так до момента пока СЧсл (3) не досчитает до нуля.

Когда СЧсл (3) становится равным нулю, вырабатывается сигнал СС0, который поступает на УПР (1). После обработки этого сигнала УПР (1) снимает сигнал ОБМ и перестает вырабатывать сигнал ЗРС. СЧоб (2), СРп (4), СЧсл (3) при снятии сигнала ОБМ сбрасываются и устанавливаются в начальное состояние. Прием информации закончен.

Для увеличения расстояния от контроллера до ОУ в ИО вводится схема кодирования входа/выхода по коду «Манчестер-2» (Лапин А. Интерфейсы. Выбор и реализация - М.: Техносфера, 2005, стр. 101-107). На фигуре 7 представлена структурная схема контроллера с кодированием информации по «Манчестер-2». Для УО, с хорошей помехозащищенностью и гарантированной работой магистрального ИО на расстояние до 50 м с гальванической развязкой, рабочая частота снижена с 4 МГц до 1 МГц (длительность одного бита равна 1 мкс) и применена схема построения гальванической развязки, в соответствии с магистральным интерфейсом по ГОСТ Р 52070-2003.

Структурная схема контроллера с кодом «Манчестер-2» приведена на фиг. 7 и имеет следующие отличия:

1. Вместо ПЕР (6) введен кодер КД (12), для кодирования выходной информации по коду «Манчестер-2».

2. Вместо ПРМ (7) введен декодер ДК (13), для декодирования входной информации по коду «Манчестер-2».

3. Сигнал ПРМ не поступает на КД (12).

4. Сигнал информация выдачи И_В заменен на два сигнала ИНФ0_В, ИНФ_1 В закодированные по коду «Манчестер-2» и поступающие из КД (12) на выход схемы.

5. Сигнал информация приема И_П заменен на два сигнала ИНФ0_П, ИНФ1_П закодированные по коду «Манчестер-2» и поступающие на ДК(13).

6. Введен сигнал ошибка кодирования (ОШк), который вырабатывается ДК (13) в операциях приема при нарушении кодирования по «Манчестер-2» и который выходит из схемы.

7. Для увеличения паузы ожидания СД от ОУ более 16 мкс в схему введен сигнал длительности паузы (Тп1-5), который поступает на СЧпау (11). В зависимости от кода, заданного в этом сигнале, время ожидание аппаратно или программно настраиваемое и может равняться 16, 32, 64, 128 мкс или более.

Оконечное устройство для работы по интерфейсу обмена.

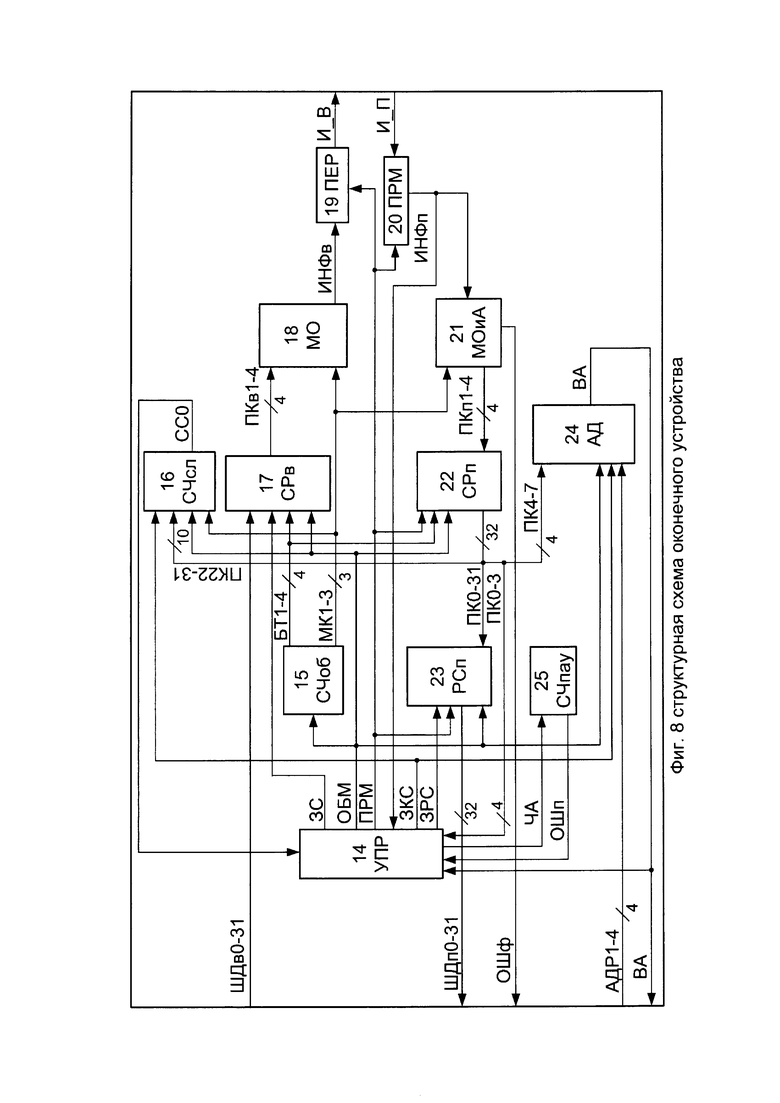

На фиг. 8 представлена структурная схема ОУ для работы по ИО включающего в себя следующие элементы:

14 - блок управления (УПР);

15 - счетчик обмена (СЧоб);

16 - счетчик слов (СЧсл);

17 - сдвиговый регистр выдачи (СРв);

18 - блок мультиплексирования обмена (МО);

19 - блок выходной информации с включением 3-го состояния (ПЕР);

20 - блок приема информации (ПРМ);

21 - блок мультиплексирования и анализа приема информации (МОиА);

22 - сдвиговый регистр приема (СРп);

23 - регистр принятого слова (РСп);

24 - блок сравнения адреса (АД);

25 - счетчик паузы ожидания слова данных от других оконечных устройств (СЧпау).

Элементы структурной схемы ОУ имеют следующие связи:

На схему ОУ поступают следующие сигналы: 32-х разрядный сигнал на выдачу информации (ШДв0-31), информация приема от контроллера - (И_П) и сигнал собственного адреса (АДР1-4). Из схемы ОУ выходят следующие сигналы: 32-х разрядный сигнал принятой информации (ШДп0-31), информация выдачи (И_В), признак ошибки формата обмена (старт - стоп) при приеме информации (ОШф) и сигнал верный адрес (ВА).

32-х разрядный сигнал ШДв0-31 поступает на СРв (17).

УПР (14) вырабатывает сигналы: загрузка слова (ЗС), который поступает на СРв (17); обмен (ОБМ), который поступает на СЧоб (15), СЧсл (16), СРв (17), СРп (22), РСп (23), АД (24); прием (ПРМ), который поступает на ПЕР (19), ПРМ (20), СРп (22), РСп (23); загрузка регистра слова (ЗРС), который поступает на РСп (23); загрузка командного слова (ЗКС), который поступает на СЧсл (16) и АД (24); чужой адрес (ЧА), который поступает на СЧпау (25), связанный с УПР (14) сигналом ошибка приема (ОШп).

СЧоб (15) вырабатывает: 4-х разрядный сигнал байт (БТ1-4), который поступает на СРв (17) и СРп (22); 3-х разрядный сигнал маркеров (МК1-3), который поступает на СЧсл (16), МО (18) и МОиА (21).

Из СЧсл (16) вырабатывается сигнал счетчик слов равен нулю (СС0), который поступает на УПР (14).

СРв (17) вырабатывает 4-х разрядный сигнал последовательного кода выдачи (ПКв1-4), поступающий на МО (18), который связан сигналом информация на выдачу (ИНФв) с ПЕР (19), который вырабатывает сигнал И_В, поступающий на выход из схемы ОУ.

Сигнал И_П поступает на ПРМ (20), который вырабатывает сигнал информация на прием (ИНФп), поступающий на УПР (14) и МОиА (21).

МОиА (21) вырабатывает сигналы: 4-х разрядный сигнал последовательного кода приема (ПКп1-4), поступающий на СРп (22); ОШф, поступающий на выход из схемы.

СРп (22) вырабатывает 32-х разрядный сигнал параллельного кода (ПК0-31), из которого разряды 0-3 поступают на УПР (14), разряды 4-7 поступают на АД (24), а разряды 22-31 поступают на СЧсл (16), при этом все 32 разряда поступают на РСп (23), вырабатывающий 32-х разрядный сигнал ШДп0-31, который поступает на выход из схемы.

Сигнал собственного адреса (АДР1-4) поступает на АД (24), который вырабатывает сигнал ВА, который поступает на УПР (14) и поступает на выход из схемы.

Принцип работы ОУ:

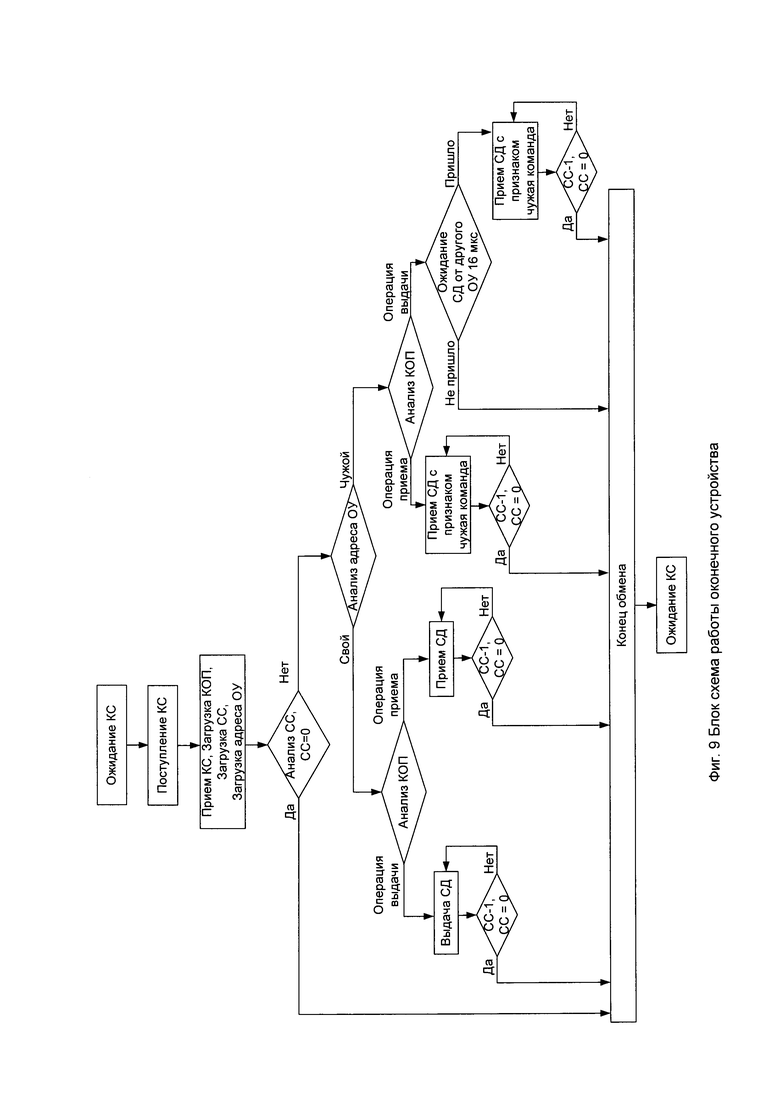

На фигуре 9 представлена блок-схема работы ОУ.

Все блоки ОУ, аналогично блокам контроллера, работают на частоте 4 МГц, кроме блока ПРМ (20), который работает на частоте 16 МГц из-за чего он не теряет принимаемую информацию.

ОУ всегда находится в ожидании КС от контроллера. Поэтому в начальном состоянии сигнал признака приема информации ПРМ в высоком уровне, что означает, что сигнал И_В из блока ПЕР (19) в 3-ем состоянии, а ПРМ (20) открыт для приема информации.

При появлении информации на сигнале И_П в блоке ПРМ (20) она переписывается частотой 16 МГц и выходит на сигнал ИНФп. По низкому уровню (признак стартового бита) на сигнале ИНФп блок УПР (14) вырабатывает сигнал ОБМ, который запускает СЧоб (15) и вырабатываются сигналы БТ1-4 и МК1-3. Сигнал ИНФп также поступает на МОиА (21), в котором с помощью управляющих сигналов МК1-3 параллельный код с ИНФп мультиплексируется в 4 сигнала по одному байту (ПКп1-4). Так же с помощью сигналов МК1-3 в МОиА (21) анализируется наличие низкого уровня на стартовом и высокого на стоповом битах. Если формат старт (низкий уровень), стоп (высокий) не соблюдается, то МОиА (21) вырабатывает сигнал ошибка формата ОШф, который идет на выход схемы.

При соблюдении формата четыре принятые МОиА (21) байта, в параллельном коде ПКп1-4 загружаются в СРп (22) с помощью сигналов БТ1-4. Таким образом, на выходном сигнале ПК0-31 блока СРп (22) сохраняется принятое КС. 0-3 разряды КС загружаются в УПР (14). С помощью сигнала ЗКС 22-31 разряды (количество слов для обмена) загружаются в СЧсл (16), а 4-7 разряды - в АД (24).

В АД (24) принятый по КС адрес сравнивается с собственным адресом ОУ, который устанавливается сигналом АДР1-4. Если адрес, при операциях приема, не совпадает, то сигнал ВА остается в низком уровне и УПР (14) не будет вырабатывать сигнал ЗРС, информация будет приниматься, но не будет переписываться в РСп (23).

Сигнал (ВА) является признаком начала приема информации при сравнении собственного адреса ОУ с принятым по КС. Отсутствие высокого уровня на сигнале ВА выдаваемого из схемы указывает на то, что обмен производится с другим ОУ.

Если адрес совпадает, то ОУ устройство переходит к выполнению принятого КС.

Если СЧсл (16), загруженный по КС равен нулю, то вырабатывается сигнал СС0 и УПР (14) устанавливается в исходное состояние и снимает сигнал ОБМ, по которому СЧоб (15), СЧсл (16), СРп (22) так же устанавливаются в исходное состояние и схема ОУ становится в ожидание следующего КС.

Операция приема для ОУ:

0-3 разряды КС равные «1010», означают операцию приема СД для ОУ.

Если СЧсл (16), загруженный по КС не равен нулю, тогда сигнал ОБМ не снимается и начинается прием СД от контроллера. Отличие в приеме СД от приема КС в том, что каждое принятое СД из сигнала ПК0-31 переписывается в РСп (23), а СЧсл (16) и АД (24) больше не загружаются.

После приема каждого СД по управляющим сигналам МК1-3 из СЧсл (16) вычитается единица. Если СЧсл (16) не равен нулю, после вычитания единицы, то продолжается прием следующего СД. Когда СЧсл (16) становится равным нулю, вырабатывается сигнал СС0, который поступает на УПР (14). После обработки этого сигнала УПР (14) снимает сигнал ОБМ. Блоки СЧоб (15), СЧсл (16), СРп (22), РСп (23) и АД (24) по отсутствию сигнала ОБМ устанавливаются в исходное состояние и схема ОУ становится в ожидание следующего КС. Прием информации закончен.

Если во время приема было зафиксировано нарушение формата старт - стоп, то блок МОиА (21) вырабатывает сигнал ОШф. Даже если было зафиксировано нарушение формата, прием информации продолжается пока ОУ не закончит прием всех СД.

Операция выдачи для ОУ:

Прием КС при операции выдачи аналогичен приему КС при операциях приема.

0-3 разряды КС равные «1100» означают операцию выдачи СД для ОУ.

Аналогично операции приема, адрес из КС сравнивается с собственным адресом. Если адрес не сравнивается, то тогда УПР (14) не снимает сигнал ПРМ и встает в ожидание приема СД от ОУ, которому было адресовано КС. УПР (14) так же вырабатывает сигнал ЧА, который запускает счетчик паузы СЧпау (25).

СЧпау (25) начинает отсчет паузы 16 мкс. Если СД от другого ОУ не приходит за 16 мкс, то СЧпау (25) вырабатывает сигнал ОШп, по которому УПР (14) снимает сигнал ОБМ, схема сбрасывается и ОУ встает в ожидание следующего КС. Если СД от другого ОУ приходит раньше, чем 16 мкс, то ОУ отрабатывает прием СД аналогично операции приема для чужого адреса.

Если адрес из КС сравнивается с собственным адресом, то ОУ переходит к выполнению операции выдачи.

Если СЧсл (16), загруженный по КС не равен нулю, тогда сигнал ОБМ не снимается и начинается выдача СД для контроллера. Блок УПР (14) снимает сигнал ПРМ, по которому закрывается прием информации в ПРМ (20), сбрасываются СРп (22) и РСп (23), а блок ПЕР (19) вырабатывает сигнал высокого уровня (вместо 3-го состояния). Так же УПР (14) вырабатывает сигнал ЗС, по которому происходит параллельная загрузка в сдвиговый регистр СРв (17) информации с входного сигнала ШДв0-31.

После параллельной загрузки СРв (17), счетчик СЧоб (15) начинает вырабатывать сигналы БТ1-4 и МК1-3 аналогично схеме контроллера. С помощью сигналов БТ1-4 на выходе СРв (17) вырабатывается 4 сигнала ПКв1-4 которому побайтно, в последовательном коде, младшими разрядами вперед выдвигается информация (СД).

С помощью сигналов МК1-3 в МО (18) мультиплексируются сигналы ПКв1-4 и добавляют стартовый (низкий уровень) и столовый (высокий уровень) биты. На выходе из МО (18) информация получается в готовом последовательном коде в соответствии с фигурой 1 и 3.

Через блок ПЕР (19), в операциях выдачи, информация проходит без изменений и выходит из схемы по сигналу И_В.

По концу выдачи первого СД, по управляющим сигналам МК1-3 из значения СЧсл (16) вычитается единица. Если СЧсл (16) не равен нулю, после вычитания единицы, то начинается выдача следующего СД и так до момента пока СЧсл (16) не досчитает до нуля.

Когда СЧсл (16) становится равным нулю, вырабатывается сигнал СС0, который поступает на УПР (14). После обработки этого сигнала УПР(14) снимает сигнал ОБМ и перестает вырабатывать сигнал ЗС. СЧоб (15), СЧсл (16), СРв (17) и АД (24) при снятии сигнала ОБМ сбрасываются и устанавливаются в начальное состояние. Выдача информации закончена.

Для увеличения расстояния от контроллера до ОУ ИО 50 м с гальванической развязкой, аналогично контроллеру, в схему ОУ вводится кодирование «Манчестер-2». Структурная схема ОУ с кодированием «Манчестер-2» представлена на фигуре 10 и имеет следующие отличия в сравнении с фиг. 8:

1. Вместо блока ПЕР (19) введен кодер КД (26), для кодирования выходной информации по коду «Манчестер-2».

2. Вместо блока ПРМ (20) введен декодера ДК (27), для декодирования входной информации по коду «Манчестер-2».

3. Сигнал ПРМ не поступает на «КД» (26).

4. Сигнала информация выдачи И_В заменен на два сигнала ИНФ0_В, ИНФ1_В закодированные по коду «Манчестер-2» и поступающие из КД (26) на выход схемы.

5. Сигнал информация приема И_П заменен на два сигнала ИНФ0_П, ИНФ1_П, закодированные по коду «Манчестер-2» и поступающие наДК (27).

6. Введен сигнал ошибка кодирования (ОШк), который вырабатывается в ДК (27) в операциях приема при нарушении кодирования по «Манчестер-2» и поступает на выход из схемы.

7. Аналогично схеме контроллера, для увеличения времени ожидания СД от других ОУ, в схему ОУ введен сигнал длительности паузы (Тп1-5), поступающий на СЧпау (25).

Техническим результатом изобретения является:

1. Обеспечение ИО скорости обмена 4 Мбод при длине слова 32 разряда, расстоянии между контроллером и ОУ до 1,5 м, ас использованием гальванической развязки - до 10 м.

2. Контроллер и оконечное устройство, обеспечивающие работу ИО.

3. Контроллер и оконечное устройство с гальванической развязкой, обеспечивающие работу с кодированием по интерфейсу «Манчестер-2» и расстояние между контроллером и ОУ до 50 м.

Таким образом заявлены:

1. Асинхронный последовательный интерфейс обмена информацией, в соответствии с которым контроллер является инициатором обмена информацией и осуществляет обмен 32-х разрядными словами, разделенными на байты; контроллер выедает для оконечного устройства командное слово, в котором каждый байт сопровождается стартовым и стоповым битами и выдается последовательным кодом младшими разрядами вперед, начиная со старшего байта; командное слово содержит резервные разряды о количестве слов для обмена, максимальное число которых 1023, направлении обмена и адресе оконечного устройства, которому оно адресовано; в операциях выдачи, после выдачи командного слова, контроллер начинает выдавать слова данных; в операциях приема, после выдачи командного слова, контроллер встает в ожидание слов данных от оконечного устройства; командное слово и слова данных передаются без пауз; стартовый бит передается низким уровнем, столовый бит и отсутствие информации - высоким уровнем; длительность одного бита 250 нс; оконечное устройство начинает обмен информацией с контроллером при совпадении собственного адреса с указанным в командном слове; при отсутствии слова данных от оконечного устройства 16 мкс контроллер заканчивает текущий обмен.

2. Контроллер, содержащий блок управления (1), сдвиговый регистр выдачи (4), сдвиговый регистр приема (9), регистр принятого слова (10), отличающийся тем, что сдвиговый регистр выдачи (4) принимает 32 разряда сигнала на выдачу информации, при этом младшие 4 разряда дополнительно поступают на блок управления (1), а старшие 10 разрядов поступают на счетчик слов (3), который принимает входной сигнал начала ввода-вывода, также поступающий на блок управления (1), который вырабатывает сигналы загрузка слова, поступающий на сдвиговый регистр выдачи (4), сигнал загрузка регистра слова, поступающий на регистр принятого слова (10), сигнал обмен, поступающий на счетчик обмена (2), счетчик слов (3), сдвиговый регистр выдачи (4), сдвиговый регистр приема (9) и регистр принятого слова (10), на который также поступает сигнал прием, дополнительно поступающий на счетчик паузы ожидания слова данных (11), сдвиговый регистр приема (9), блок приема информации (7) и блок выходной информации с включением 3-го состояния (6); счетчик обмена (2) вырабатывает 4-х разрядный сигнал байт, который поступает на сдвиговый регистр выдачи (4) и на сдвиговый регистр приема (9) и 3-х разрядный сигнал маркеров, который поступает на блок мультиплексирования обмена (5), блок мультиплексирования и анализа принимаемой информации (8) и счетчик слов (3), вырабатывающий соответствующий сигнал, который равен логическому нулю и поступает на блок управления (1); сдвиговый регистр выдачи (4) вырабатывает 4-х разрядный сигнал последовательного кода выдачи, который поступает на блок мультиплексирования обмена (5), вырабатывающий сигнал информация на выдачу, поступающий на блок выходной информации с включением 3-го состояния (6), который вырабатывает сигнал информация выдачи, поступающий на выход устройства; сигнал информация приема поступает в устройство на блок приема информации (7), который вырабатывает сигнал информация на прием, поступающий на блок управления (1), счетчик паузы ожидания слова данных (11) и блок мультиплексирования и анализа принимаемой информации (8), который вырабатывает сигнал ошибка формата, поступающий на выход из устройства и 4-х разрядный сигнал последовательного кода приема, который поступает на сдвиговый регистр приема (9), вырабатывающий 32-х разрядный сигнал параллельного кода, поступающий на регистр принятого слова (10), вырабатывающий 32-х разрядный сигнал принятой информации, выходящий из устройства, счетчик паузы ожидания слова данных (11) вырабатывает сигнал ошибка приема, который поступает в блок управления (1) и выходит из устройства.

3. Устройство контроллера по п. 2, отличающийся тем, что блок выходной информации с включением 3-го состояния (6) заменяется на кодер (12), на который не поступает сигнал приема и из которого на выход устройства поступает два сигнала информация выдачи по коду «Манчестер-2», а блок приема информации (7) заменяется на декодер (13), на который поступают два сигнала информация приема по коду «Манчестер-2» и вырабатывается дополнительный сигнал ошибка кодирования, при этом в устройство на счетчик паузы ожидания слова данных (11) приходит 5-ти разрядный сигнал длительности паузы.

4. Оконечное устройство асинхронного последовательного интерфейса обмена информацией, содержащее блок управления (14), сдвиговый регистр выдачи (17), сдвиговый регистр приема (22), регистр принятого слова (23), отличающееся тем, что сдвиговый регистр выдачи (17) принимает 32 разряда сигнала на выдачу информации; блок управления (14) вырабатывает сигнал загрузка слова, поступающий на сдвиговый регистр выдачи (17), сигнал загрузка регистра слова, который поступает на регистр принятого слова (23), сигнал обмен, который поступает на счетчик обмена (15), счетчик слов (16), сдвиговый регистр выдачи (17), регистр принятого слова (23), блок сравнения адреса (24) и сдвиговый регистр приема (22), сигнал прием, который поступает на регистр принятого слова (23), сдвиговый регистр приема (22), блок приема информации (20) и блок выходной информации с включением 3-го состояния (19), сигнал чужой адрес, который поступает на счетчик паузы ожидания слов данных от других оконечных устройств (25) и сигнал загрузка командного слова, который проступает на счетчик слов (16) и блок сравнение адреса (24); счетчик обмена (15) вырабатывает 4-х разрядный сигнал байт, который поступает на сдвиговый регистр выдачи (17) и на сдвиговый регистр приема (22) и 3-х разрядный сигнал маркеров, который поступает на счетчик слов (16), блок мультиплексирования обмена (18) и блок мультиплексирования и анализа принимаемой информации (21); счетчик слов (16) вырабатывает сигнал счетчик слов равен нулю, который поступает на блок управления (14); сдвиговый регистр выдачи (17) вырабатывает 4-х разрядный сигнал последовательного кода выдачи, который поступает на блок мультиплексирования обмена (18), вырабатывающий сигнал информация на выдачу, поступающий на блок выходной информации с включением 3-го состояния (19), который вырабатывает сигнал информация выдачи, поступающий на выход из устройства; сигнал информация приема поступает на блок приема информации (20), который вырабатывает сигнал информация на прием, поступающий на блок управления (14) и блок мультиплексирования и анализа принимаемой информации (21), который вырабатывает сигнал ошибка формата, поступающий на выход из устройства и 4-х разрядный сигнал последовательного кода приема, который поступает на сдвиговый регистр приема (22); счетчик паузы ожидания слова данных от других оконечных устройств (25) вырабатывает сигнал ошибка приема, который поступает в блок управления (14), вырабатывающий 32-х разрядный сигнал параллельного кода, который поступает на регистр принятого слова (23), из которого 4 младших разряда поступают на блок управления (14), а 10 старших разрядов поступают на счетчик слов (16), 4 разряда поступают на блок сравнения адреса (24), а все 32 разряда поступают на регистр принятого слова (23), который вырабатывает 32-х разрядный сигнал принятой информации, поступающий на выход из устройства; в устройство поступает 4-х разрядный сигнал собственного адреса и далее поступает на блок сравнения адреса (24); из блока сравнения адреса (24) выходит сигнал верный адрес, который поступает на блок управления (14) и выходит из устройства.

5. Оконечное устройство по п. 4, в котором блок выходной информации с включением 3-го состояния (19) заменяется на кодер (26), на который не поступает сигнал приема и из которого выходят два сигнала информация выдачи по коду «Манчестер-2», выходящие из устройства; блок приема информации (20) заменяется на декодер (27); в устройство и далее в декодер (27) поступают два сигнала информации приема по коду «Манчестер-2» и вырабатывается дополнительный сигнал ошибка кодирования; в устройство, а далее в счетчик паузы ожидания слов данных от других оконечных устройств (25) приходит 5-ти разрядный сигнал длительности паузы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система обмена для управления электропитанием вычислительного комплекса | 1988 |

|

SU1654830A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЛЕТАТЕЛЬНЫМ АППАРАТОМ, ИСПОЛЬЗУЮЩЕЕ КОМБИНИРОВАННУЮ СИСТЕМУ ИНФОРМАЦИОННОГО ОБМЕНА | 2000 |

|

RU2166461C1 |

| Устройство для контроля цифровых каналов связи | 1991 |

|

SU1807490A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198530A1 |

| АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО ОПЕРАТОРА УПРАВЛЕНИЯ ВОЗДУШНЫМ ДВИЖЕНИЕМ | 2001 |

|

RU2219586C2 |

| КОНТРОЛЛЕР ОБМЕНА | 1993 |

|

RU2032214C1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Устройство для сопряжения оконечного устройства с мультиплексным каналом передачи информации | 1987 |

|

SU1538172A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения абонентов с магистралью | 1986 |

|

SU1361570A1 |

Изобретение относится к цифровой технике в области обмена информацией. Технический результат заключается в создании надежного асинхронного интерфейса и необходимых для его работы контроллера и оконечного устройства (ОУ), которые обеспечат обмен 32-разрядными словами с высокой скоростью передачи информации с минимальным количеством сигналов между устройствами. Асинхронный последовательный интерфейс обмена (ИО) предназначен для обмена информацией между контроллером и оконечным устройством. Обмен информацией ведется 32-разрядными словами, разделенными на байты и дополненными стартовым и стоповым битами. Инициализатором обмена всегда выступает контроллер, который выдает командное слово (КС) для ОУ. В КС передается код операции (КОП), адрес ОУ и количество слов для обмена. Получив КС, ОУ сравнивает адрес в КС с собственным адресом, после чего выполняет его (адрес совпадает) или игнорирует (чужой адрес). Если в КОП заложена операция приема, то ОУ принимает указанное в КС количество слов данных (СД), если операция выдачи, то ОУ выдает указанное количество СД. 3 н. и 2 з.п. ф-лы, 10 ил.

1. Асинхронный последовательный интерфейс обмена информацией, в соответствии с которым контроллер является инициатором обмена информацией и осуществляет обмен 32-разрядными словами, разделенными на байты; контроллер выдает для оконечного устройства командное слово, в котором каждый байт сопровождается стартовым и стоповым битами и выдается последовательным кодом младшими разрядами вперед, начиная со старшего байта; командное слово содержит резервные разряды о количестве слов для обмена, максимальное число которых 1023, направлении обмена и адресе оконечного устройства, которому оно адресовано; в операциях выдачи, после выдачи командного слова, контроллер начинает выдавать слова данных; в операциях приема, после выдачи командного слова, контроллер встает в ожидание слов данных от оконечного устройства; командное слово и слова данных передаются без пауз; стартовый бит передается низким уровнем, стоповый бит и отсутствие информации - высоким уровнем; длительность одного бита 250 нс; оконечное устройство начинает обмен информацией с контроллером при совпадении собственного адреса с указанным в командном слове; при отсутствии слова данных от оконечного устройства 16 мкс контроллер заканчивает текущий обмен.

2. Контроллер, содержащий блок управления, сдвиговый регистр выдачи, сдвиговый регистр приема, регистр принятого слова, отличающийся тем, что сдвиговый регистр выдачи принимает 32 разряда сигнала на выдачу информации, при этом младшие 4 разряда дополнительно поступают на блок управления, а старшие 10 разрядов поступают на счетчик слов, который принимает входной сигнал начала ввода-вывода, также поступающий на блок управления, который вырабатывает сигналы загрузка слова, поступающий на сдвиговый регистр выдачи, сигнал загрузка регистра слова, поступающий на регистр принятого слова, сигнал обмен, поступающий на счетчик обмена, счетчик слов, сдвиговый регистр выдачи, сдвиговый регистр приема и регистр принятого слова, на который также поступает сигнал прием, дополнительно поступающий на счетчик паузы ожидания слова данных, сдвиговый регистр приема, блок приема информации и блок выходной информации с включением 3-го состояния; счетчик обмена вырабатывает 4-разрядный сигнал байт, который поступает на сдвиговый регистр выдачи и на сдвиговый регистр приема и 3-разрядный сигнал маркеров, который поступает на блок мультиплексирования обмена, блок мультиплексирования и анализа принимаемой информации и счетчик слов, вырабатывающий соответствующий сигнал, который равен логическому нулю и поступает на блок управления; сдвиговый регистр выдачи вырабатывает 4-разрядный сигнал последовательного кода выдачи, который поступает на блок мультиплексирования обмена, вырабатывающий сигнал информация на выдачу, поступающий на блок выходной информации с включением 3-го состояния, который вырабатывает сигнал информация выдачи, поступающий на выход устройства; сигнал информация приема поступает в устройство на блок приема информации, который вырабатывает сигнал информация на прием, поступающий на блок управления, счетчик паузы ожидания слова данных и блок мультиплексирования и анализа принимаемой информации, который вырабатывает сигнал ошибка формата, поступающий выходит из устройства и 4-разрядный сигнал последовательного кода приема, который поступает на сдвиговый регистр приема, вырабатывающий 32-разрядный сигнал параллельного кода, поступающий на регистр принятого слова, вырабатывающий 32-разрядный сигнал принятой информации, выходящий из устройства, счетчик паузы ожидания слова данных вырабатывает сигнал ошибка приема, который поступает в блок управления и выходит из устройства.

3. Устройство контроллера по п. 2, отличающееся тем, что блок выходной информации с включением 3-го состояния заменяется на кодер, на который не поступает сигнал приема и из которого на выход устройства два сигнала информация выдачи по коду «Манчестер-2», а блок приема информации заменяется на декодер, на который поступают два сигнала информация приема по коду «Манчестер-2» и вырабатывается дополнительный сигнал ошибка кодирования, при этом в устройство на блок счетчик паузы ожидания слова данных приходит 5-разрядный сигнал длительности паузы.

4. Оконечное устройство асинхронного последовательного интерфейса обмена информацией, содержащее блок управления, сдвиговый регистр выдачи, сдвиговый регистр приема, регистр принятого слова, отличающееся тем, что сдвиговый регистр выдачи принимает 32 разряда сигнала на выдачу информации; блок управления вырабатывает сигнал загрузка слова, поступающий на сдвиговый регистр выдачи, сигнал загрузка регистра слова, который поступает на регистр принятого слова, сигнал обмен, который поступает на счетчик обмена, счетчик слов, сдвиговый регистр выдачи, регистр принятого слова, блок сравнения адреса и сдвиговый регистр приема, сигнал прием, который поступает на регистр принятого слова, сдвиговый регистр приема, блок приема информации и блок выходной информации с включением 3-го состояния, сигнал чужой адрес, который поступает на счетчик паузы ожидания слов данных от других оконечных устройств и сигнал загрузка командного слова, который проступает на счетчик слов и блок сравнение адреса; счетчик обмена вырабатывает 4-разрядный сигнал байт, который поступает на сдвиговый регистр выдачи и на сдвиговый регистр приема, и 3-разрядный сигнал маркеров, который поступает на счетчик слов, блок мультиплексирования обмена и блок мультиплексирования и анализа принимаемой информации; счетчик слов вырабатывает сигнал счетчик слов равен нулю, который поступает на блок управления; сдвиговый регистр выдачи вырабатывает 4-разрядный сигнал последовательного кода выдачи, который поступает на блок мультиплексирования обмена, вырабатывающий сигнал информация на выдачу, поступающий на блок выходной информации с включением 3-го состояния, который вырабатывает сигнал информация выдачи, поступающий на выход из устройства; сигнал информация приема поступает на блок приема информации, который вырабатывает сигнал информация на прием, поступающий на блок управления и блок мультиплексирования и анализа принимаемой информации, который вырабатывает сигнал ошибка формата, поступающий на выход из устройства и 4-разрядный сигнал последовательного кода приема, который поступает на сдвиговый регистр приема; счетчик паузы ожидания слова данных от других оконечных устройств вырабатывает сигнал ошибка приема, который поступает в блок управления, вырабатывающий 32-разрядный сигнал параллельного кода, который поступает на регистр принятого слова, из которого 4 младших разряда поступают на блок управления, а 10 старших разрядов поступают на счетчик слов, 4 разряда поступают на блок сравнения адреса, а все 32 разряда поступают на регистр принятого слова, который вырабатывает 32-разрядный сигнал принятой информации, поступающий на выход из устройства; в устройство поступает 4-разрядный сигнал собственного адреса и далее поступает на блок сравнения адреса; из блока сравнения адреса выходит сигнал верный адрес, который поступает на блок управления и выходит из устройства.

5. Оконечное устройство по п. 4, в котором блок выходной информации с включением 3-го состояния заменяется на кодер, на который не поступает сигнал приема и из которого выходят два сигнала информация выдачи по коду «Манчестер-2», выходящие из устройства; блок приема информации заменяется на декодер; в устройство и далее в декодер поступают два сигнала информации приема по коду «Манчестер-2» и вырабатывается дополнительный сигнал ошибка кодирования; в устройство, а далее в блок счетчик паузы ожидания слов данных от других оконечных устройств приходит 5-разрядный сигнал длительности паузы.

| СПОСОБ ПРИГОТОВЛЕНИЯ АНОДНОЙ МАССЫ | 0 |

|

SU177629A1 |

| Способ изготовления турбинных лопаток из металлических листов | 1948 |

|

SU72772A1 |

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Устройство для контроля цифровых каналов связи | 1991 |

|

SU1807490A1 |

| Устройство для обмена информацией | 1977 |

|

SU734655A1 |

Авторы

Даты

2019-08-23—Публикация

2018-11-09—Подача