приоритета, коммутатор сигнала записи, триггер признака информациониого слова, триггер признака командного слова, регистр хранения командного слова, регистр хранения адреса командного слова, блок разрешения повторения командного слова, блок формирования паузы и счетчик формирования сигнала отказа связи, причем первые информационные входы . коммутатора сигнала записи и мультиплексоров адреса и входного числа подключены соответственно к третьему, четвертому и пятому выходам блока связи с процессором, первые и вторые управляющие - соответственно к первому и второму выходам блока приоритета, а выходы коммутатора сигнала.записи и мультиплексоров адреса и входного слова - соответственно к управляющему, адресному и первому информационному входам оперативной памяти, первый выход которой соединен с информационными входами регистра хранения командного слова и формирователя сигнала четности, пятым входом блока связи с процессором и четвертым информационным входом сдвигового регистра, второй и третий информационные выходы которого подключены соответственно к второму информационному входу мультиплексора входного числа и к первому входу блока разрешения повторения командного слова, второй вход которого соединен с выходом блока анализа четности, третий и четвертьй входы блока разрешения повторения командного слова соединены соответственно с входом признака ответного слова устройства и первым выходом регистра хранения командного слова пятый вход - с вторым выходом счетчика промежутка, а выход - с первым входом блока формирования паузы, BTopbw управляющим входом счетчика адресов и управляющим входом первого вычитателя слов и через счетчик формирования сигнала отказа связи - с вьЬсодом сигнала отказа связи устройства, установочные входы триггеров признаков командного слова и информационного слова соединены с вторым выходом оперативной памяти, а входы сброса - с выходом счетчика тактовых импульсов, а выходы триггеров признаков командного слова и информационного слова - соответственно с выходами признака командного слова и признака информационного слова устройства, вторвй информационный вход оперативной памяти соединен с третьим выходом регистра настройки, управляющий и информационный входы блока приоритета подключены соответственно к выходу счетчика тактовых импульсов и шестому выходу блока связи с процессором, шестой вход которого соединен с вторым выходом коммутатора сигнала записи, третий выход и второй информационный вход которого подключены соответственно к третьему управляющему входу сдвигового регистра и выходу блока формирования сигнада записи, управляющий вход которого соединен с выходом блока формирования паузы, второй, третий и четвертый входы которого подключены соответственно к входу признака ответного слова устройства,выходу второго вычитателя количества слов и выходу генератора тактовых импульсов, а пятый вход к пятому входу элемента И-ИЛИ и второму выходу регистра хранения командного слова, третий выход которого соединен с информационным входом второго вычитателя количества слов, а управляющий вход с выходом триггера признака командного слова и управляющим входом регистра хранения адреса командного слова, выход которого подключен к второму информационному входу счетчика адресов, а информационный вход - к выходу счетчика адресов и второму информационному входу мультиплексора адреса,

2. Устройство по п. 1, о т л и чающее.с я тем, что блок связ с процессором содержит дешифратор адреса, вход которого является третьим входом блока, счетчик адресов, выход которого является четвертым выходом блока, первый и второй элементы И, первые входы и выходы которых являются соответственно четвертым и вторым входами и шестым и третьим выходами блока, первую и вторую группы шинных усилителей, выходы которых являются соответственно вторым и пятым выходами блока а информационные входы - первым входом блока, третью группу шинных усилителей, выходы и информационные входы которых являются соответственно первым выходом и пятым входом блока, и три элемента НЕ, причем первый выход дешифратора адреса соединен с вторьми входами первого и второго элементов И, счетным входо счетчика адресов и через первый элемент НЕ - с управляющими входами шинных усилителей первой группы, второй выход дешифратора адреса подключен через второй элемент НЕ к управляющим входам шинных усилителей второй группы, управляющие входы шинных усилителей третьей группы соединены через третий элемент НЕ с шестым входом блока.

3.Устройство ПОП.1, ОТЛИчающе е с я тем, что блок разрешения повторения командного слова содержит схему сравнения, первый, второй и третий входы которого являются соответственно первым, третьим и четвертым входами блока, элемент. ИЛИ-НЕ, выход которого является выходом блока, и элемент ИЛИ-НЕ первый вход которого соединен с выходом схемы сравнения, второй и третий входы - соответственно с пятым и вторым входами блока,а выход - с входом элемента НЕ

4.Устройство по п. I, отличающееся тем, что блок формирования сигнала записи содержит элемент ИЛИ-НЕ, выход которого является выходом блока, триггер и элемент И-НЕ, причем выходы элемента И-НЕ и триггера подключены соответственно к первому и второму входам элемента ИЛИ-НЕ, а первые

и вторые входы - соответственно

8530

к счетному и управляющему входам блока,

5.Устройство по п. 1, отличающееся тем, что блок фор:мирования ваузы содержит счетчик, счетный вход которого является четвертьм входом блока, дешифратор, выход которого является выходом блока и соединен с входом сброса счетчика, первый и второй элементы И, первые входы которых являются соответственно вторым и третьим входами блока, вторые входы - пятым входом блока, и элемент ИЛИ, первый вход которого является первым входом блока, второй и третий входы подключены соответственно к выходам первого и второго элементов И, а выход - к входу пуска счетчика, выходом Подключенного к входу дешиф.ратора.

6.Устройство по п. 1, отличающееся тем, что коммутатор сигнала записи содержит два элемента НЕ, элемент ИЛИ-НЕ, выход которого является первым выходом коммутатора, два шинных формирователя, , выходы которых являются соответственно вторым и третьим выходами блока, два элемента И, первые входы которых являются соответственно первым и вторым управляющими входами коммутатора, а вторые входы - соответственно первым и вторым информационньми входами коммутатора и соединены соответственно через первый

и второй элементы НЕ с входами первого и второго шинных формирователей .

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Устройство для контроля цифровых каналов связи | 1991 |

|

SU1807490A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Многоканальная система обмена для управления электропитанием вычислительного комплекса | 1988 |

|

SU1654830A1 |

| СИСТЕМА УПРАВЛЕНИЯ КОНВЕЙЕРИЗОВАННЫМ ЦИКЛОМ ПРОЦЕССОРА ШИРОКОГО КОМАНДНОГО СЛОВА | 2001 |

|

RU2184389C1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство для вывода информации | 1983 |

|

SU1124278A1 |

1. УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЩ1ЕЙ, содержащее блок связи с процессором, первые вход и выход которого являются соответственно первыми информационными входом и выходом устройства, второй, третий и четвертый входы - соответственно входами сигналов режима и адреса и первым входом синхронизации устройства, а второй выход подключен к входу регистра настройки, блок анализа четности, генератор тактовых iwnynbcoB, счетчик промежутка, счетчик тактовых импульсов, элемент И-ИЛИ два вычитателя количества слов, счетчик адресов, блок формирования сигнала записи, дешифратор нуля, выход которого является выходом сигнала прерьшания устройства, формирователь сигнала четности и сдвиговый регистр первые информационные вход и выход которого являются соответственно вторыми информационными входом и выходом устройства, первый к второй управляющие входы - соответственно входами признака ответного слова и признака информационного слова устройства, причем выход генератора тактовых импульсов соединен с вторым информационным входом сдвигового регистра, выходом синхронизации устройства, счетным входом счетчика промежутка и первым входом элемента И-ИЛИ, вход синхронизации сдвигового регистра является вторым входом синхронизации устройства и подключен к управляющему входу счетчика промежутка и второму входу элемента И-ИЛИ, третьим входом соединенного с первым выходом счетчика промежутка, а выходом - с входом счетчика тактовых импульсов, выход которого подключен к счетному входу счетчика адресов, тактовым входам первого и второго выS читателей количества слов, блока анализа четности, блока формирования ел сигнала записи и формирователя сигС нала четности, выходом соединенного с третьим информационным входом сдвигового регистра, информационный вход блока анализа четности соединен с вторым информационным входом устройства, первый и второй выходы регистсо ра настройки соединены соответствен00 но с первым информационным входом сд счетчика адресов и информационным 00 входом первого вычитателя количества слов, выходом подключенного к информационному входу дешифратора нуля, управляющий вход которого соединен с первым управляющим входом счетчика адресов и третьим выходом регистра настройки, выход второго вычитателя слов подключен к четвертому входу элемента И-Ш1И, о т личающеес я тем, что, с целью повыщения быстродействия устройства, в него введены оперативная память, мультиплексор адреса, мультиплексор входного числа, блок

Устройство относится к вычислителе ной технике и предназначено для обмена информацией между компонентами оборудования объекта в виде последовательных кодов, циркулирующих на мультиплексной магистрали обмена.

, Целью изобретения является повышение быстродействия устройства.

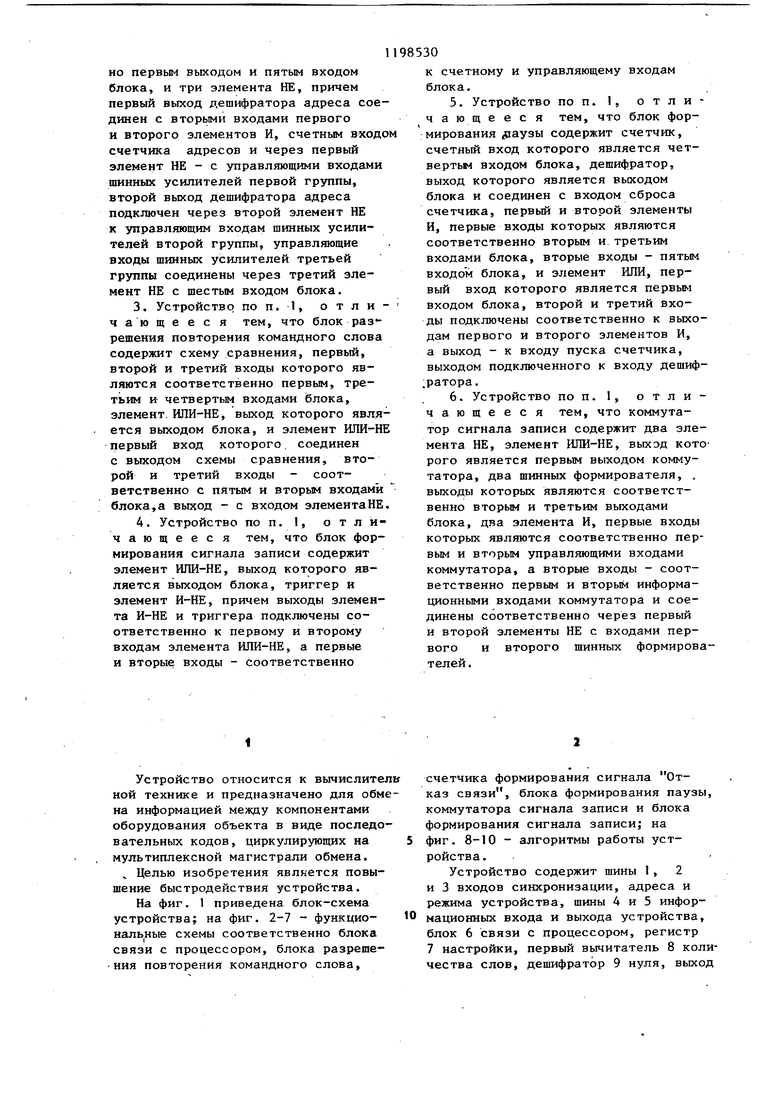

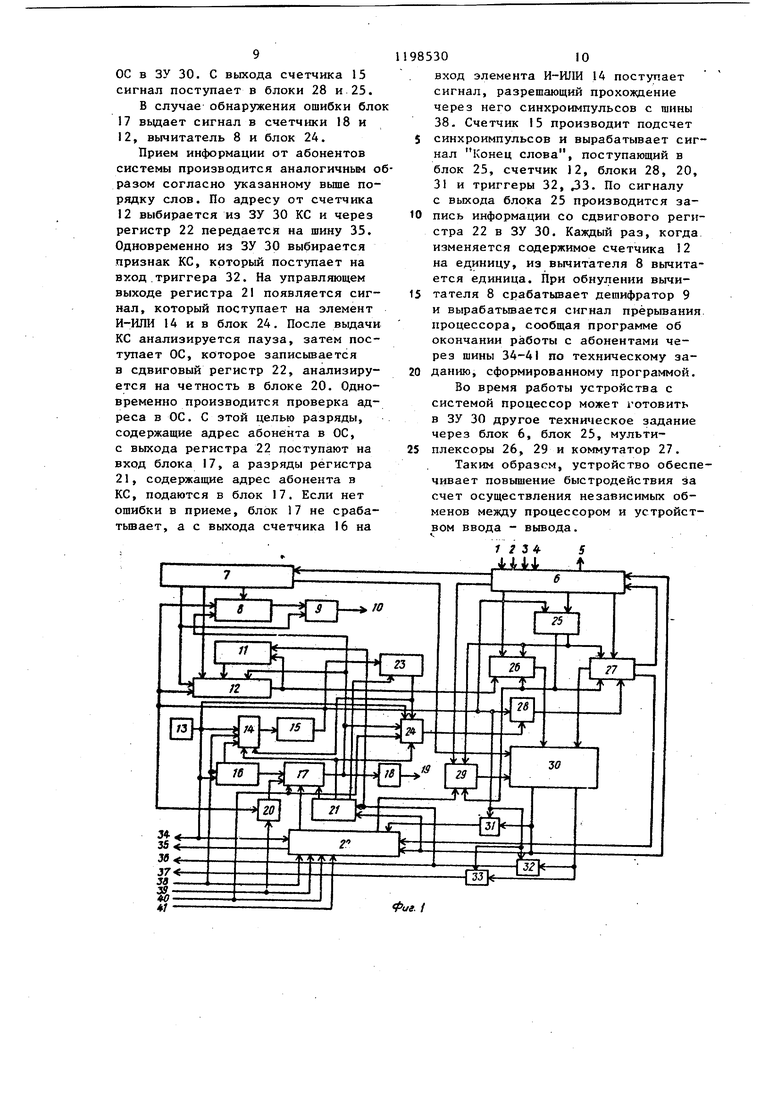

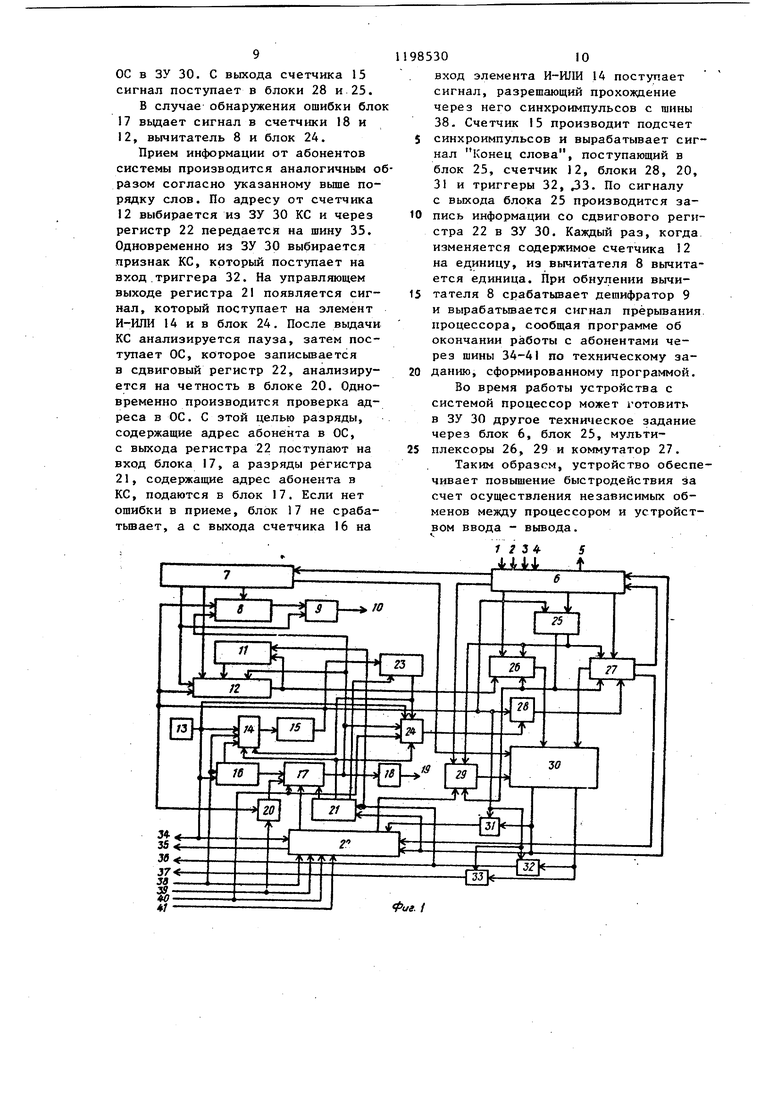

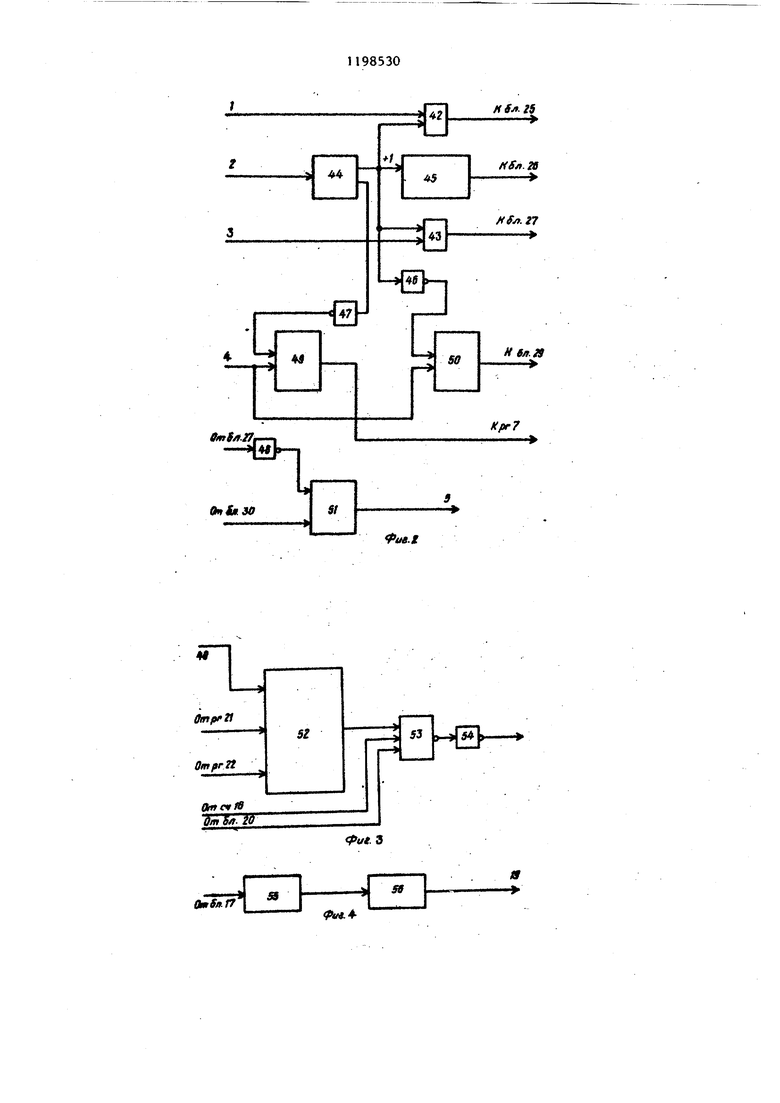

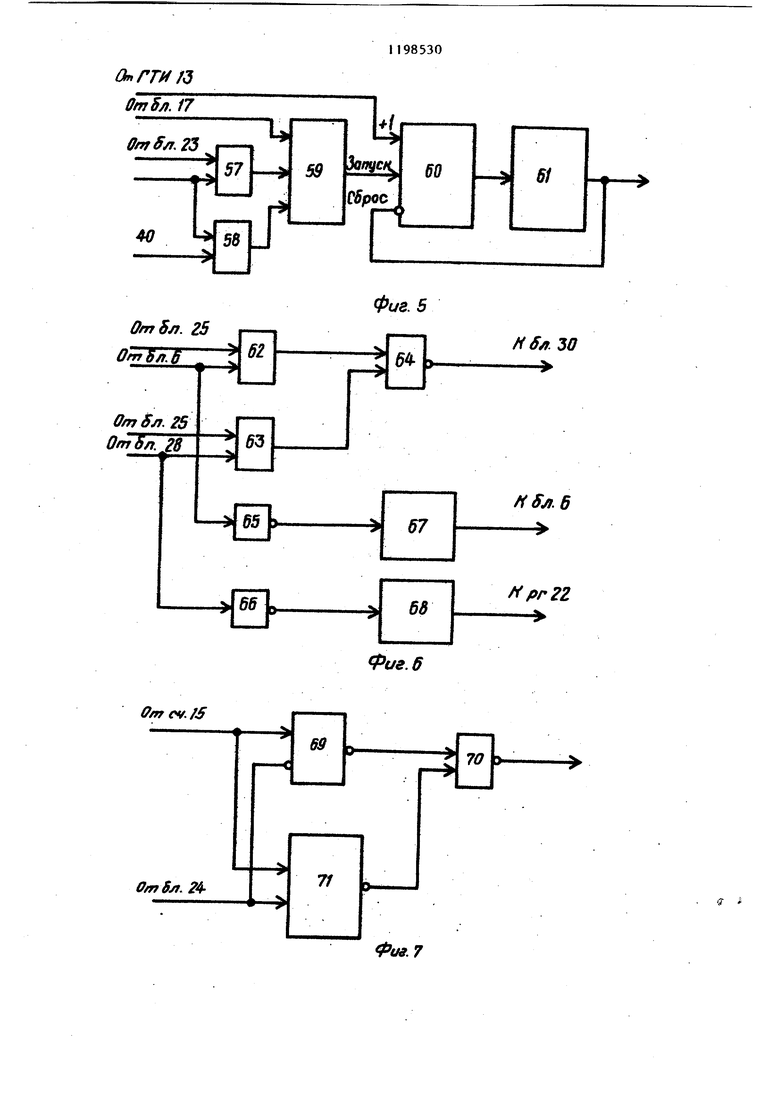

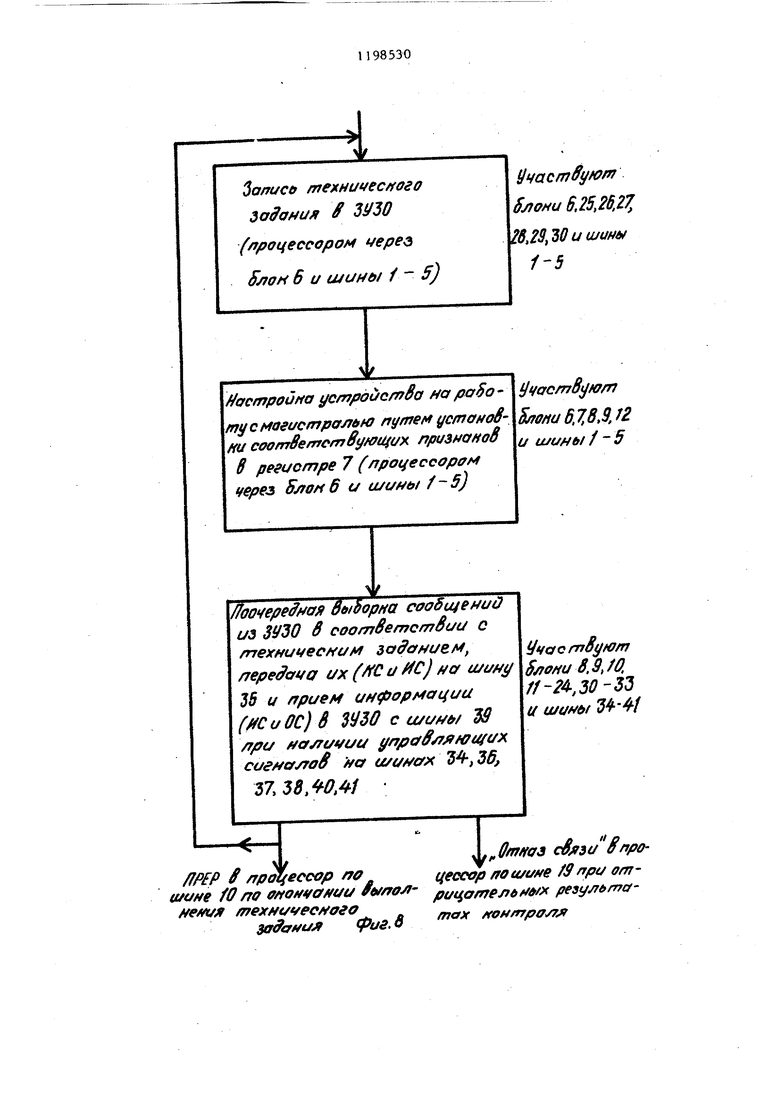

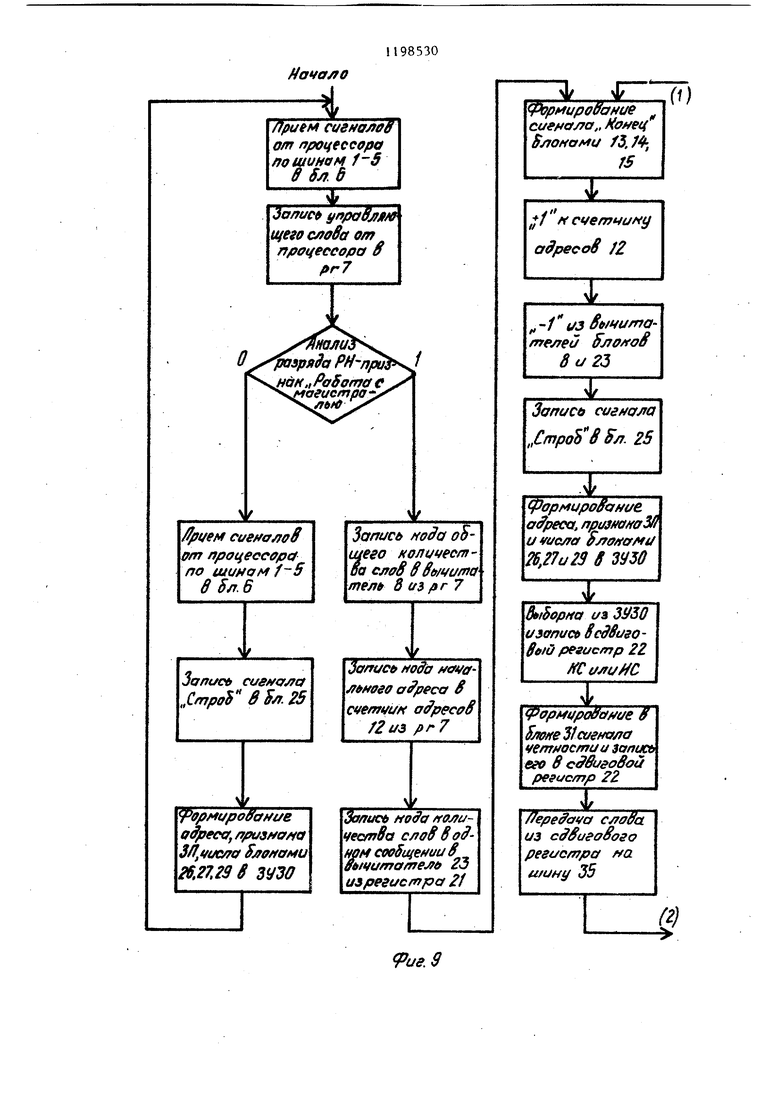

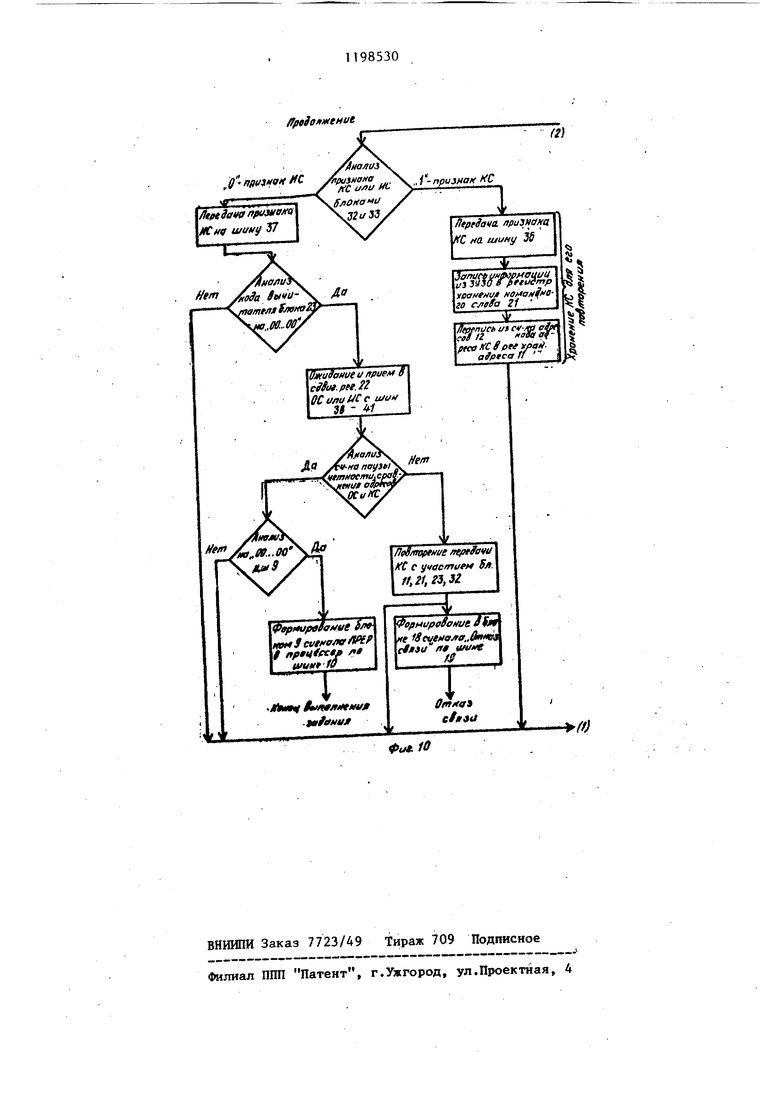

На фиг. 1 приведена блок-схема устройства; на фиг. 2-7 - функциональные схемы соответственно блока связи с процессором, блока разрешения повторения командного слова.

счетчика формирования сигнала Отказ связи, блока формирования паузы, коммутатора сигнала записи и блока формирования сигнала записи; на фиг. 8-10 - алгоритмы работы устройства.

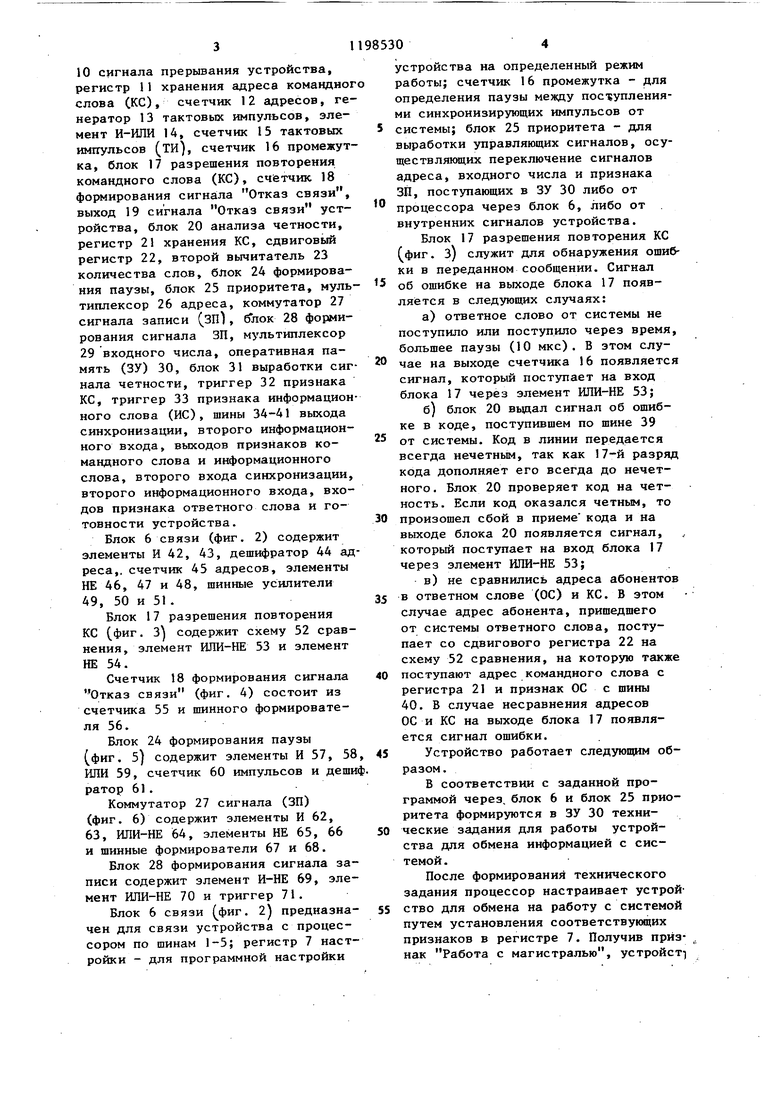

Устройство содержит шины 1, 2 и 3 входов синхронизации, адреса и режима устройства, шины 4 и 5 информационных входа и выхода устройства, блок 6 связи с процессором, регистр 7 настройки, первый вычитатель 8 количества слов, дешифратор 9 нуля, выход 10 сигнала прерывания устройства, регистр 11 хранения адреса командно слова (КС), счетчик 12 адресов, ге нератор 13 тактовых импульсов, элемент И-ИЛИ 14, счетчик 15 тактовых импульсов (ТИ), счетчик 16 промежут ка, блок 17 разрешения повторения командного слова (КС), счетчик 18 формирования сигнала Отказ связи, выход 19 сигнала Отказ связи устройства, блок 20 анализа четности, регистр 21 хранения КС, сдвиговый регистр 22, второй вычитатель 23 количества слов, блок 24 формирования паузы, блок 25 приоритета, муль типлексор 26 адреса, коммутатор 27 сигнала записи (ЗП), блок 28 формирования сигнала ЗП, мультиплексор 29 входного числа, оперативная память (ЗУ) 30, блок 31 выработки сиг нала четности, триггер 32 признака КС, триггер 33 признака информацион ного слова (ИС), шины 34-41 выхода синхронизации, второго информационного входа, выходов признаков командного слова и информационного слова, второго входа синхронизации, второго информационного входа, входов признака ответного слова и готовности устройства. Блок 6 связи (фиг. 2) содержит элементы И 42, 43, дешифратор 44 ад реса,, счетчик 45 адресов, элементы НЕ 46, 47 и 48, шинные усилители 49, 50 и 51. Блок 17 разрешения повторения КС (фиг. 3 содержит схему 52 сравнения, элемент ИЛИ-НЕ 53 и элемент НЕ 54. Счетчик 18 формирования сигнала Отказ связи (фиг. 4) состоит из счетчика 55 и шинного формирователя 56. Блок 24 формирования паузы (фиг. 5) содержит элементы И 57, 58 ИЛИ 59, счетчик 60 импульсов и деши ратор 61. Коммутатор 27 сигнала (ЗП) (фиг. 6) содержит элементы И 62, 63, ИЛИ-НЕ 64, элементы НЕ 65, 66 и шинные формирователи 67 и 68. Блок 28 формирования сигнала записи содержит элемент И-НЕ 69, элемент ИЛИ-НЕ 70 и триггер 71. Блок 6 связи (фиг. 2) предназначен для связи устройства с процессором по шинам 1-5; регистр 7 настройки - для программной настройки устройства на определенный режим работы; счетчик 16 промежутка - для определения паузы между пос5уплениями синхронизирующих импульсов от системы; блок 25 приоритета - для выработки управляющих сигналов, осуществляющих переключение сигналов адреса, входного числа и признака ЗП, поступающих в ЗУ 30 либо от процессора через блок 6, либо от внутренних сигналов устройства. Блок 17 разрешения повторения КС (фиг. з) служит для обнаружения ошибки в переданном сообщении. Сигнал об ошибке на выходе блока 17 появляется в следующих случаях: а)ответное слово от системы не поступило или поступило через время, большее паузы (10 мкс). В этом случае на выходе счетчика 16 появляется сигнал, который поступает на вход блока 17 через элемент ИЛИ-НЕ 53; б)блок 20 вьдал сигнал об ошибке в коде, поступившем по шине 39 от системы. Код в линии передается всегда нечетным, так как 17-й разряд кода дополняет его всегда до нечетного. Блок 20 проверяет код на четность. Если код оказался четным, то произошел сбой в приеме кода и на выходе блока 20 появляется сигнал, который поступает на вход блока 17 через элемент ИЛИ-НЕ 53; в)не сравнились адреса абонентов в ответном слове (ОС) и КС. В этом случае адрес абонента, пришедшего от системы ответного слова, поступает со сдвигового регистра 22 на схему 52 сравнения, на которую также поступают адрес командного слова с регистра 21 и признак ОС с шины 40. В случае несравнения адресов ОС и КС на выходе блока 17 появляется сигнал ошибки. Устройство работает следующим образом. В соответствии с заданной программой через, блок 6 и блок 25 приоритета формируются в ЗУ 30 технические задания для работы устройства для обмена информацией с системой . После формирования технического задания процессор настраивает устройство для обмена на работу с системой путем установления соответствующих признаков в регистре 7. Получив признак Работа с магистралью, устройст во начинает самостоятельно управлят обменом информации, проходящей чере оконечное устройство в систему. Технические задания, сформирован ные процессором в ЗУ 30, состоят из сообщений. Каждое сообщение состоит из КС, ИС и ОС. Инициатором обмена является процессор, формирующий КС для передачи его через выходные щины в систему. КС содержит адрес абонента, признак прием-выдача, количество слов, содержащихся, в сообщении. ОС от абоне та содержит адрес абонента, признак ошибки в сообщении. Сообщение на выдачу информации (вывод) имеет следующий порядок сло ИС I ИС )ИС Сообщение на прием информации (ввод) имеет следующий порядок слов j ... Все КС, ИС и ОС на выходные шины или с них передаются 17-разрядным последовательным кодом частотой I М с признаком слова. Паузы внутри сообщения и между сообщениями равны 10 МКС. Блок 24 формирует паузу в трех случаях.При вьздаче информации в систему сообщение заканчицается ответным словом. В этом случае пауза формируется при наличии управлякяцего сиг нала с регистра 21 Г признак вьщачи) и сигнала с шины 40 (признак ОС) на входах элемента И 58. С выхо да элемента И 58 сигнал через элемент ИЛИ 59 поступает на запускающий вход счетчика 60, разрешая поступление счетных импульсов от генератора 13 на вход счетчика 60. Содержимое счетчика 60 подается на дешифратор 61, который настрюен на определенный код, по времени определяющий паузу. С выхода дешифратора 61 сигнал подается на вход бло ка 28 и на сброс счетчика 60. При приеме информации ст системы сообщение заканчивается выдачей мас сива информационных слов. Б этом сл чае пауза формируется при наличии управляющего сигнала на выходе вычитателя 23 при его обнулении и отсутствии запрещающего сигнала с выхода регистра 21. С выхода элемента И 57 управляющий сигнал через элемент ИЛИ 59 поступает на запуск счет чика 60. При повторении сообщения в случае обнаружения ошибки в сообщении от блока 17 поступает сигнал, который через элемент ИЛИ 59 запускает счетчик 60. При записи информации в ЗУ 30 от процессора по шинам I, 2, Зи 4 поступают соответственно строб, адрес, сигнал записи и информация в блок 6, который вьщает управляющий сигнал на вход блока 25, адрес записьюаемой информации на первый информационный вход мультиплексора 26, информацию на первый информационный -вход мультиплексора 29 и сигнал записи на вход коммутатора 27, с вь1ходов которых информация по адресу и сигналу ЗП поступает в ЗУ 30. Сигнал ЗП коммутатор 27 (фиг. б) передает в ЗУ 30 через элементы И 62, ИЛИ-НЕ 64 или от блока 28 через элементы И 63 и ИПИ-НЕ 64 в зависи-. мости от наличия управляющих сигна- . лов с блока 25. Признак ЗП (запись информации в ЗУ 30) формирует блок 28 (фиг. 9). При наличии сигнала от счетчика 15 и при отсутствии сигнала от блока 24 на входах элемента И-НЕ 69 сигнал ЗП (без паузы) с элемента ИЛИ-НЕ 70 поступает в блок 27. Аналогично при наличии сигнала от блока 24 триггер 71 срабатьгоает и через элемент ИЛИ-НЕ 70 сигнал ЗП с задержкой на паузу поступает в блок 27. . При считывании информации по шинам 1 и 2 поступают строб и адрес в блок 6, который выдает сигналы на входы блока 25 и мультиплексора 26, с выхода которого адрес поступает на вход ЗУ 30. При этом выходная информация из ЗУ 30 и управляющий .сигнал с вьпсода коммутатора 27 поступают на входы блока 6 и далее через шину 5 - в процессор. Работа устройства для обмена информацией с абонентами при вьщаче . информации происходит следующим образом . После подготовки технического задания в ЗУ 30 процессор устанавливает информацию в регистр 7 через блок 6 ( например, 16-разрядное число). Один разряд регистра 7 предназначен 7 для включения счетчика 12 и разреше ния работы дешифратора 9 нуля. Несколько разрядов, например восемь, предназначены для выбора начального адреса зоны ЗУ 30, откуда должна считьюаться информация для выдачи в систему. Они переписываются из регистра 7 в счетчик 12. Несколько разрядов, например шесть, предназна чены для выбора количества слов, вы даваемых по заданию. Они переписываются из регистра 7 в вычитатель 8 Один разряд регистра 7 является при знаком КС и записывается в ЗУ 30 17-разрядом одновременно при записи информации от процессора. Таким образом, записью, в ЗУ командного слова процессор в регистре 7 должен установить признак КС. Генератор 13 выдает импульсы, которые через элемент И-ИЛИ 14 пост пают на счетный вход счетчика 15, который считает количество импульсо определяющее разрядность слова. Счетчик 15 выдает сигнал Конец слова, который поступает на счетны вход счетчика 12. На выходе счетчик 12 появляется адрес ЗУ. 30, который поступает на мультиплексор 26. Одно временно сигнал с выхода счетчика 1 поступает на вхсды блоков 25 и 28. Блок .28 формирует сигнал записи, поступающий на коммутатор 27. При поступлении сигнала с выхода блока 25 на выходе мультиплексора 26 появляется адрес, который подается на адресный вход ЗУ 30, откуда считывается информация (|-1б разрядов) и подается на вход блока 31 и на со ответствующий вход сдвигового регистра 22. Одновременно на выходе коммутатора 27 появляется управляющий сигнал, который поступает на управляющий вход сдвигового регист ра 22, 17-й разряд информации с вто рого выхода ЗУ 30 поступает на триг гер 32, выход которого соединен с шиной 36. При наличии сигнала на выходе триггера 32 происходит запись информации в регистр 21 и запись содержимого счетчика 12 в регистр 11. Несколько разрядов КС содержит адрес абонента, который с выхода регистра 21 поступает на вход блока 17. Кроме того, один разряд регистра 21 содержит признак прием-вьща30ча, который поступает на элемент И-ИЛИ 14, означает выдачу информации и разрешает прохожденива тактовых импульсов от генератора 13 через элемент И-ИЛИ 14 на вход счетчика 15. Следующие несколько разрядов регистра 21 означают количество информационных слов, содержащихся в сообщении. Это количество слов с выхода регистра 21 поступает на вход вьиитателя 23. В 17-й разряд сдвигового регистра 22 из блока 31 записывается . зультат подсчета четности информации, поступающей из ЗУ 30 в сдвиговый регистр 22. По тактовым импульсам, поступающим от генератора 13 на синхронизирующий вход сдвигового регистра 22, информация последовательно выталкивается в систему через шину 35. Одновременно тактовые импульсы через шину 34 передаются в систему. По окончании передачи слова в систему счетчик 15 вьщает сигнал Конец слова, который изменяет адрес на +I в счетчике 12, вычитает, единицу из вычитателя 23 и обнуляет блоки 20, 31 и триггеры 32 и 33. Адрес через мультиплексор 26 поступает в ЗУ 30, из которого считывается информация на вход сдвигового регистра 22 и на вход блока 31. Кроме того, 17-й разряд поступает на триггер 33 и далее на шину 37. Аналогичным образом из ЗУ 30 вьщаются все информационные слова, при этом каждый раз прибавляется +1 в счетчик 12 адресов и вычитается -1 из вычитателя 23. При обнулении на выходе вычитателя 23 появляется сигнал, который поступает на элемент И-ИЛИ 14 и запрещает прохождение импульсов от генератора I3 на вход счетчика 15. Затем по шине 38 в устройство поступает пауза длительностью 10 мне которую анализирует счетчик 16, и на его выходе появляется сигнал, разрешающий прохождение синхроимпульсов, поступакяцих по шине 38. По синхроимпульсам код записывается в сдвиговый регистр 22, а са.ми синхроимпульсы поступают на счетный вход счетчика 15, который выдает сигнал Конец слова, поступающий на счетчик 12, формируя адрес для записи ОС в ЗУ 30. с выхода счетчика 15 сигнал поступает в блоки 28 и 25. В случае обнаружения ошибки бло 17 вьщает сигнал в счетчики 18 и I2, вычитатель 8 и блок 24. Прием информации от абонентов системы производится аналогичньм о разом согласно указанному вьше порядку слов. По адресу от счетчика 12 выбирается из ЗУ 30 КС и через регистр 22 передается на шину 35. Одновременно из ЗУ 30 выбирается признак КС, который поступает на вход.триггера 32. На управляющем выходе регистра 21 появляется сигнал, который поступает на элемент И-ИЛИ 14 и в блок 24. После выдачи КС анализируется пауза, затем поступает ОС, которое записывается в сдвиговый регистр 22, анализируется на четность в блоке 20. Одновременно производится проверка адреса в ОС. С этой целью разряды, содержащие адрес абонента в ОС, с выхода регистра 22 поступают на вход блока 17, а разряды регистра 21, содержащие адрес абонента в КС, подаются в блок 17. Если нет ошибки в приеме, блок 17 не сраба тьшает, а с выхода счетчика 16 на 3010 вход элемента И-ШШ 14 поступает сигнал, разрешающий прохождение через него синхроимпульсов с шины 38. Счетчик 15 производит подсчет синхроимпульсов и вырабатывает сигнал Конец слова, поступающий в блок 25, счетчик 12, блоки 28, 20, 31 и триггеры 32, 33. По сигналу с выхода блока 25 производится запись информации со сдвигового регистра 22 в ЗУ 30. Каждый раз, когда изменяется содержимое счетчика 12 на единицу, из вычитателя 8 вычитается единица. При обнулении вычитателя 8 срабатывает дешифратор 9 и вырабатьшается сигнал прерывания процессора, сообщая программе об окончании работы с абонентами через шины 34-41 по техническому заДанию, сформированному программой. Во время работы устройства с системой процессор может готовить в ЗУ 30 другое техническое задание через блок 6, блок 25, мультиплексоры 26, 29 и коммутатор 27. Таким образом, устройство обеспечивает повышение быстродействия за счет осуществления независимых обменов между процессором и устройством ввода - вывода.

л rf li

44

«6л.26

45

АЛ, г

43

lU

ц«

emf/t-fff-t

Omffn

$г

ОтргЛ

О/я СУ Л

dmSA.id

S3

ОпГГИ 13

ffmS/f, 17

ffmS/r. 25

61

OfrrS/t.S

}-

От5л.25

63

От 5 ft. 28

-i

65

66

ffmfv./S

6S

71

ffmS/t. 24Фие. 5

H6/t.ZO

64

S7

-

pr2Z

65

Фиг. 6

70

-

Фи9.7

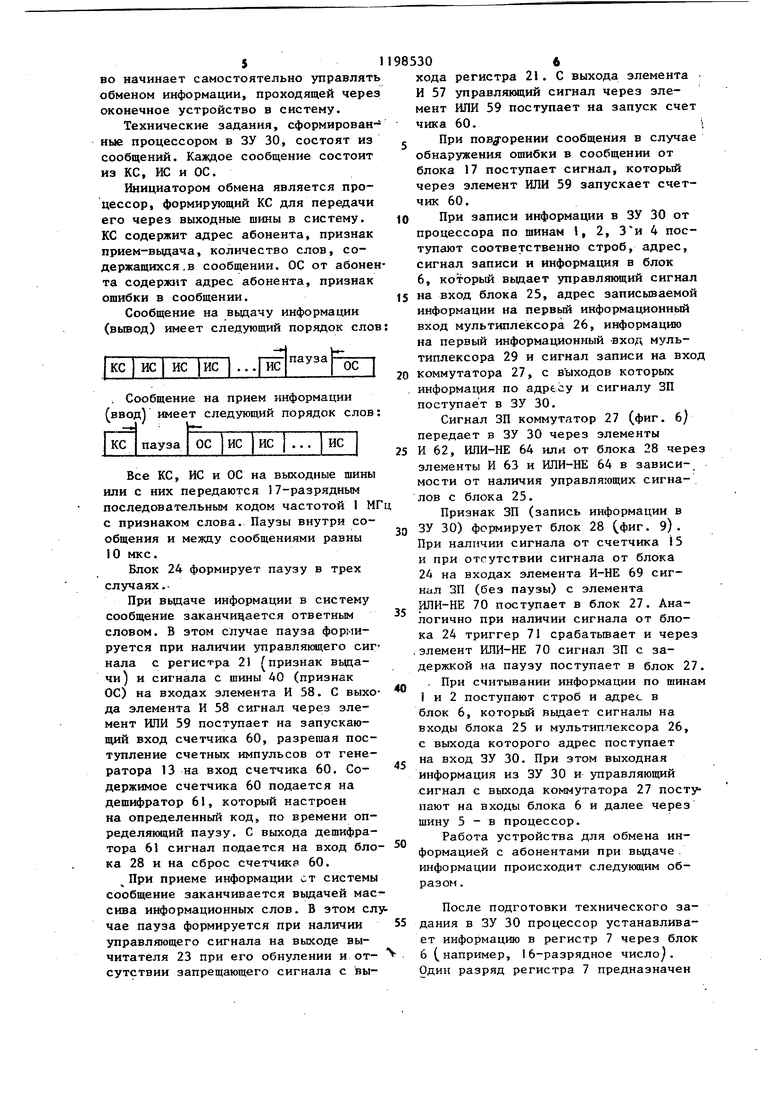

аписо mexHut ecffoeo давания ff ЗУЗО

(процессором уере 5лон 6 и шины i 5)

Настрой на устрдйстВа на ра5о тусмоеистралью путем дстанобни соотВетству/оЩ(/)(. призианоВ 8 peeifompe 7 (лрас ессорам ерез 5лом 6 а шины f-5)

/ оо /ередная Btubopna сообщений из ЗУЗО в соответствии с mexHut ecHu 5одоние.М, передав/о их (/fC а С) о шииу

35 14 ггрием

(ffCuOC) В ШО с W /Tpt/ f/a uvutf упрс/в/г юи/(/з. //a

Ъг 38. 0.1

y fOmwa св;гза впроffPfP о /rpolfeccop п0цессор /rott/t/ffe 9 при отu/uf/e fO /70 ffftoftvofft/u 9b//fe оииатель /х реау ьтоf/efft/я mexHt/ve c oeo

a oHUJt us.8 нтрау,

Участвуют 5лоии 6.25.26Д ШВ. Оишины 1-5

|jчac/тtB |Юfn

Ofta 6.7.8.3.12 и шины f 5

У facm8t/юm SflOfiU В.9./0. Г/-24.. 30-3 и шины

Mava/fO

1

сигналво от процессора по шинам в 6л 6

Зо/гис управ /в

щего cjtoBo от npot eecopo S ffpt/€M ct/etfa oS от процессоре по шинам в 5л. 6

Запись cuef vjjct „СтроУ В S/f. 25

Запись ffojfuчеопВа с/гo8 Водном cooSufCffuu в аычи/ла/пе г Zo

pi upoffoHue cufHcf/Ja., Ho/fet4 Влонами /Д/

rs

1 ffct/emnuf y адресов IZ Запись ffoda о шеео количестоа cjroS 8 8wvu/na тем 8 из 7

B ibopHd (/a t/3ffnu 8c98tteO регистр 22

/fCt/ tjf/C

opffi/poffc/ e/e ff

S/Kwe 3tcc/effcf/fcf vemnocmua запись его 8 c ffusoSou pesuc/nf) 22

uspest/cfftpo 21

Риг.З S f uma/rre/reu ло/foS 8 и 2:5 Sonuctt „СтроЪ 8 5л. 25 opf upoodMue адреса, npaiftOffaSfi UWCffO O Offy/ t/ 26.27u29 8 ЗУ50

O evyifvt ifC

JSE:

fltptaaw npuwoffd ИСнд u/t/t/t/ 37

ntpfjava. признака КС на шику 36

,, f.fx f j ffui/a

из ЗИЗО fffetvmjo vooHftJuf NOf aM HOго cjiata 21

fftofnycii a ctcfl t2мж

ttfco КС Spff vpai). afptcaff

l/fm

Фвр1 р«1амие fjv

ivtuSevifOMrflKP f npetticce /

tuunrw .1

I

4hM4r А««пм1гмиг 9ei«M4f

Фop upoЙoнut

че 8смиала„вт 1ол Iff /

| Устройство для сопряжения вычислительной машины с каналами связи | 1977 |

|

SU703799A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1975 |

|

SU579607A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1983-10-12—Подача