(5) УСТРОЙСТВО ДЛЯ ОБМЕНА ДВУХМАШИННОГО ВЬИ СЛИТЕЛЬНОГО КОМПЛЕКСА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532937A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

,

Изобретение относится к вычисли тельной технике, в частности к устройствам сопряжения, и может быть использовано при объединении в вычислительную систему двух цифровых вычислительных машин, работающих в реальном масштабе времени, через интерфейсы ввода-вывода. Известны устройства для сопряжения цифровых вычислительных машин, содержащие блоки синхронизации и управления микрооперациями, блок формирования сигналов прерывания, дешифратор команд, блок дешифрации и сравнения адресов, регистр состояния, буферный регистр, выходной и входной блоки согласования, шифратор команд, счетчик слогов, генератор импульсов, имитатор кодов номеров зон, причем первый блок синхронизации и управления микрооперациями соединен с блоком формирования сигналов прерывания, с дешифратором команд, с блоком дешифрации и сравнения адресоа, с регистром состояния, с буферным регистром, с выходным блоком согласования и с вторым блоком синхронизации и управления микрооперациями, который соединен с шифратором команд, счетчиком слогов, с генератором импульсов, с имитатором кодов номеров зон, с буферным регистром, который подключен к входному блоку согласования 1 .

10

Недостатком этих устройств является необходимость применения быстродействующего аппарата обработки прерываний и ответвление программы от хода решения основных задач 5 обработки внешнего прерывания, что приводит к уменьшению производительности вычислительного комплекса и снижению пропускной способности ка нала.

20

Наиболее близким к предлагаемому по технической сущности являетея устройство для сопряжения ЭВМ, содержащее два буферных регистра, блок управления обменом, блок подсчета вр мени, регистр словосостояния и два блока выдачи информации, причем соответствующие входы и выходы блока управления обмена являются управляющими входами и выходами устройству, а группа выходов подключена к управляющим входам регистра словосостояния, блоков выдачи и буферных регистров, информационные входы и выходы которых являются информационными входами и выходами устройства 2 Недостаток этого устройства состоит в низкой производительности. Целью изобретения является повышение производительности вычислитель ного комплекса путем выполнения операций по аппаратурной обработке информации без участия в ходе обмена самих процессоров. Поставленная цель дос гигается тем, что в устройство, содержащее регистр приема информации, вход которого является информационным входом устройства, кбнтроллер обмена, вход-выход которого является входомвыходом устройства, а первый и второ выходы подключены соответственно к первым входам регистра базы обмена и регистра выдачи информации, выход ко торого является информационным выхо дом устройства, введены дешифратор команд, регистр текущего адреса, три гер блокировки, триггер запроса и дв элемента И, причем первый выход регистра приема информации подключен к первым входам контроллера обмена, де шифратора команд и регистра текущего адреса, выход и второй и третий входы которого соединены соответственно с адресным выходом устройства и выхо дом регистра базы обмена и третьим выходом контроллера обмена, четвертым выходом соединенного с вторыми входами регистра выдачи информации и регистра базы обмена, а вторым и третьим входами и пятым-восьмым выхо дами - соответственно с вторым входо регистра приема информации, первым выходом триггера блокировки, вторым входом дешифратора команд и первыми входами триггера запроса, первого эл мента И и триггера блокировки, второ выход и вход которого подключены соответственно к первому входу второго элемента И и выходу первого элемента И, вторые входы которых соединены со ответственно с первым и вторым выход ми триггера запроса, вторым входом соединенного с первым выходом дешифратора команд, второй выход которого подключен к третьему входу регистра выдачи информации, четвертым входом соединенного с выходом второго элемента И и четвертым входом регистра текущего адреса. Контроллер обмена содержит коммутатор интерфейсных шин, вход-выход и выход-которого являются соответственно входом-выходом и четвертым выходом контроллера, блок формирования микрокоманд, первая группа выходов которого соединена с пятым, седьмым, восьмым и вторым выходами контроллера, счетчик модификации числа слов, выход которого является шестым выходом контроллера, блок приоритета, первые вход и выход которого являются соответственно третьим входом и первым выходом контроллера, дешифратор команд и блок элементов И, информационные входы которых соединены с первым входом контроллера, и блок дешифрации команд обращения к памяти, причем первый, второй и третий входы счетчика модификации числа слов соединены соответственно с первым входом и первым, и вторым выходами блока формирования команд, второй вход И вторая группа выходов которого подключены соответственно к второму входу контроллера, второму входу и группе входов блока приоритета, а третьи вход и выход - соответственно к выходу и управляющему входу дешифратора команд, группа выходов которого соединена с группой входов счетчика модификации числа слов, первым входом подключенного к выходу коммутатора интерфейсных шин, вход которого соединен с выходами блока элементов И и блока приоритета, второй выход и третий.вход которого подключены соответственно к первым входу и выходу блока дешифрации команд обращения к памяти, второй и третий выходы которого соединены соответственно с третьим выходом контроллера и управляющим входом блока элементов И. Блок формирования микрокоманд содержит адресный регистр, два сдвиговых регистра, дешифратор и коммутатор, причем вход, выход и группа выходов адресного регистра соединены соответ г ственно с первым входом блока и первым и вторым входами первого сдвигового регистра и группой входов дешифратора, первый вход которого соеди- нен с третьим входом первого сдвигового регистра; группа выходов которого подключена к второй группе входов коммутатора, а выход - к первому входу второго сдвигового регистра, второй и третий входы, выход и группа выходов которого соединены соответстченно с вторым и третьим входами блока, вторым выходом блока и третьей группой .входов коммутатора, первыйt второй выходы и две группы выходов которого являются соответственно первым и третьим выходами блока и первой и второй группами выходов лока

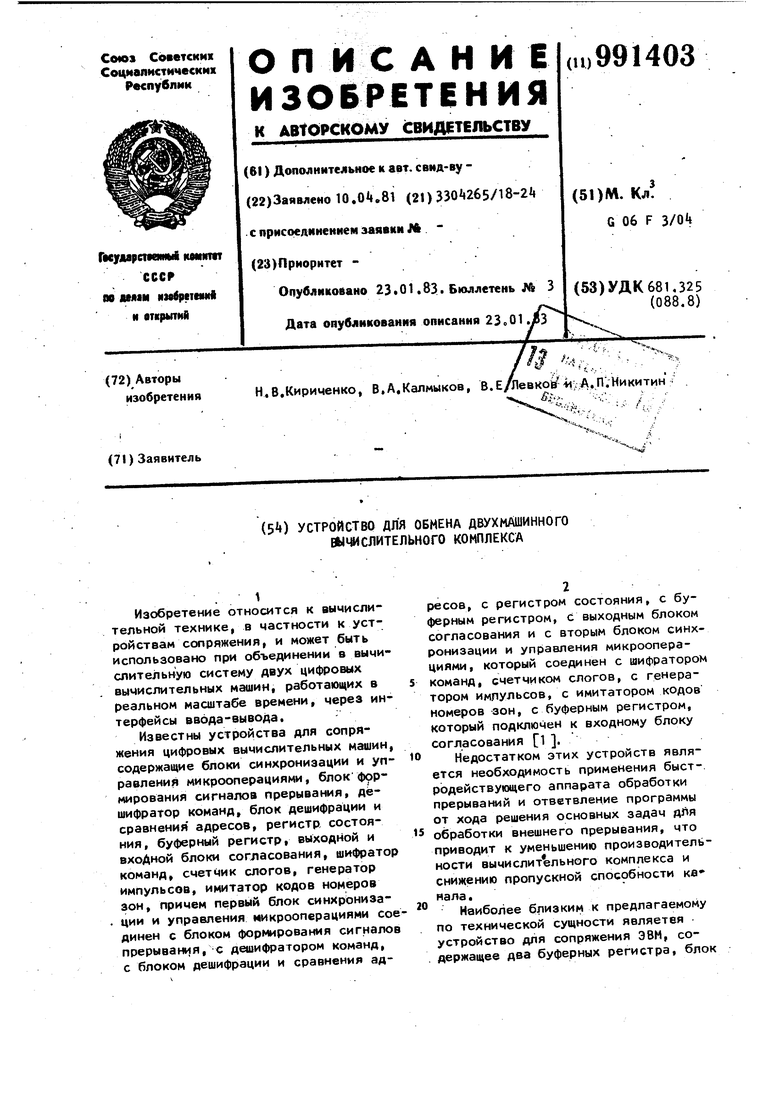

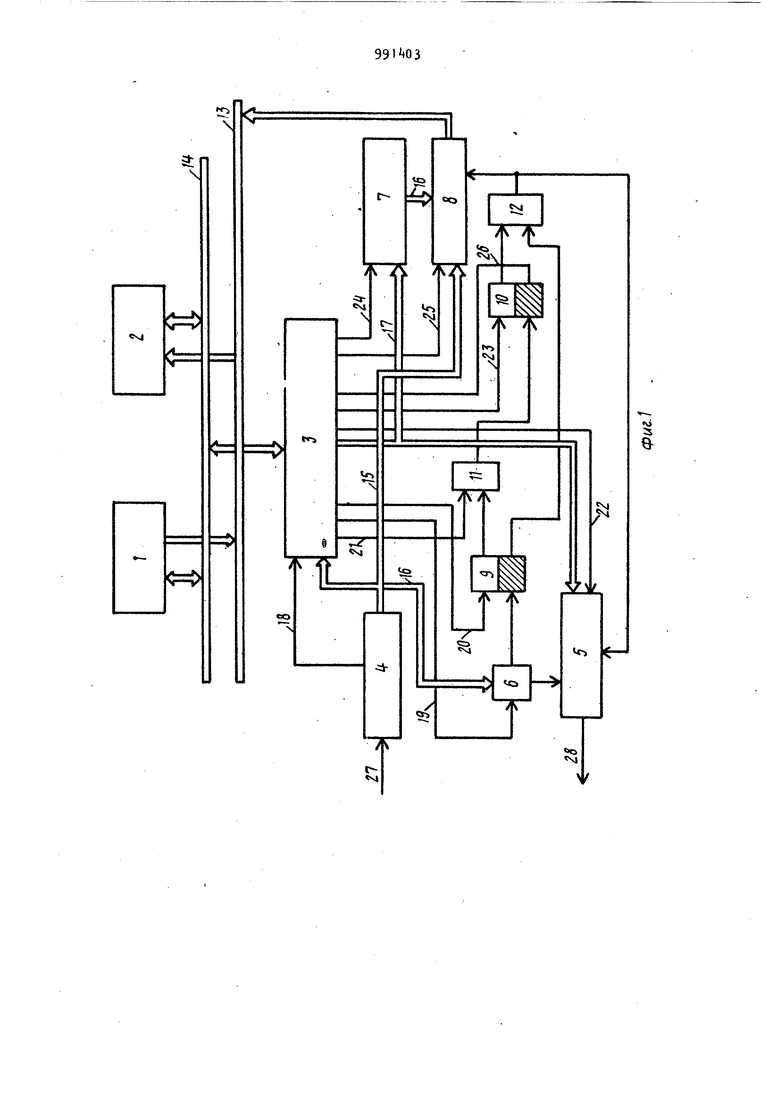

На фиг, 1 представлена блок-схема устройства; на {)иг. 2-7 - функциональные схемы контроллера обмена коммутатора интерфейсных ижн, дешифратора служебных сигналов блока формирования микрокоманд, блока приоритета и блока дешифрации команд обращения к памяти.

Устройство (фиг. 1) подключено к процессору 1 и запоминающему устройству (ЗУ) 2 и содержит контроллер 3 обмена, регистр k памяти информации, регистр 5 выдачи информации, дешифратор 6 служебных сигналов,регистр 7 базы обмена, регистр 8 текущего адреса, триггер 9 запроса, триггер 10 блокировки, элементы И 11 и 12, магистраль 13 адресов, магистраль 14 данных, магистраль 15 данных обме на, магистраль 17 адресов и данных контроллера обмена, идину 18 признака конца слова, шины управления контроллера обмена, шину 26 блокировки, шины 27 информационного входа и UJHHM 28 информационного выхода устройства,

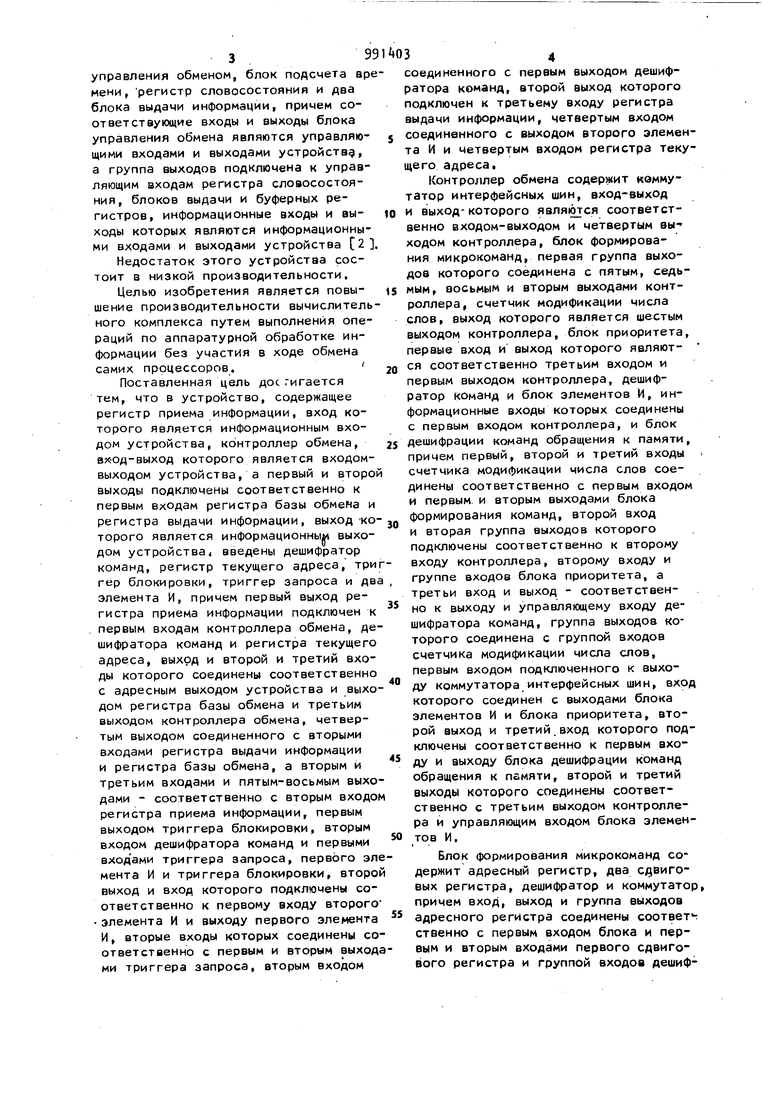

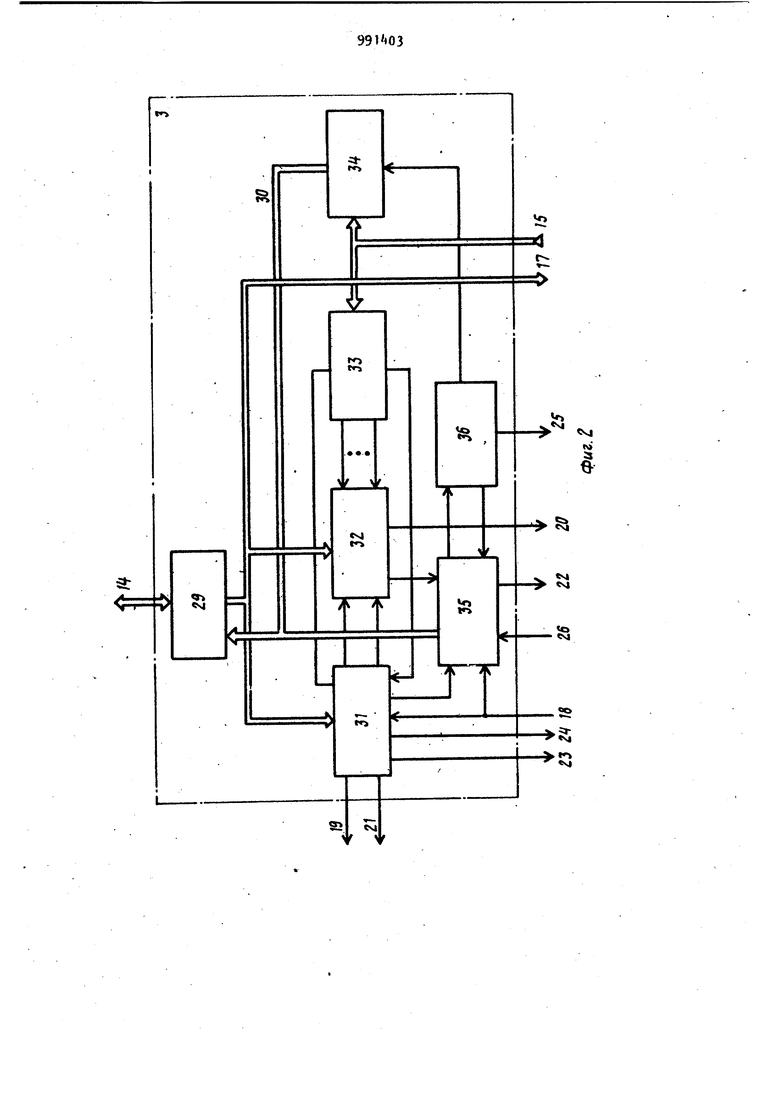

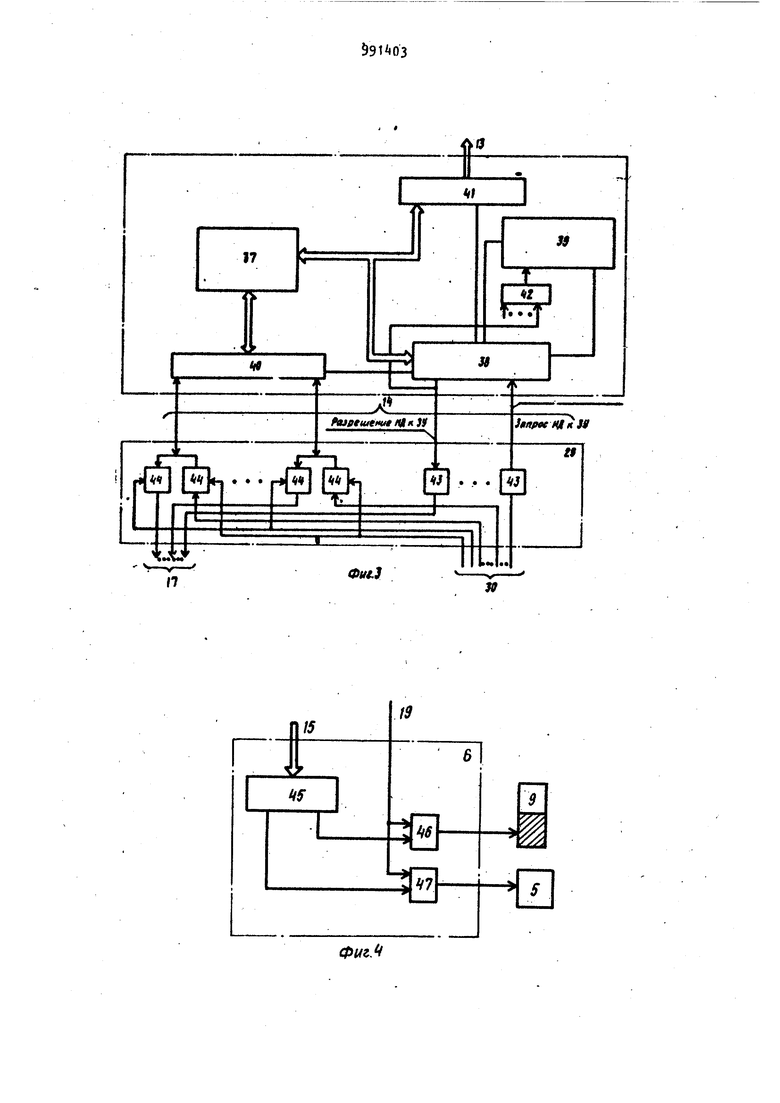

В состав контроллера 3 обмена (фиг, 2) входит коммутатор 29 интерфейсных шин, предназначенных для сопряжения двунаправленной магистрали 1 данных с внутренней магистралью 30 данных контроллера и магистралью 17 адресов и данных, блок 31 формирования микрокоманд, счетчик 32 модификации числа 51ов,обеспечивакичий отсчет требуемого числа слов и сеанс обмена, дешифратор 33 команд, блок И элементов 3 блок 35 приоритета, обеспечивающий выполнение режимов непосредственного доступа (НД) к запбминающему устройству 2 как со ;тороны процессора 1, так и со стороны самого канала обмена, а также разрешающий Конфликтные ситуации при одновременном запросе на обмен со стороны двух процессоров, и блок 36 дешифрации комаквд обращения и памяти. . Процессор 1 (фиг, 3) содержит,1 например, операционное устройство37 устройство 38 управления, блок 39 синхронизации, двунаправленные элементы И kO магистрали И данных. Однонаправленные элементы И 4), магистрали 13 адресов, элемент ИЛИ (2, Структурная операционного устройства 37 устройства 38 управления и блока 39 синхронизации выполнена по классической схеме процессоров и отличается только лишь формированием сигнала Останов блока 39 nq сигналу Разрешение НД к ЗУ.

Коммутатор 29 интерфейсных шин состоит фиг. З) из однонаправленных элементов И 3 и двунаправленных элементов И причем однонаправленные элементы И 43 предназначены для передами управляк|щйх сигналов а двунаправленные элементы 44 И - для передчи адресов ч данных. I

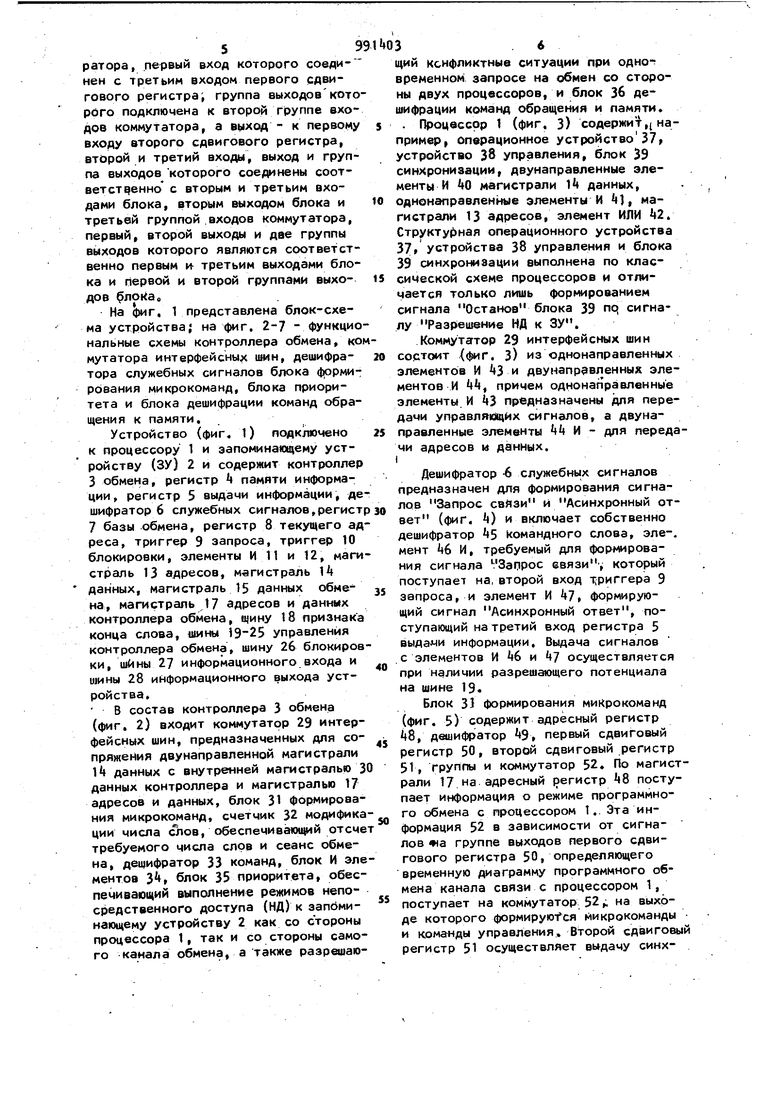

Дешифратор -6 служебных сигналов предназначен для формирования сигналов Запрос связи И Асинхронный ответ (фиг. 4) и включает собственно дешифратор 45 Командного слова, эле-, мент 46 И, требуемый для формирования сигнала Запрос евязи , который поступает на, второй вход 1;риггера 9 запроса, и элемент И 47, формирующий сигнал Асинхронный ответ, поступающий на третий вход регистра 5 выдачи информации. Выдача сигналов ,с элементов И 46 и 47 осуществляется при наличии разрешающего потенциала на шине 19.

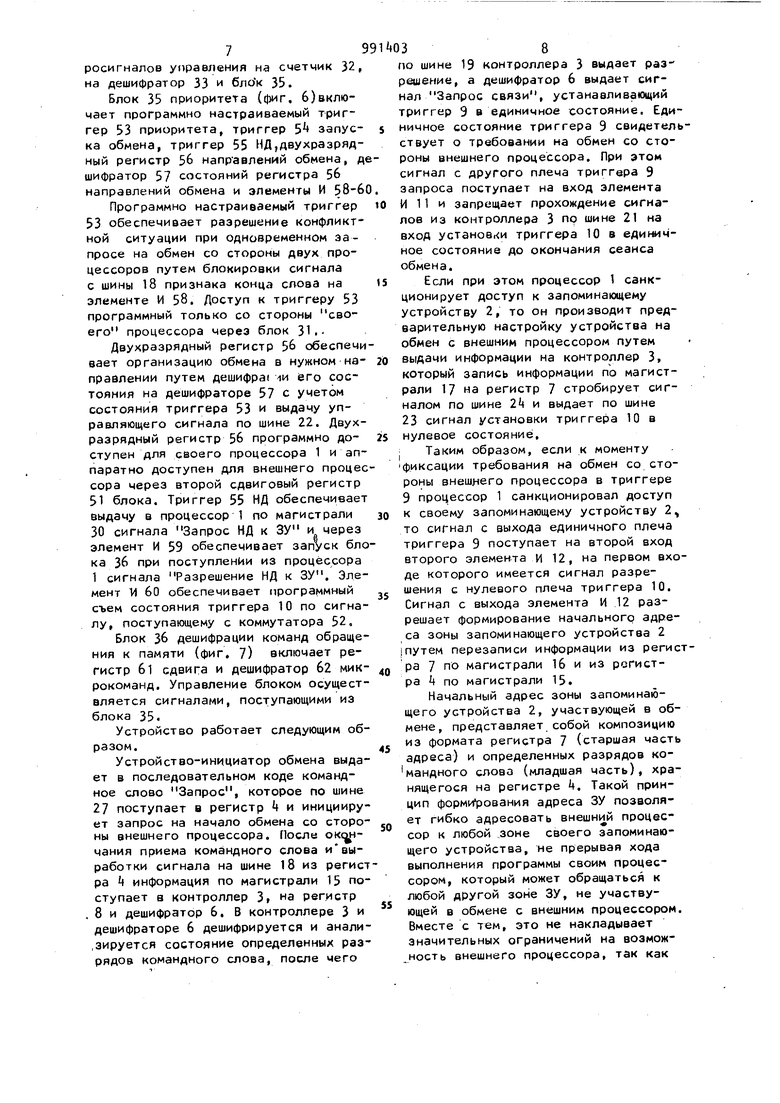

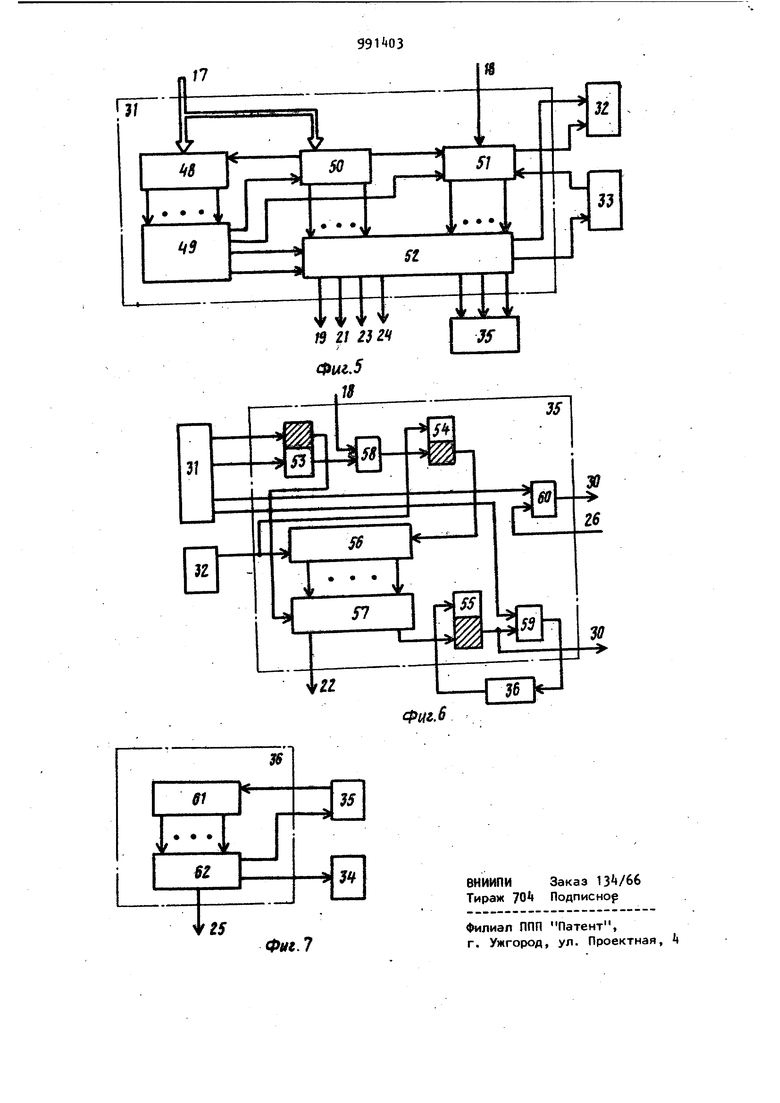

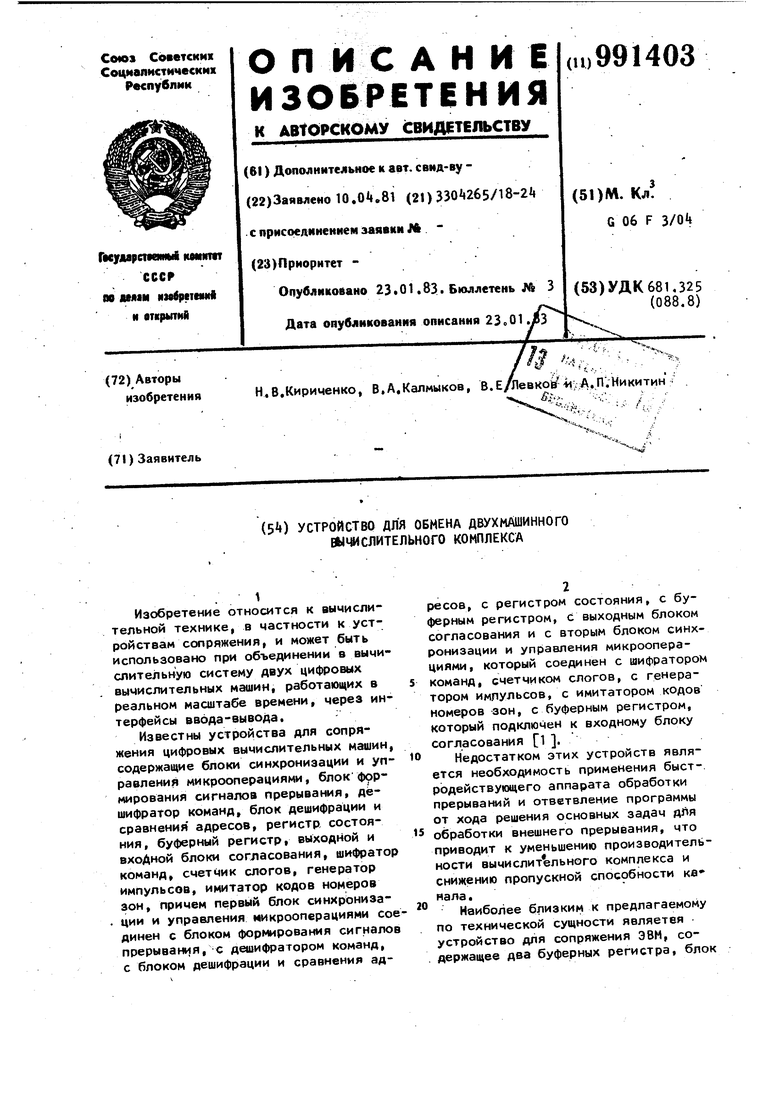

Блок 3J формирования микрокоманд (фиг. 5) содержит адресный регистр 48, дешифратор 49, первый сдвиговый регистр 50, второй сдвиговый регистр 51, группы и коммутатор 52. По магистрали 17 на адресный регистр 48 поступает информация о режиме программного обмена с процессором 1.. Эта информация 52 в зависимости от сигналов «на группе выходов первого сдвигового регистра 50, определяющего временную диаграмму программного обмена канала связи с процессором 1, поступает на коммутатор 52,; на выходе которого формируются микрокоманды и команды управления. Второй сдвиговы регистр 51 осуществляет выдачу синхросигналов управления на счетчик 32, на дешифратор 33 и блок 35. Блок 35 приоритета (фиг. 6)включает программно настраиваемый триггер 53 приоритета, триггер 5 запуска обмена, триггер 55 ИД,двухразрядный регистр 5б направлений обмена, д шифратор 57 состояний регистра 56 направлений обмена и элементы И 58-6 Программно настраиваемый триггер 53 обеспечивает разрешение конфликтной ситуации при одновременном запросе на обмен со стороны двух процессоров путем блокировки сигнала с шины 18 признака конца слова на элементе И 58. Доступ к триггеру 53 программный только со стороны своего процессора через блок 31.Двухразрядный регистр 5б обеспечи вает организацию обмена в нужном направлении путем дешифра 1И его состояния на дешифраторе 57 с уметом состояния триггера 53 и выдачу управляющего сигнала по шине 22. Двухразрядный регистр 56 программно доступен для своего процессора 1 и аппаратно доступен для внешнего процес сора через второй сдвиговый регистр 51 блока. Триггер 55 НД обеспечивает выдачу в процессор 1 по магистрали 30 сигнала Запрос НД к ЗУ и через элемент И 59 обеспечивает запуск бло ка 36 при поступлении из процессора 1 сигнала Разрешение НД к ЗУ. Элемент V) 60 обеспечивает программный съем состояния триггера 10 по сигналу, поступающему с коммутатора 52, Блок 36 дешифрации команд обращения к памяти (фиг. 7) включает регистр б1 сдвига и дешифратор б2 микрокоманд. Управление блоком осуществляется сигналами, поступающими из блока 35. Устройство работает следующим образом. Устройство-инициатор обмена выдает в последовательном коде командное слово Запрос, которое по шине 27 поступает в регистр k и инициирует запрос на начало обмена со стороны внешнего процессора. После OKCJHчания приема командного слова ивыработки сигнала на шине 18 из регист ра информация по магистрали 15 поступает в контроллер 3, на регистр , 8 и дешифратор 6. В контроллере 3 и дешифраторе 6 дешифрируется и анали.зируется состояние определенных разрядов командного слова, после чего ПО шине 19 контроллера 3 выдает разрешение, а дешифратор 6 выдает сигнал Запрос связи, устанавливающий триггер 9 в единичное состояние. Единичное состояние триггера 9 свидетельствует о требовании на обмен со стороны внешнего процессора. При этом сигнал с другого плеча триггера 9 запроса поступает на вход элемента И 11 и запрещает прохождение сигналов из контроллера 3 по шине 21 на вход установ,и триггера 10 в единичное состояние до окончания сеанса обмена. Если при этом процессор 1 санкционирует доступ к запоминающему устройству 2, то он производит предварительную настройку устройства на обмен с внешним процессором путем выдачи информации на контроллер 3, который запись информации по магистрали 17 на регистр 7 стробирует сигналом по шине 2k и выдает по шине 23 сигнал установки триггера 10 в нулевое состояние, Таким образом, если к моменту фиксации требования на обмен со стороны внешнего процессора в триггере 9 процессор 1 санкционировал доступ к своему запоминающему устройству 2, то сигнал с выхода единичного плеча триггера 9 поступает на второй вход второго элемента И 12, на первом входе которого имеется сигнал разрешения с нулевого плеча триггера 10. Сигнал с выхода элемента И 12 разрешает формирование начального адреса зоны запоминающего устройства 2 путем перезаписи информации из регистра 7 по магистрали 16 и из регистра k по магистрали 15. Начальный адрес зоны запоминающего устройства 2, участвующей в обмене, представляет собой композицию из формата регистра 7 (старшая часть адреса) и определенных разрядов командного слова (младшая часть), хранящегося на регистре k. Такой принцип формирования адреса ЗУ позволяет гибко адресовать внешний процес сор к любой ,зоне своего запоминающего устройства, не прерывая хода выполнения программы своим процессором, который может обращаться к любой другой зоне ЗУ, не участвующей в обмене с внешним процессором. Вместе с тем, это не накладывает значительных ограничений на возможность внешнего процессора, так как отведение определенного количе,ства разрядов адреса под младшую часть (из числа разрядов командного слова Запрос) позволяет широко оперировать выбором конкретных ячеек в отведенной зоне-запоминающего устройства. Формирование последующих адресов для данного сеанса обмена производится путем модификации образованного начального ад реса. С целью исключения возможности несанкционированного доступа к ЗУ со стороны внешнего процессора или получения им некомплектной информации .(под некомплектной информацией понимается информация состоящая из данных разных тактов решения какойлибо задачи) в устройство введены два элемента И и триггер 10. Если со стороны процессора 1 отсутствует разрешение на обмен, то триггер 10 находится в единичном состоянии, блокирует на элементе И 12 прохожде ние сигнала разрешения на формирование в регистре 8 текущего адреса 3 а поми нающе го у ст р ой ст ва, а эл емен т И 11 исключает возможность обращения своего процессора к зоне обмена запоминающего устройства в тот м мент времени, когда с нИм работает внешний процессор. Сигнал с выхода элемента И 12 по ступает одновременна на входы регистров 5 и 8. На регистре 5 при на личии этого сигнала и сигнала Асин ронный ответ с дешифратора 6 вырабатывается командное слово Асинхро ный ответ, которое затем по шине 28 передается в смежное устройство указывает на готовность к обмену информации. Возможны два режима работы устро ства: режим приема информации и ре жим выдачи информации. В режиме приема информации после выдачи в смежное устройства командного слова Асинхронный ответ в регистр k по шине 2 поступают информационные слова. После получения сигнала по шине 18 контроллер 3 об мена вырабатывает сигнал Запрос НД к ЗУ, поступающий в процессор 1, После получения этого сигнала процессор 1 вырабатывает сигнал Разрешение НД, поступающий в контроллер 3 где формируется временная ди аграмма НД к ЗУ. При этом, по сигна лу из контроллера 3 Вызов адреса. 310 поступающему по шине 25 на вход регистра 8, на магистраль 13 выдается содержимое этого регистра, а на магистраль I из контроллера 3 выдается содержимое регистра 1, из контроллера 3 выдается содержимое регистра k. Прием следующих информационных слов производится аналогично. После окончания обработки последнего принятого слова (число слов задается в содержимом командного слова Запрос) контроллер 3 по шине 20 устанавливает триггер 9 в нулевое состояние. В режиме выдачи информации после выдачи в смежное устройство командного слова Асинхронный ответ консигнал За3 вырабатывает троллер прос НД к ЗУ, поступающий в процессор 1. После получения этого сигнала процессор 1 выдает в контроллер 3 сигнал Разрешение НД, где формируется временная диаграмма -НД к ЗУ в режиме чтения информации из запоминающего устройства 2. При этом по сигналу Вызов адреса,поступающего из контрЬллера 3 по шине 25, на магистраль 13 выдается содержимое регистра 8. По этому адресу из ЗУ 2 на магистраль выдается содержимое указанной ячейки запоминающего устройства 2. Информация с магистрали 1 через . контроллер 3 по магистрали 16 поступает на информационные входы регистра 5. Загрузка информации в регистр 5 стробируется сигналом, поступающим по шине 22 из контроллера 3. Из регистра 5 информация по шине 28 передается в смежное устройство. После окончания выдачи последнего слова контроллер 3 по шине 20 устанавливает триггер 9 в нулевое состояние. Обращение процессора 1 к зоне запоминающего устройства 2, выделенной для обмена, возможно только после окончания сеанса обмена с ней внешнего процессора. При этом процессор 1 обращается к контроллеру 3i который вырабатывает по шине 21 сигнал установки триггера 10 в единичное состояние. Если к этому моменту сеанс обмена с внешним процессором не закончен, запись 1 в триггер 10 не производится, таккак прохождение сигнала происходит по шине 21 на триггера 9 на элементе И П. В данной ситуации процессор 1 выбирает другую зону запоминающего устройства 2, произВОДИТ загрузку а нее информации и пе рзкастраивает свое устройство на работу с вновь выбранной зоной, путем записи в регистр 7 старшей части адреса выбранной зоны. Если сеанс обме на закончен, сигнал шины 21 через эл мент И 11 проходит на триггер 10 и устанавливает его в единичное состояние. В этом случае сигнал с выхода триггера 10 по шине 26 поступает в контроллер 3 и информирует процессор 1 с предоставлением ему возможности работы с зоной обмена запоминающего устройства 2, а выход с другого плеча триггера 10 блокирует формирование адреса ЗУ 2 в регистре 8 и командного слова Асинхронный отает в регистре 5. если в этот момент фиксируется командное слово За прос от внешнего процессора. После окончаний работы процессора 1 с зоной обмена запоминающего устройства 2 процессор 1 обращается к контроллеру 3, который вырабатывает на ши|Не 23 сигнал обнуления триггера 10, таким образом, обеспечивая готовност информации в зоне обмена для пользования ею внешним процессором. Возможна ситуация, когда могу.т быть одновременно зафиксированы принятое в регистр 4 командное слово Запрос и выданное из регисАа 5 собственное командное слово Запрос Данная конфликтная ситуация может бы разрешена путем присвоения приоритета в контроллере 3 какому-либо из процессоров, при этом из канала с ни шим приоритетом выдается командное слово Асинхронный ответ, санкционирующее начало обмена в нужном направлении. Таким образом, устройство обеспечивает более производительный обмен информацией между процессорами двухмашинного вычислительного комплекса за счет обеспечения возможности независимого обращения каждого процессора к ЗУ другой машины без предварительной программной настройки. Формула изобретения 1е Устройство для обмена двухмаши ного вычислительного комплекса, содержащее регистр приема информации, вход которого является информационным входом устройства, контроллер обмена, вход-выход которого является входом-выходом устройства, а первый и второй входы подключены соответственно к первым входам регистра базы обмена и регистра выдачи информации, выдод которого является информационным выходом устройства, отличающееся тем, что, с целью повышения производительности вычислительного комплекса, в устройство введены дешифратор команд, регистр текущего адреса, триггер блокировки, триггер запроса и два эле- мента И, причем первый выход регистра приема Информации подключен к первым входам контроллера обмена, дешифратора команд и регистра текущего адреса, выход и второй и третий входы которого соединены соответственно с адресным выходом устройства и выходом регистра базы обмена и третьим выходом контроллера обмена, четвертым выходом соединенного с вторыми входами регистра выдачи информации и регистра базы обмена, а вторым и третьим входами и пятым - восьмым выходами - соответственно с вторым входом регистра приема информации, первым выходом триггера блокировки, вторым входом дешифратора команд и первыми входами триггера запроса, первого элемента И и триггера блокировки, второй выход и вход которого подключены соответственно к первому входу второго элемента И и выходу первого элJгмeнтa И, вторые входы которых соединены соответственно с первым и вторым выходами триггера запроса, вторым входом соединенного с первым выходом дешифратора команд, второй выход которого подключен к третьему входу регистра выдачи информации, четвертым входом соединенного с выходом второго элемента И и четвертым входом регистра текущего адреса. 2. Устройство по п. 1, отличающееся тем, что контроллер обмена содержит коммутатор интерфейсных шин, вход-выход и выход которого являются соответственно входом- выходом и чзтвертым выходом контроллера, блок формирования микрокоманд, первая группа выходов которого соединена с пятым, седьмым, восьмым и вторым выходами контроллера, счетчик модификации числа слор, выход которого является шестым выходом контроллера, блок приоритета, первые вход и выход которого являют-.

13

ся соответственно третьим входом и первым выходом контроллера, дешифратор команд и блок элементов И, информационные входы которых соединены с первым входом контроллера, и блок дешифрации команд Обращения к памяти, причем первый, второй и третий входы сметчика модификации числа слов соединены соответственно с первым входом и первым и вторым выходами блока формирования микрокоманд, второй вход и вторая группа выходов которого подключены соответственно к второму вхо АУ контроллера, второму входу и груп пе входов блока приоритета, а третьи вход и выход - соответственно к выходу и управляющему входу дешифратора команд, группа выходов которого соединена с группой входов счетчика модификации числа слов, первым входом подключенного к выходу коммутатора интерфейсных шин, вход которого соединен с выходом блока элементов И и блока приоритета, второй выход и третий вход которого подключены соответственно к первым входу и выходу блока дешифрации команд обращения к памяти, второй и третий выходы которого соединены соответствен но с третьим выходом контроллера и управляющим входом блока эл ентов И I 3. Устройство по п. 1 и 3, отличающееся тем, что блок

армирования микрокоманд содержит адресный регистр, два сдвиговых регистра, дешифратор и коммутатор, причем вход, выход и группа выходов ад5 ресного регистра соединены соответственно с первым входом блока и первым и вторым входами первого сдвигового регистра и группой входов дешифратора , первый вход которого с третьим входом первого сдвигового регистра, группа выходов которого подключена к второй группе входов коммутатора, а выход - к первому входу второго сдвигового регистра, второй и третий входы, выход и группа выходов соединены соответственно с вторым и третьим входами блока вторым выходом блока и третьей группой входов коммутатора, первый, второй выходы и две группы выходов которого являются соответ- . ственно первым и третьим выходами блока и первой и второй группами выходов блока. Источники информации, принятые во внимание при экспертизе 1« Авторское свидетельство СССР 9 , кл. G Об F 3/0, 1976. 2. Авторское свидетельство СССР N581467-, кл. G 06 F 3/0, 1975 (прототип).

Q

ЧГ

i 7.

«4

S2

r r

«o

r

:f

i:

v

«4

4 M - M

«o

19

фигМ

рцг.6

Авторы

Даты

1983-01-23—Публикация

1981-04-10—Подача