1

Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных вычислительных систем и в автоматизированных системах контроля и управления технологическими процессами.

Известно устройство обмена информацией, содержащее блок памяти, соединенный двусторонними связями с входами-выходами устройства, регистры записи и чтения с адресной и с первой и второй числовой частью, узлы модификации и дешифраторы 1.

Однако это устройство сложно и наличие в регистрах записи и чтения вторых числовых частей усложняет программу обмена и уменьшает быстродействие устройства.

Наиболее близким по технической сушности к изобретению является устройство, содержаш,ее счетчики ввода и вывода, подключенные к буферному запоминаюш.ему блоку, входы и выходы которого соединены с коммутатором, связанным с абонентами, входы и выходы счетчиков ввода и вывода соединены с узлом модификации управляющих слов, входы и выходы счетчика объема буферной области соединены с узлом модификации управляющих слов и узлом анализа состояний буферных областей, узел модификации управляющих слов связан с ассоциативным запоминающим блоком, входы которого подключены к коммутатору. Устройство обеспечивает одновременный обмен информацией

между абонентами, работающими с различными скоростями. В устройстве за каждой парой абонентов, участвующих в обмене, закрепляется область памяти буферного запоминающего блока. Причем, один из абонентов является передатчиком информации,

10 а другой - приемником. В процессе работы производится последовательное заполнение информацией от абонента-передатчика выделенной буферной области запоминающего блока и после ее заполнения абоненту-приемнику разрешается считывание информации из этой области. Повторное заполнение области разрешается только после полного считывания информации абонентом-приемником из данной области буферного запоминающего блока 2.

20 Однако это устройство обладает следующими недостатками. Разделение абонентов на передатчики и приемники информации ограничивает область применения этого устройства. Так, при организации обмена информацией между двумя и более ЭВМ одни и те же абоненты, между которыми осуществляется обмен информацией, могут являться приемниками и передатчиками информации в зависимости от того, выполняется чтение информации из буферного запоминающего блока или запись в него.

Кроме того, устройства, между которыми осуществляется обмен информацией, работают с информационными словами различной длины, обычно от одного до четырех байтов. Хранение информации в буферном запоминающем блоке побайтно не выгодно, так как это приводит к увеличению объема аппаратуры. В целях универсальности и удобства буферный запоминающий блок может иметь максимальную длину информационного слова до 64 двоичных разрядов (4 байта). В одном слове запоминающего блока может располагаться несколько сообщений, принятых от разных каналов или внешних устройств. Например, для автоматизированных систем управления технологическими процессами или систем обработки данных такими сообщениями могут быть сообщения о состоянии оборудования, цифровые сообщения о выработке продукции или значения технологических параметров. При этом длина сообщения составляет один или несколько байтов. При обработке больщих массивов информации, поступающих от указанных комплексов или систем, нецелесообразно использовать память вычислительной мащины и затрачивать мащинное время на запись в память и последующий анализ всего входного массива, так как обработка разных сообщений, расположенных в каждом слове входного массива, может происходить с циклом различной длительности. Поэтому для повыщения эффективности работы устройства обмена целесообразно производить запись в память вычислительной мащины только тех сообщений входного массива, которые требуются для обработки в данный момент времени.

Цель изобретения - повышение эффективности работы и расширение функциональных возможностей.

Поставленная цель достигается тем, что в устройство для обмена информацией, содержащее блоки сопряжения, первые входы и выходы которых подключены соответственно к входам и выходам устройства, вторые выходы блоков сопряжения соединены с первым входом блока управления, первый выход которого подключен к управляющим входам блоков сопряжения, информационные выходы которых соединены со входом блока регистров управляющего байта, первый и второй выходы которого соединены соответственно со вторым входом блока управления и с первым входом блока формирования адресов, второй вход которого соединен с выходом блока счетчиков ввода-вывода, а выход - подключен к адресному входу

буферного запоминающего блока, введены регистр записи, указатель байтов обмена и коммутатор байтов, выход которого подключен к информационным входам блоков сопряжения, выход регистра записи соединен

с информационным входом буферного запоминающего блока, выход которого соединен с информационным входом коммутатора байтов и с первым входом регистра записи, второй вход которого соединен с информационными выходами блоков сопряжения,

вход указателя байтов обмена соединен с третьим выходом блока регистров управляющего байта, выход подключен к третьему входу блока управления, второй выход которого соединен с управляющими входами коммутатора байтов, блока формирования

адресов, указателя байтов обмена, блока регистров управляющего байта, блока счетчиков ввода-вывода и регистра записи.

Это обеспечивает двусторонний обмен информацией между устройствами обработки и вычислительными мащинами, промежуточное хранение результатов обработки и обмен информацией между буферным запоминающим блоком и блоками сопряжения не только полными словами массива, но и необходимыми сообщениями, входящими

в эти слова, что сокращает время обмена расширяет функциональные возможности и повыщает эффективность работы устройств, участвующих в обмене информацией.

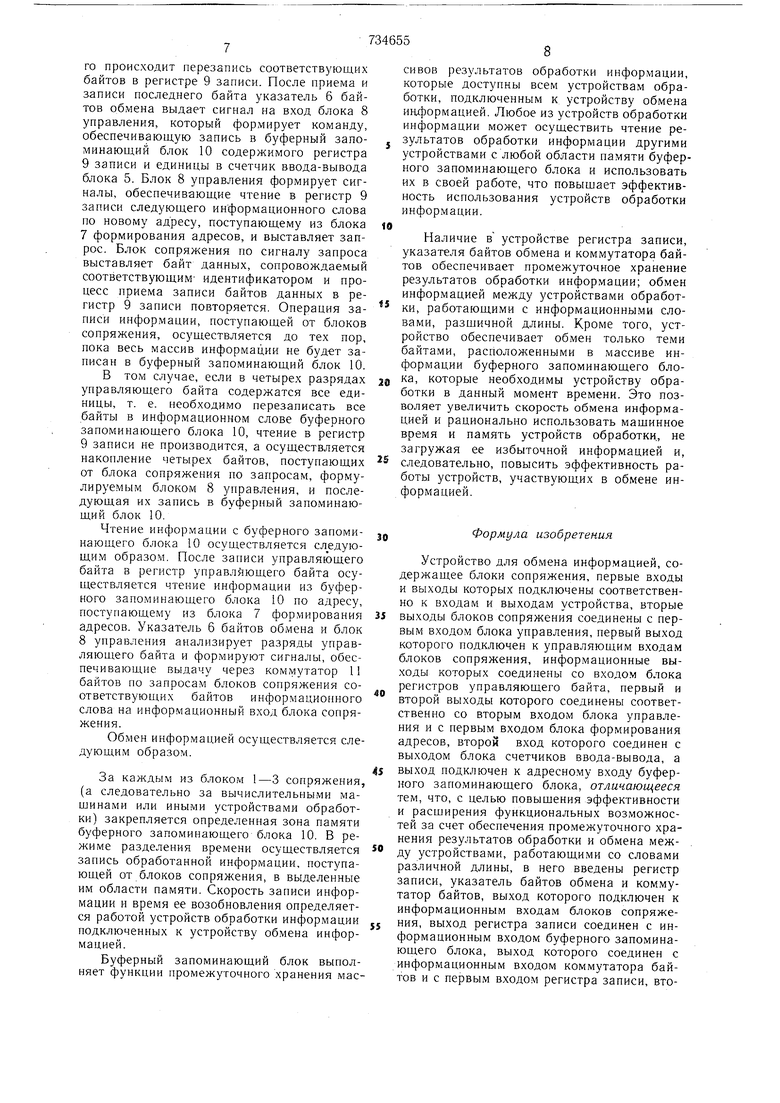

На чертеже изображена блок-схема устройства для обмена информацией.

Схема устройства содержит блоки 1-3 сопряжения, блок 4 регистров управляющего байта, блок 5 счетчиков ввода-вывода, указатель 6 байтов обмена, блок 7 формирования адресов, блок 8 управления, регистр 9

записи, буферный запоминающий блок 10, коммутатор 11 ба,йтов.

Код в трех разрядах управляющего байта указывает зону памяти буферного запоминающего блока, в которую производится запись или чтение информации при обмене; четыре разряда управляющего байта указывают, какие байты информационного, слова буферного запоминающего блока подлежат обмену; один разряд управляющего байта указывает направление обмена - запись

информации в буферное запоминающее устройство или чтение из него. Операции запись соответствует «1 в этом разряде операции чтение «О. Один разряд управляющего байта является контрольным - дополняет число единиц управляющего байта до

нечетного и обеспечивает осуществление контроля принятого управляющего байта по четности.

Блоки 1-3 сопряжения включают регистры приема-выдачи, элементы И-НЕ, согласователи уровня сигналов и представляют устройства, согласующие интерфейс буферного запоминающего блока с интерфейсами ввода-вывода вычислительных мащин.

Регистры управляющего байта блока 4, представляющие 9-ти разрядные регистры, каждый из которых закреплен за одним из блоков сопряжения, предназначены для записи и хранения управляющих байтов, поступающих от блоков сопряжения в момент начальной выборки. Управляющий байт содержит признаки программы обмена информацией между буферным запоминающим блоком и блоком сопряжения.

Счетчики ввода-вывода блока 5, каждый из которых закреплен за одним из блоков сопряжения, служат для формирования текущих адресов обмена информации.

Блок 7 формирования адресов, включающий элементы И-НЕ, ИЛИ-НЕ, обеспечивает формирование адресов обмена буферного запоминающего блока для каждого из блоков сопряжения при помощи соответствующего регистра управляющего байта и содержимого счетчика ввода-вывода.

Указатель 6 байтов обмена, включающий триггеры, логические элементы И-НЕ, представляет автомат, обеспечивающий выдачу в узел 9 управления обменом управляющих сигналов в соответствии с управляющим байтом, записанным в регистр 4 управляющего байта.

Блок 8 управления, содержащий триггеры, дещифраторы, регистры, логические элементы, предназначен для синхронизации работы всех узлов устройства обменом информацией.

Буферный запоминающий блок 10, содержащий запоминающее устройство, входной информационный регистр, регистр адреса, регистр числа, схему управления, служит для записи, хранения, чтения, регенерации и выдачи информации.

Устройство работает по принципу разделения времени. Обмен информацией осуществляется по инициативе устройств обработки информации, подключенных к буферному запоминающему блоку через блоки сопряжения. Метод обмена информацией между блоками сопряжения и буферным запоминающим блоком - асинхронный. Запросы на обслуживание от каждого из блоков сопряжения поступают в блок 8 управления, который вырабатывает сигнал, свидетельствующий о готовности к обмену и обеспечивающий логическое подключение соответствующего блока сопряжения устройству. Блок сопряжения формирует управляющий байт, который сопровождается соответствующим идентификатором.

Блок 8 управления формирует управляющие сигналы, обеспечивающие запись управляющего байта в регистр управляющего байта блока 4, соответствующего данному блоку сопряжения, сброс в «О соответствующего счетчика ввода-вывода блока и выдает сигнал, подтверждающий прием и запись управляющего байта. Записанный в

регистр управляющий байт содержит признаки программы обмена на все время обмена с данным блоком сопряжения и хранится в регистре блока 4 до конца обмена.

Запись информации, поступающей от блоков сопряжения в буферный запоминающий блок, осуществляется следующим образом.

С выхода блока 4 разряда управляющего байта поступают в указатель 6 байтов обмена и блок 8 управления, которые осуществляют анализ разрядов управляющего байта и формирование соответствующих сигналов, обеспечивающих запись информации в буферный запоминающий блок.

Три разряда управляющего байта указывают зону памяти буферного запоминающего блока 10, с которой осуществляется обмен информацией. Эти разряды поступают на вход блока 7 формирования адресов, где совместно с содержимым счетчика вводавывода блока 5 формируется управляющее слово (адрес) буферного запоминающего блока 10.

Указатель 6 байтов обмена осуществляет анализ кода четырех разрядов управляющего байта, которые указывают, какие байты четырехбайтного слова буферного запоминающего блока 10 подлежат замене.

Например, код 1001 в разрядах управляющего байта указывает, что в слове буферного запоминающего блока необходимо изменить (перезаписать) первый и четвертый байт, а второй и третий байты оставить без изменений.

При наличии «О в любом из этих разрядов управляющего байта блок 8 управления формирует сигналы, обеспечивающие чтение информационного слова с буферного запоминающего блока 10 в регистр 9 записи по адресу, поступающему с блока 7 формирования адресов и формирует сигнал запроса. По сигналу запроса блок сопряжения выставляет на информационном выходе байт данных, сопровождаемый соответствующим идентификатором на втором выходе. По сигналу-идентификатору блок 8 управления формирует сигналы,, обеспечивающие прием и запись байта данных в регистр 9 записи. После записи принятого байта блок управления снимает запрос, что свидетельствует о приеме и записи байта в регистр 9 записи. По спаду запроса блок сопряжения снимает идентификатор, по спаду которого блок 8 управления формирует сигналы, подготавливающие прием следующего байта, и затем выставляет новый запрос. По сигналу запроса блок сопряжения выставляет следующий байт данных, сопровождаемый идентификатором. Прием и запись последующих байтов данных в регистр 9 записи осуществляется аналогично, при этом блок управления формирует столько, запросов, сколько единиц содержится в четырех разрядах управляющего байта. В результате этого происходит перезапись соответствующих байтов в регистре 9 записи. После приема и записи последнего байта указатель 6 байтов об.мена выдает сигнал на вход блока 8 управления, который формирует команду, обеспечиваюш,ую запись в буферный запоминающий блок 10 содержимого регистра 9 записи и единицы в счетчик ввода-вывода блока 5. Блок 8 управления формирует сигналы, обеспечивающие чтение в регистр 9 записи следующего информационного слова по новому адресу, поступающему из блока 7 формирования адресов, и выставляет запрос. Блок сопряжения по сигналу запроса выставляет байт данных, сопровождае.мый соответствующим- идентификатором и процесс приема записи байтов данных в регистр 9 записи повторяется. Операция записи информации, поступающей от блоков сопряжения, осуществляется до тех пор, пока весь массив информации не буд-ет записан в буферный запоминающий блок 10.

В том случае, если в четырех разрядах управляющего байта содержатся все единицы, т. е. необходимо перезаписать все байты в информационном слове буферного запоминающего блока 10, чтение в регистр 9 записи не производится, а осуществляется накопление четырех байтов, поступающих от блока сопряжения по запросам, формулируемым блоком 8 управления, и последующая их запись в буферный запоминающий блок 10,

Чтение информации с буферного запоминающего блока 10 осуществляется следующим образом. После записи управляющего байта в регистр управлйющего байта осуществляется чтение информации из буферного запоминающего блока 10 по адресу, поступающему из блока 7 формирования адресов. Указатель 6 байтов обмена и блок 8 управления анализирует разряды управляющего байта и формируют сигналы, обеспечивающие выдачу через коммутатор 11 байтов по запросам блоков сопряжения соответствующих байтов информациопного слова на информационный вход блока сопряжения.

Обмен информацией осуществляется следующим образом.

За каждым из блоком 1-3 сопряжения, (а следовательно за вычислительными мащинами или иными устройствами обработки) закрепляется определенная зона памяти буферного запоминающего блока 10. В режиме разделения времени осуществляется запись обработанной информации, поступающей от блоков сопряжения, в выделенные им области памяти. Скорость записи информации и время ее возобновления определяется работой устройств обработки информации подключенных к устройству обмена информацией.

Буферный запоминающий блок выполняет функции промежуточного хранения массивов результатов обработки информации, которые доступны всем устройствам обработки, подключенным к устройству обмена информацией. Любое из устройств обработки информации может осуществить чтение результатов обработки информации другими устройствами с любой области памяти буферного запоминающего блока и использовать их в своей работе, что повыщает эффективность использования устройств обработки информации.

Наличие в устройстве регистра записи, указателя байтов обмена и коммутатора байтов обеспечивает промежуточное хранение результатов обработки информации; обмен информацией между устройствами обработки, работающими с информационными словами, разщичной длины. Кроме того, устройство обеспечивает обмен только теми байтами, расположенными в массиве информации буферного запоминающего блока, которые необходимы устройству обработки в данный момент времени. Это позволяет увеличить скорость обмена информацией и рационально использовать машинное время и память устройств обработки., не загружая ее избыточной информацией и, следовательно, повысить эффективность работы устройств, участвующих в обмене информацией.

Формула изобретения

Устройство для обмена информацией, содержащее блоки сопряжения, первые входы и выходы которых подключены соответственно к входам и выходам устройства, вторые выходы блоков сопряжения соединены с первым входом блока управления, первый выход которого подключен к управляющим входам блоков сопряжения, информационные выходы которых соединены со входом блока регистров управляющего байта, первый и второй выходы которого соединены соответственно со вторым входом блока управления и с первым входом блока формирования адресов, второй вход которого соединен с выходом б.лока счетчиков ввода-вывода, а выход подключен к адресному входу буферного запоминающего блока, отличающееся тем, что, с целью повыщения эффективности и расщирения функциональных возможностей за счет обеспечения промежуточного хранения результатов обработки и обмена между устройствами, работающими со словами различной длины, в него введены регистр записи, указатель байтов обмена и коммутатор байтов, выход которого подключен к информационным входам блоков сопряжения, выход регистра записи соединен с информационным входом буферного запоминающего блока, выход которого соединен с информационным входом коммутатора байтов и с первым входом регистра записи, второй вход которого соединен с информационными выходами блоков сопряжения, вход указателя байтов обмена соединен с третьим выходом блока регистров управляющего байта, выход подключен к третьему входу блока управления, второй выход которого соединен с управляющими входами коммутатора байтов, блока формирования адресов, указателя байтов обмена, блока регистров управляющего байта, блока счетчиков пода-вывода и регистра записи.

Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР

№ 455345, кл. G Об F 13/00, 1972. 2. Авторское свидетельство СССР

№ 496551, кл. G 06 F3/04, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройтво для обмена данными | 1977 |

|

SU691830A1 |

| Устройство для обмена информацией | 1979 |

|

SU857966A1 |

| Устройство для обмена информацией | 1985 |

|

SU1339572A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения оконечного устройства с мультиплексным каналом передачи информации | 1987 |

|

SU1538172A1 |

| Устройство для обмена информацией | 1985 |

|

SU1310828A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

Авторы

Даты

1980-05-15—Публикация

1977-12-20—Подача