Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны сумматоры по модулю три (см., например, авт.св. СССР 1381488, кл. G06F 7/49, 1988 г.), которые реализуют операцию (A+B)mod 3, где А, В ∈ {00,01,10} есть двухразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных сумматоров по модулю три, относятся ограниченные функциональные возможности и схемная сложность, обусловленные соответственно тем, что не допускается обработка не приведенных значений операндов и, в частности, упомянутый аналог содержит логические элементы четырех типов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип сумматор по модулю три (авт. св. СССР 1432503, кл. G06F 7/49, 1988 г.), который содержит логические элементы и реализует операцию (А+В) mod 3,

где А,В∈{00,01,10,11} есть двухразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится схемная сложность, обусловленная тем, что цена по Квайну схемы прототипа равна 30 и он содержит логические элементы четырех типов.

Техническим результатом изобретения является упрощение схемы сумматора по модулю три за счет уменьшения ее цены по Квайну и сокращения количества типов логических элементов аппаратурного состава при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в сумматоре по модулю три, содержащем два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и шесть элементов И, особенность заключается в том, что в него дополнительно введены пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый, второй входы пятого и первый, второй входы j-го  элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами третьего, второго и первым, вторым входами j-го элементов И, первый и второй входы третьего, первый, второй входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом первого элемента И и выходами второго, первого, шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий входы шестого и первый, второй, третий входы седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходами пятого, шестого элементов И и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходами четвертого, шестого элементов И, а первый, второй входы k-го

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами третьего, второго и первым, вторым входами j-го элементов И, первый и второй входы третьего, первый, второй входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом первого элемента И и выходами второго, первого, шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий входы шестого и первый, второй, третий входы седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходами пятого, шестого элементов И и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходами четвертого, шестого элементов И, а первый, второй входы k-го  и первый, второй входы (k-4)-го элементов И соединены соответственно с выходами (2×k-7)-го, (2×k-9)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и (k-4)-ым, (k-2)-ым входами сумматора по модулю три, первый и второй выходы которого соединены соответственно с выходами четвертого и седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

и первый, второй входы (k-4)-го элементов И соединены соответственно с выходами (2×k-7)-го, (2×k-9)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и (k-4)-ым, (k-2)-ым входами сумматора по модулю три, первый и второй выходы которого соединены соответственно с выходами четвертого и седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

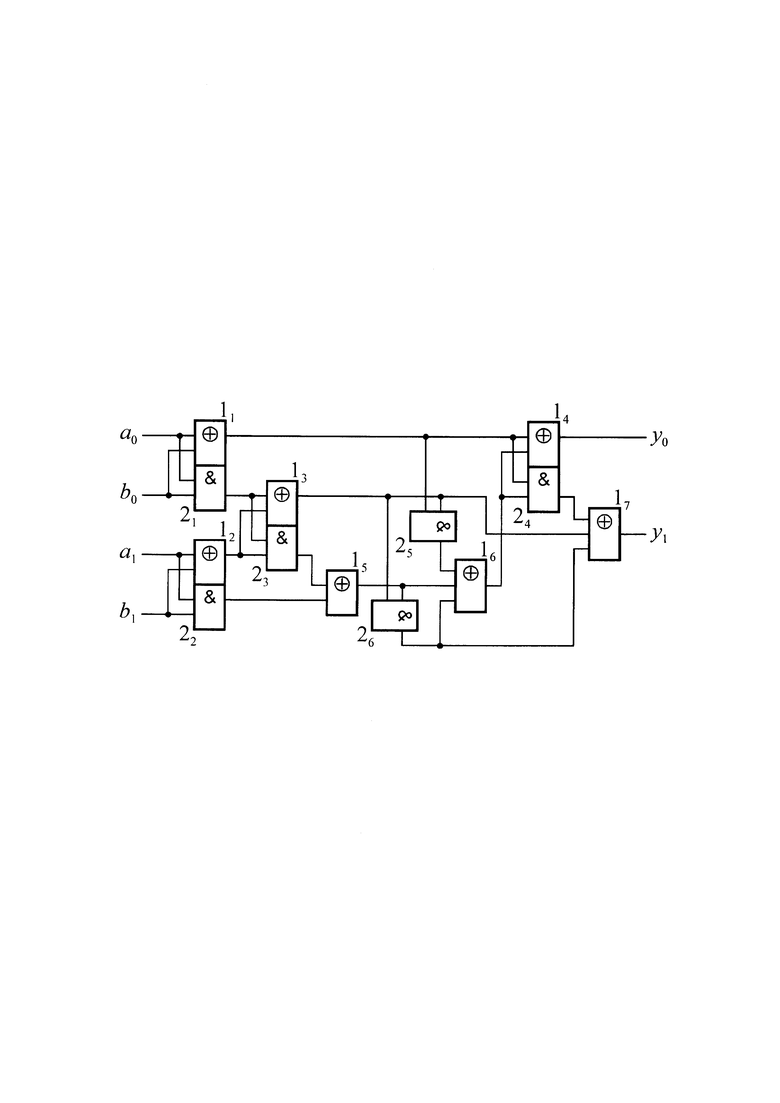

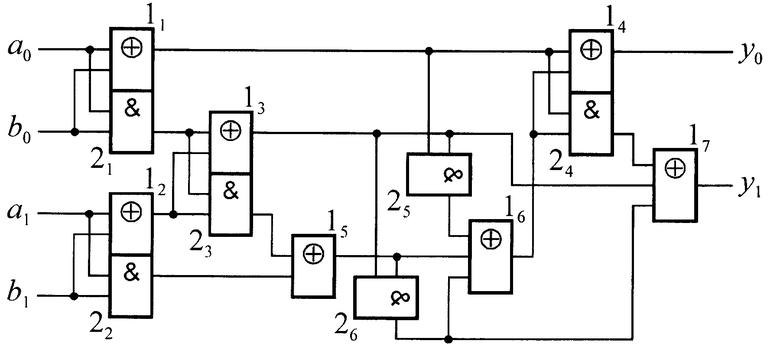

На чертеже представлена схема предлагаемого сумматора по модулю три.

Сумматор по модулю три содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11, …, 17 и элементы И 21, …, 26, причем первый, второй входы элемента 15 и первый, второй входы элемента  соединены соответственно с выходами элементов 23, 22 и первым, вторым входами элемента 2j, первый, второй входы элемента 13 и первый, второй входы элемента 14 соединены соответственно с выходами элементов 21, 12 и 11, 16, первый, второй, третий входы элемента 16 и первый, второй, третий входы элемента 17 соединены соответственно с выходами элементов 15, 25, 26 и 13, 24, 26, а первый, второй входы элемента

соединены соответственно с выходами элементов 23, 22 и первым, вторым входами элемента 2j, первый, второй входы элемента 13 и первый, второй входы элемента 14 соединены соответственно с выходами элементов 21, 12 и 11, 16, первый, второй, третий входы элемента 16 и первый, второй, третий входы элемента 17 соединены соответственно с выходами элементов 15, 25, 26 и 13, 24, 26, а первый, второй входы элемента  и первый, второй входы элемента 2k-4 соединены соответственно с выходами элементов 12×k-7, 12×k-9 и (k-4)-ым, (k-2)-ым входами сумматора по модулю три, первый и второй выходы которого соединены соответственно с выходами элементов 14 и 17.

и первый, второй входы элемента 2k-4 соединены соответственно с выходами элементов 12×k-7, 12×k-9 и (k-4)-ым, (k-2)-ым входами сумматора по модулю три, первый и второй выходы которого соединены соответственно с выходами элементов 14 и 17.

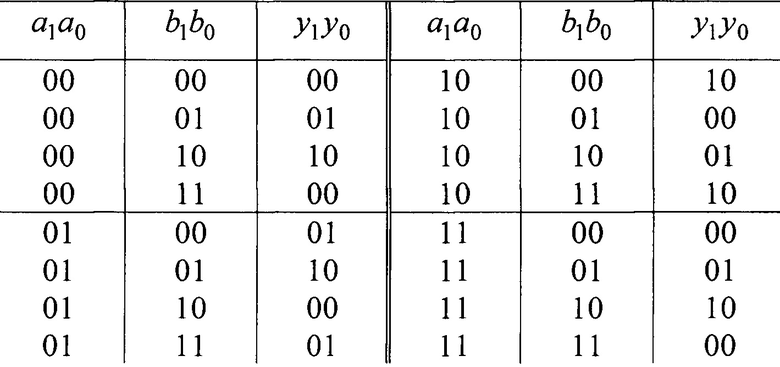

Работа предлагаемого сумматора по модулю три осуществляется следующим образом. На его первый, второй и третий, четвертый входы подаются соответственно двоичные сигналы а0, а1∈{0,1} и b0, b1∈{0,1}, которые задают подлежащие обработке двухразрядные двоичные числа А=а1а0, B=b1b0, причем а1, b1 и а0, b0 определяют значения старших и младших разрядов соответственно, А,В∈{00,01,10,11}. В представленной ниже таблице приведены значения выходных сигналов y0, у1 предлагаемого сумматора, полученные с учетом работы элементов 11, …, 17, 21, …, 26 для всех возможных наборов значений сигналов a0, a1, b0, b1.

Согласно представленной таблицы имеем Y=(А+В)mod 3, где Y=y1y0 - двухразрядное двоичное число, задаваемое двоичными сигналами y0,y1∈{0,1} (y1 и y0 определяют значения старшего и младшего разрядов соответственно).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый сумматор по модулю три реализует операцию (А+В) mod 3, где А,В∈{00,01,10,11} есть двухразрядные двоичные числа, задаваемые двоичными сигналами. При этом схема предлагаемого сумматора проще чем у прототипа, поскольку ее цена по Квайну равна 28 и аппаратурный состав образован из логических элементов двух типов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР-УМНОЖИТЕЛЬ ПО МОДУЛЮ ТРИ | 2020 |

|

RU2762548C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2019 |

|

RU2708793C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ q | 2019 |

|

RU2713862C1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 2018 |

|

RU2702969C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ ТРИ | 2021 |

|

RU2770801C1 |

| СУММАТОР ПО МОДУЛЮ q | 2018 |

|

RU2702970C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2021 |

|

RU2778675C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ | 2021 |

|

RU2778676C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ | 2020 |

|

RU2757831C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ СЕМЬ | 2021 |

|

RU2764707C1 |

Изобретение относится к области цифровой вычислительной техники. Технический результат заключается в упрощении схемы сумматора по модулю три за счет уменьшения ее цены по Квайну и сокращении количества типов логических элементов аппаратурного состава при сохранении функциональных возможностей прототипа. Технический результат достигается за счет сумматора по модулю три, который содержит семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (11, …, 17) и шесть элементов И (21, …, 26). 1 ил.

Сумматор по модулю три, содержащий два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и шесть элементов И, отличающийся тем, что в него дополнительно введены пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый, второй входы пятого и первый, второй входы j-го  элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами третьего, второго и первым, вторым входами j-го элементов И, первый и второй входы третьего, первый, второй входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом первого элемента И и выходами второго, первого, шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий входы шестого и первый, второй, третий входы седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходами пятого, шестого элементов И и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходами четвертого, шестого элементов И, а первый, второй входы k-го

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами третьего, второго и первым, вторым входами j-го элементов И, первый и второй входы третьего, первый, второй входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом первого элемента И и выходами второго, первого, шестого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий входы шестого и первый, второй, третий входы седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходами пятого, шестого элементов И и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходами четвертого, шестого элементов И, а первый, второй входы k-го  и первый, второй входы (k-4)-го элементов И соединены соответственно с выходами (2×k-7)-го, (2×k-9)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и (k-4)-м, (k-2)-м входами сумматора по модулю три, первый и второй выходы которого соединены соответственно с выходами четвертого и седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

и первый, второй входы (k-4)-го элементов И соединены соответственно с выходами (2×k-7)-го, (2×k-9)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и (k-4)-м, (k-2)-м входами сумматора по модулю три, первый и второй выходы которого соединены соответственно с выходами четвертого и седьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

| Сумматор по модулю три | 1986 |

|

SU1432503A2 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ | 2012 |

|

RU2500017C1 |

| Арифметико-логическое устройство для сложения чисел по модулю | 2016 |

|

RU2628180C1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

Авторы

Даты

2019-10-21—Публикация

2019-03-11—Подача