Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны сумматоры-умножители по модулю три (см., например, авт. св. СССР 1441395, кл. G06F 7/72, 1988 г.), которые реализуют операцию (A+B) mod 3 либо операцию (А×B) mod 3, где А, В ∈ {00,01,10} есть двухразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных сумматоров-умножителей по модулю три, относится схемная сложность, обусловленная тем, что цена по Квайну схемы, в частности, упомянутого аналога равна 57 и он имеет два настроечных входа.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип сумматор-умножитель по модулю три (авт. св. СССР 1667054, кл. G06F 7/72, 1991 г.), который содержит логические элементы и реализует операцию (A+B) mod 3 либо операцию (А×B) mod 3, где А, В ∈ {00,01,10} есть двухразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится схемная сложность, обусловленная тем, что цена по Квайну схемы прототипа равна 34 и он имеет два настроечных входа.

Техническим результатом изобретения является упрощение схемы сумматора-умножителя по модулю три за счет уменьшения ее цены по Квайну и сокращения количества настроечных входов при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в сумматоре-умножителе по модулю три, содержащем три элемента И, шесть элементов ИЛИ и четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй входы третьего элемента И соединены соответственно с выходами третьего, четвертого элементов ИЛИ, особенность заключается в том, что в него введен седьмой элемент ИЛИ, j-й ( ) вход третьего и первый вход четвертого элементов ИЛИ соединены соответственно с третьим входом j-го элемента ИЛИ, вторым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом первого элемента ИЛИ, второй вход четвертого и первый, второй входы (j+5)-го элементов ИЛИ соединены соответственно с первым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторым входом второго элемента ИЛИ и выходом j-го элемента И, выходом (j+2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй, третий входы j-го элемента И и первый, второй входы (j+2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом третьего элемента И и выходами j-го, пятого элементов ИЛИ, а второй вход пятого, первый, второй входы (j+2)-го и выход (j+5)-го элементов ИЛИ соединены соответственно с выходом третьего элемента И, (2×j-1)-ым, (2×j)-ым входами и j-ым выходом сумматора-умножителя по модулю три, настроечный вход которого соединен с первым входом пятого элемента ИЛИ и первыми входами j-ых элементов ИЛИ, И.

) вход третьего и первый вход четвертого элементов ИЛИ соединены соответственно с третьим входом j-го элемента ИЛИ, вторым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом первого элемента ИЛИ, второй вход четвертого и первый, второй входы (j+5)-го элементов ИЛИ соединены соответственно с первым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторым входом второго элемента ИЛИ и выходом j-го элемента И, выходом (j+2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй, третий входы j-го элемента И и первый, второй входы (j+2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом третьего элемента И и выходами j-го, пятого элементов ИЛИ, а второй вход пятого, первый, второй входы (j+2)-го и выход (j+5)-го элементов ИЛИ соединены соответственно с выходом третьего элемента И, (2×j-1)-ым, (2×j)-ым входами и j-ым выходом сумматора-умножителя по модулю три, настроечный вход которого соединен с первым входом пятого элемента ИЛИ и первыми входами j-ых элементов ИЛИ, И.

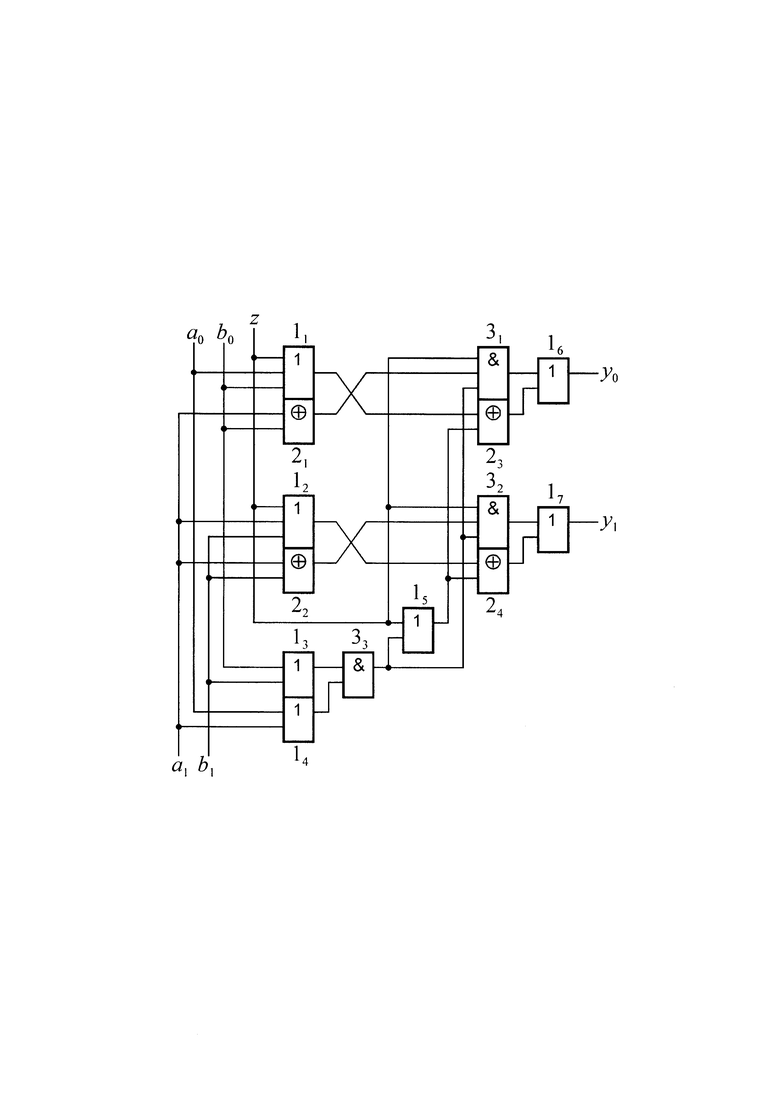

На чертеже представлена схема предлагаемого сумматора-умножителя по модулю три.

Сумматор-умножитель по модулю три содержит элементы ИЛИ 11, …, 17, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 21, …, 24 и элементы И 31, 32, 33, причем j-й ( ) вход элемента 13 и первый вход элемента 14 соединены соответственно с третьим входом элемента 1j, вторым входом элемента 2j и вторым входом элемента 11 второй вход элемента 14 и первый, второй входы элемента 1j+5 соединены соответственно с первым входом элемента 2j, вторым входом элемента 12 и выходами элементов 3j, 2j+2, второй, третий входы элемента 3j, первый, второй входы элемента 33 и первый, второй входы элемента 2j+2 соединены соответственно с выходами элементов 2j, 33, 13, 14 и 1j, 15, а второй вход элемента 15, первый, второй входы элемента 1j+2 и выход элемента 1j+5 соединены соответственно с выходом элемента 33, (2×j-1)-ым, (2×j)-ым входами и j-ым выходом сумматора-умножителя по модулю три, настроечный вход которого соединен с первыми входами элементов 1j, 15, 3j.

) вход элемента 13 и первый вход элемента 14 соединены соответственно с третьим входом элемента 1j, вторым входом элемента 2j и вторым входом элемента 11 второй вход элемента 14 и первый, второй входы элемента 1j+5 соединены соответственно с первым входом элемента 2j, вторым входом элемента 12 и выходами элементов 3j, 2j+2, второй, третий входы элемента 3j, первый, второй входы элемента 33 и первый, второй входы элемента 2j+2 соединены соответственно с выходами элементов 2j, 33, 13, 14 и 1j, 15, а второй вход элемента 15, первый, второй входы элемента 1j+2 и выход элемента 1j+5 соединены соответственно с выходом элемента 33, (2×j-1)-ым, (2×j)-ым входами и j-ым выходом сумматора-умножителя по модулю три, настроечный вход которого соединен с первыми входами элементов 1j, 15, 3j.

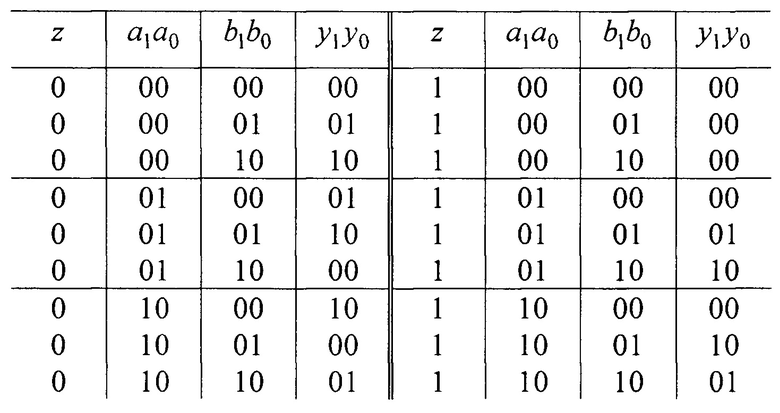

Работа предлагаемого сумматора-умножителя по модулю три осуществляется следующим образом. На его настроечном входе фиксируется сигнал z ∈ {0,1}, который определяет вид реализуемой операции. На его третий, четвертый и первый, второй входы подаются соответственно двоичные сигналы а0,a1 ∈{0,1} и b0,b1 ∈ {0,1}, которые задают подлежащие обработке двухразрядные двоичные числа A=a1a0, B=b1b0, причем а1,b1 и a0,b0 определяют значения старших и младших разрядов соответственно, А, В ∈ {00,01,10}. В представленной ниже таблице приведены значения выходных сигналов y0,y1 предлагаемого сумматора-умножителя, полученные с учетом работы элементов 11, …, 17, 21, …, 24, 31, 32, 33 для всех возможных наборов значений сигналов z, а0, a1, b0, b1.

Если z = 0 либо z=1, то согласно представленной таблицы имеем Y=(А+В) mod 3 либо Y=(А×В) mod 3, где Y=у1у0 - двухразрядное двоичное число, задаваемое двоичными сигналами y0, y1 ∈ {0,1} {у1 и у0 определяют значения старшего и младшего разрядов соответственно).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый сумматор-умножитель по модулю три реализует операцию (А+B) mod 3 либо операцию (A×B) mod 3, где А, В ∈ {00,01,10} есть двухразрядные двоичные числа, задаваемые двоичными сигналами. При этом схема предлагаемого сумматора-умножителя проще, чем у прототипа, поскольку ее цена по Квайну равна 32 и предлагаемый сумматор-умножитель имеет один настроечный вход.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР ПО МОДУЛЮ ТРИ | 2019 |

|

RU2708793C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2019 |

|

RU2703676C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ | 2020 |

|

RU2757831C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2021 |

|

RU2778675C1 |

| СУММАТОР ПО МОДУЛЮ q | 2018 |

|

RU2702970C1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 2018 |

|

RU2702969C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ ТРИ | 2021 |

|

RU2770801C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ q | 2019 |

|

RU2713862C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ ПЯТЬ | 2021 |

|

RU2762544C1 |

| ВЫЧИТАТЕЛЬ ПО МОДУЛЮ q | 2021 |

|

RU2770798C1 |

Изобретение относится к сумматору-умножителю по модулю три. Технический результат заключается в упрощении конструкции устройства. Устройство содержит три элемента И, шесть элементов ИЛИ и четыре элемента исключающее ИЛИ, причем первый, второй входы третьего элемента И соединены соответственно с выходами третьего, четвертого элементов ИЛИ, отличающееся тем, что в него введен седьмой элемент ИЛИ, j-й ( ) вход третьего и первый вход четвертого элементов ИЛИ соединены соответственно с третьим входом j-го элемента ИЛИ, вторым входом j-го элемента исключающее ИЛИ и вторым входом первого элемента ИЛИ, второй вход четвертого и первый, второй входы (j+5)-го элементов ИЛИ соединены соответственно с первым входом j-го элемента исключающее ИЛИ, вторым входом второго элемента ИЛИ и выходом j-го элемента И, выходом (j+2)-го элемента исключающее ИЛИ, второй, третий входы j-го элемента И и первый, второй входы (j+2)-го элемента исключающее ИЛИ соединены соответственно с выходом j-го элемента исключающее ИЛИ, выходом третьего элемента И и выходами j-го, пятого элементов ИЛИ, а второй вход пятого, первый, второй входы (j+2)-го и выход (j+5)-го элементов ИЛИ соединены соответственно с выходом третьего элемента И, (2×j-1)-м, (2×j)-м входами и j-м выходом сумматора-умножителя по модулю три, настроечный вход которого соединен с первым входом пятого элемента ИЛИ и первыми входами j-х элементов ИЛИ, И. 1 ил., 1 табл.

) вход третьего и первый вход четвертого элементов ИЛИ соединены соответственно с третьим входом j-го элемента ИЛИ, вторым входом j-го элемента исключающее ИЛИ и вторым входом первого элемента ИЛИ, второй вход четвертого и первый, второй входы (j+5)-го элементов ИЛИ соединены соответственно с первым входом j-го элемента исключающее ИЛИ, вторым входом второго элемента ИЛИ и выходом j-го элемента И, выходом (j+2)-го элемента исключающее ИЛИ, второй, третий входы j-го элемента И и первый, второй входы (j+2)-го элемента исключающее ИЛИ соединены соответственно с выходом j-го элемента исключающее ИЛИ, выходом третьего элемента И и выходами j-го, пятого элементов ИЛИ, а второй вход пятого, первый, второй входы (j+2)-го и выход (j+5)-го элементов ИЛИ соединены соответственно с выходом третьего элемента И, (2×j-1)-м, (2×j)-м входами и j-м выходом сумматора-умножителя по модулю три, настроечный вход которого соединен с первым входом пятого элемента ИЛИ и первыми входами j-х элементов ИЛИ, И. 1 ил., 1 табл.

Сумматор-умножитель по модулю три, содержащий три элемента И, шесть элементов ИЛИ и четыре элемента исключающее ИЛИ, причем первый, второй входы третьего элемента И соединены соответственно с выходами третьего, четвертого элементов ИЛИ, отличающийся тем, что в него введен седьмой элемент ИЛИ, j-й ( ) вход третьего и первый вход четвертого элементов ИЛИ соединены соответственно с третьим входом j-го элемента ИЛИ, вторым входом j-го элемента исключающее ИЛИ и вторым входом первого элемента ИЛИ, второй вход четвертого и первый, второй входы (j+5)-го элементов ИЛИ соединены соответственно с первым входом j-го элемента исключающее ИЛИ, вторым входом второго элемента ИЛИ и выходом j-го элемента И, выходом (j+2)-го элемента исключающее ИЛИ, второй, третий входы j-го элемента И и первый, второй входы (j+2)-го элемента исключающее ИЛИ соединены соответственно с выходом j-го элемента исключающее ИЛИ, выходом третьего элемента И и выходами j-го, пятого элементов ИЛИ, а второй вход пятого, первый, второй входы (j+2)-го и выход (j+5)-го элементов ИЛИ соединены соответственно с выходом третьего элемента И, (2×j-1)-м, (2×j)-м входами и j-м выходом сумматора-умножителя по модулю три, настроечный вход которого соединен с первым входом пятого элемента ИЛИ и первыми входами j-х элементов ИЛИ, И.

) вход третьего и первый вход четвертого элементов ИЛИ соединены соответственно с третьим входом j-го элемента ИЛИ, вторым входом j-го элемента исключающее ИЛИ и вторым входом первого элемента ИЛИ, второй вход четвертого и первый, второй входы (j+5)-го элементов ИЛИ соединены соответственно с первым входом j-го элемента исключающее ИЛИ, вторым входом второго элемента ИЛИ и выходом j-го элемента И, выходом (j+2)-го элемента исключающее ИЛИ, второй, третий входы j-го элемента И и первый, второй входы (j+2)-го элемента исключающее ИЛИ соединены соответственно с выходом j-го элемента исключающее ИЛИ, выходом третьего элемента И и выходами j-го, пятого элементов ИЛИ, а второй вход пятого, первый, второй входы (j+2)-го и выход (j+5)-го элементов ИЛИ соединены соответственно с выходом третьего элемента И, (2×j-1)-м, (2×j)-м входами и j-м выходом сумматора-умножителя по модулю три, настроечный вход которого соединен с первым входом пятого элемента ИЛИ и первыми входами j-х элементов ИЛИ, И.

| Сумматор-умножитель по модулю три | 1989 |

|

SU1667054A1 |

| Сумматор-умножитель по модулю три | 1987 |

|

SU1441395A1 |

| Прибор для производства записей в сводной ведомости по отдельным расчетным листам | 1929 |

|

SU17277A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЭНЕРГИИ НА РАССТОЯНИЕ ПРИ ПОМОЩИ СЖАТОГО ВОЗДУХА И ПНЕВМАТИЧЕСКИХ ВОДОПОДЪЕМНЫХ АППАРАТОВ | 1928 |

|

SU17137A1 |

| Способ приготовления цемента из доменного шлака | 1929 |

|

SU18246A1 |

| Железобетонная шпала | 1929 |

|

SU19245A1 |

| Станок для окорки бревен и разделения их на части определённой длины | 1929 |

|

SU20313A1 |

| Сумматор-умножитель по модулю три | 1989 |

|

SU1667054A1 |

Авторы

Даты

2021-12-21—Публикация

2020-09-25—Подача