Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны умножители по модулю q (см., например, правый рис. во второй сверху строке хвостовой части таблицы на рис. 3.20 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988 г.), которые реализуют операцию (А×В)mod 2, где A, B∈{0,1} есть одноразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных умножителей по модулю q, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется операция (А×В)mod 3, где А, В∈{00,01,10,11} есть двухразрядные двоичные числа, задаваемые двоичными сигналами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип умножитель по модулю q (рис. в первой сверху строке хвостовой части таблицы на рис. 3.35 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988 г.), который содержит элемент И и реализует операцию (А×В)mod 2, где А, В∈{0,1} есть одноразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется операция (А×B)mod 3, где А, В∈{00,01,10,11} есть двухразрядные двоичные числа, задаваемые двоичными сигналами.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации операции (А×В)mod q при q=2 либо при q=3, где А, В (0≤A<2×q-2, 0≤В<2×q-2) есть (log2(2×q-2)) - разрядные двоичные числа, задаваемые двоичными сигналами.

Указанный технический результат при осуществлении изобретения достигается тем, что в умножителе по модулю q, содержащем элемент И, особенность заключается в том, что в него дополнительно введены два элемента И и четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход третьего и первый, второй входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с вторыми и первыми входами второго, первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй входы j-го  и первый, второй входы третьего элементов И соединены соответственно с выходом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом третьего элемента И и выходами третьего, четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы (j+2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход j-го элемента И соединены соответственно с (2×j-1)-м, (2×j)-м входами и j-м выходом умножителя по модулю q.

и первый, второй входы третьего элементов И соединены соответственно с выходом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом третьего элемента И и выходами третьего, четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы (j+2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход j-го элемента И соединены соответственно с (2×j-1)-м, (2×j)-м входами и j-м выходом умножителя по модулю q.

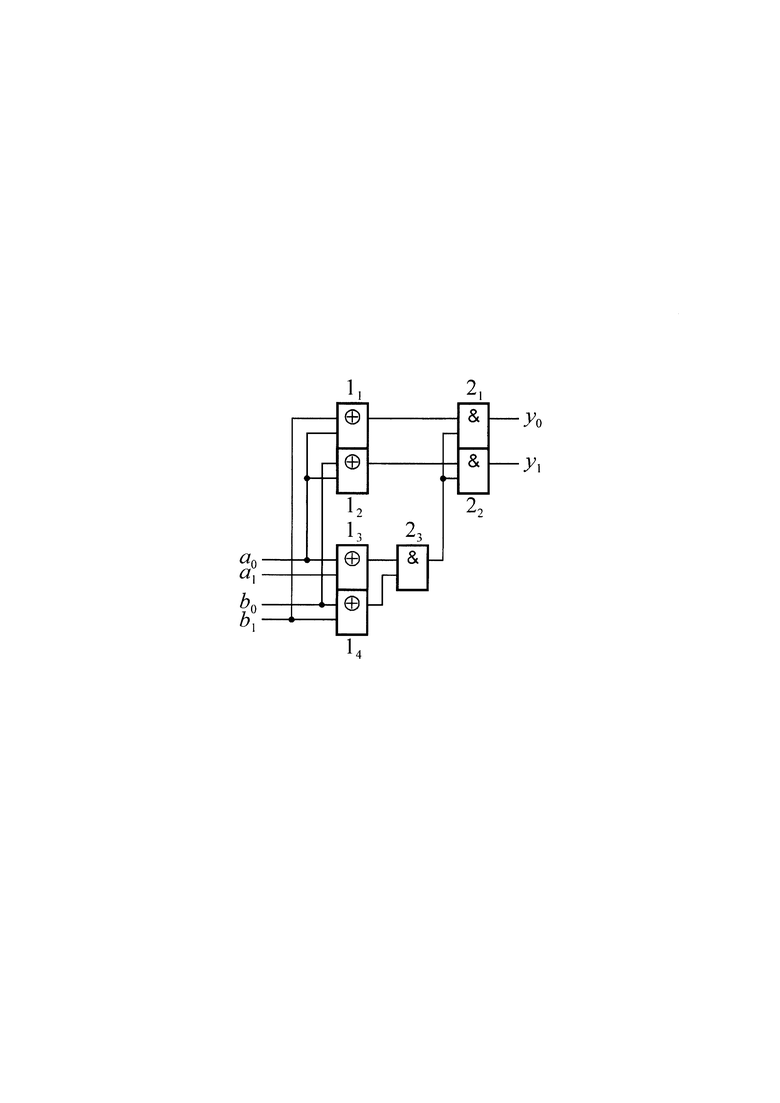

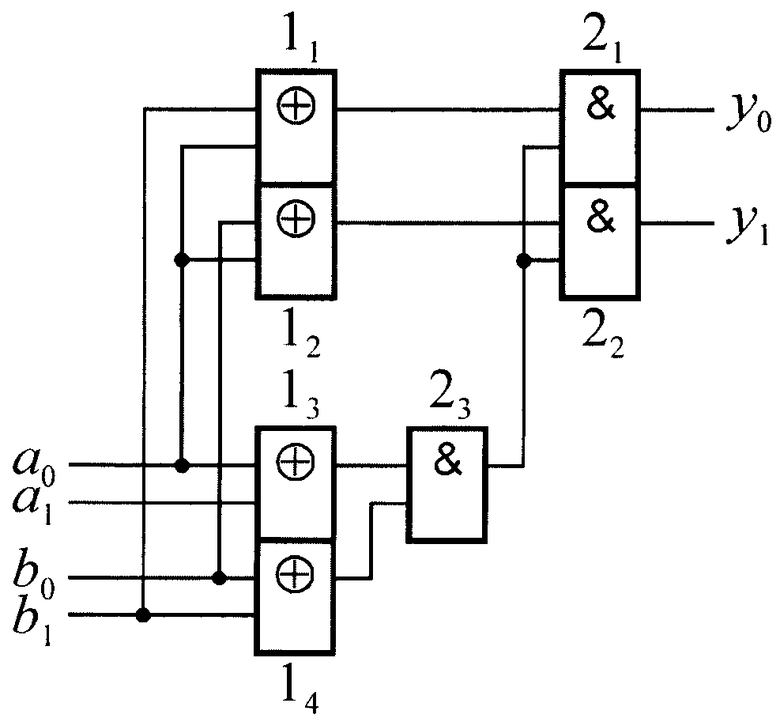

На чертеже представлена схема предлагаемого умножителя по модулю q.

Умножитель по модулю q содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11, 12, 13, 14 и элементы И 21, 22, 23, причем первый вход элемента 13 и первый, второй входы элемента 14 соединены соответственно с вторыми и первыми входами элементов 12, 11, первый, второй входы элемента 2j  и первый, второй входы элемента 23 соединены соответственно с выходами элементов 1j, 23 и 13, 14, а первый, второй входы элемента 1j+2 и выход элемента 2j соединены соответственно с (2×j-1)-м, (2×j)-м входами и j-м выходом умножителя по модулю q.

и первый, второй входы элемента 23 соединены соответственно с выходами элементов 1j, 23 и 13, 14, а первый, второй входы элемента 1j+2 и выход элемента 2j соединены соответственно с (2×j-1)-м, (2×j)-м входами и j-м выходом умножителя по модулю q.

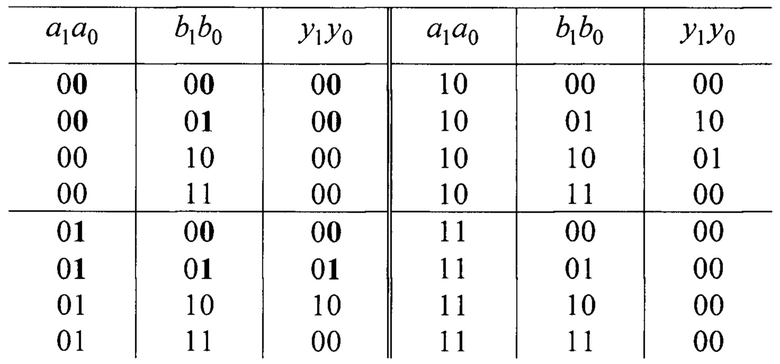

Работа предлагаемого умножителя по модулю q осуществляется следующим образом. На его первый, второй и третий, четвертый входы подаются соответственно двоичные сигналы a0,a1∈{0,1} и b0,b1∈{0,1}, которые задают подлежащие обработке двухразрядные двоичные числа А=a1a0, B=b1b0, причем a1,b1 и a0,b0 определяют значения старших и младших разрядов соответственно, А, В∈{00,01,10,11}. В представленной ниже таблице приведены значения выходных сигналов y0,y1 предлагаемого умножителя, полученные с учетом работы элементов 11, 12, 13, 14, 21, 22, 23 для всех возможных наборов значений сигналов а0,а1,b0,b1.

Согласно представленной таблице имеем Y=(А×В)mod 3, где Y=y1y0 - двухразрядное двоичное число, задаваемое двоичными сигналами y0, y1∈{0,1} (y1 и y0 определяют значения старшего и младшего разрядов соответственно). Если a1=b1=0, то согласно представленной таблицы (см. значения сигналов a0, b0, y0, выделенные жирным шрифтом) получим Y=(А×В)mod 2, где А=а0, B=b0, Y=y0 - одноразрядные двоичные числа, задаваемые указанными сигналами.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый умножитель по модулю q обладает более широкими по сравнению с прототипом функциональными возможностями, так как реализует операцию (A×B)mod q при q=2 либо при q=3, где А, В (0≤A<2×q-2, 0≤В<2×q-2) есть (log2(2×q-2)) - разрядные двоичные числа, задаваемые двоичными сигналами.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИТАТЕЛЬ ПО МОДУЛЮ q | 2021 |

|

RU2770798C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ ТРИ | 2021 |

|

RU2770801C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2019 |

|

RU2703676C1 |

| СУММАТОР-УМНОЖИТЕЛЬ ПО МОДУЛЮ ТРИ | 2020 |

|

RU2762548C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ | 2020 |

|

RU2757831C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ ТРИ | 2021 |

|

RU2778676C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2019 |

|

RU2708793C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| СУММАТОР ПО МОДУЛЮ q | 2018 |

|

RU2702970C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2006 |

|

RU2300131C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в расширении арсенала средств того же назначения. Умножитель по модулю q, содержащий элемент И, при этом в умножитель q дополнительно введены два элемента И и четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. 1 табл., 1 ил.

Умножитель по модулю q, содержащий элемент И, отличающийся тем, что в него дополнительно введены два элемента И и четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход третьего и первый, второй входы четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с вторыми и первыми входами второго, первого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй входы j-го  и первый, второй входы третьего элементов И соединены соответственно с выходом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом третьего элемента И и выходами третьего, четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы (j+2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход j-го элемента И соединены соответственно с (2×j-1)-м, (2×j)-ым входами и j-м выходом умножителя по модулю q.

и первый, второй входы третьего элементов И соединены соответственно с выходом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом третьего элемента И и выходами третьего, четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы (j+2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход j-го элемента И соединены соответственно с (2×j-1)-м, (2×j)-ым входами и j-м выходом умножителя по модулю q.

| МНОГОРАЗРЯДНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР ПО МОДУЛЮ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ | 2010 |

|

RU2439661C2 |

| Железобетонные плиты для полов, тротуаров, укрепления откосов и т.п. | 1928 |

|

SU9600A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2010 |

|

RU2446444C1 |

| Двухразрядный двоичный умножитель | 1988 |

|

SU1501048A1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ | 2015 |

|

RU2589361C1 |

| Способ сожигания угольной пыли в цилиндрах двигателей внутреннего горения и в паропроизводителях с непосредственным действием продуктов горения на воду | 1925 |

|

SU7002A1 |

| US 8903882 B2, 02.12.2014. | |||

Авторы

Даты

2020-02-07—Публикация

2019-03-11—Подача