Заявляемое изобретение относится к области автоматического управления устройствами, использующими пропорционально-интегрально-дифференциальные законы (ПИД-законы) регулирования, и может найти применение в радиотехнических системах в условиях интенсивного информационного возмущения.

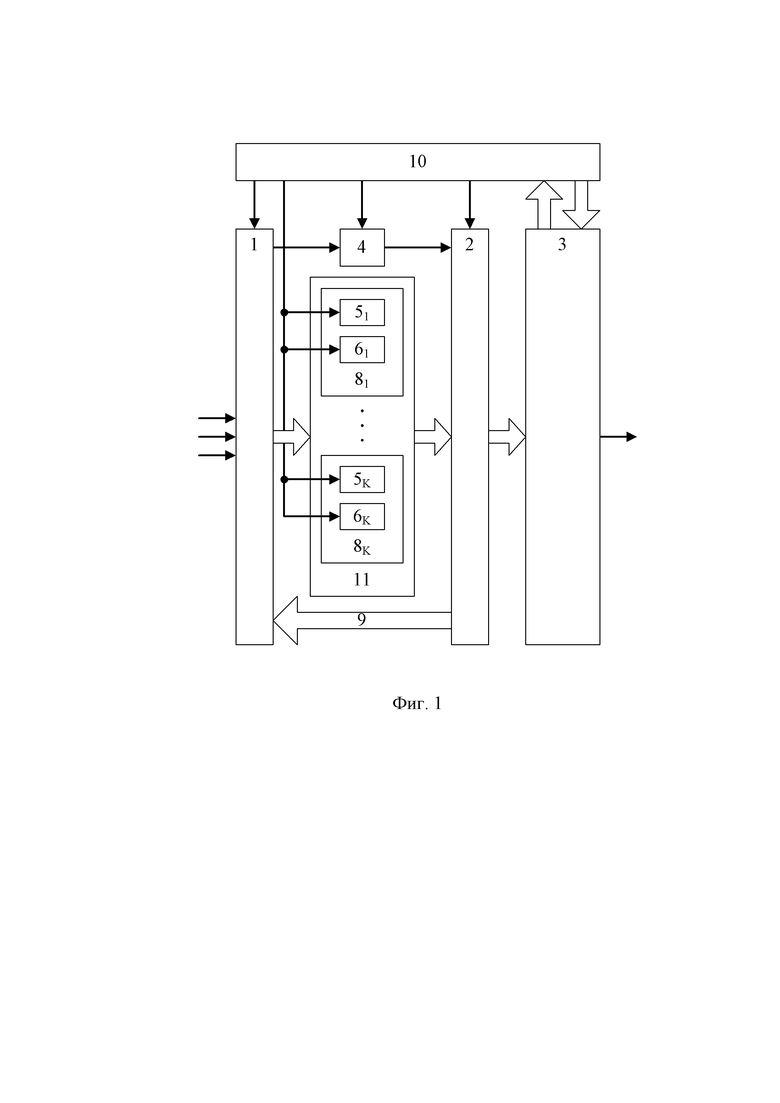

Известна система адаптивного управления по ПИД-закону [1], принятая в качестве прототипа. Структурно-функциональная схема устройства-прототипа приведена на фиг. 1, где приняты следующие обозначения:

1 - коммутационная матрица входов (КМвх);

2 - коммутационная матрица выходов (КМвых);

3 - решающее устройство (РУ);

4 - пропорциональный блок (ПБ);

51…5K - интегрирующие блоки (ИБ);

61…6K - дифференцирующие блоки (ДБ);

81…8K - интегрирующе-дифференцирующие кластеры (ИДК);

9 - сигнальная шина (СШ);

10 - контроллер функциональной логики (КФЛ);

11 - интегрирующе-дифференцирующий блок (ИДБ);

Устройство-прототип содержит коммутационную матрицу входов (КМвх) 1, первый выход которой соединен с сигнальным входом пропорционального блока (ПБ) 4, выход которого соединен с первым сигнальным входом коммутационной матрицы выходов (КМвых) 2, первый выход которой соединен с первым сигнальным входом решающего устройства (РУ) 3. Входами устройства-прототипа являются сигнальные входы КМвх 1.

Интегрирующе-дифференцирующий блок (ИДБ) 11 устройства-прототипа содержит К интегрирующе-дифференцирующих кластеров (ИДК) 81…8K, каждый из которых содержит один из K интегрирующих блоков (ИБ) 51…5K с собственным нормирующим коэффициентом (И1…ИK) и один из K дифференцирующих блоков (ДБ) 61…6K с собственным нормирующим коэффициентом (Д1…ДK) соответственно.

Причем в ИДБ 11 имеется K пар сигнальных входов (т. е. 2K сигнальных входов), которые в то же время, являются парами сигнальных входов соответствующих ИДК 81…8K, где первый сигнальный вход ИДК 8 является сигнальным входом соответствующего ИБ 5, а второй сигнальный вход ИДК 8 является сигнальным входом соответствующего ДБ 6. Кроме того, в ИДБ 11 имеется K пар выходов (т.е. 2K выходов), которые в то же время являются парами выходов соответствующих ИДК 81…8K, где первый выход ИДК 8 является выходом соответствующего ИБ 5, а второй выход ИДК 8 является выходом соответствующего ДБ 6.

При этом K пар сигнальных входов ИДБ 11 соединены соответственно с K парами выходов КМвх 1, а K пар выходов ИДБ 11 соединены с соответствующими K парами сигнальных входов КМвых 2, K пар выходов которой соединены с соответствующими K парами сигнальных входов РУ 3, выход которого является выходом устройства-прототипа.

Также устройство-прототип содержит контроллер функциональной логики (КФЛ) 10, первый выход которого соединен с управляющим входом КМвх 1, второй выход - с управляющим входом ПБ 4, третий выход - с управляющими входами каждого из K интегрирующих 51…5K и K дифференцирующих 61…6K блоков; четвертый выход - с управляющим входом КМвых 2, а остальные выходы КФЛ 10 соединены с соответствующими управляющими входами РУ 3, информационные выходы которого соединены с соответствующими информационными входами КФЛ 10.

Кроме того, группа выходов КМвых 2 посредством сигнальной шины (СШ) 9 соединена с группой сигнальных входов КМвх 1.

Устройство-прототип работает следующим образом.

При включении КФЛ 10 инициализирует значения коэффициентов И1…ИK и Д1…ДK блоков 5 и 6, производит установку параметров ПБ 4 и инициализацию структуры соединений КМвх 1 и КМвых 2 путем подачи на управляющие входы этих блоков соответствующих управляющих сигналов.

Далее КФЛ 10 считывает начальные значения всех сигналов из информационных выходов РУ 3. Полученные данные сохраняют в КФЛ 10 для проведения последующих вычислений.

Входной регулируемый сигнал поступает на первый сигнальный вход КМвх 1. На второй сигнальный вход КМвх 1 подается сигнал обратной связи, на третий сигнальный вход КМвх 1 поступает сигнал внешнего возмущения.

Блоки КМвх 1 и КМвых 2 организуют соединения ИДК 81…8K в единую структуру, которая обеспечивает подачу входного сигнала на сигнальные входы ПБ 4 и ИДБ 11.

В ПБ 4 осуществляется пропорциональное преобразование входного сигнала в соответствии с установленными ранее параметрами; затем преобразованный сигнал с выхода ПБ 4 через КМвых 2 подается на первый сигнальный вход РУ 3.

В блоке 11 осуществляется интегрально-дифференциальное преобразование входного сигнала, заключающееся в устранении статических ошибок и упреждении по возмущению. Преобразованный сигнал с выходов ИДБ 11 через КМвых 2 подается на остальные сигнальные входы РУ 3.

СШ 9, образующая интерфейс между КМвых 2 и КМвх 1, позволяет организовывать последовательные соединения ИДК 81…8K (обеспечивает подключение выходов ИДК 81…8K к входам ИДК 81…8K при необходимости реализации последовательной структуры).

При этом количество задействованных сигнальных входов и выходов блоков 1, 2, 3 и 11 определяется задачей управления и степенью неопределенности параметров управляемого объекта.

Каждый ИБ 51…5K и ДБ 61…6K имеет собственный нормирующий коэффициент, вычисляемый в КФЛ 10 на основе предшествующих значений сигнала. Упреждающее управление реализуется в ДБ 61…6K с нормирующими коэффициентами Д1…ДK. Компенсация статических ошибок реализуется в ИБ 51…5K с нормирующими коэффициентами И1…ИK. Далее с выхода РУ 3 информация о сигналах подается на информационные входы КФЛ 10.

В КФЛ 10 производится расчет значений управляющих сигналов по всем контурам регулирования, и определяются значения результирующих коэффициентов. При этом КФЛ 10, реализующий управляющую логику, использует условные правила, заложенные в программном обеспечении, для преобразования массива входных сигналов в управляющие.

Управляющие сигналы с выходов КФЛ 10 подаются на КМвх 1, КМвых 2, РУ 3, ПБ 4 и ИДБ 11, причем могут переконфигурироваться значения коэффициентов ПБ 4, И1…ИK и Д1…ДK блока 11.

Получив управляющие сигналы, КМвх 1 и КМвых 2 могут переконфигурировать структуру соединений.

Получив управляющие сигналы, РУ 3 формирует выходной сигнал.

Поскольку система состоит из множества связанных между собой с помощью КМвх 1 и КМвых 2 блоков ИДК 81…8K, количество и структура взаимосвязей может варьироваться в зависимости от поставленной задачи.

Недостатком устройства-прототипа является ограничение функциональности в реализации адаптивного регулирования, заключающееся в использовании только ПИД-законов формирования управляющего воздействия. В случаях внезапных и/или сильных изменений внешних воздействий для восстановления устойчивого регулирования с использованием только ПИД-законов может потребоваться значительно большее время. Кроме того, существует вероятность возникновения неблагоприятного сочетания внешних условий, которое может привести к формированию ПИД-регуляторами рассогласованных управляющих воздействий.

Задача, на решение которой направлено заявляемое изобретение, заключается в расширении функциональных возможностей устройства адаптивного управления.

Достигаемый технический результат - способность устройства адаптивного управления принимать альтернативные решения, не основанные на ПИД-законах, а заранее сформированные на основе экспертных знаний [2].

Для хранения экспертных данных предлагается использовать таблицы соответствия (таблицы поиска, look up table, LUT) [3] и [4], которые на практике являются специализированными запоминающими устройствами и в настоящее время применяются в области вычислительной техники.

Для решения поставленной задачи в устройство адаптивного управления по ПИД-закону, содержащее коммутационные матрицы входов (КМвх) и выходов (КМвых), решающее устройство, пропорциональный блок, контроллер функциональной логики (КФЛ), интегрирующе-дифференцирующий блок (ИДБ), включающий K интегрирующе-дифференцирующих кластеров (ИДК), каждый из которых содержит по интегрирующему и дифференцирующему блоку с собственными нормирующими коэффициентами, согласно изобретению, введена в каждый ИДК таблица соответствия. Выход решающего устройства является выходом устройства адаптивного управления. Для каждого ИДК первый сигнальный вход является сигнальным входом соответствующего интегрирующего блока, второй сигнальный вход - сигнальным входом соответствующего дифференцирующего блока, а третий сигнальный вход - сигнальным входом соответствующей таблицы соответствия. Группы из трех сигнальных входов всех ИДК являются 3K сигнальными входами ИДБ, которые соединены с соответствующими 3K выходами КМвх. Для каждого ИДК первый выход является выходом соответствующего интегрирующего блока, второй выход - выходом соответствующего дифференцирующего блока, а третий выход - выходом соответствующей таблицы соответствия. Группы из трех выходов всех ИДК являются 3K выходами ИДБ, которые соединены с соответствующими 3K сигнальными входами КМвых. Сигнальный вход пропорционального блока соединен с первым выходом КМвх, а выход - с первым сигнальным входом КМвых. Группа выходов КМвых посредством сигнальной шины соединена с группой сигнальных входов КМвх, остальные сигнальные входы которой являются входами устройства. Первый выход КМвых соединен с первым сигнальным входом решающего устройства, 3K сигнальных входов которого соединены с соответствующими 3K выходами КМвых. Первый выход КФЛ соединен с управляющим входом КМвх, второй выход - с управляющим входом пропорционального блока, третий выход - с управляющими входами каждого из K интегрирующих, K дифференцирующих блоков и каждой из K таблиц соответствия, четвертый выход - с управляющим входом КМвых. Остальные выходы КФЛ соединены с соответствующими управляющими входами решающего устройства, информационные выходы которого соединены с соответствующими информационными входами КФЛ.

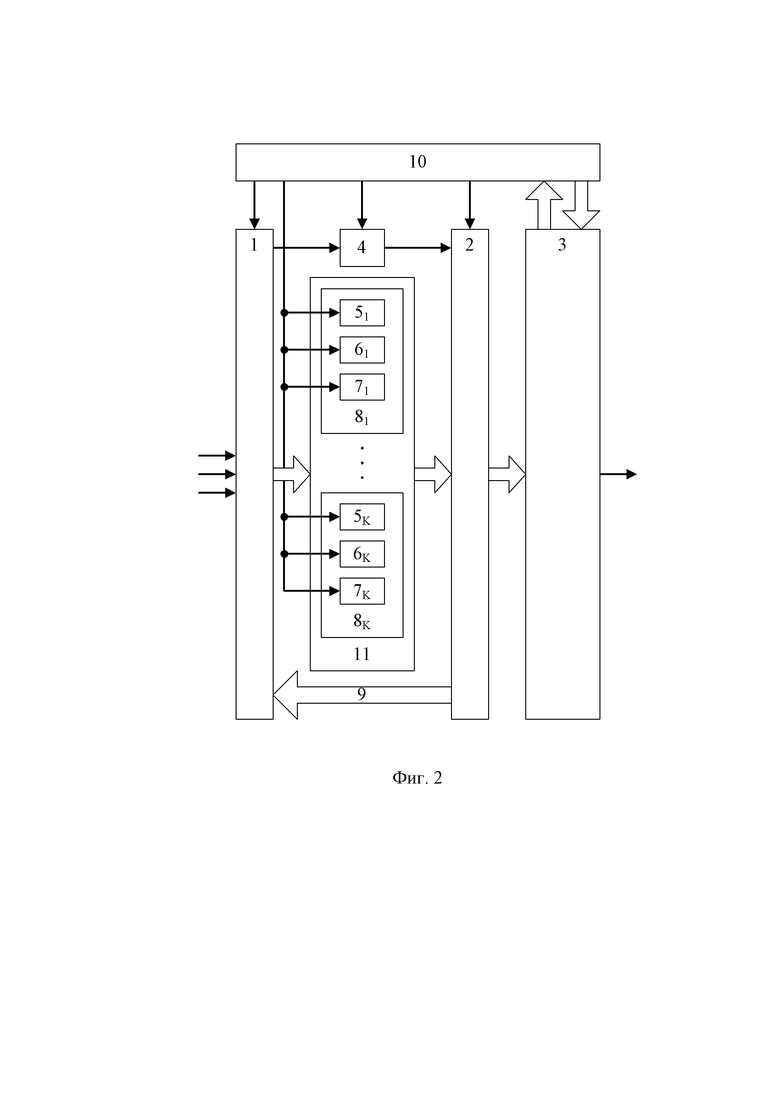

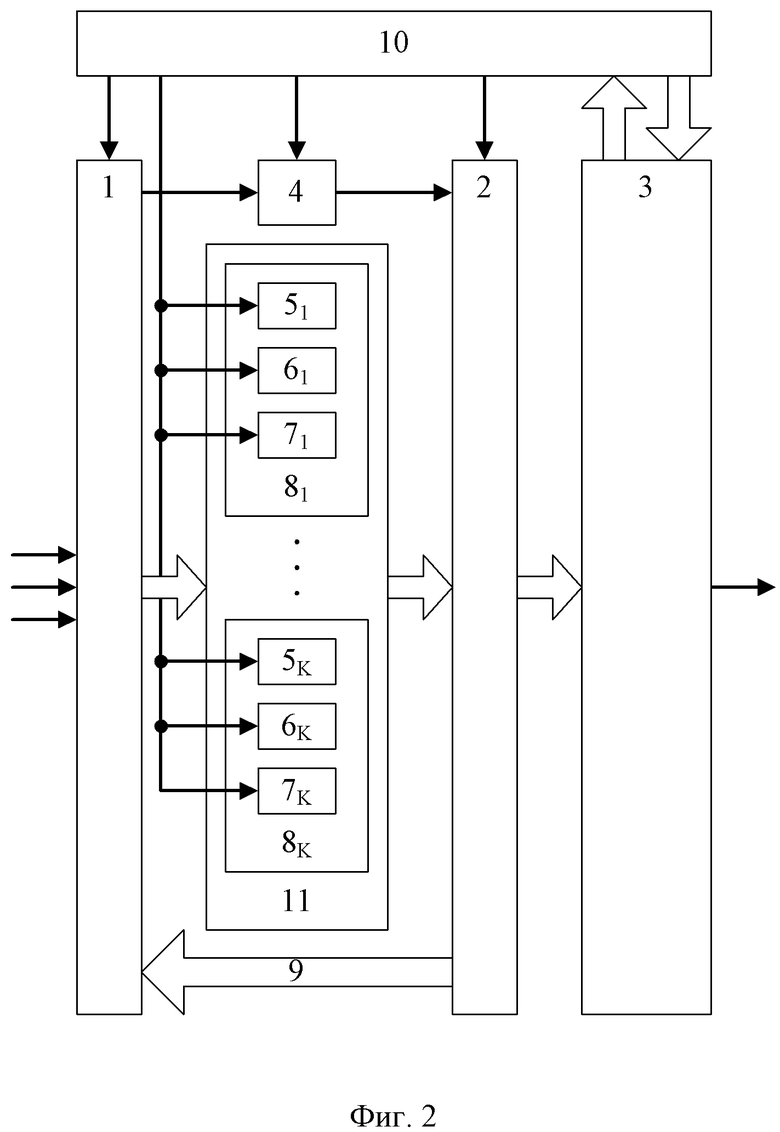

Структурно-функциональная схема предлагаемого устройства представлена на фиг. 2, где приняты следующие обозначения:

1 - коммутационная матрица входов (КМвх);

2 - коммутационная матрица выходов (КМвых);

3 - решающее устройство (РУ);

4 - пропорциональный блок (ПБ);

51…5K - интегрирующие блоки (ИБ);

61…6K - дифференцирующие блоки (ДБ);

71…7K - таблицы соответствия (ТС);

81…8K - интегрирующе-дифференцирующие кластеры (ИДК);

9 - сигнальная шина (СШ);

10 - контроллер функциональной логики (КФЛ);

11 - интегрирующе-дифференцирующий блок (ИДБ);

Заявляемое устройство содержит коммутационную матрицу входов (КМвх) 1, первый выход которой соединен с сигнальным входом пропорционального блока (ПБ) 4, выход которого соединен с первым сигнальным входом коммутационной матрицы выходов (КМвых) 2, первый выход которой соединен с первым сигнальным входом решающего устройства (РУ) 3. Входами устройства являются сигнальные входы КМвх 1. Группа выходов КМвых 2 посредством сигнальной шины (СШ) 9 соединена с группой сигнальных входов КМвх 1.

Интегрирующе-дифференцирующий блок (ИДБ) 11 заявляемого устройства содержит К интегрирующе-дифференцирующих кластеров (ИДК) 81…8K, каждый из которых содержит один из K интегрирующих блоков (ИБ) 51…5K с собственным нормирующим коэффициентом И1…ИK соответственно, один из K дифференцирующих блоков (ДБ) 61…6K с собственным нормирующим коэффициентом Д1…ДK соответственно и одна из K таблиц соответствия (ТС) 71…7K.

В ИДБ 11 имеется K групп из трех сигнальных входов (т. е. 3K сигнальных входов), которые в то же время, являются группами из трех сигнальных входов соответствующих ИДК 81…8K, где первый сигнальный вход ИДК 8 является сигнальным входом соответствующего ИБ 5, второй сигнальный вход ИДК 8 является сигнальным входом соответствующего ДБ 6, а третий сигнальный вход ИДК 8 является сигнальным входом соответствующей ТС 7. Кроме того, в ИДБ 11 имеется K групп из трех выходов (т.е. 3K выходов), которые в то же время являются группами из трех выходов соответствующих ИДК 81…8K, где первый выход ИДК 8 является выходом соответствующего ИБ 5, второй выход ИДК 8 является выходом соответствующего ДБ 6, а третий выход ИДК 8 является выходом соответствующей ТС 7. При этом K групп из трех сигнальных входов ИДБ 11 соединены соответственно с K группами из трех выходов КМвх 1, а K групп из трех выходов ИДБ 11 соединены с соответствующими K группами из трех сигнальных входов КМвых 2, K групп из трех выходов которой соединены с соответствующими K группами из трех сигнальных входов РУ 3, выход которого является выходом устройства.

Также предлагаемое устройство содержит контроллер функциональной логики (КФЛ) 10, первый выход которого соединен с управляющим входом КМвх 1, второй выход - с управляющим входом ПБ 4, третий выход - с управляющими входами каждого из K интегрирующих 51…5K, K дифференцирующих 61…6K блоков и K таблиц соответствия 71…7K; четвертый выход – с управляющим входом КМвых 2, а остальные выходы КФЛ 10 соединены с соответствующими управляющими входами РУ 3, информационные выходы которого соединены с соответствующими информационными входами КФЛ 10.

Предлагаемое устройство работает следующим образом.

При включении КФЛ 10 инициализирует значения коэффициентов интегрирующих блоков 51…5K, дифференцирующих блоков 61…6K (И1…ИK, Д1…ДK соответственно) и ТС 71…7K, производит установку параметров ПБ 4, КМвх 1 и КМвых 2 путем подачи на управляющие входы перечисленных блоков соответствующих управляющих сигналов. КФЛ 10 считывает начальные значения сигналов из информационных выводов РУ 3.

На первый, второй и третий сигнальные входы КМвх 1 поступают соответственно входной регулируемый сигнал, сигнал обратной связи и сигнал внешнего возмущения. Далее эти сигналы подаются на сигнальные входы ПБ 4 и ИДБ 11.

ПБ 4 реализует пропорциональное преобразование входного сигнала. С выхода ПБ 4 преобразованный сигнал через КМвых 2 поступает на первый сигнальный вход РУ 3.

В каждом ИДК 8 блока 11 ИБ 5 осуществляет интегральное преобразование входного сигнала с соответствующим нормирующим коэффициентом ИДБ 6 реализует дифференциальное преобразование входного сигнала с соответствующим нормирующим коэффициентом Д, ТС 7 выдает сигнал с требуемыми данными. Сигналы с выходов ИДБ 11 через КМвых 2 поступают на остальные сигнальные входы РУ 3.

С выхода РУ 3 информация о сигналах поступает на информационные входы КФЛ 10. С использованием полученных данных в КФЛ 10 реализуется алгоритм адаптивного управления, результатом которого является формирование в КФЛ 10 управляющих сигналов на всех его выходах.

За счет управляющего сигнала, ПБ 4 может изменить свои параметры, ИБ 51…5K и ДБ 61…6K могут обновить значения коэффициентов И1…ИK и Д1…ДK соответственно, КМвх 1 и КМвых 2 могут переконфигурировать структуру соединений. Причем СШ 9 позволяет организовать последовательное соединение ИДК 81…8K (подключение выходов ИДК 81…8K к сигнальным входам ИДК 81…8K). Количество и структура взаимосвязей ИДК 81…8K могут варьироваться в пределах существующей задачи.

Получив управляющие сигналы, РУ 3 формирует сигнал, который поступает на выход устройства.

ТС 7 блока ИДК 8 используется в следующих случаях:

- ПИД-регулирование не дает положительного результата либо контрпродуктивно, когда значения анализируемых параметров находятся за допустимыми пределами;

- ПИД-регулирование имеет низкую эффективность, что приводит к увеличению времени адаптации и, как следствие, вероятности нарушения установившегося режима работы устройства.

В этих случаях КФЛ 10 формирует управляющие сигналы, поступающие на управляющие входы ТС 71…7K тех блоков ИДК 81…8K, в которых необходимо реализовать табличное преобразование входного регулируемого сигнала. На сигнальный вход каждой из этих ТС 7 подается сигнал с кодом расположения требуемых данных из ТС 7. Далее ТС 7 выдает эти данные, которые поступают в КМвых 2.

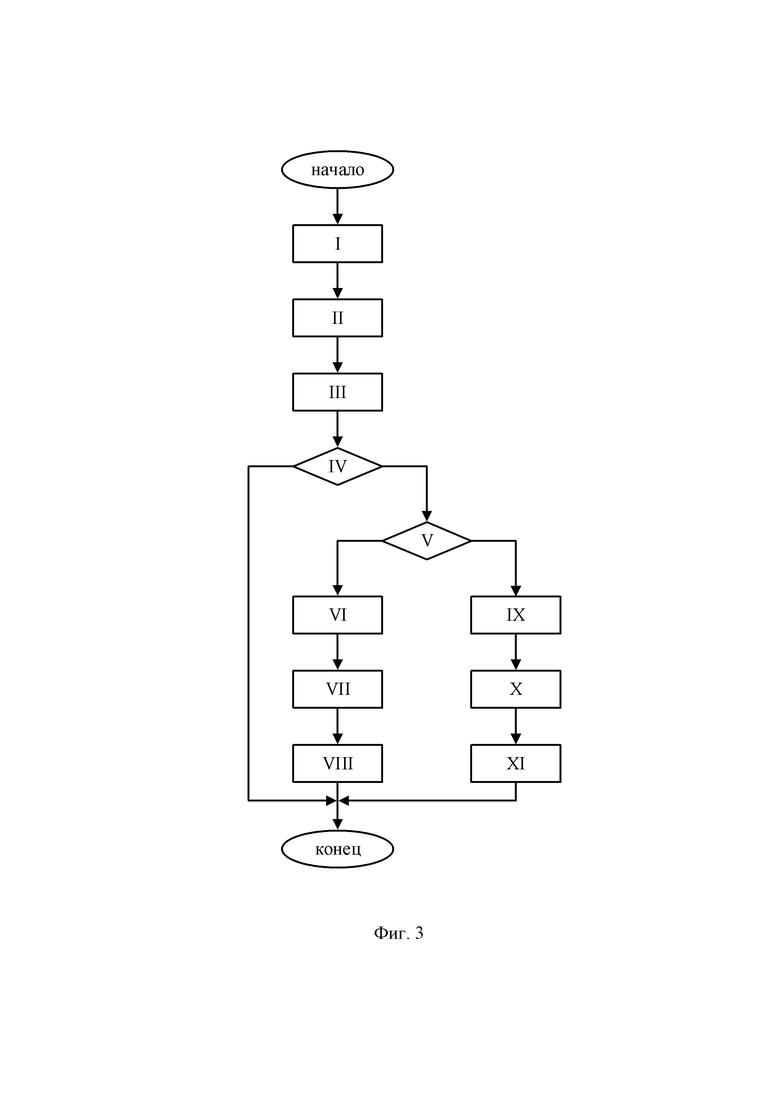

Алгоритм функционирования КФЛ 10 поясняется с помощью фиг. 3.

В блоке I происходит инициализация коэффициентов интегрирующих блоков 51…5K, дифференцирующих блоков 61…6K (И1…ИK, Д1…ДK соответственно) и ТС 71…7K, производится установка параметров ПБ 4, КМвх 1 и КМвых 2 путем подачи на управляющие входы перечисленных блоков соответствующих управляющих сигналов.

В блоке II происходит считывание значений входных сигналов из информационных выводов РУ 3.

В блоке III происходит сравнение полученных значений входных сигналов с требуемыми значениями.

В блоке IV выносится решение о необходимости коррекции управляющего воздействия. Если коррекция не требуется, алгоритм функционирования КФЛ 10 на этом заканчивается, иначе производится переход к блоку 5.

В блоке V определяется способ формирования управляющего воздействия: на основе ПИД-законов или с использованием данных из ТС 71…7K.

Если в формировании управляющего воздействия требуются ТС 71…7K, то производится переход к блоку VI. В этом блоке осуществляется коррекция данных для ТС 71…7K.

В блоке VII производится запись обновленных в предыдущем блоке значений в ТС 71…7K.

В блоке VIII происходит включение ТС 71…7K и установление взаимосвязей между ними и остальными элементами ИДБ 11 с помощью переконфигурирования КМвх 1 и КМвых 2.

Если в формировании управляющего воздействия достаточно использования ПИД-законов регулирования, то выполняется переход с блока V к блоку IX. В блоке IX корректируются нормирующие коэффициенты интегрирующих блоков И1…ИK и дифференцирующих блоков Д1…ДK.

В блоке X обновленные нормирующие коэффициенты И1…ИK и Д1…ДK записываются в соответствующие ИБ 51…5K и ДБ 61…6K.

В блоке XI происходит отключение ранее использовавшихся ТС 71…7K и обновление конфигурации соединений между элементами ИДБ 11 с помощью КМвх 1 и КМвых 2.

Действия в блоке I выполняются, как правило, при включении устройства адаптивного управления. Действия в блоках II - XI представляют собой цикл операций КФЛ 10, который периодически выполняется во время работы устройства.

Таким образом, таблицы соответствия в устройстве адаптивного управления реализуют дополнительные функциональные возможности, которые становятся востребованными в случае угрозы существенного снижения эффективности ПИД-регулирования вследствие внезапных и/или сильных изменений внешних воздействий. В результате расширяется область применения предлагаемого устройства.

Реализация

Предлагаемое устройство можно реализовать на следующих элементах:

- коммутационные матрицы, таблицы соответствия можно сконфигурировать на основе ПЛИС (программируемых логических интегральных схем), например, фирмы «ALTERA» [5];

- решающее устройство, пропорциональные, интегрирующие и дифференцирующие блоки можно реализовать на специализированных аналоговых и/или цифровых устройствах, предназначенных для управления требуемыми физическими параметрами системы (например, для управления частотой необходимы многофункциональные датчики, включая АЦП и/или ЦАП) [6, 7, 8, 9];

- контроллер функциональной логики можно реализовать на основе микроконтроллера или микропроцессора, например, отечественной интегральной микросхемы микропроцессора 1892ВМ10Я [10].

Источники информации

1. Патент РФ на изобретение №2510956 «Способ адаптивного управления по ПИД-закону и система для его реализации». / Асосков А. Н., Малышева И. Н., Плахотнюк Ю. А., Орлянский В. Н., 2014.

2. Макаренко С. И. Интеллектуальные информационные системы: учебное пособие. - Ставрополь: СФ МГГУ им. М. А. Шолохова, 2009. - 206 с.

3. Угрюмов Е. П. Цифровая схемотехника: учеб. пособие для вузов. - 3-е изд., перераб. и доп. - СПб.: БХВ-Петербург, 2010. - 816 с.

4. Патент РФ на изобретение №2559772 «Устройство для основного деления модулярных чисел в формате системы остаточных классов». / Червяков Н. И., Бабенко М. Г., Ляхов П. А, Лавриненко И. Н., Лавриненко А. В., 2015.

5. http://www.altera.ru - радиоэлектронные компоненты компании «ALTERA».

6. http://www.analog.com/ru/products.html - радиоэлектронные компоненты компании «Analog Devices».

7. http://www.maximintegrated.com/en.html - радиоэлектронные компоненты компании «Maxim Integrated».

8. http://www.ti.com/ru-ru/homepage.html - радиоэлектронные компоненты компании «Texas Instruments».

9. http://www.murata.com - радиоэлектронные компоненты компании «Murata Manufacturing Company, Ltd.».

10. http://www.multicore.ru - отечественные микросхемы компании АО НПЦ «Элвис» (г. Зеленоград).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АДАПТИВНОГО УПРАВЛЕНИЯ ПО ПИД-ЗАКОНУ И СИСТЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2510956C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| КОРРЕЛЯТОР ДЛЯ ШИРОКОПОЛОСНЫХ СИГНАЛОВ С ЧАСТОТНЫМ СДВИГОМ | 2000 |

|

RU2205502C2 |

| Генератор случайных сигналов | 1988 |

|

SU1656662A1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2007 |

|

RU2364022C2 |

| УСТРОЙСТВО ДЛЯ ПРЕДСТАВЛЕНИЯ ГИСТОГРАММЫ СТАТИСТИЧЕСКОГО РАСПРЕДЕЛЕНИЯ | 1972 |

|

SU347760A1 |

| СПОСОБ УПРАВЛЕНИЯ СВЕТОВЫМИ ПОТОКАМИ СВЕТОДИОДНЫХ СВЕТИЛЬНИКОВ В СИСТЕМЕ АРХИТЕКТУРНОЙ ПОДСВЕТКИ ЗДАНИЙ И СООРУЖЕНИЙ | 2013 |

|

RU2547834C1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1756889A1 |

| СИСТЕМА ДЛЯ ВЫПУСКА ПОЛЕЗНЫХ КЛЕЩЕЙ И ЕЕ ПРИМЕНЕНИЯ | 2018 |

|

RU2780624C2 |

| ЦИФРОВОЙ КОРРЕЛЯТОР ПРИЕМНИКА СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2006 |

|

RU2310212C1 |

Устройство адаптивного управления содержит коммутационные матрицы входов (КМвх) и выходов (КМвых), решающее устройство, пропорциональный блок, контроллер функциональной логики (КФЛ), интегрирующе-дифференцирующий блок (ИДБ), сигнальную шину. ИДБ содержит K интегрирующе-дифференцирующих кластеров (ИДК). ИДК содержит интегрирующие блоки, дифференцирующие блоки, таблицы соответствия. Обеспечивается способность устройства управления вырабатывать решения, заранее сформированные на основе экспертных знаний. 3 ил.

Устройство адаптивного управления, содержащее коммутационные матрицы входов (КМвх) и выходов (КМвых), решающее устройство, выход которого является выходом устройства; интегрирующе-дифференцирующий блок (ИДБ), включающий K интегрирующе-дифференцирующих кластеров (ИДК), каждый из которых содержит по интегрирующему и дифференцирующему блоку с собственными нормирующими коэффициентами, причем K пар сигнальных входов ИДБ являются парами сигнальных входов соответствующих ИДК, где первый сигнальный вход ИДК является сигнальным входом соответствующего интегрирующего блока, а второй сигнальный вход ИДК является сигнальным входом соответствующего дифференцирующего блока; K пар выходов ИДБ являются парами выходов соответствующих ИДК, из которых первый выход является выходом соответствующего интегрирующего блока, а второй выход является выходом соответствующего дифференцирующего блока; пропорциональный блок, сигнальный вход которого соединен с первым выходом КМвх, остальные K пар выходов которой соединены с соответствующими K парами сигнальных входов ИДБ, K пар выходов которого соединены с соответствующими K парами сигнальных входов КМвых, группа выходов которой посредством сигнальной шины соединена с группой сигнальных входов КМвх, остальные сигнальные входы которой являются входами устройства; выход пропорционального блока соединен с первым сигнальным входом КМвых, первый выход которой соединен с первым сигнальным входом решающего устройства, остальные K пар сигнальных входов которого соединены с соответствующими K парами выходов КМвых; контроллер функциональной логики (КФЛ), первый выход которого соединен с управляющим входом КМвх, второй выход – с управляющим входом пропорционального блока, третий выход – с управляющими входами каждого из K интегрирующих и K дифференцирующих блоков, четвертый выход – с управляющим входом КМвых, а остальные выходы – с соответствующими управляющими входами решающего устройства, информационные выходы которого соединены с соответствующими информационными входами КФЛ; отличающееся тем, что в каждый ИДК введена таблица соответствия, сигнальный вход которой является третьим сигнальным входом, а выход – третьим выходом соответствующего ИДК, причем третьи сигнальные входы каждого ИДК являются K дополнительными сигнальными входами ИДБ, которые соединены с соответствующими выходами КМвх, а третьи выходы каждого ИДК являются K дополнительными выходами ИДБ, которые соединены с соответствующими сигнальными входами КМвых, K дополнительных выходов которой соединены с соответствующими сигнальными входами решающего устройства, кроме того, управляющий вход каждой из K таблиц соответствия соединен с третьим выходом КФЛ.

| НЕЛИНЕЙНАЯ АДАПТИВНАЯ СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2004 |

|

RU2267147C1 |

| АДАПТИВНЫЙ ИНТЕЛЛЕКТУАЛЬНЫЙ ЛОГИЧЕСКИЙ РЕГУЛЯТОР, РАБОТАЮЩИЙ В УСЛОВИЯХ НЕЧЕТКО ЗАДАННОЙ ИНФОРМАЦИИ | 2014 |

|

RU2579987C2 |

| САМОНАСТРАИВАЮЩИЙСЯ ПИД-РЕГУЛЯТОР | 2009 |

|

RU2419122C2 |

| WO 2007001252 A1, 04.01.2007 | |||

| WO 2017044481 A1, 16.03.2017. | |||

Авторы

Даты

2019-11-22—Публикация

2019-02-06—Подача