Предпосылки создания изобретения

[0001] Система печати может содержать печатающую головку, которая имеет сопла для дозирования печатной текучей среды на мишень. В системе двухмерной (2D) печати мишенью является носитель печати, такой как бумага или подложка другого типа, на которой можно формировать печатные изображения. Примеры систем 2D-печати включают системы струйной печати, которые могут дозировать капельки чернил. В системах трехмерной (3D) печати мишенью может быть слой или несколько слоев модельного материала, наносимых для формирования 3D-объекта.

[0001a] Документ US 6575548 B1 относится к системе и протоколу печати для обеспечения эффективного управления характеристиками энергии струйной печатающей головке. Система печати содержит контроллер, источник питания и узел печатающей головки, имеющий устройство памяти и распределительный процессор, интегрированный с драйвером чернил. Распределительный процессор поддерживает характеристики энергии узла печатающей головки в предварительно запрограммированных приемлемых границах.

Краткое описание чертежей

[0002] Некоторые реализации настоящего раскрытия описаны в отношении следующих фигур.

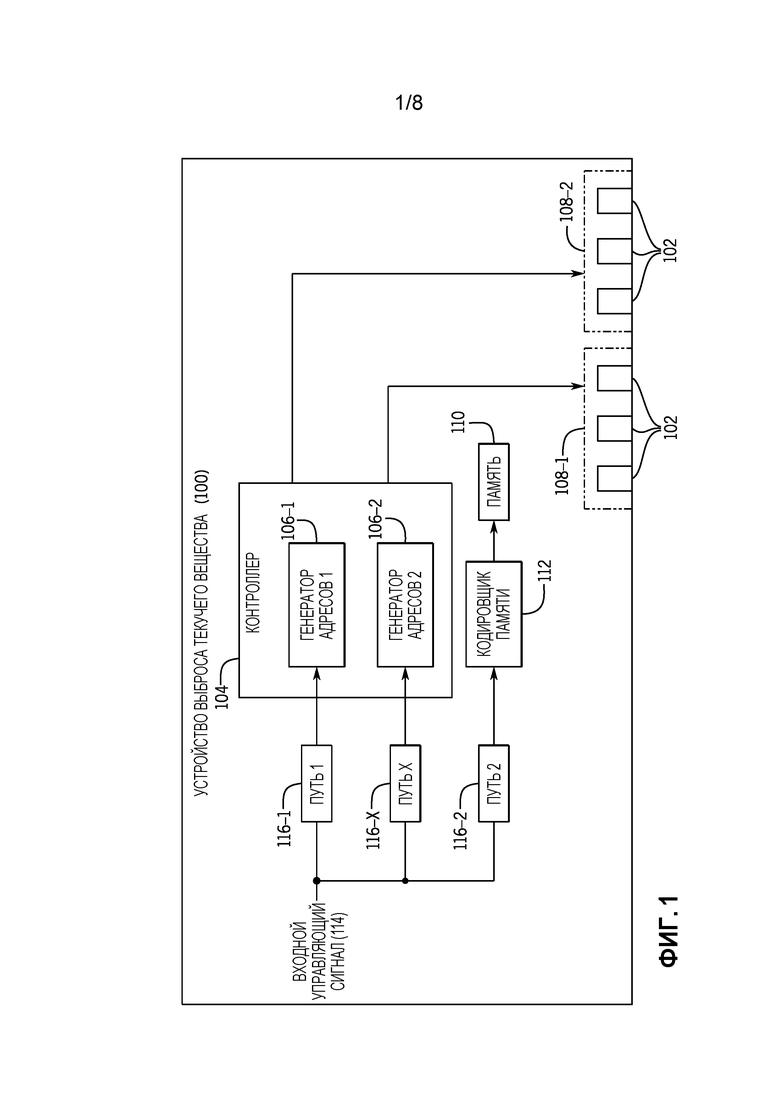

[0003] На фиг. 1 представлена блок-схема устройства выброса текучей среды в соответствии с некоторыми примерами.

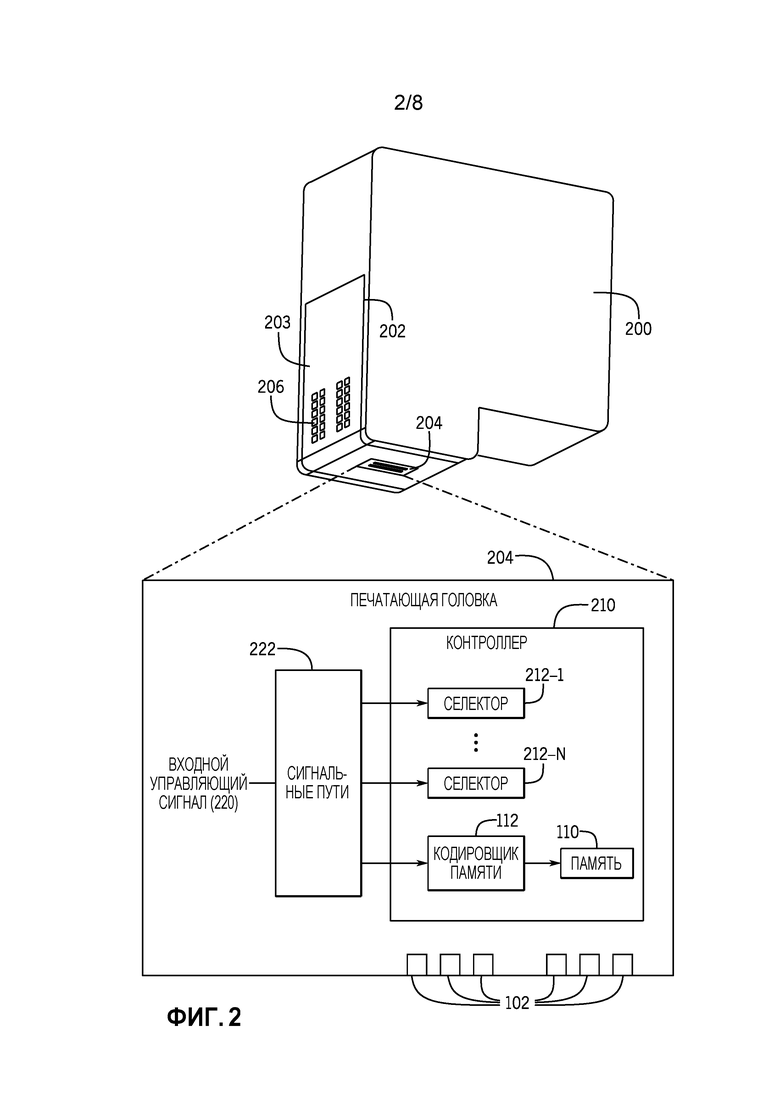

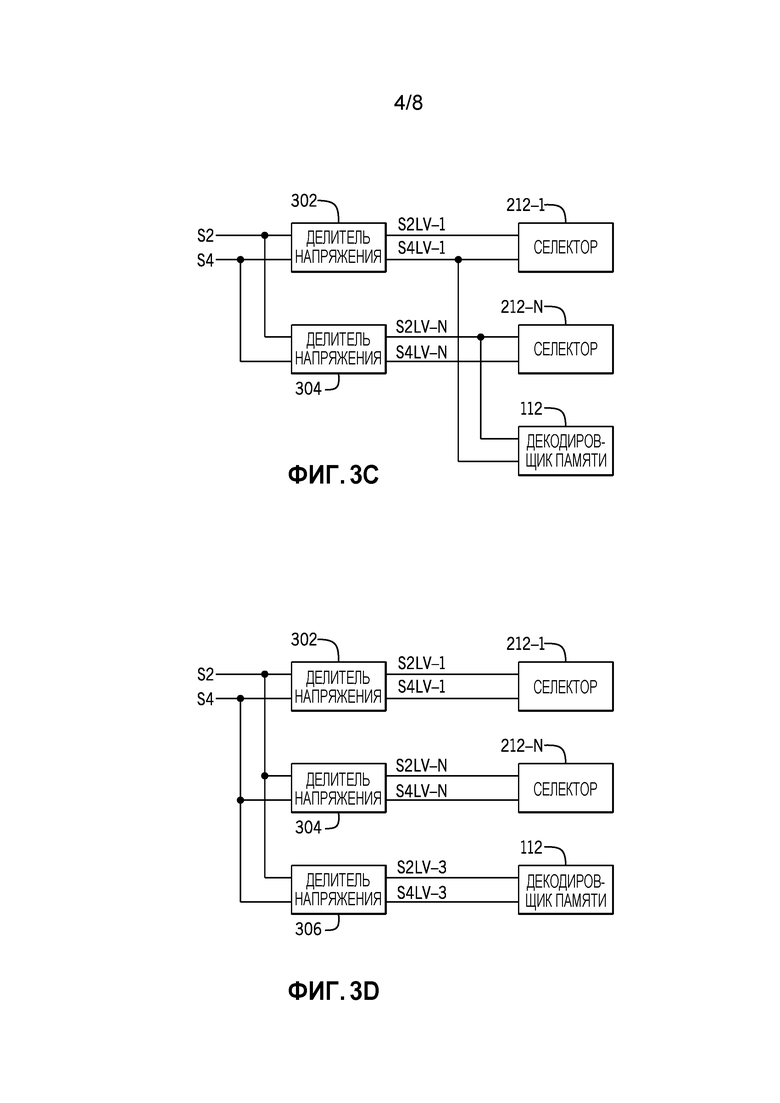

[0004] На фиг. 2 представлена блок-схема печатного картриджа с текучей средой, содержащего печатающую головку, в соответствии с некоторыми примерами.

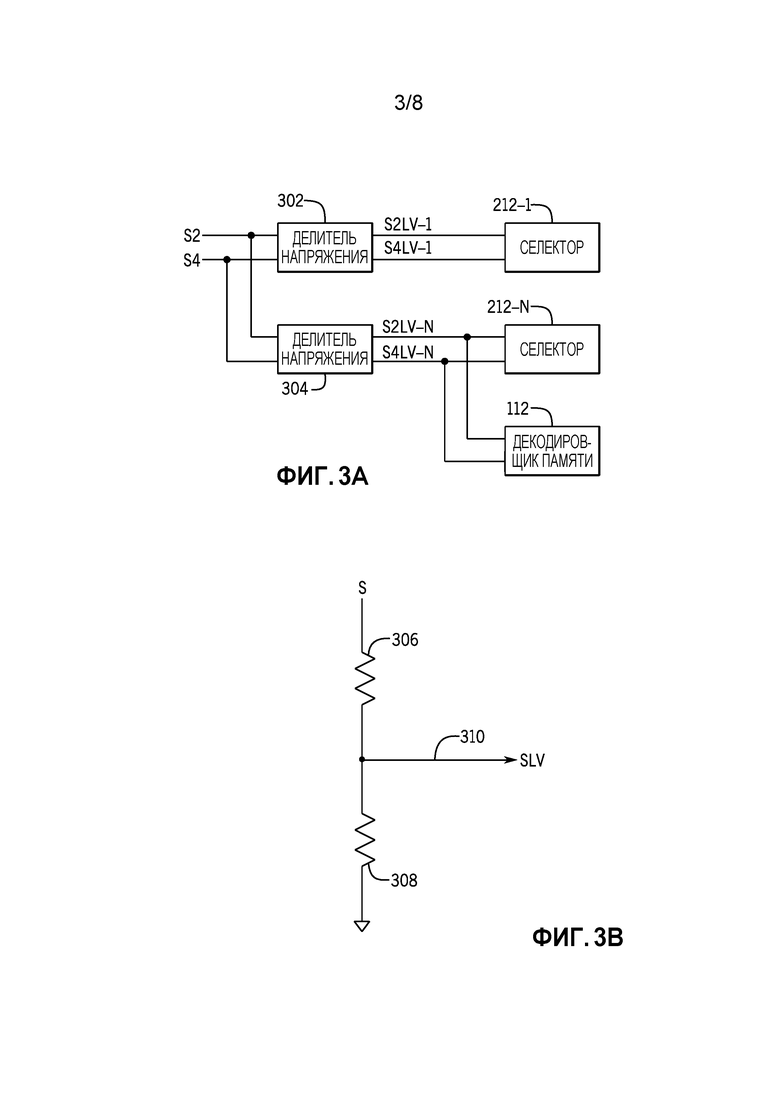

[0005] На фиг. 3A-3D представлены блок-схемы компоновок, в которых для обеспечения отдельных сигнальных путей используют делители напряжения, в соответствии с некоторыми примерами.

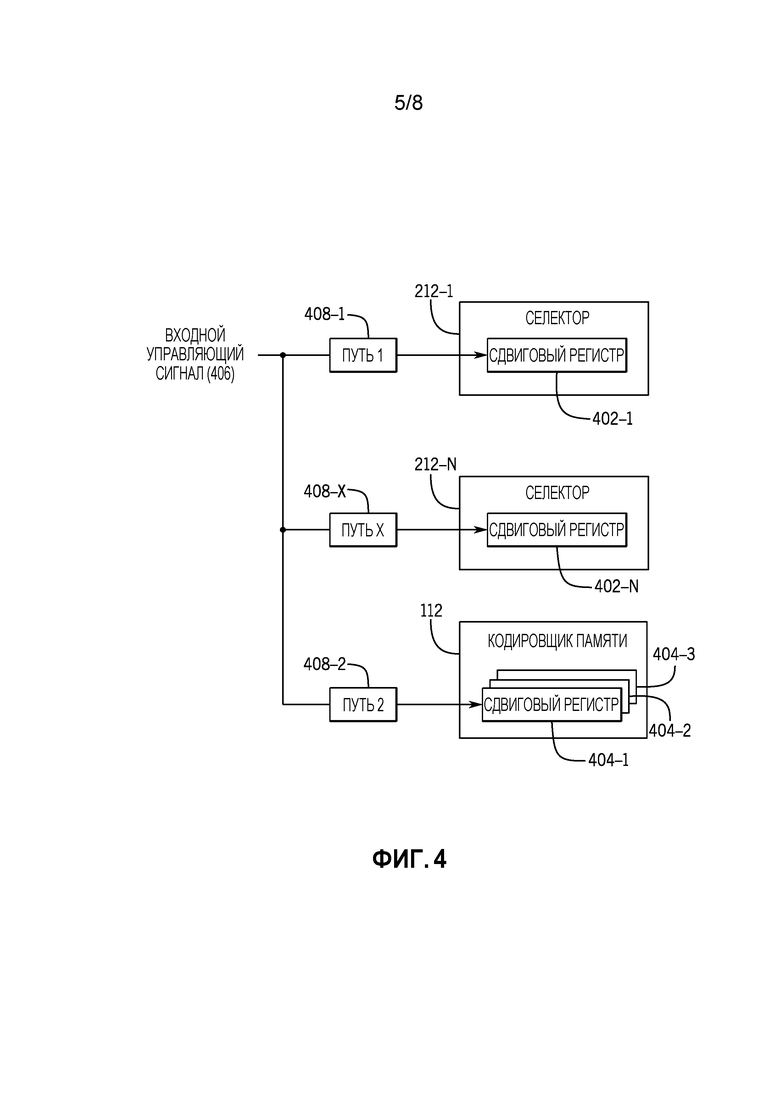

[0006] На фиг. 4 представлена блок-схема компоновки, которая содержит селекторы и кодировщик памяти, содержащие сдвиговые регистры, в соответствии с некоторыми примерами.

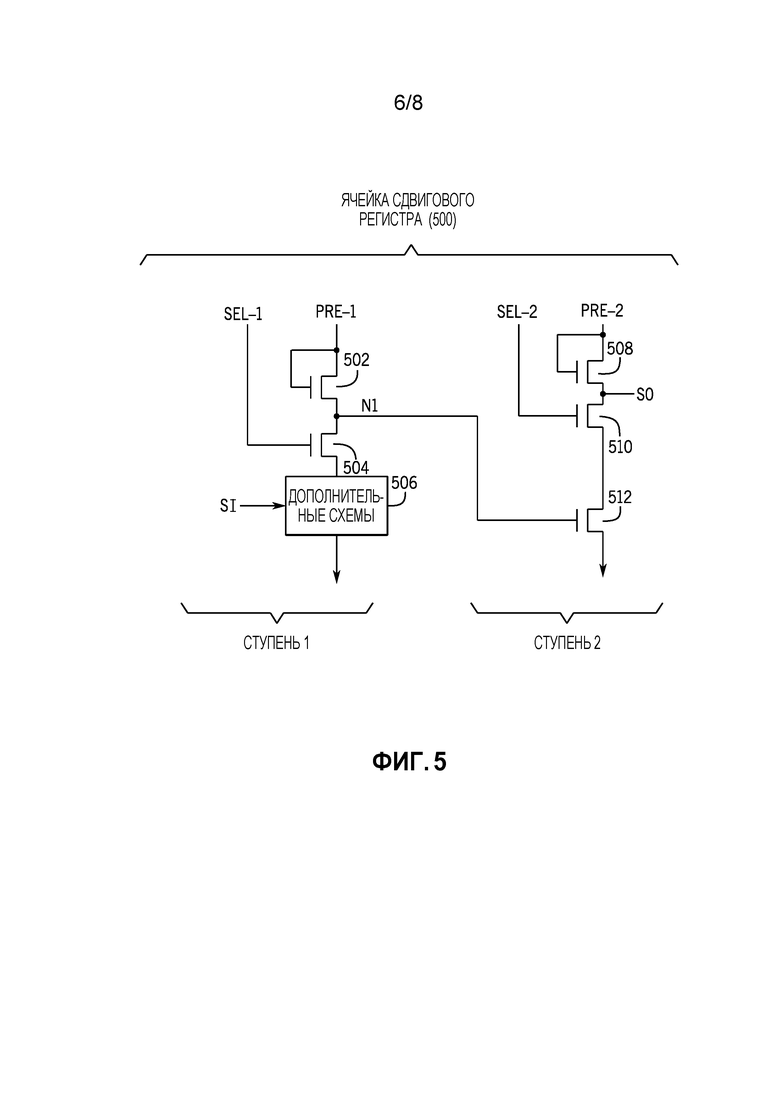

[0007] На фиг. 5 представлена схема соединений ячейки сдвигового регистра в соответствии с некоторыми примерами.

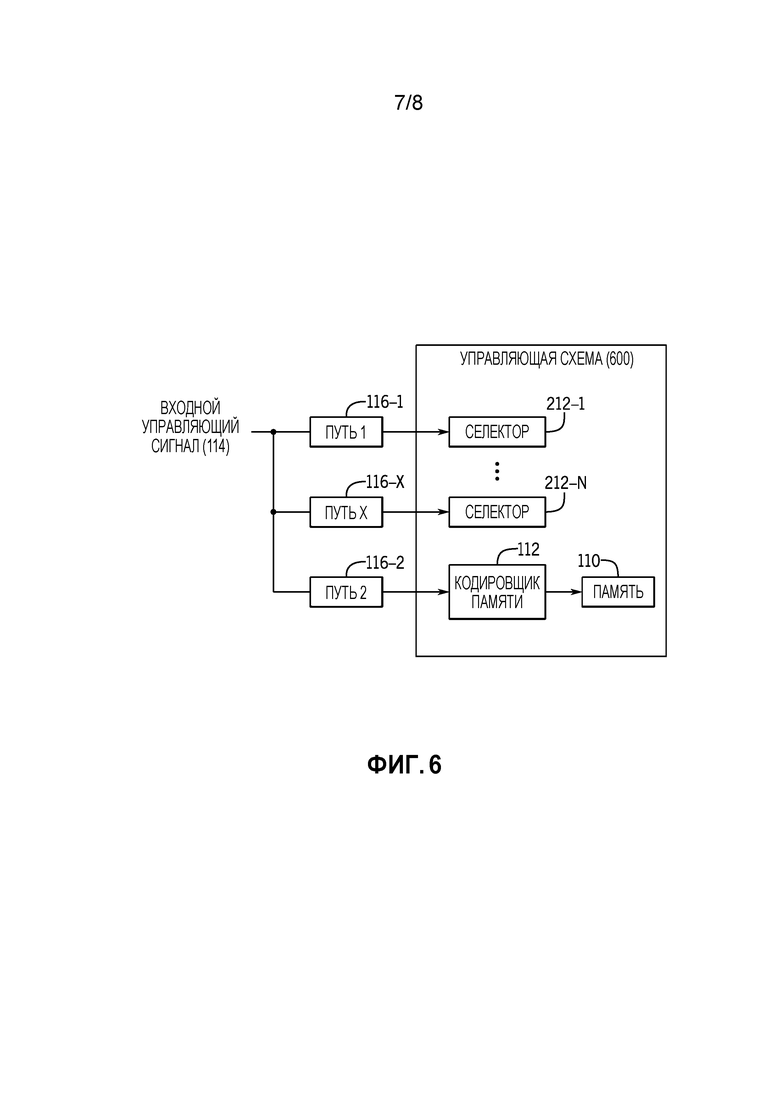

[0008] На фиг. 6 представлена блок-схема цепи управления для устройства выброса текучей среды в соответствии с некоторыми примерами.

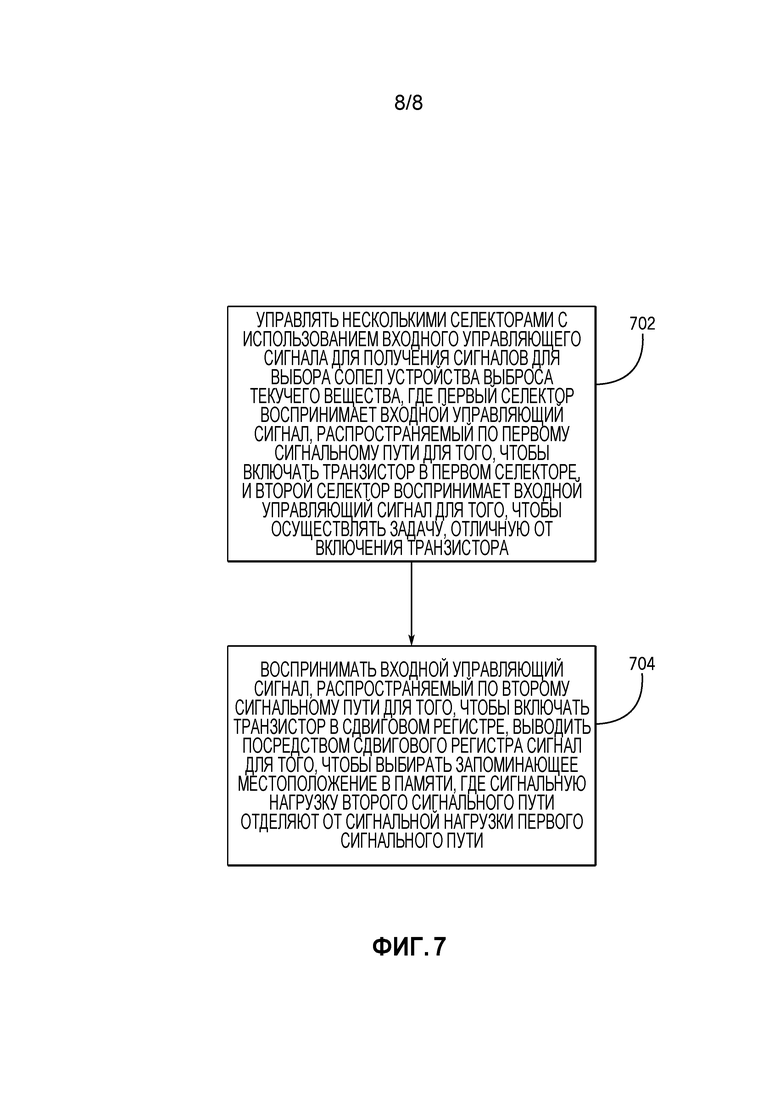

[0009] На фиг. 7 представлена блок-схема последовательности операций процесса в соответствии с некоторыми примерами.

Подробное описание

[0010] В настоящем раскрытии формы единственного числа могут использоваться для отсылки к единственному элементу или альтернативно к нескольким элементам, пока контекст явное не указывает иное. Кроме того, термины «включает», «включающий», «содержит», «содержащий», «имеет» или «имеющий» являются открытыми и означают присутствие указанного элемента(ов), но не исключают присутствия или добавления других элементов.

[0011] Печатающая головка для использования в системе печати может содержать сопла, которые активируют, чтобы вызвать выброс капелек печатной текучей среды из соответствующих сопел. Каждое сопло содержит нагревательный элемент, который при активации создает тепло для испарения печатной текучей среды в камере сгорания сопла, что вызывает выпуск капельки печатной текучей среды из сопла. Система печати может представлять собой систему двухмерной (2D) или трехмерной (3D) печати. Система 2D-печати распределяет печатную текучую среду, такую как чернила, для формирования изображения на носителях печати, таких как бумажные носители или носители печати других типов. Система 3D-печати формирует 3D-объект путем нанесения последовательных слоев модельного материала. Печатные текучие среды, распределяемые из системы 3D-печати, могут включать чернила, а также текучие среды, используемые для слияния порошков в слое модельного материала, детализации слоя модельного материала (например, путем определения границ краев или форм слоя модельного материала) и так далее.

[0012] В последующем обсуждении термин «печатающая головка» может относиться в целом к кристаллу печатающей головки или общему узлу, который содержит несколько кристаллов печатающей головки, установленных на несущей конструкции. Несмотря на то, что в некоторых примерах сделана ссылка на печатающую головку для использования в системе печати, следует отметить, что методы или механизмы по настоящему раскрытию применимы к устройствам выброса текучей среды других типов, используемым в непечатных применениях, которые способны распределять текучие среды через сопла. Примеры таких устройств выброса текучей среды других типов включают те, которые используют в системах восприятия текучих сред, медицинских системах, транспортных средствах, системах управления потоками текучих сред и так далее.

[0013] Печатающая головка может содержать селекторы, которые используют для выбора сопел для активации (приведения в действие). Активированное сопло способно выбрасывать печатную текучую среду. В некоторых реализациях селекторы включают генераторы адресов, которые генерируют адреса, точно определяющие, какие сопла подлежат активации. Сопла, не выбранные посредством генерируемых адресов, остаются неактивным и, таким образом, не выбрасывают печатную текучую среду. В других примерах селекторы могут генерировать другие сигналы для выбора сопел, подлежащих активации.

[0014] Некоторые примерные печатающие головки также содержат память (запоминающие устройства). Память в печатающей головке можно использовать для хранения определенной информации, такой как идентификатор, связанный с печатающей головкой, серийный номер, информация о безопасности и так далее. Печатающая головка может дополнительно содержать кодировщик памяти, который используют для выбора ячейки памяти в памяти, где из выбранной ячейки памяти можно выполнять считывание или выполнять запись в неё. В некоторых примерах кодировщик памяти содержит сдвиговые регистры, которые принимают последовательный ввод и обеспечивают параллельный вывод нескольких сигналов, которые используют для выбора ячейки памяти (или несколько ячеек памяти) в памяти в печатающей головке. Ввод в сдвиговый регистр кодировщика памяти может включать сигнал доступа к памяти, который используют для осуществления доступа к ячейке памяти в памяти.

[0015] Входные управляющие сигналы могут подаваться печатающей головке для осуществления различных задач. При более высоких рабочих частотах входной управляющий сигнал может быть чувствительным к сигнальной нагрузке входного управляющего сигнала. Сигнальная нагрузка основана на числе устройств, таких как транзисторы, с которыми соединяют входной управляющий сигнал. Например, если входной управляющий сигнал используют для включения большого числа транзисторов, то сигнальная нагрузка, испытываемая входным управляющим сигналом, возрастает. Увеличенная сигнальная нагрузка может приводить в результате к тому, что переходы входного управляющего сигнала от низкого к высокому или от высокого к низкому будут пропущены, особенно переходы входного управляющего сигнала на более высокой частоте. Отсутствие переходов входного управляющего сигнала могут приводить к ошибкам при работе определенной схемы печатающей головки, такой как генераторы адресов и кодировщики памяти для памяти. Например, высокая сигнальная нагрузка входного управляющего сигнала может приводить в результате к отсутствию активации определенных сопел, когда они должны быть активированы, что может приводить к неоптимальным печатным изображениям (например, в форме пустых областей в печатных изображениях).

[0016] В соответствии с некоторыми реализациями настоящего раскрытия, применяют изоляцию сигнального пути для изоляции первого сигнального пути, по которому входной управляющий сигнал проходит к первому селектору (например, первому генератору адресов), который используют для выбора сопла(ел) для активации, от второго сигнального пути, по которому входной управляющий сигнал проходит к кодировщику памяти, который используют для выбора ячейки(ек) памяти в памяти. Входной управляющий сигнал также подают на второй селектор (например, второй генератор адресов) для выбора сопла(ел) для активации. Поскольку входной управляющий сигнал обуславливает различные задачи, подлежащие осуществлению на первом и втором селекторах, первый селектор может быть более чувствительным к сигнальной нагрузке входного управляющего сигнала, чем второй селектор. Следует отметить, что первый селектор и второй селектор можно использовать для выбора различных подмножеств сопел для активации. Например, первый селектор можно использовать для выбора сопел в первой области устройства выброса текучей среды (например, печатающей головки или устройства выброса текучей среды другого типа), тогда как второй селектор можно использовать для выбора сопел во второй области устройства выброса текучей среды, причем вторая область отличается от первой области. Различные области могут представлять собой отдельные физические области или отдельные логические области устройства выброса текучей среды.

[0017] Несмотря на то, что сделана ссылка на первый и второй селекторы для выбора сопел для активации, следует отметить, что в других примерах в устройстве выброса текучей среды можно предусмотреть более двух селекторов.

[0018] Фиг. 1 иллюстрирует пример устройства 100 выброса текучей среды, которое может представлять собой печатающую головку, используемую в системе печати (например, системе 2D- или 3D-печати), или устройство выброса текучей среды, используемое не в системе печати. Устройство выброса текучей среды можно реализовать в виде кристалла интегральной схемы (IC), который содержит подложку, на которой предусмотрены сопла и управляющая схема для управления выбросом текучей среды с помощью сопел. Для системы печати кристалл может представлять собой кристалл печатающей головки, который можно устанавливать или прикреплять на каретке системы печати или который можно устанавливать или прикреплять на печатном картридже с текучей средой.

[0019] Устройство 100 выброса текучей среды содержит сопла 102 и контроллер 104 для управления активацией сопел 102. В данном контексте термин «контроллер» может относиться к любому или некоторой комбинации из следующего: микропроцессор, ядро многоядерного микропроцессора, микроконтроллер, программируемая вентильная матрица, программируемое устройство интегральной схемы или любая другая схема обработки аппаратного обеспечения. В дополнительных примерах «контроллер» может относиться к комбинации схемы обработки аппаратного обеспечения и машиночитаемых инструкций, исполняемых в схеме обработки аппаратного обеспечения.

[0020] Контроллер 104 содержит первый генератор 106-1 адресов и второй генератор 106-2 адресов. Каждый генератор 106-1 или 106-2 адресов предназначен для генерирования адреса, который подлежит использованию для выбора сопла (или сопел) для активации. Первый генератор 106-1 адресов используют для управления активацией сопел 102 в первой группе 108-1 сопел, а второй генератор 106-2 адресов служит для управления активацией сопел 102 во второй группе 108-2 сопел. Несмотря на то, что два генератора адресов и две соответствующие группы сопел показаны на фиг. 1, следует отметить, что в других примерах контроллер 104 может содержать больше чем два генератора адресов для управления больше чем двумя группами сопел. Также, в более общем смысле, генераторы 106-1 и 106-2 адресов можно обозначать как селекторы.

[0021] Несмотря на то, что не показано, контроллер 104 дополнительно может содержать пусковые схемы для управления активацией соответствующих сопел. В некоторых примерах имеется одна пусковая схема на сопло. В других примерах может иметь место одна пусковая схема на несколько сопел. Пусковую схему также можно обозначать как пусковую ячейку. Пусковая схема содержит нагревательный элемент, такой как пусковой резистор, который при активации образует тепло для выброса текучей среды из камеры сгорания сопла. Адрес, генерируемый генератором 106-1 или 106-2 адресов, предоставляют на пусковую схему. Адрес управляет тем, какая из определенных пусковых схем выбирается, которая соответственно управляет тем, какое из определенных сопел 102 выбирается.

[0022] Устройство 100 выброса текучей среды дополнительно содержит память 110 и кодировщик 112 памяти, который управляет выбором ячеек памяти в памяти 110 для осуществления доступа (в качестве части выполнения чтения или записи). Кодировщик 112 памяти и память 110 можно реализовать в качестве части устройства памяти, такой как кристалл памяти, или альтернативно, кодировщик 112 памяти и память 110 можно реализовать в виде отдельных компонентов.

[0023] Память 110 может представлять собой энергонезависимую память, такую как стираемое программируемое постоянное запоминающее устройство (EPROM), флэш-память или энергонезависимая память любого другого типа. В других примерах память 110 может представлять собой энергозависимую память, такую как динамическое оперативное запоминающее устройство (DRAM), статическое оперативное запоминающее устройство (SRAM), или энергозависимая память любого другого типа.

[0024] Кодировщик 112 памяти принимает входные сигналы и на основе входных сигналов кодировщик 112 памяти выдает сигналы выбора памяти для выбора ячейки памяти (или ячеек памяти) в памяти 110 для доступа. Аналогичным образом генераторы 106-1 и 106-2 адресов выдают адреса в ответ на входные сигналы.

[0025] Один из входных сигналов, совместно используемый кодировщиком 112 памяти и генераторами 106-1 и 106-2 адресов, представляет собой входной управляющий сигнал 114. Несмотря на то, что выполнена ссылка на один входной управляющий сигнал, совместно используемый кодировщиком 112 памяти и генераторам 106-1 и 106-2 адресов, следует отметить, что в других примерах кодировщик 112 памяти и генераторы 106-1 и 106-2 адресов могут совместно использовать несколько входных управляющих сигналов.

[0026] Высокая нагрузка входного управляющего сигнала в устройстве выброса текучей среды может вызывать ошибки при работе устройства выброса текучей среды, особенно при более высоких рабочих частотах. В соответствии с некоторыми реализациями настоящего раскрытия, сигнальные пути, по которым входной управляющий сигнал 114 подают на соответствующие различные управляющие схемы, можно изолировать друг от друга для снижения или устранения влияний сигнальной нагрузки. В примерах в соответствии с фиг. 1 входной управляющий сигнал 114 подают по первому сигнальному пути 116-1 на первый генератор 106-1 адресов. Входной управляющий сигнал 114 подают по второму сигнальному пути 116-2 на кодировщик 112 памяти. Сигнальную нагрузку первого сигнального пути 116-1 изолируют от сигнальной нагрузки второго сигнального пути 116-2. Сигнальную нагрузку первого и второго сигнальных путей изолируют друг от друга, если источники, которые используют для возбуждения перехода сигнала (от низкого к высокому или от высокого к низкому) для сигнала по первому и второму сигнальному пути, являются различными.

[0027] Кодировщик 112 памяти реагирует на входной управляющий сигнал 114, проходящий по второму сигнальному пути 116-2, включающему в себя устройства (такие как транзисторы) в кодировщике 112 памяти. В настоящем раскрытии включение устройства (например, транзистора) относится к переключению устройства из выключенного состояния во включенное состояние. Аналогичным образом, первый генератор 106-1 адресов реагирует на входной управляющий сигнал 114, проходящий по первому сигнальному пути 106-1, включающему в себя устройства (такие как транзисторы) в первом генераторе 106-1 адресов. Поскольку может иметь место относительно большое число устройств для включения в первом генераторе 106-1 адресов и кодировщике 112 памяти, входной управляющий сигнал 114 будет подвержен высокой нагрузке, если отдельные сигнальные пути 116-1 и 116-2 не предусмотрены для обеспечения изоляции сигнальной нагрузки.

[0028] Кроме того, входной управляющий сигнал 114 используют для включения устройств в первом генераторе 106-1 адресов и в кодировщике 112 памяти по существу в одно и то же время, что будет дополнительно обострять влияния высокой нагрузки входного управляющего сигнала 114. Включение устройств «по существу в одно и то же время» может относиться к включению устройств одновременно или в пределах точно определенного временного диапазона друг за другом.

[0029] Второй генератор 106-2 адресов реагирует на входной управляющий сигнал 114, проходящий по сигнальному пути 116-X, выполняя задачу в первом генераторе 106-2 адресов, которая отличается от задачи в ответ на входной управляющий сигнал 114 в первом генераторе 106-1 адресов и в кодировщике 112 памяти. Сигнальный путь 116-X может представлять собой то же, что и сигнальный путь 116-2, или альтернативно сигнальный путь 116-X может отличаться от сигнального пути 116-2, так что сигнальную нагрузку сигнального пути 116-X изолируют от сигнальной нагрузки сигнального пути 116-2. Входной управляющий сигнал 114, поданный на второй генератор 106-2 адресов и на кодировщик 112 памяти, может совместно использовать общий сигнальный путь, поскольку число устройств во втором генераторе 106-2 адресов и кодировщике 112 памяти, на которые направляют входной управляющий сигнал 114, не будет вызывать чрезмерную нагрузку.

[0030] В некоторых примерах задача, выполняемая во втором генераторе 106-2 адресов в ответ на входной управляющий сигнал 114, может включать предварительную зарядку узлов во втором генераторе 106-2 адресов. Предварительная зарядка узла может относиться к зарядке узла до точно определенного напряжения. В целом предварительная зарядка узла менее чувствительна к влияниям сигнальной нагрузки, чем включение устройства, которое основано на высокоскоростной работе на высоких частотах.

[0031] В других примерах задача, выполняемая во втором генераторе 106-2 адресов в ответ на входной управляющий сигнал 114, включает в себя включение устройств (таких как транзисторы) во втором генераторе 106-2 адресов в другой момент времени, нежели включение устройства в первом генераторе 106-1 адресов или кодировщике 112 памяти. Включение устройства в соответствии с привязкой по времени сигналов может относиться ко включению устройства на основе сигнала, осуществляющего переход (переходы от низкого к высокому и от высокого к низкому) в конкретные моменты времени. В более общем смысле второй генератор 106-2 адресов может выполнять задачу в ответ на входной управляющий сигнал 114 в соответствии с другой привязкой по времени, нежели задача, выполняемая первым генератором 106-1 адресов.

[0032] На фиг. 2 представлена блок-схема примерного печатного картриджа 200 с текучей средой (такого как чернильный картридж) для использования в системе 2D-печати или системе 3D-печати. Несмотря на то, что показан печатный картридж с текучей средой, следует отметить, что компоненты, изображенные на фиг. 2, можно модифицировать для включения в непечатные применения.

[0033] TAB-узел 202 головки (ленточный носитель) можно прикреплять к поверхности (или поверхностям) печатного картриджа 200 с текучей средой. TAB-узел 202 головки содержит гибкий кабель 203, на котором может быть предусмотрена печатающая головка 204 (которая в примерах в соответствии с фиг. 2 представляет собой кристалл печатающей головки), электропроводящие площадки 206 и другой компонент(ы) (не показано). В дополнительных примерах в качестве части TAB-узла 202 головки может быть предусмотрено несколько кристаллов печатающей головки. На фиг. 2 печатающая головка 204 представляет собой пример устройства 100 выброса текучей среды, показанного на фиг. 1. Гибкий кабель 203 содержит электрические проводники для электрического соединения компонентов TAB-узла 202 головки, в том числе печатающую головку 204, электропроводящие площадки 206 и другой компонент(ы).

[0034] На фиг. 2 представлен пример интегрированной печатающей головки, которая является частью печатного картриджа 200 с текучей средой. С интегрированной печатающей головкой кристалл печатающей головки прикрепляют к печатному картриджу 200 с текучей средой. Печатный картридж 200 с текучей средой съемным образом устанавливают в системе печати; например, печатный картридж с текучей средой можно удалять из системы печати и заменять новым печатным картриджем с текучей средой. Когда печатный картридж 200 с текучей средой устанавливают в гнездо или другой приемник в каретке системы печати, электропроводящие площадки 206 образуют электрический контакт с соответствующими электрическими конструкциями каретки с тем, чтобы система печати могла сообщаться с и управлять печатным картриджем 200 с текучей средой, содержащим печатающую головку 204.

[0035] Печатающая головка 204 содержит контроллер 210, который содержит несколько селекторов 212-1 - 212-N (N > 2). Селекторы 212-1 - 212-N используют для выбора соответствующих сопел 102 печатающей головки 204 для активации. В некоторых примерах селекторы 212-1 и 212-N могут быть генераторами адресов, такими как генераторы 106-1 и 106-2 адресов, изображенные на фиг. 1.

[0036] Контроллер 210 также содержит память 110 и кодировщик 112 памяти, как рассмотрено выше. Кроме того, изоляции сигнальной нагрузки для входного управляющего сигнала 220 можно достичь путем предоставления отдельных сигнальных путей 222, по которым входной управляющий сигнал 220 проходит к селекторам 212-1 и 212-N и кодировщику 112 памяти. Отдельные сигнальные пути 222 могут быть схожи с сигнальными путями 116-1, 116-X и 116-2 на фиг. 1.

[0037] В других примерах печатающую головку 204 можно устанавливать на каретку системы печати, такой как система 2D- или 3D-печати.

[0038] На фиг. 3A-3D изображены примеры отдельных сигнальных путей, которые можно использовать. На каждой из фиг. 3A, 3C и 3D допускается, что селектором 212-1, селектором 212-N и кодировщиком 112 памяти совместно используются два входных управляющих сигнала S2 и S4. В других примерах селектором 212-1, селектором 212-N и кодировщиком 112 памяти могут совместно использоваться больше входных управляющих сигналов.

[0039] На фиг. 3A два отдельных сигнальных пути содержат первый сигнальный путь, который содержит первую цепь 302 делителя напряжения, и второй сигнальный путь, который содержит вторую цепь 304 делителя напряжения. Каждая цепь 302 или 304 делителя напряжения содержит делитель напряжения для входного управляющего сигнала S2 и другой делитель напряжения для входного управляющего сигнала S4.

[0040] Пример делителя напряжения представлен на фиг. 3B, где делитель напряжения содержит резисторы 306 и 308, расположенные последовательно между входным управляющим сигналом S (например, S2 или S4) и опорным напряжением (например, землей). Узел между резисторами 306 и 308 обеспечивает вариант более низкого напряжения, SLV, входного управляющего сигнала S. Уровень напряжения SLV основан на уровне напряжения S, умноженном на отношение сопротивления резистора 306 к сопротивлению резистора 308.

[0041] В каждой цепи 302 или 304 делителя напряжения на фиг. 3A могут быть предусмотрены два из делителей напряжения, представленных на фиг. 3B, один для S2 и один для S4. Цепь 302 делителя напряжения производит S2LV-1 из S2 (где S2LV-1 представляет собой вариант более низкого напряжения S2) и S4LV-1 из S4 (где S4LV-1 представляет собой вариант более низкого напряжения S4). Цепь 304 делителя напряжения производит S2LV-N из S2 (где S2LV-N представляет собой вариант более низкого напряжения S2) и S4LV-N из S4 (где S4LV-N представляет собой вариант более низкого напряжения S4).

[0042] На фиг. 3A каждый из входных управляющих сигналов S2 и S4 подают по первому сигнальному пути (который содержит цепь 302 делителя напряжения) на селектор 212-1. Выходные сигналы S2LV-1 и S4LV-1 от цепи 302 делителя напряжения подают на селектор 212-1.

[0043] Каждый из входных управляющих сигналов S2 и S4 подают по второму сигнальному пути (который содержит цепь 304 делителя напряжения) на селектор 212-N и декодировщик 112 памяти. Выходные сигналы S2LV-N и S4LV-N от цепи 302 делителя напряжения подают на селектор 212-N и декодировщик 112 памяти. В некоторых примерах сигнал S2LV-1 используют для включения транзисторов в селекторе 212-1, а сигнал S2LV-N для включения транзисторов в декодировщике 112 памяти. Сигнал S2LV-N предназначен для побуждения селектора 212-N осуществлять задачу, которая отличается от задачи, выполняемой в селекторе 212-1 в ответ на сигнал S2LV-1.

[0044] На фиг. 3C показана вариация компоновки, показанной на фиг. 3A. На фиг. 3C входной управляющий сигнал S2 проходит по первому сигнальному пути (включающему в себя цепь 302 делителя напряжения) к селектору 212-1 и по второму сигнальному пути (включающему в себя цепь 304 делителя напряжения) к селектору 212-N и декодировщику 112 памяти. Входной управляющий сигнал S4 проходит по первому сигнальному пути (включающему в себя цепь 302 делителя напряжения) к селектору 212-1 и декодировщику 112 памяти и входной управляющий сигнал S4 проходит по второму сигнальному пути (включающему цепь 304 делителя напряжения) к селектору 212-N.

[0045] На фиг. 3D изображен другая примерная компоновка, которая содержит другую цепь 306 делителя напряжения в дополнение к цепям 302 и 304 делителя напряжения. На фиг. 3D входные управляющие сигналы S2 и S4 подают по трем сигнальным путям (включающим в себя делители напряжения 302, 304 и 306, соответственно) к селектору 212-1, 212-N и декодировщику 112 памяти, соответственно. Другими словами, на фиг. 3D каждый сигнал S2 или S4 проходит по соответствующему отдельному сигнальному пути к каждому из селектора 212-1, селектора 212-N и декодировщика 112 памяти.

[0046] В дополнительных примерах вместо использования различных делителей напряжения для обеспечения отдельных сигнальных путей, можно использовать другую схему. Например, можно использовать несколько формирователей сигнала (драйверов), где каждый формирователь сигнала выводит входной управляющий сигнал в различных вариантах. В качестве еще одного примера для подачи входного управляющего сигнала в различных вариантах можно использовать несколько контактных площадок.

[0047] На фиг. 4 представлена блок-схема конкретного примера компоновки, которую можно использовать в обсужденных выше контроллере 104 или контроллере 210. На фиг. 4 каждый из селекторов 212-1 и 212-N и декодировщик 112 памяти содержит сдвиговый регистр, который используют для сдвига входных сигналов в выходные сигналы. Селектор 212-1 содержит сдвиговый регистр 402-1, селектор 212-N содержит сдвиговый регистр 402-N и кодировщик 112 памяти содержит сдвиговые регистры 404-1, 404-2 и 404-3. Несмотря на то, что конкретное число сдвиговых регистров показано в качестве включенных в каждый из селекторов 212-1, 212-N и кодировщика 112 памяти, в других примерах можно использовать другое число сдвиговых регистров. Также следует отметить, что каждый из селекторов 212-1, 212-N и кодировщика 112 памяти может содержать дополнительную схему в дополнение к соответствующему сдвиговому регистру(ам).

[0048] Каждый сдвиговый регистр 402-1, 402-N, 404-1, 404-2 или 404-3 содержит серию ячеек сдвигового регистра, которую можно реализовать в виде триггеров или других запоминающих элементов, которые могут сохранять свои значения до следующего выбора запоминающих элементов. Выходной сигнал одной ячейки сдвигового регистра в упомянутой серии можно подавать на вход следующей ячейки сдвигового регистра для осуществления сдвига данных через сдвиговый регистр.

[0049] Входные управляющие сигналы 406 подают по сигнальным путям 408-1, 408-X и 408-2, управляя сдвигами битов данных в сдвиговых регистрах 402-1, 402-N и 404-1, 404-2, 404-3. Сигнальные пути 408-1, 408-X и 408-2 могут обеспечивать изоляцию сигнальной нагрузки подобно схеме, обсужденной выше в связи с фиг. 1, 2, и 3A-3D.

[0050] На фиг. 5 представлен пример ячейки 500 сдвигового регистра, которую можно использовать в сдвиговых регистрах на фиг. 4. Ряд ячеек 500 сдвигового регистра можно соединять последовательно, формируя сдвиговый регистр. Ячейка 500 сдвигового регистра содержит первый каскад и второй каскад. В первом каскаде сигнал PRE-1 используют для предварительной зарядки внутреннего узла N1 через транзистор 502 в ответ на высокоимпульсный сигнал PRE-1. Кроме того, после предварительной зарядки внутреннего узла N1 с помощью сигнала PRE-1, подают высокоимпульсный сигнал выбора SEL-1, включая транзистор 504, который заставляет узел N1 оставаться заряженным или разряжаться, в зависимости от уровня входного сигнала SI на дополнительные цепи 506 ячейки 500 сдвигового регистра.

[0051] Во втором каскаде сигнал PRE-2 используют для предварительной зарядки выходного узла SO через транзистор 508 в ответ на высокоимпульсный сигнал PRE-2. После предварительной зарядки выхода SO сдвигового регистра, сигнал SEL-2 выбора можно использовать для включения транзистора 510, а выход сдвигового регистра либо разряжают, либо сохраняют заряженным, в зависимости от состояния узла N1, который управляет транзистором 512.

[0052] Сигналы PRE-1, SEL-1, PRE-2 и SEL-2 являются примерами входных управляющих сигналов 406, показанных на фиг. 4. Кроме того, в некоторых примерах входной управляющий сигнал 114 по фиг. 1 или входной управляющий сигнал 220 по фиг. 2 может представлять собой либо сигнал SEL-1, либо сигнал SEL-2.

[0053] На фиг. 6 представлена блок-схема примерной компоновки, которая содержит управляющую цепь 600. Управляющая цепь 600 может быть частью контроллера 104, показанного на фиг. 1, контроллера 210, показанного на фиг. 2, или другой управляющей цепью. Управляющая цепь 600 содержит селекторы 212-1 - 212-N, подобные селекторам контроллера 210 на фиг. 2. Кроме того, управляющая цепь 600 содержит память 110 и кодировщик 112 памяти, подобные памяти 110 в кодировщике 112 памяти, которые изображены на фиг. 1.

[0054] Селекторы 212-1 - 212-N находятся под управлением входного управляющего сигнала 114, создавая сигналы для выбора соответствующих сопел устройства выброса текучей среды. Первый селектор 212-1 реагирует на входной управляющий сигнал 114, проходящий по первому сигнальному пути 116-1, включая устройство в первом селекторе 212-1, а второй селектор 212-N реагирует на входной управляющий сигнал 114, проходящий по сигнальному пути 116-X, осуществляя другую задачу, нежели включение устройства в первом селекторе 212-1.

[0055] Кодировщик 112 памяти реагирует на входной управляющий сигнал 114, проходящий по второму сигнальному пути 116-2, включая устройство в кодировщике 112 памяти, причем сигнальная нагрузка второго сигнального пути 116-2 изолирована от сигнальной нагрузки первого сигнального пути 116-1.

[0056] На фиг. 7 представлена блок-схема последовательности операций примерного процесса управления устройством выброса текучей среды. Процесс включает управление (на этапе 702) несколькими селекторами с использованием входного управляющего сигнала для создания сигналов для выбора соответствующих сопел устройства выброса текучей среды, причем первый селектор реагирует на входной управляющий сигнал, проходящий по первому сигнальному пути, включая транзистор в первом селекторе, а второй селектор реагирует на входной управляющий сигнал, осуществляя задачу, которая отличается от включения транзистора.

[0057] Процесс дополнительно включает, в ответ на входной управляющий сигнал, проходящий по второму сигнальному пути с включением транзистора в сдвиговом регистре, вывод (на этапе 704) с помощью сдвигового регистра сигнала для выбора ячейки памяти в памяти, причем сигнальная нагрузка второго сигнального пути изолирована от сигнальной нагрузки первого сигнального пути.

[0058] В вышеприведенном описании многие подробности изложены для обеспечения понимания раскрытого здесь предмета изобретения. Однако реализации можно осуществлять на практике без некоторых из этих подробностей. Другие реализации могут включать модификации и вариации рассмотренных выше деталей. Подразумевается, что приложенная формула изобретения покрывает такие модификации и вариации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВА ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ, ВКЛЮЧАЮЩИЕ В СЕБЯ ПЕРВУЮ ПАМЯТЬ И ВТОРУЮ ПАМЯТЬ | 2019 |

|

RU2779068C1 |

| СЕЛЕКТОРЫ ДЛЯ ФОРСУНОК И ЭЛЕМЕНТОВ ПАМЯТИ | 2017 |

|

RU2747446C1 |

| ИНТЕГРАЛЬНЫЕ СХЕМЫ, ВКЛЮЧАЮЩИЕ В СЕБЯ ЗАПОМИНАЮЩИЕ ЯЧЕЙКИ | 2019 |

|

RU2779793C1 |

| СИСТЕМА И СПОСОБ ПЕЧАТИ ИЗОБРАЖЕНИЯ НА ПОВЕРХНОСТИ | 2016 |

|

RU2648201C2 |

| ПЕЧАТАЮЩИЕ ГОЛОВКИ С ИЗМЕРЕНИЕМ ИМПЕДАНСА СЕНСОРНОЙ ПЛАСТИНЫ | 2014 |

|

RU2654178C2 |

| ДАТЧИК УРОВНЯ ТЕКУЧЕЙ СРЕДЫ И СВЯЗАННЫЕ С НИМ СПОСОБЫ | 2011 |

|

RU2572766C2 |

| УСТРОЙСТВО ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ СО ВСТРОЕННЫМ ДАТЧИКОМ УРОВНЯ ЧЕРНИЛ | 2012 |

|

RU2635080C2 |

| ДОСТУП К БЛОКАМ ПАМЯТИ В БАНКЕ ПАМЯТИ | 2017 |

|

RU2748727C2 |

| ИНДИКАТОР ЗАПОЛНЕНИЯ ПЕЧАТАЮЩЕГО КОНТЕЙНЕРА | 2006 |

|

RU2397873C2 |

| ДАТЧИК УРОВНЯ ЧЕРНИЛ И ОТНОСЯЩИЕСЯ К НЕМУ СПОСОБЫ | 2011 |

|

RU2561029C1 |

Устройство управления для устройства выброса текучей среды содержит множество селекторов, управляемых входным управляющим сигналом, для формирования сигналов для выбора соответствующих сопел устройства выброса текучей среды, причем первый селектор реагирует на входной управляющий сигнал, проходящий по первому сигнальному пути, включая устройство в первом селекторе, а второй селектор реагирует на входной управляющий сигнал, выполняя другую задачу. Кодировщик памяти предназначен для выбора ячейки памяти в памяти, причем кодировщик памяти реагирует на входной управляющий сигнал, проходящий по второму сигнальному пути, включая устройство в кодировщике памяти, при этом сигнальная нагрузка второго сигнального пути изолирована от сигнальной нагрузки первого сигнального пути. 3 н. и 11 з.п. ф-лы, 7 ил.

1. Устройство управления для устройства (100) выброса текучей среды, содержащее:

множество селекторов (212-1, 212-N), управляемых входным управляющим сигналом (114, 220, 406), чтобы формировать сигналы для выбора соответствующих сопел (102) устройства (100) выброса текучей среды, причем множество селекторов (212-1, 212-N) содержит множество генераторов (106-1, 106-2) адресов, чтобы генерировать адреса для выбора соответствующих сопел (102), первый селектор (212-1) из множества селекторов (212-1, 212-N) реагирует на входной управляющий сигнал (114, 220, 406), проходящий по первому сигнальному пути (116-1, 408-1), включая устройство в первом селекторе (212-1), а второй селектор (212-N) из множества селекторов (212-1, 212-N) реагирует на входной управляющий сигнал (114, 220, 406), предварительно заряжая узел во втором генераторе (106-2) адресов;

память (110); и

кодировщик (112) памяти для выбора ячейки памяти в памяти, причем кодировщик (112) памяти реагирует на входной управляющий сигнал (114, 220, 406), проходящий по второму сигнальному пути (116-2, 408-2), включая устройство в кодировщике (112) памяти, причем входной управляющий сигнал (114, 220, 406) используется для включения устройств в первом генераторе (106-1) адресов и в кодировщике (112) памяти по существу в одно и то же время, при этом сигнальная нагрузка второго сигнального пути (116-2, 408-2) изолирована от сигнальной нагрузки первого сигнального пути (116-1, 408-1), при этом изоляция сигнальной нагрузки достигнута за счет обеспечения отдельных сигнальных путей (222), по которым входной управляющий сигнал (114, 220, 406) проходит на селекторы (212-1, 212-N) и кодировщик (112) памяти.

2. Устройство управления по п. 1, в котором устройство в первом селекторе (212-1), включаемое в ответ на входной управляющий сигнал (114, 220, 406), содержит транзистор и в котором устройство в кодировщике (112) памяти, включаемое в ответ на входной управляющий сигнал (114, 220, 406), содержит транзистор.

3. Устройство управления по п. 1, в котором первый сигнальный путь (116-1, 408-1) содержит первый делитель (302) напряжения для вывода сигнала (S2LV-1, S4LV-1), соответствующего входному управляющему сигналу (114, 220, 406), на первый селектор (212-1), а второй сигнальный путь (116-2, 408-2) содержит второй делитель (304) напряжения для вывода сигнала (S2LV-N, S4LV-N), соответствующего входному управляющему сигналу (114, 220, 406), на второй селектор (212-N) и на кодировщик (112) памяти.

4. Устройство управления по п. 1, в котором первый сигнальный путь (116-1, 408-1) содержит первый делитель (302) напряжения для вывода сигнала (S2LV-1, S4LV-1), соответствующего входному управляющему сигналу (114, 220, 406), на первый селектор (212-1), а второй сигнальный путь (116-2, 408-2) содержит второй делитель (304) напряжения для вывода сигнала (S2LV-N, S4LV-N), соответствующего входному управляющему сигналу (114, 220, 406), на кодировщик (112) памяти.

5. Устройство управления по п. 1, в котором первый сигнальный путь (116-1, 408-1) содержит первый делитель (302) напряжения для вывода сигнала (S2LV-1, S4LV-1), соответствующего входному управляющему сигналу (114, 220, 406), на первый селектор (212-1) и на кодировщик (112) памяти, а второй сигнальный путь (116-2, 408-2) содержит второй делитель (304) напряжения для вывода сигнала (S2LV-N, S4LV-N), соответствующего входному управляющему сигналу (114, 220, 406), на второй селектор (212-N) и на кодировщик (112) памяти.

6. Устройство управления по п. 1, в котором первый сигнальный путь (116-1, 408-1) содержит первый делитель (302) напряжения для вывода сигнала (S2LV-1, S4LV-1), соответствующего входному управляющему сигналу (114, 220, 406), на первый селектор (212-1), а второй сигнальный путь (116-2, 408-2) содержит второй делитель (306) напряжения для вывода сигнала (S2LV-3, S4LV-3), соответствующего входному управляющему сигналу (114, 220, 406), на кодировщик (112) памяти, причем устройство управления дополнительно содержит:

третий сигнальный путь (116-X), содержащий третий делитель (304) напряжения для вывода сигнала (S2LV-N, S4LV-N), соответствующего входному управляющему сигналу (114, 220, 406), на второй селектор (212-N).

7. Устройство управления по п. 1, в котором кодировщик (112) памяти содержит сдвиговый регистр (404-1, 404-2, 404-3) для осуществления сдвига сигнала доступа к памяти за счет множества ячеек (500) сдвигового регистра (404-1, 404-2, 404-3) с выводом сигнала для выбора ячейки памяти в памяти (110).

8. Устройство управления по п. 7, в котором сдвиговый регистр (404-1, 404-2, 404-3) реагирует на входной управляющий сигнал (114, 220, 406), проходящий по второму сигнальному пути (116-2, 408-2), включая множество устройств в сдвиговом регистре (404-1, 404-2, 404-3).

9. Устройство управления по п. 8, в котором множество устройств в сдвиговом регистре (404-1, 404-2, 404-3) содержит множество транзисторов, которые включаются в ответ на входной управляющий сигнал (114, 220, 406).

10. Устройство (100) выброса текучей среды, содержащее:

множество сопел (102) для доставки текучей среды во время работы системы; и

контроллер (104, 210), содержащий:

множество генераторов (106-1, 106-2) адресов, управляемых входным управляющим сигналом (114, 220, 406), чтобы получать адреса для выбора соответствующих сопел (102) из множества сопел (102), причем первый генератор (106-1) адресов из множества генераторов (106-1, 106-2) адресов реагирует на входной управляющий сигнал (114, 220, 406), проходящий по первому сигнальному пути (116-1, 408-1), включая устройство в первом генераторе (106-1) адресов в соответствии с первой привязкой по времени, а второй генератор (106-2) адресов из множества генераторов (106-1, 106-2) адресов реагирует на входной управляющий сигнал (114, 220, 406), выполняя задачу во втором генераторе адресов (106-2) в соответствии со второй отличающейся привязкой по времени, при этом задача содержит по меньшей мере одно из включения устройства и предварительной зарядки узла;

память (110); и

кодировщик (112) памяти для выбора ячейки памяти в памяти (110), причем кодировщик (112) памяти реагирует на входной управляющий сигнал (114, 220, 406), проходящий по второму сигнальному пути (116-2, 408-2), включая устройство в кодировщике (112) памяти, причем входной управляющий сигнал (114, 220, 406) используется для включения устройств в первом генераторе (106-1) адресов и в кодировщике (112) памяти по существу в одно и то же время, при этом сигнальная нагрузка второго сигнального пути (116-2, 408-2) изолирована от сигнальной нагрузки первого сигнального пути (116-1, 408-1), при этом изоляция сигнальной нагрузки достигнута за счет обеспечения отдельных сигнальных путей (222), по которым входной управляющий сигнал (114, 220, 406) проходит на генераторы (106-1, 106-2) адресов и кодировщик (112) памяти.

11. Устройство выброса текучей среды по п. 10, в котором первый сигнальный путь (116-1, 408-1) содержит первый делитель (302) напряжения для вывода сигнала (S2LV-1, S4LV-1), соответствующего входному управляющему сигналу (114, 220, 406), на первый генератор (106-1) адресов, а второй сигнальный путь (116-2, 408-2) содержит второй делитель (304) напряжения для вывода сигнала (S2LV-N, S4LV-N), соответствующего входному управляющему сигналу (114, 220, 406), на второй генератор адресов.

12. Устройство выброса текучей среды по п. 10, содержащее кристалл печатающей головки, который содержит множество сопел (102) и контроллер (104, 210).

13. Способ, включающий:

управление множеством селекторов (212-1, 212-N) с использованием входного управляющего сигнала (114, 220, 406), чтобы формировать сигналы для выбора соответствующих сопел (102) устройства (100) выброса текучей среды, причем первый селектор (212-1) из множества селекторов (212-1, 212-N) реагирует на входной управляющий сигнал (114, 220, 406), проходящий по первому сигнальному пути (116-1, 408-1), включая транзистор в первом селекторе (212-1), а второй селектор (212-N) из множества селекторов (212-1, 212-N) реагирует на входной управляющий сигнал (114, 220, 406), проходящий по третьему сигнальному пути (116-Х, 408-X), включая устройство во втором селекторе (212-N) или предварительно заряжая узел во втором селекторе (212-N); и

вследствие реакции на входной управляющий сигнал (114, 220, 406), проходящий по второму сигнальному пути (116-2, 408-2), с включением транзистора в сдвиговом регистре (404-1, 404-2,404-3) кодировщика (112) памяти, вывод сдвиговым регистром (404-1, 404-2, 404-3) сигнала для выбора ячейки памяти в памяти (110), причем входной управляющий сигнал (114, 220, 406) используется для включения устройств в первом генераторе (106-1) адресов и в кодировщике (112) памяти по существу в одно и то же время, при этом сигнальная нагрузка второго сигнального пути (116-2, 408-2) изолирована от сигнальной нагрузки первого сигнального пути (116-1, 408-1), при этом изоляция сигнальной нагрузки достигнута за счет обеспечения отдельных сигнальных путей (222), по которым входной управляющий сигнал (114, 220, 406) проходит на селекторы (212-1, 212-N) и кодировщик (112) памяти.

14. Способ по п. 13, в котором второй сигнальный путь (116-2, 408-2) изолирован от сигнальной нагрузки первого сигнального пути (116-1, 408-1) за счет использования отдельных делителей (306, 304, 302) напряжения.

| US 6575548 B1, 10.06.2003 | |||

| US 6435668 B1, 20.08.2002 | |||

| EP 1029675 A2, 23.08.2000. |

Авторы

Даты

2020-01-09—Публикация

2016-10-06—Подача