ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

[0001] Система струйной печати в качестве одного примера системы выброса текучей среды может включать в себя печатающую головку, источник чернил, который подает жидкие чернила в печатающую головку, и электронный контроллер, который управляет печатающей головкой. Печатающая головка в качестве одного примера устройства выброса текучей среды выбрасывает капли чернил через множество сопел или дюз и к носителю печати, такому как лист бумаги, для печати на носителе печати. В некоторых примерах дюзы располагаются в по меньшей мере одном столбце или массиве, благодаря чему надлежащим образом упорядоченный выброс чернил из дюз позволяет печатать знаки или другие изображения на носителе печати, когда печатающая головка и носитель печати перемещаются относительно друг друга.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

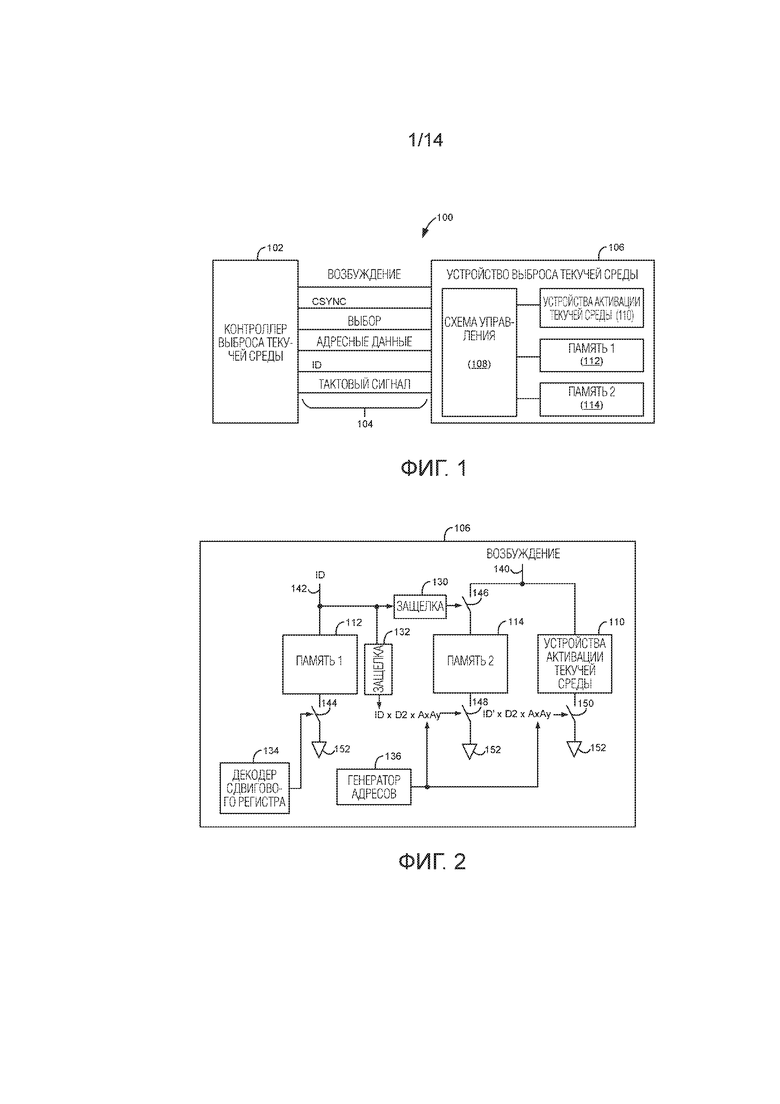

[0002] Фиг. 1 - блок-схема, иллюстрирующая один пример системы выброса текучей среды.

[0003] Фиг. 2 - примерная схема, иллюстрирующая один пример устройства выброса текучей среды.

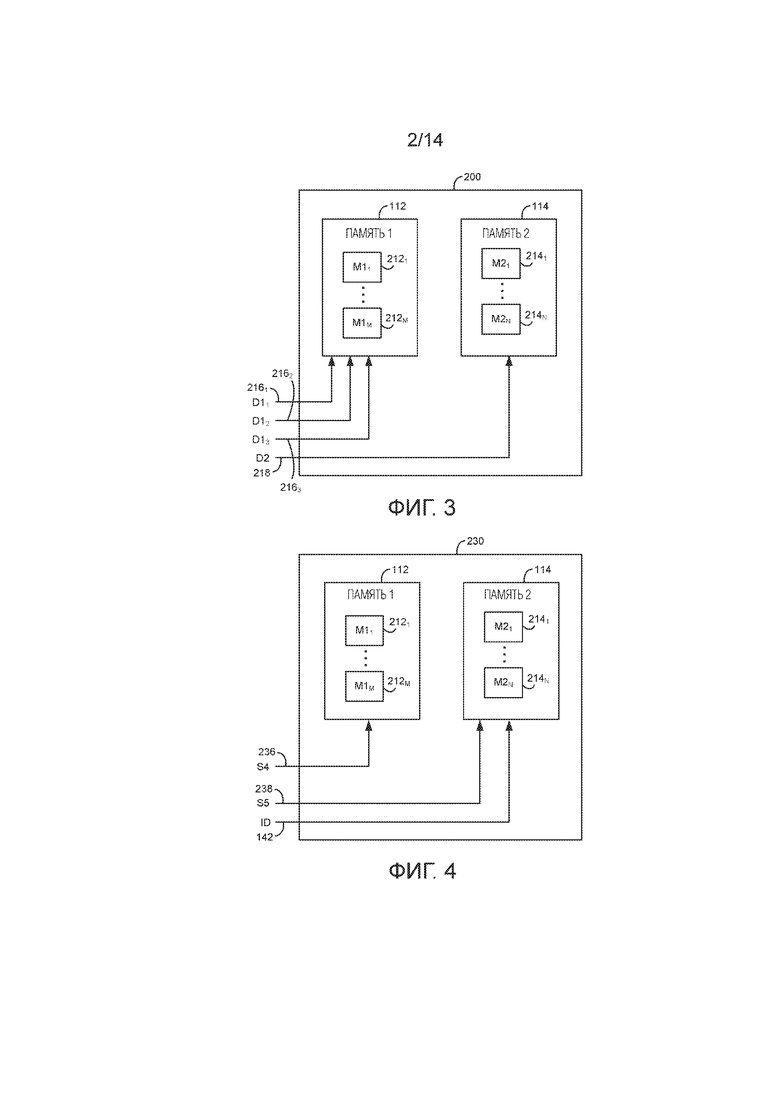

[0004] Фиг. 3 - блок-схема, иллюстрирующая один пример схемы (цепи), включающей в себя первую память и вторую память устройства выброса текучей среды.

[0005] Фиг. 4 - блок-схема, иллюстрирующая другой пример схемы, включающей в себя первую память и вторую память устройства выброса текучей среды.

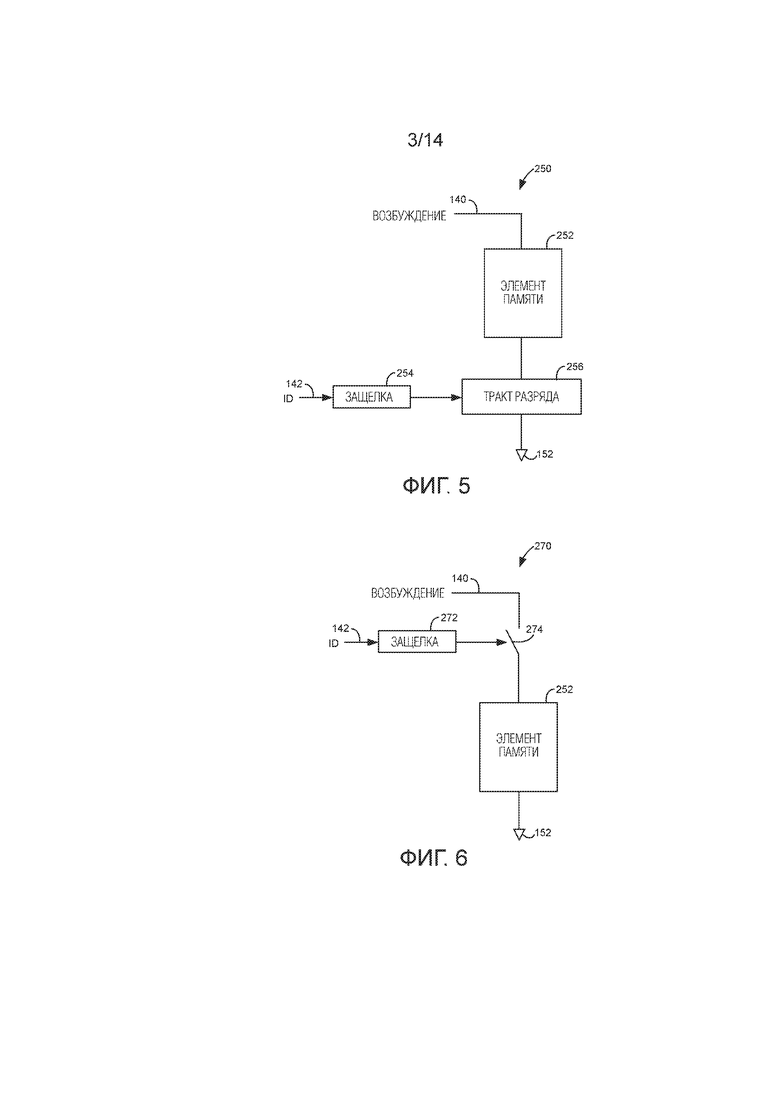

[0006] Фиг. 5 - примерная схема, иллюстрирующая один пример схемы, включающей в себя элемент памяти устройства выброса текучей среды.

[0007] Фиг. 6 - примерная схема, иллюстрирующая другой пример схемы, включающей в себя элемент памяти устройства выброса текучей среды.

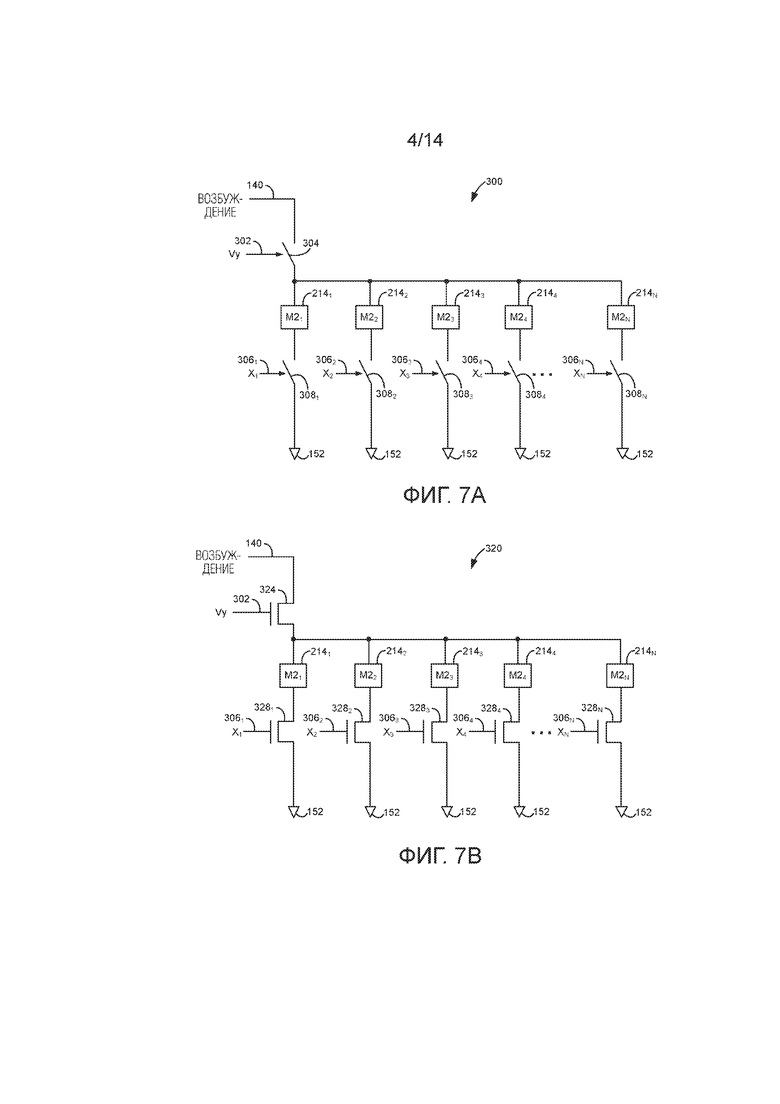

[0008] Фиг. 7A - примерная схема, иллюстрирующая один пример схемы, включающей в себя множество элементов памяти устройства выброса текучей среды.

[0009] Фиг. 7B - примерная схема, иллюстрирующая другой пример схемы, включающей в себя множество элементов памяти устройства выброса текучей среды.

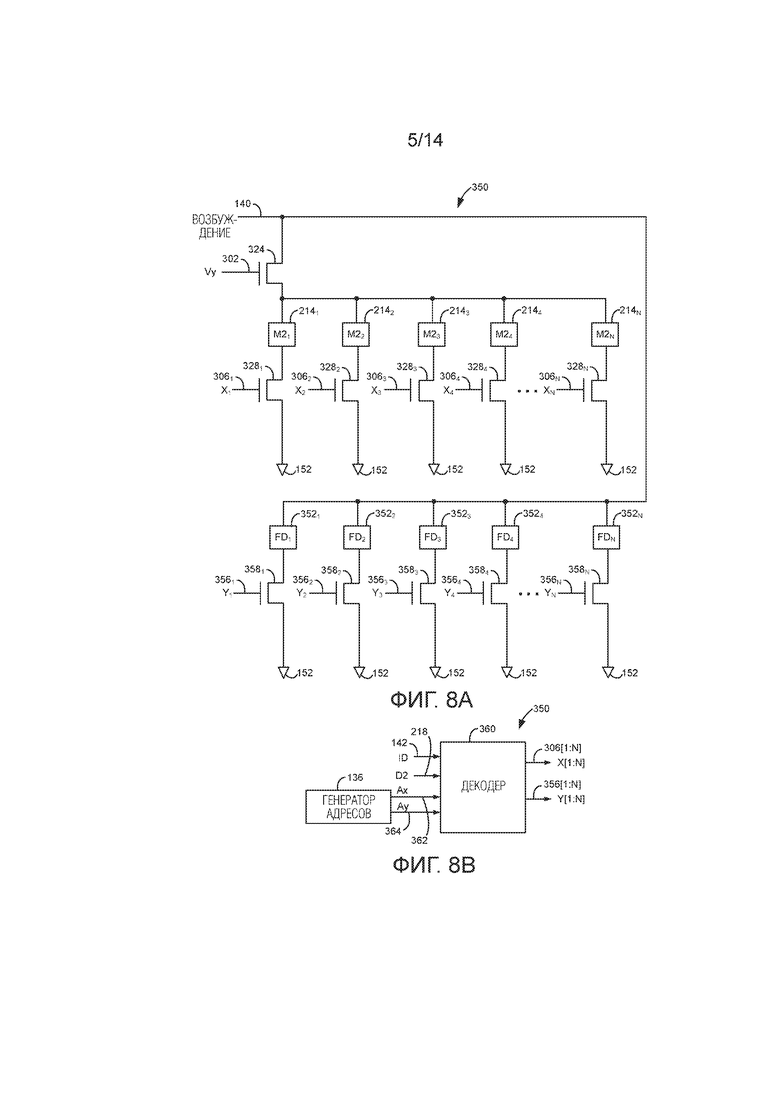

[0010] Фиг. 8A-8B - примерные схемы, иллюстрирующие один пример схемы, включающей в себя множество элементов памяти и множество устройств активации текучей среды устройства выброса текучей среды.

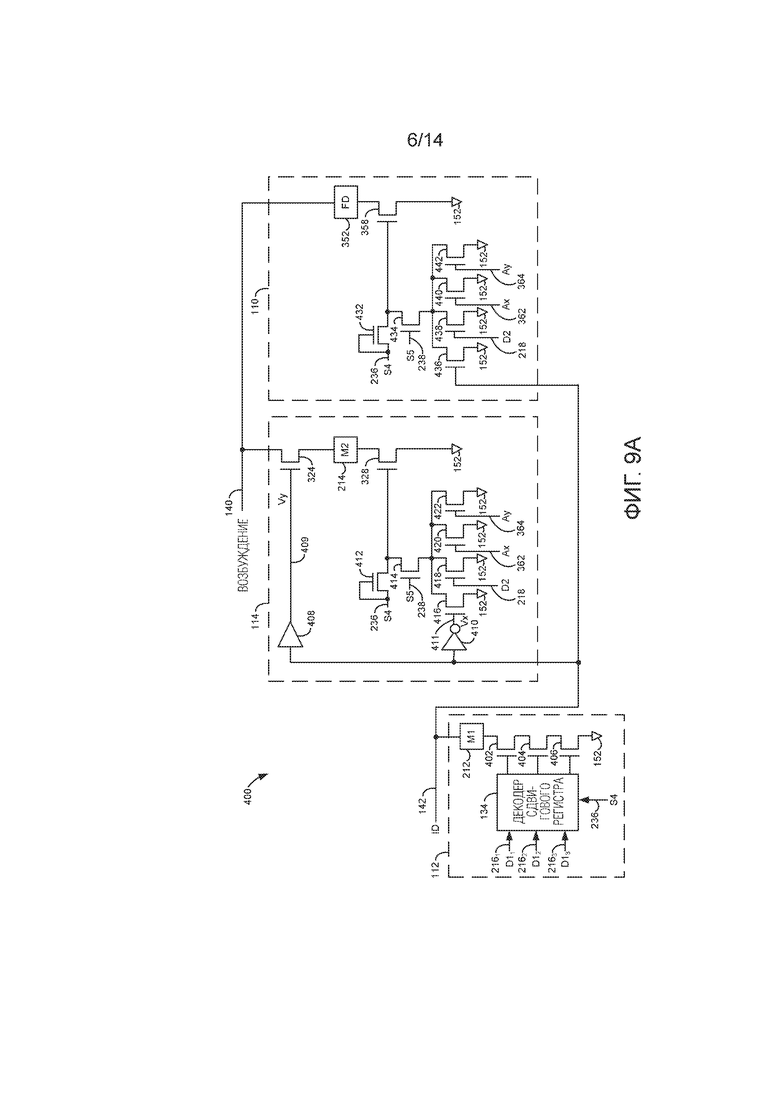

[0011] Фиг. 9A - примерная схема, иллюстрирующая один пример схемы, включающей в себя первую память, вторую память и устройства активации текучей среды.

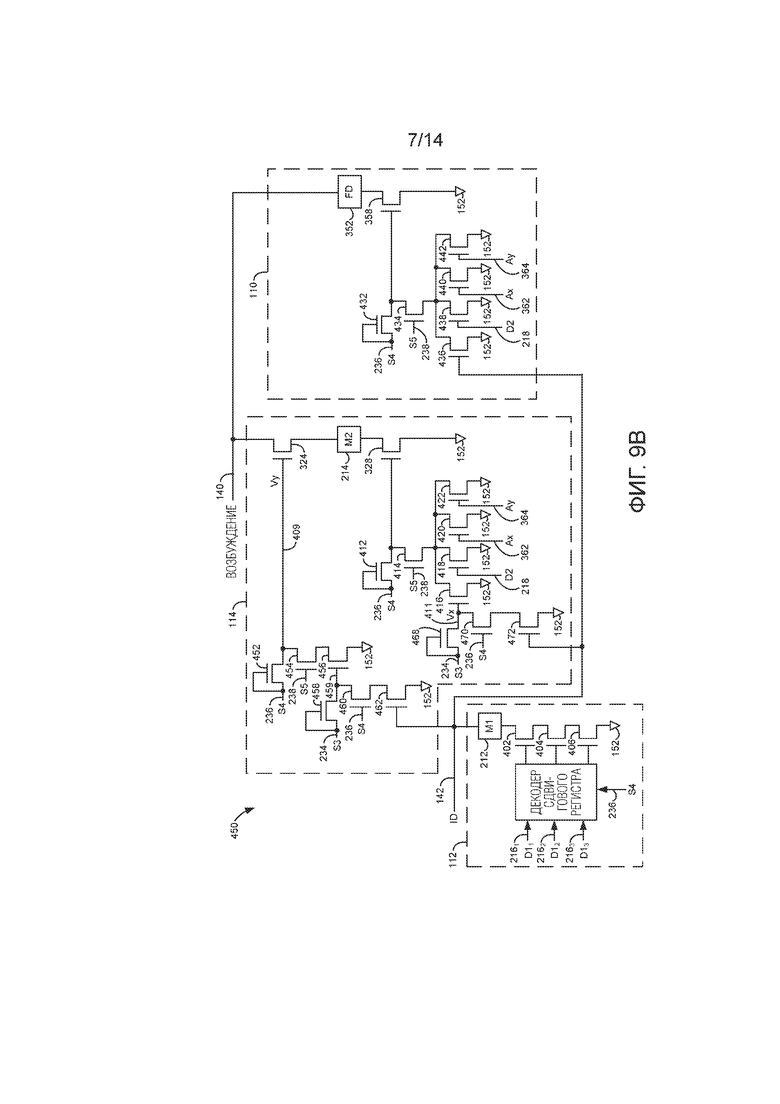

[0012] Фиг. 9B - примерная схема, иллюстрирующая другой пример схемы, включающей в себя первую память, вторую память и устройства активации текучей среды.

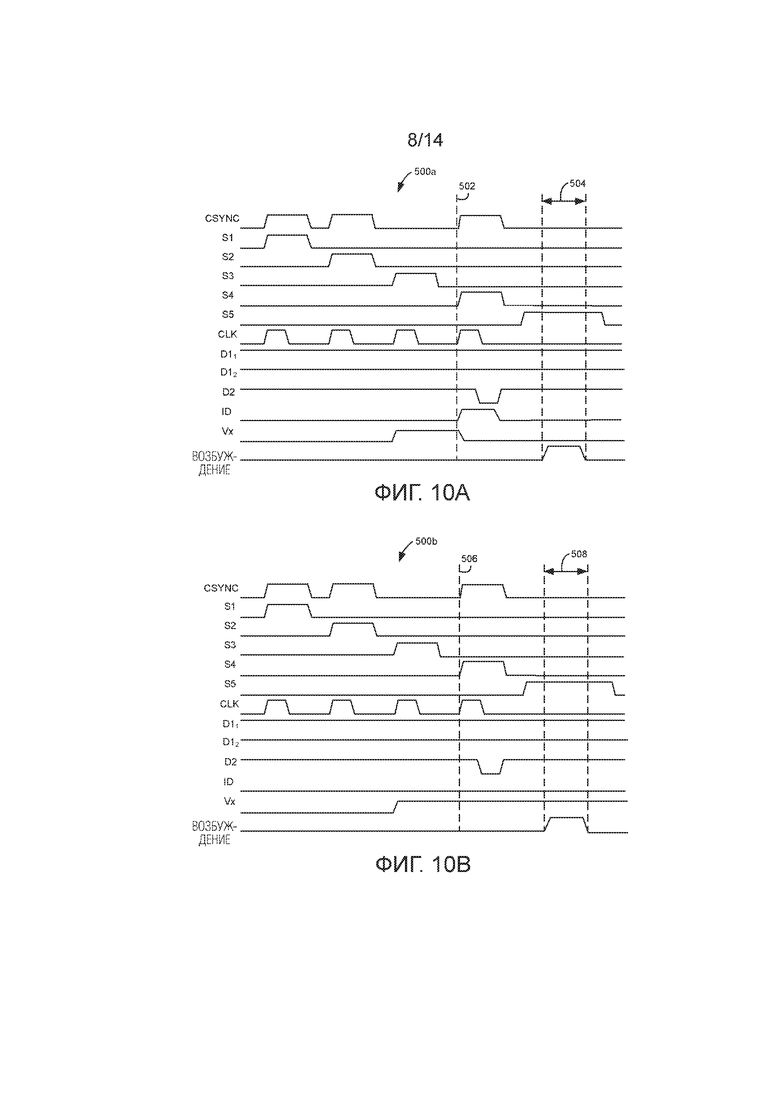

[0013] Фиг. 10A и 10B - временные диаграммы, иллюстрирующие один пример работы схемы по фиг. 9B.

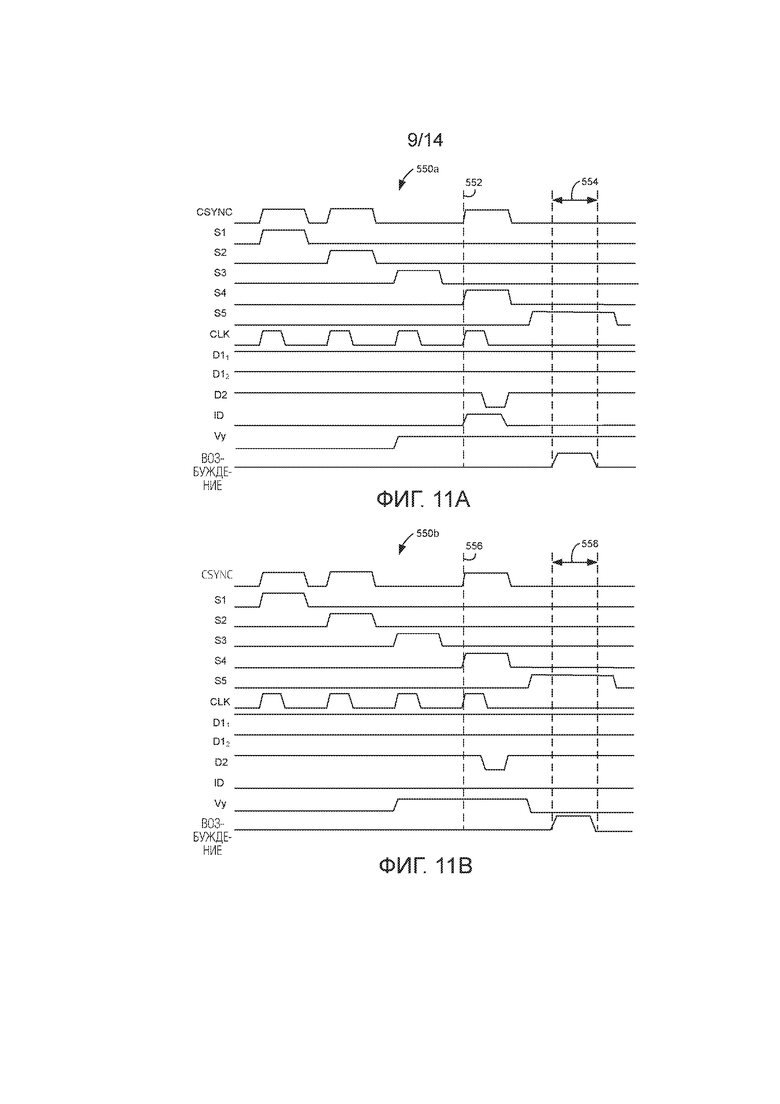

[0014] Фиг. 11A и 11B - временные диаграммы, иллюстрирующие другой пример работы схемы по фиг. 9B.

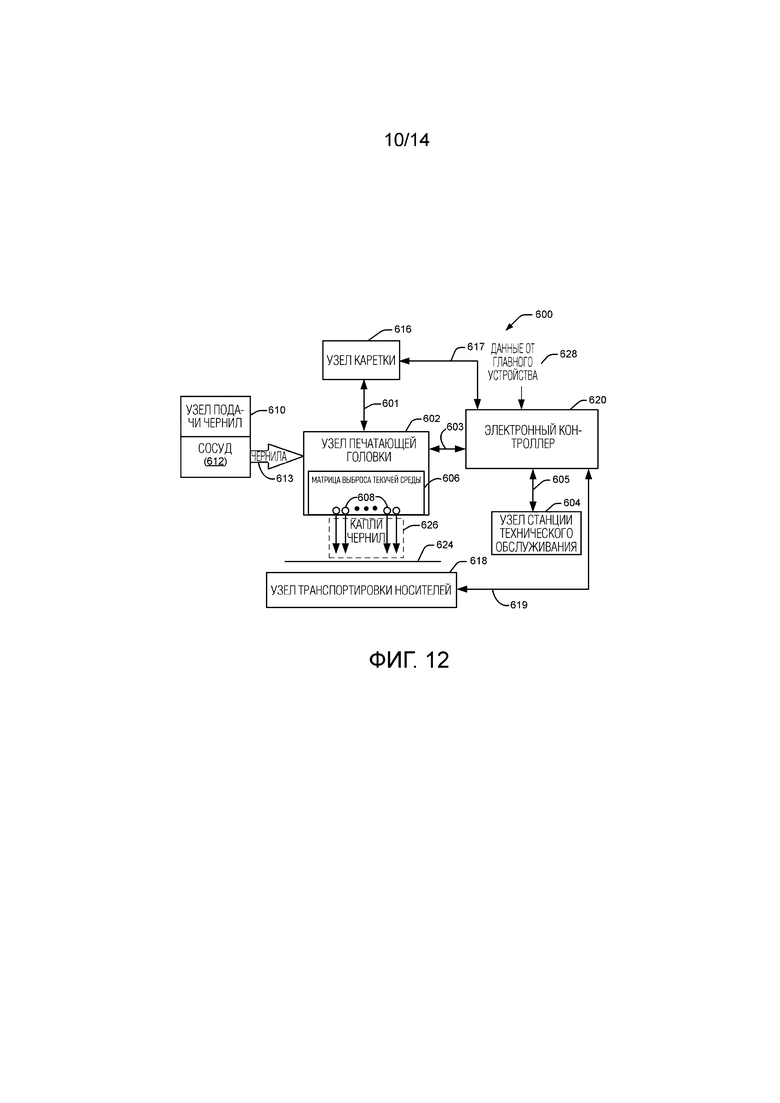

[0015] Фиг. 12 - блок-схема, иллюстрирующая один пример системы выброса текучей среды.

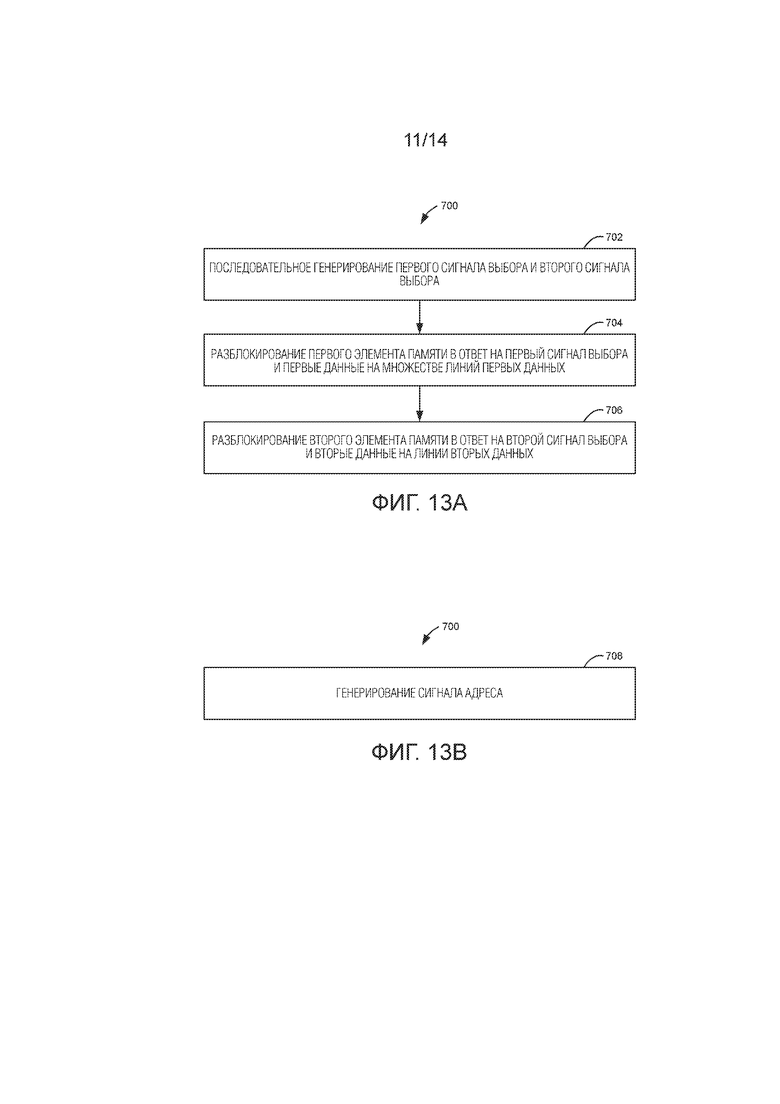

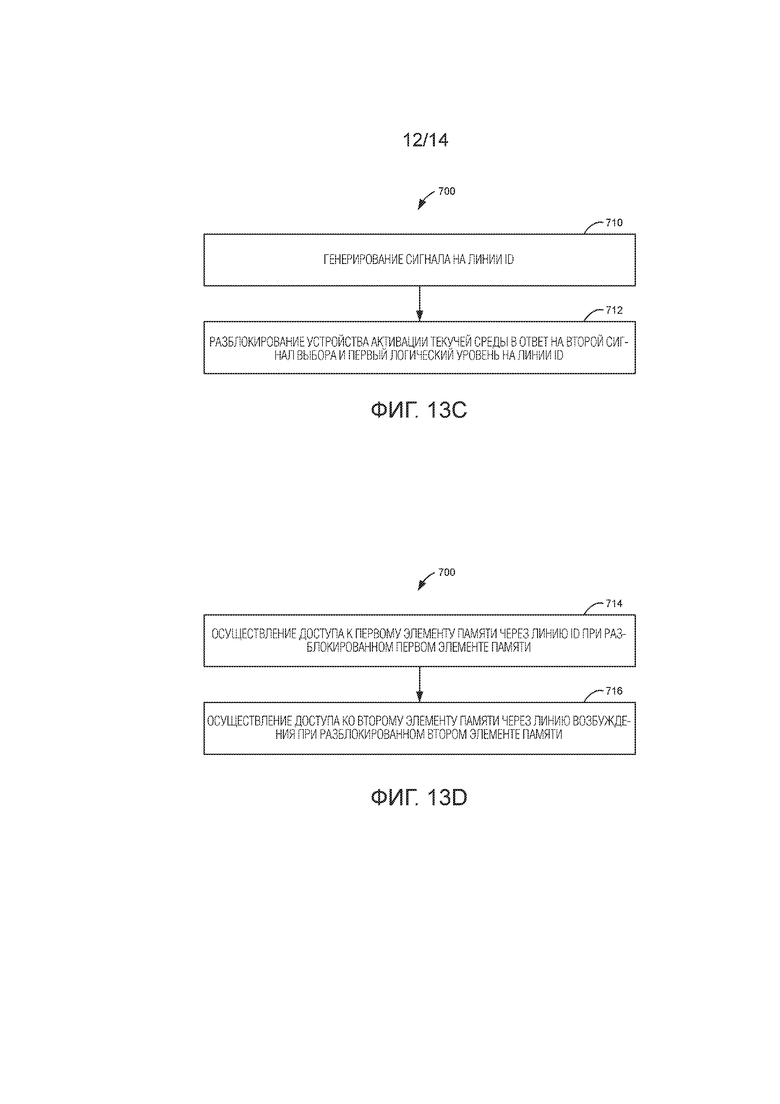

[0016] Фиг. 13A-13D - блок-схемы последовательности операций, иллюстрирующие один пример способа осуществления доступа к первой памяти и второй памяти устройства выброса текучей среды.

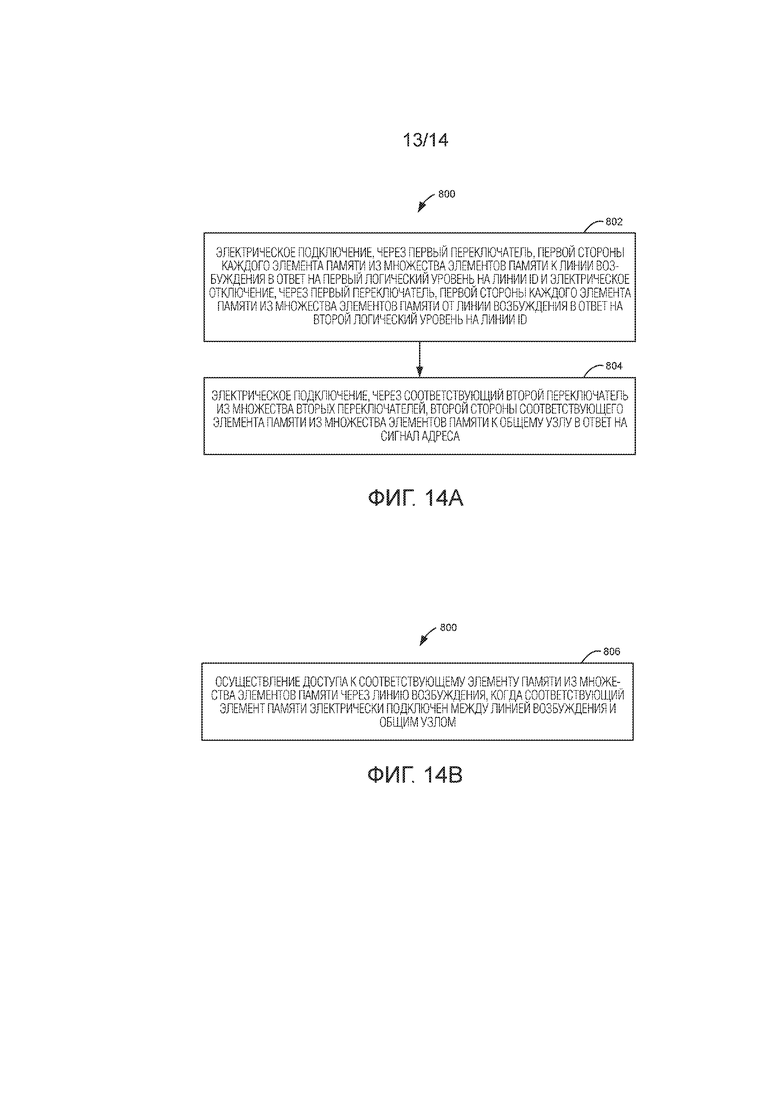

[0017] Фиг. 14A-14B - блок-схемы последовательности операций, иллюстрирующие один пример способа осуществления доступа к памяти устройства выброса текучей среды.

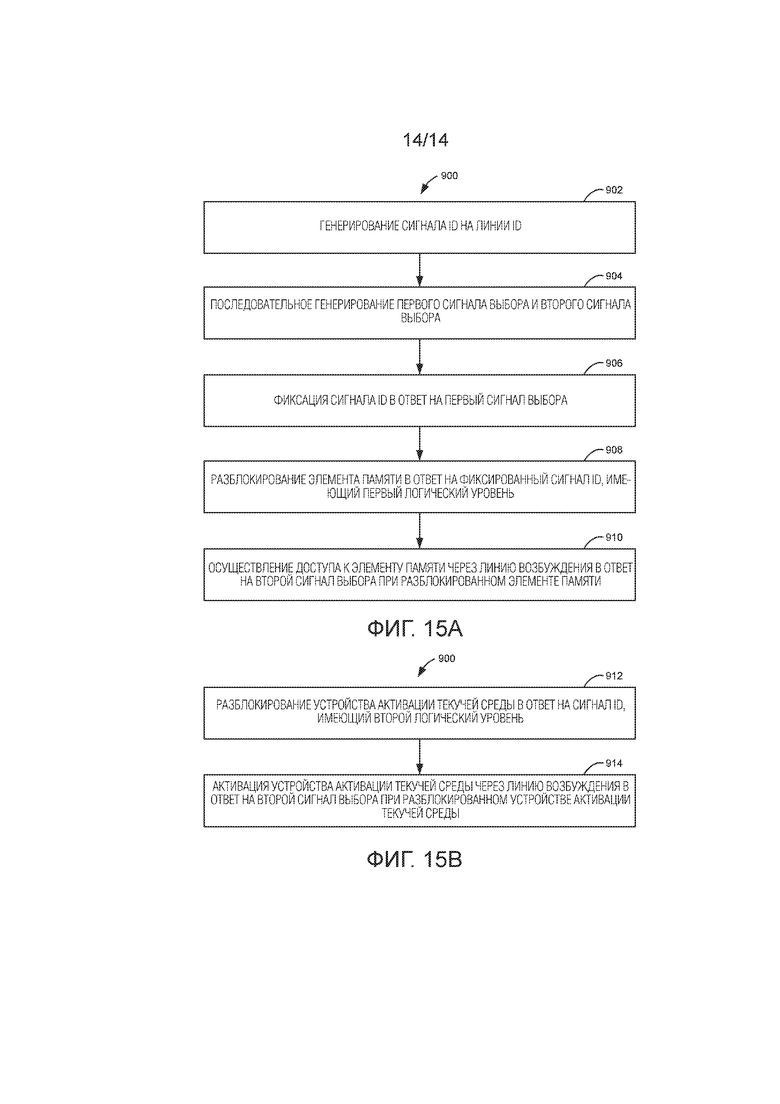

[0018] Фиг. 15A-15B - блок-схемы последовательности операций, иллюстрирующие другой пример способа осуществления доступа к памяти устройства выброса текучей среды.

ПОДРОБНОЕ ОПИСАНИЕ

[0019] В нижеследующем подробном описании выполнена ссылка на прилагаемые чертежи, которые составляют его часть, и на которых в порядке иллюстрации показаны конкретные примеры практической реализации раскрытия. Следует понимать, что можно использовать другие примеры и выполнять конструктивные или логические изменения, не выходя за рамки настоящего раскрытия. Поэтому нижеследующее подробное описание не следует рассматривать в ограничительном смысле, и объем настоящего раскрытия характеризуется прилагаемой формулой изобретения. Следует понимать, что признаки различных описанных здесь примеров можно комбинировать частично или полностью, если конкретно не указано иное.

[0020] Как использовано здесь, “логически высокий” сигнал представляет собой сигнал логической “1” или “включено” или сигнал, имеющий напряжение, примерно равное питанию логики, подаваемому на интегральную схему (например, от около 1,8 В до 15 В, такому как 5,6 В). Как использовано здесь, “логически низкий” сигнал представляет собой сигнал логического “0” или “выключено” или сигнал, имеющий напряжение, примерно равное заземлению питания логики для питания логики, подаваемого на интегральную схему (например, около 0 В).

[0021] Печатающая головка для использования в системе печати может включать в себя сопла, которые активируются, вызывая выброс капель текучей среды для печати из соответствующих сопел. Каждое сопло включает в себя устройство активации текучей среды. Устройства активации текучей среды, будучи активированы, вызывают выброс капель текучей среды для печати соответствующими соплами. В одном примере каждое устройство активации текучей среды включает в себя нагревательный элемент (например, терморезистор), который, будучи активирован, выделяет тепло, испаряя текучую среду для печати в камере возбуждения сопла. Испарение текучей среды для печати вызывает выброс капли текучей среды для печати из сопла. В других примерах каждое устройство активации текучей среды включает в себя пьезоэлектрический элемент. Будучи активирован, пьезоэлектрический элемент прилагает силу для выброса капли текучей среды для печати из сопла. В других примерах среды для выброса текучей среды из сопла можно использовать другие типы устройств активации текучей среды.

[0022] Система печати может быть системой двумерной (2D) или трехмерной (3D) печати. Система 2D-печати распределяет текучую среду для печати, такую как чернила, формируя изображения на носителях печати, таких как бумажные носители или носители печати других типов. Система 3D-печати формирует 3D-объект путем осаждения последовательных слоев модельного материала. Текучие среды для печати, распределяемые из системы 3D-печати, могут включать в себя чернила, а также агенты, используемые для сплавления порошков слоя модельного материала, детали слоя модельного материала (например, путем задания краев или форм слоя модельного материала) и т.д.

[0023] Как использовано здесь, термин “печатающая головка” относится в общем случае к матрице печатающей головки или узлу, который включает в себя множественные матрицы, установленные на опорной конструкции. Матрица (также называемая “кристаллом интегральной схемы” (матрицей с интегральной схемой)) включает в себя подложку, на которой обеспечиваются различные слои, образующие сопла и/или схему управления, управляющую выбросом текучей среды из сопел.

[0024] Хотя в некоторых примерах выполнена ссылка на печатающую головку для использования в системе печати, отметим, что методы или механизмы настоящего раскрытия применимы к другим типам устройств выброса текучей среды, используемым в областях применения, не связанных с печатью, которые способны распределять текучие среды через сопла. Примеры таких других типов устройств выброса текучей среды включают в себя используемые в системах регистрации текучей среды, медицинских системах, транспортных средствах, системах управления потоком текучей среды и т.д.

[0025] По мере того, как устройства, включающие в себя матрицы печатающей головки или другие типы матриц выброса текучей среды, продолжают уменьшаться в размерах, число сигнальных линий, используемых для управления схемой устройства, может отрицательно влиять на общий размер устройства. Большое число сигнальных линий может приводить к использованию большого числа сигнальных площадок (называемых “контактными площадками” или «столбиковыми выводами»), которые используются для электрического соединения сигнальных линий с внешними линиями. Добавление элементов к устройствам выброса текучей среды может приводить к использованию увеличенного числа сигнальных линий (и соответствующих контактных площадок), которые могут занимать ценное пространство на матрице. Примеры дополнительных элементов, которые могут добавляться к устройству выброса текучей среды, включают в себя запоминающие устройства.

[0026] Соответственно, здесь раскрыты различные примерные схемы устройства выброса текучей среды (которое включает в себя одну матрицу или множественные матрицы), которые могут совместно использовать линии управления и данных для уменьшения числа сигнальных линий устройства выброса текучей среды. Как использовано здесь, термин “линия” означает электрический проводник (или, альтернативно, несколько электрических проводников), который можно использовать для переноса сигнала (или множественных сигналов).

[0027] Фиг. 1 представляет собой блок-схему, иллюстрирующую один пример системы 100 выброса текучей среды. Система 100 выброса текучей среды включает в себя контроллер 102 выброса текучей среды и устройство 106 выброса текучей среды. Контроллер 102 выброса текучей среды подключен с возможностью обмена данными к устройству 106 выброса текучей среды через множество линий 104 управления. Устройство 106 выброса текучей среды может включать в себя схему 108 управления, устройства 110 активации текучей среды, первую память 112 и вторую память 114. Схема 108 управления электрически подключена к устройствам 110 активации текучей среды, первой памяти 112 и второй памяти 114.

[0028] Контроллер 102 выброса текучей среды отделен от устройства 106 выброса текучей среды. Контроллер 102 выброса текучей среды может включать в себя процессор, специализированную интегральную схему (ASIC) или другую подходящую логическую схему для управления устройством 106 выброса текучей среды через линии 104 управления. Например, в системе печати контроллер 102 выброса текучей среды может быть контроллером привода печатающей головки, который составляет часть системы печати, тогда как устройство 106 выброса текучей среды может быть кристаллом интегральной схемы печатающей головки, который составляет часть картриджа печати (который включает в себя чернила или другой агент) или часть другой конструкции.

[0029] Устройства 110 активации текучей среды устройства 106 выброса текучей среды может включать в себя массив сопел, которые являются выборочно управляемыми для распределения текучей среды. Первая память 112 может включать в себя память ID, используемую для хранения данных идентификации и/или другой информации об устройстве 106 выброса текучей среды, такую, чтобы однозначно идентифицировать устройство 106 выброса текучей среды. Вторая память 114 может включать в себя память возбуждения, используемую для хранения данных, относящихся к устройствам 110 активации текучей среды, где данные могут включать в себя любое или некоторую комбинацию из следующих, в качестве примеров: положение матрицы (кристалла), информация о регионе, информация кодирования веса капли, аутентификационная информация, данные для разблокирования или блокирования выбранных устройств активации текучей среды и т.д.

[0030] Первая память 112 и вторая память 114 могут быть реализованы с помощью отличающихся блоков памяти с образованием смешанной компоновки памяти. Первая память 112 может быть реализована с помощью энергонезависимой памяти, такой как электрически программируемая постоянная память (EPROM). Вторая память 114 может быть реализована с помощью энергонезависимой памяти, такой как память на плавких перемычках, где память на плавких перемычках включает в себя массив плавких перемычек, которые могут выборочно пережигаться (или не пережигаться) для программирования данных во вторую память 114. Хотя выше перечислены конкретные примеры типов памяти, отметим, что в других примерах первая память 112 и вторая память 114 могут быть реализованы с помощью других типов памяти. В некоторых примерах первая память 112 и вторая память 114 могут быть реализованы с помощью одинакового типа памяти.

[0031] В одном примере устройства 110 активации текучей среды, первая память 112 и вторая память 114 устройства 106 выброса текучей среды могут формироваться на общем кристалле (т.е. матрице выброса текучей среды). В другом примере устройства 110 активации текучей среды могут быть реализованы на одном кристалле (т.е. матрице выброса текучей среды), тогда как первая память 112 и вторая память 114 могут быть реализованы на отдельном кристалле (или соответствующих отдельных кристаллах). Например, первая память 112 и вторая память 114 могут формироваться на втором кристалле, который отделен от матрицы выброса текучей среды, или, альтернативно, первая память 112 и вторая память 114 могут формироваться на соответствующих разных кристаллах, отдельных от матрицы выброса текучей среды. В других примерах часть первой памяти 112 может находиться на одном кристалле, а другая часть первой памяти 112 может находиться на другом кристалле. Аналогично, часть второй памяти 114 может находиться на одном кристалле, а другая часть второй памяти 114 может находиться на другом кристалле.

[0032] Схема 108 управления управляет работой устройств 110 активации текучей среды, первой памяти 112 и второй памяти 114 на основании сигналов управления, принимаемых через линии 104 управления. Линии (шины) 104 управления включают в себя линию возбуждения, линию CSYNC, линию выбора, линию адресных данных, линию ID, линию тактового сигнала и другие линии. В других примерах могут иметься множественные линии возбуждения и/или множественные линии выбора, и/или множественные линии адресных данных. Схема 108 управления может выбирать устройства 110 активации текучей среды или вторую память 114 на основании сигнала ID на линии ID. Линия ID также может использоваться для осуществления доступа к первой памяти 112 для операций считывания и/или записи. К элементам памяти первой памяти 112 можно обращаться на основании сигналов выбора и данных на линиях выбора и адресных данных.

[0033] Линия возбуждения используется для управления активацией устройств 110 активации текучей среды, когда устройства 110 активации текучей среды выбираются схемой 108 управления в ответ на первый логический уровень на линии ID. Сигнал возбуждения на линии возбуждения, когда он задан на первый логический уровень, вызывает активацию соответствующего устройства активации текучей среды (или устройства активации текучей среды), если к такому устройству активации текучей среды (или устройствам активации текучей среды) обращаются на основании сигналов выбора и данных на линиях выбора и адресных данных. Если сигнал возбуждения задан на второй логический уровень, отличный от первого логического уровня, то устройство активации текучей среды (или устройства активации текучей среды) не активируются. Линия возбуждения также может использоваться для осуществления доступа ко второй памяти 114 для операций считывания и/или записи, когда вторая память 114 выбирается схемой 108 управления в ответ на второй логический уровень на линии ID. К элементам памяти второй памяти 114 можно обращаться на основании сигналов выбора и данных на линиях выбора и адресных данных.

[0034] Сигнал CSYNC используется для инициирования адреса (называемого Ax и Ay) в устройстве 106 выброса текучей среды. Линию выбора можно использовать для выбора определенных устройств активации текучей среды или элементов памяти. Линию адресных данных можно использовать для переноса бита адреса (или битов адреса) на адрес конкретного устройства активации текучей среды или элемента памяти (или конкретной группы устройств активации текучей среды или группы элементов памяти). Линию тактового сигнала можно использовать для переноса тактового сигнала для схемы 108 управления.

[0035] В соответствии с некоторыми реализациями настоящего раскрытия для повышения гибкости и уменьшения числа площадок ввода/вывода (I/O), которые нужно обеспечивать на устройстве 106 выброса текучей среды, каждая из линии возбуждения и линии ID осуществляет как первичные, так и вторичные задачи. Как указано выше, первичная задача линии возбуждения состоит в активации выбранного устройства (устройств) 110 активации текучей среды. Вторичная задача линии возбуждения состоит в передаче данных второй памяти 114. Таким образом может обеспечиваться тракт передачи данных между контроллером 102 выброса текучей среды и второй памятью 114 (по линии возбуждения) без необходимости обеспечения отдельной линии данных между контроллером 102 выброса текучей среды и устройством 106 выброса текучей среды.

[0036] Первичная задача линии ID состоит в передаче данных первой памяти 112. Вторичная задача линии ID состоит в побуждении схемы 108 управления разблокировать либо устройства 110 активации текучей среды, либо вторую память 114. Таким образом общую линию возбуждения можно использовать для управления активацией устройств 110 активации текучей среды и для передачи данных второй памяти 114, где линию ID можно использовать для выбора, когда устройства 110 активации текучей среды управляются линией возбуждения и когда линию возбуждения можно использовать для передачи данных второй памяти 114.

[0037] Фиг. 2 представляет собой примерную схему, более подробно иллюстрирующую один пример устройства 106 выброса текучей среды по фиг. 1. Устройство 106 выброса текучей среды включает в себя устройства 110 активации текучей среды, первую память 112, вторую память 114, защелки 130 и 132, декодер 134 сдвигового регистра, генератор 136 адресов, линию 140 возбуждения, линию 142 ID и переключатели 144, 146, 148 и 150. В одном примере линия 140 возбуждения и линия 142 ID составляют часть линий 104 управления по фиг. 1. Защелки 130 и 132, декодер 134 сдвигового регистра, генератор 136 адресов и переключатели 144, 146, 148 и 150 могут входить в состав схемы 108 управления по фиг. 1.

[0038] Линия 142 ID электрически подключена ко входу защелки 130, входу защелки 132 и к первой памяти 112. Линия 140 возбуждения электрически подключена к одной стороне переключателя 146 и к устройствам 110 активации текучей среды. Выход защелки 130 электрически подключен ко входу управления переключателя 146. Другая сторона переключателя 146 электрически подключена ко второй памяти 114. Выход защелки 132 электрически подключен ко входу управления переключателя 148. Переключатель 148 электрически подключен между второй памятью 114 и общим узлом или узлом 152 заземления. Переключатель 150 электрически подключен между устройствами 110 активации текучей среды и общим узлом или узлом 152 заземления. Выход генератора 136 адресов электрически подключен ко входу управления переключателя 148 и входу управления переключателя 150. Выход сдвигового регистра 134 электрически подключен ко входу управления переключателя 144. Переключатель 144 электрически подключен между первой памятью 112 и общим узлом или узлом 152 заземления.

[0039] Первая память 112 может включать в себя множество элементов памяти. Переключатель 144 может включать в себя множество переключателей, где каждый переключатель соответствует одному из элементов памяти первой памяти 112. Декодер 134 сдвигового регистра выбирает элемент памяти первой памяти 112 для осуществления доступа для считывания и/или записи путем замыкания переключателя 144, соответствующего выбранному элементу памяти. Декодер 134 сдвигового регистра блокирует элементы памяти первой памяти 112 путем размыкания переключателей 144, соответствующих заблокированным элементам памяти. Когда декодер 134 сдвигового регистра выбирает элемент памяти первой памяти 112, к этому элементу памяти можно осуществлять доступ для операций считывания и/или записи через линию 142 ID.

[0040] Защелка 130 принимает сигнал ID на линии 142 ID, фиксирует логический уровень сигнала ID и управляет переключателем 146 на основании фиксированного значения. В ответ на первый логический уровень (например, логически высокий) фиксированного значения защелка 130 включает переключатель 146. В ответ на второй логический уровень (например, логически низкий) фиксированного значения защелка 130 отключает переключатель 146. При замкнутом переключателе 146 вторая память 114 разблокируется для осуществления доступа для считывания и/или записи через линию 140 возбуждения. При разомкнутом переключателе 146 вторая память 114 блокируется.

[0041] Вторая память 114 может включать в себя множество элементов памяти. Переключатель 148 может включать в себя множество переключателей, где каждый переключатель соответствует одному из элементов памяти второй памяти 114. Переключатель 150 может включать в себя множество переключателей, где каждый переключатель соответствует одному из устройств 110 активации текучей среды. Защелка 132 принимает сигнал ID на линии 142 ID, фиксирует инвертированный логический уровень сигнала ID и управляет переключателем 148 на основании фиксированного значения. В ответ на первый логический уровень (например, логически высокий) фиксированного значения защелка 132 блокирует переключатель 148 (т.е. предотвращает включение переключателя 148). В ответ на второй логический уровень (например, логически низкий) фиксированного значения защелка 132 разблокирует переключатель 148 (т.е. разрешает включить переключатель 148).

[0042] Генератор 136 адресов генерирует сигналы Ax и Ay адреса для выбора элемента памяти второй памяти 114 или устройства 110 активации текучей среды. Выбор элемента памяти второй памяти 114 или устройства 110 активации текучей среды также может основываться на сигнале (D2) данных на линии адресных данных. Соответственно, как показано на фиг. 2 и более подробно описано ниже, переключателем 148 можно управлять на основании ID × D2 × AxAy, а переключателем 150 можно управлять на основании ID’ × D2 × AxAy. При разомкнутом переключателе 150, замкнутом переключателе 146 и замкнутом переключателе 148 доступ ко второй памяти 114 можно осуществлять для операций считывания и/или записи через линию 140 возбуждения. При разомкнутом переключателе 146, разомкнутом переключателе 148 и замкнутом переключателе 150 устройства 110 активации текучей среды могут активироваться через линию 140 возбуждения.

[0043] Фиг. 3 представляет собой блок-схему, иллюстрирующую один пример схемы 200, включающей в себя первую память и вторую память устройства выброса текучей среды. В одном примере схема 200 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Схема 200 включает в себя первую память 112 и вторую память 114. Первая память 112 включает в себя множество элементов 2121-212M первой памяти, где “M” - любое подходящее число элементов памяти. Вторая память 114 включает в себя множество элементов 2141-214N второй памяти, где “N” - любое подходящее число элементов памяти. Первая память 112 и вторая память 114 могут включать в себя одинаковое число элементов памяти или разное число элементов памяти.

[0044] Схема 200 также включает в себя множество линий 2161-2163 первых данных (D11 - D13) и линию 218 вторых данных (D2). Линии 2161-2163 первых данных электрически подключены к первой памяти 112, и линия 218 вторых данных электрически подключена ко второй памяти 114. В одном примере линии 2161-2163 первых данных и линия 218 вторых данных составляют часть линий адресных данных линий 104 управления по фиг. 1. В этом примере элемент 212 памяти первой памяти 112 разблокируется в ответ на первые данные на множестве линий 2161-2163 первых данных, и элемент 214 памяти второй памяти 114 разблокируется в ответ на вторые данные на линии 218 вторых данных.

[0045] Фиг. 4 представляет собой блок-схему, иллюстрирующую другой пример схемы 230, включающей в себя первую память и вторую память устройства выброса текучей среды. В одном примере схема 230 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Схема 230 включает в себя первую память 112 и вторую память 114, которые описаны ранее и проиллюстрированы со ссылкой на фиг. 3. Схема 230 также включает в себя линию 142 ID, линию 236 первого выбора (S4) и линию 238 второго выбора (S5). Линия 236 первого выбора электрически подключена к первой памяти 112, а линия 238 второго выбора и линия 142 ID электрически подключены ко второй памяти 114. В этом примере элемент 212 памяти первой памяти 112 разблокируется в ответ на первый логический уровень на линии 236 первого выбора, а элемент 214 памяти второй памяти 114 разблокируется в ответ на первый логический уровень на линии 238 второго выбора и первый логический уровень на линии ID.

[0046] В одном примере схема 200 по фиг. 3 может объединяться со схемой 230 по фиг. 4. Поэтому доступ к первой памяти 112 может осуществляться на основании адреса, сгенерированного первыми данными D11, D12 и D13 (например, через декодер 134 сдвигового регистра по фиг. 1), тогда как доступ ко второй памяти 114 может осуществляться на основании адреса, сгенерированного вторыми данными D2. Первые данные и вторые данные могут быть полностью независимы друг от друга. Кроме того, первая память 112 может разблокироваться в ответ на сигнал выбора S4, тогда как вторая память 114 может разблокироваться в ответ на сигнал выбора S5. Сигнал выбора S4 и сигнал выбора S5 могут быть ступенчатыми. Таким образом можно избежать искажения сигнала ID из-за сдвигового регистра (например, декодера 134 сдвигового регистра по фиг. 1).

[0047] Фиг. 5 представляет собой примерную схему, иллюстрирующую один пример схемы 250, включающей в себя элемент памяти устройства выброса текучей среды. В одном примере схема 250 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Схема 250 включает в себя линию 140 возбуждения, линию 142 ID, элемент 252 памяти, защелку 254 и тракт 256 разряда. Линия 140 возбуждения электрически подключена к элементу 252 памяти. Линия 142 ID электрически подключена ко входу защелки 254. Выход защелки 254 электрически подключен ко входу тракта 256 разряда. Тракт 256 разряда электрически подключен между элементом 252 памяти и общим узлом или узлом 152 заземления.

[0048] Тракт 256 разряда удерживает элемент 252 памяти от плавающего режима, когда элемент 252 памяти не разблокирован для осуществления доступа для считывания и/или записи. В этом примере защелка 254 блокирует тракт разряда в ответ на первый логический уровень (например, логически высокий) на линии 142 ID и разблокирует тракт разряда в ответ на второй логический уровень (например, логически низкий) на линии ID. Когда элемент 252 памяти разблокируется, тракт 256 разряда блокируется и доступ к элементу 252 памяти может осуществляться через линию 140 возбуждения для операций считывания и/или записи. В одном примере защелка 254 обеспечивает защелку 132 по фиг. 2, тракт 256 разряда составляет часть входа управления для переключателя 148, и элемент 252 памяти является элементом памяти второй памяти 114 по фиг. 2.

[0049] Фиг. 6 представляет собой примерную схему, иллюстрирующую другой пример схемы 270, включающей в себя элемент памяти устройства выброса текучей среды. В одном примере схема 270 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Схема 270 включает в себя линию 140 возбуждения, линию 142 ID, элемент 252 памяти, защелку 272 и переключатель 274. Переключатель 274 электрически подключен между линией 140 возбуждения и элементом 252 памяти. Вход защелки 272 электрически подключен к линии 142 ID. Выход защелки 272 электрически подключен ко входу управления переключателя 274. Элемент 252 памяти электрически подключен к общему узлу или узлу 152 заземления.

[0050] В этом примере защелка 272 разблокирует (т.е. включает) переключатель 274 в ответ на первый логический уровень (например, логически высокий) на линии 142 ID и блокирует (т.е. отключает) переключатель 274 в ответ на второй логический уровень (например, логически низкий) на линии ID. При разблокированном переключателе 274 линия 140 возбуждения электрически подключена к элементу 252 памяти. При заблокированном переключателе 274 линия 140 возбуждения электрически отключена от элемента 252 памяти. При разблокированном переключателе 274 доступ к элементу 252 памяти может осуществляться через линию 140 возбуждения для операций считывания и/или записи. В одном примере защелка 272 обеспечивает защелку 130 по фиг. 2, переключатель 274 обеспечивает переключатель 146 по фиг. 2, и элемент 252 памяти является элементом памяти второй памяти 114 по фиг. 2.

[0051] Фиг. 7A представляет собой примерную схему, иллюстрирующую один пример схемы 300, включающей в себя множество элементов памяти устройства выброса текучей среды. В одном примере схема 300 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Схема 300 включает в себя линию 140 возбуждения, множество элементов 2141-214N памяти, первый переключатель 304 и множество вторых переключателей 3081-308N. Переключатель 304 электрически подключен между линией 140 возбуждения и первой стороной каждого элемента 2141-214N памяти. Вход управления переключателя 304 электрически подключен к линии 302 сигнала управления (Vy). Одна сторона каждого второго переключателя 3081-308N электрически подключена ко второй стороне соответствующего элемента 2141-214N памяти. Другая сторона каждого второго переключателя 3081-308N электрически подключена к общему узлу или узлу 152 заземления. Вход управления каждого второго переключателя 3081-308N электрически подключен к линиям 3061-306N сигнала управления (X1 - XN) соответственно.

[0052] Сигнал управления Vy может основываться на сигнале ID (например, на линии 142 ID). Сигналы управления X1 - XN могут основываться на сигнале ID (например, на линии 142 ID), сигнале данных D2 (например, на линии 218 данных D2), а также адресных сигналах Ax и Ay (например, от генератора 136 адресов). В этом примере элемент 2141-214N памяти может разблокироваться путем включения переключателя 304 в ответ на сигнал Vy и включения по меньшей мере одного соответствующего второго переключателя 3081-308N в ответ на соответствующий сигнал X1 - XN. При разблокированном элементе 2141-214N памяти доступ к разблокированному элементу памяти может осуществляться для операций считывания и/или записи через линию 140 возбуждения. В одном примере первый переключатель 304 обеспечивает переключатель 146 по фиг. 2, а каждый второй переключатель 3081-308N обеспечивает переключатель 148 по фиг. 2.

[0053] Фиг. 7B представляет собой схему, иллюстрирующую другой пример схемы 320, включающей в себя множество элементов памяти устройства выброса текучей среды. В одном примере схема 320 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Схема 320 подобна схеме 300, ранее описанной и проиллюстрированной со ссылкой на фиг. 7A, за исключением того, что в схеме 320 вместо первого переключателя 304 используется первый транзистор 324, а вместо вторых переключателей 3081-308N используется множество вторых транзисторов 3281-328N. Первый транзистор 324 имеет канал сток-исток, электрически подключенный между линией 140 возбуждения и первой стороной каждого элемента 2141-214N памяти. Каждый второй транзистор 3281-328N имеет канал сток-исток, электрически подключенный между соответствующим элементом 2141-214N памяти и общим узлом или узлом 152 заземления. Затвор каждого второго транзистора 3281-328N электрически подключен к линиям 3061-306N сигнала управления, соответственно.

[0054] В этом примере элемент 2141-214N памяти может разблокироваться путем включения первого транзистора 324 в ответ на логически высокий сигнал Vy и включения по меньшей мере одного соответствующего второго транзистора 3281-328N в ответ на соответствующий логически высокий сигнал X1 - XN. При разблокированном элементе 2141-214N памяти доступ к разблокированному элементу памяти может осуществляться для операций считывания и/или записи через линию 140 возбуждения. В одном примере первый транзистор 324 обеспечивает переключатель 146 по фиг. 2, а каждый второй транзистор 3281-328N обеспечивает переключатель 148 по фиг. 2.

[0055] Фиг. 8A-8B представляют собой примерные схемы, иллюстрирующие один пример схемы 350, включающей в себя множество элементов памяти и множество устройств активации текучей среды устройства выброса текучей среды. В одном примере схема 350 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Схема 350 включает в себя схему 320, ранее описанную и проиллюстрированную со ссылкой на фиг. 7B. Кроме того, как показано на фиг. 8A, схема 350 включает в себя множество устройств 3521-352N активации текучей среды и множество третьих переключателей (например, третьих транзисторов) 3581-358N. Каждое устройство 3521-352N активации текучей среды электрически подключено между линией 140 возбуждения и одной стороной канала сток-исток соответствующего третьего транзистора 3581-358N. Другая сторона канала сток-исток каждого третьего транзистора 3581-358N электрически подключена к общему узлу или узлу 152 заземления. Затвор каждого третьего транзистора 3581-358N электрически подключен к линии 3561-356N сигнала управления (Y1 - YN), соответственно.

[0056] Как показано на фиг. 8B, схема 350 также включает в себя генератор 136 адресов и декодер 360. Выходы генератора 136 адресов электрически подключены ко входам декодера 360 через линию 362 сигнала адреса Ax и линию 364 сигнала адреса Ay. Другие входы декодера 360 электрически подключены к линии 142 ID и линии 218 вторых данных. Первые выходы декодера 360 электрически подключены к затворам вторых транзисторов 3281-328N через линии 3061-306N сигнала управления, соответственно. Вторые выходы декодера 360 электрически подключены к затворам третьих транзисторов 3581-358N через линии 3561-356N сигнала управления, соответственно.

[0057] Ax и Ay выводятся генератором 136 адресов, например, в ответ на сигнал выбора на линии выбора и сигнал CSYNC на линии CSYNC. В одном примере декодер 360 получает адрес (например, D2, Ax, Ay) для включения соответствующего второго транзистора 3281-328N или соответствующего третьего транзистора 3581-358N в ответ на адрес. В другом примере в ответ на первый логический уровень (например, логически высокий) на линии 142 ID декодер 360 включает соответствующий второй транзистор 3281-328N в ответ на адрес, а в ответ на второй логический уровень (например, логически низкий) на линии 142 ID, декодер 360 включает соответствующий третий транзистор 3581-358N в ответ на адрес для разблокирования соответствующего устройства 3521-352N активации текучей среды. При разблокированном устройстве 3521-352N активации текучей среды разблокированное устройство активации текучей среды может быть активировано через линию 140 возбуждения. В одном примере каждый третий транзистор 3581-358N обеспечивает переключатель 150 по фиг. 2.

[0058] Фиг. 9A представляет собой примерную схему, иллюстрирующую более подробно один пример схемы 400, включающей в себя первую память 112, вторую память 114 и устройства 110 активации текучей среды. В одном примере схема 400 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Хотя первая память 112 включает в себя множество элементов памяти, на фиг. 9A показан только один элемент 212 памяти. Аналогично, хотя вторая память 114 включает в себя множество элементов памяти, на фиг. 9A показан только один элемент 214 памяти, и, хотя устройства 110 активации текучей среды включают в себя множество устройств активации текучей среды, на фиг. 9A показано только одно устройство 352 активации текучей среды.

[0059] Схема 400 включает в себя линию 140 возбуждения, линию 142 ID, линии 2161-2163 первых данных, линию 218 вторых данных, линии 236 и 238 выбора, линию 362 сигнала адреса Ax, линию 364 сигнала адреса Ay, декодер 134 сдвигового регистра и транзисторы 324, 328 и 358, как описано ранее. Кроме того, схема 400 включает в себя буфер 408, инвертор 410 и транзисторы 402, 404, 406, 412, 414, 416, 418, 420, 422, 432, 434, 436, 438, 440 и 442. В одном примере транзисторы 402, 404 и 406 могут обеспечивать переключатель 144 по фиг. 2. Буфер 408 может обеспечивать защелку 130 по фиг. 2 или защелку 272 по фиг. 6. Инвертор 410 может обеспечивать защелку 132 по фиг. 2 или защелку 254 по фиг. 5. Транзистор 416 может обеспечивать часть тракта 256 разряда по фиг. 5 для первой памяти 114. Транзистор 436 может обеспечивать тракт разряда для устройств 110 активации текучей среды. Транзисторы 412, 414, 418, 420, 422, 432, 434, 438, 440 и 442 могут обеспечивать часть декодера 360 по фиг. 8B.

[0060] Первые входы декодера 134 сдвигового регистра электрически подключены к линиям 2161-2163 первых данных. Второй вход декодера 134 сдвигового регистра электрически подключен к линии 236 первого выбора (S4). Выходы декодера 134 сдвигового регистра электрически подключены к затворам транзисторов 402, 404 и 406. Транзисторы 402, 404 и 406 электрически подключены последовательно между элементом 212 памяти и общим узлом или узлом 152 заземления. Когда транзисторы 402, 404 и 406 включаются, осуществляется обращение к элементу 212 памяти, в результате чего можно осуществлять доступ к данным элемента 212 памяти через линию 142 ID.

[0061] Декодер 134 сдвигового регистра включает в себя сдвиговые регистры, подключенные к каждой из линий 2161-2163 первых данных для ввода битов адресных данных в декодер 134 сдвигового регистра. Каждый сдвиговый регистр включает в себя серию ячеек сдвигового регистра, которые могут быть реализованы как триггеры, другие элементы хранения или любые схемы выборки и удержания (такие как схемы для предварительной зарядки и оценивания битов адресных данных), которые могут удерживать свои значения до следующего выбора элементов хранения. Выходной сигнал одной ячейки сдвигового регистра в этой серии может подаваться на вход следующей ячейки сдвигового регистра для осуществления сдвига данных с помощью сдвигового регистра. Биты адресных данных, обеспеченные с помощью каждого сдвигового регистра, поступают на затвор соответствующего из транзисторов 402, 404 и 406.

[0062] За счет использования сдвиговых регистров на декодере 134 сдвигового регистра, для выбора увеличенного адресного пространства можно использовать небольшое число линий 2161-2163 (передачи) данных. Например, каждый сдвиговый регистр может включать в себя восемь (или любое другое число) ячеек сдвигового регистра. Когда три бита адресных данных (D11, D12 и D13) вводятся в декодер 134 сдвигового регистра, который включает в себя три сдвиговых регистра, каждый длиной восемь, адресное пространство, к которому можно обращаться декодером 134 сдвигового регистра, составляет 512 битов (вместо всего лишь восьми битов в случае использования трех битов адреса без использования сдвиговых регистров декодера 134 сдвигового регистра). Выход декодера 134 сдвигового регистра может разблокироваться в ответ на первый логический уровень на линии 236 первого выбора (S4) и блокироваться в ответ на второй логический уровень на линии 236 первого выбора (S4).

[0063] Буфер 408 электрически подключен между линией 142 ID и затвором транзистора 324 через узел 409 Vy. Инвертор 410 электрически подключен между линией 142 ID и затвором транзистора 416 через узел 411 Vx. Одна сторона канала сток-исток транзистора 416 электрически подключена к общему узлу или узлу 152 заземления. Другая сторона канала сток-исток транзистора 416 электрически подключена к одной стороне канала сток-исток транзистора 414, одной стороне канала сток-исток транзистора 418, одной стороне канала сток-исток транзистора 420 и одной стороне канала сток-исток транзистора 422. Другая сторона канала сток-исток каждого транзистора 418, 420 и 422 электрически подключена к общему узлу или узлу 152 заземления. Затвор транзистора 418 электрически подключен к линии 218 вторых данных. Затвор транзистора 420 электрически подключен к линии 362 сигнала адреса Ax. Затвор транзистора 422 электрически подключен к линии 364 сигнала адреса Ay. Затвор транзистора 414 электрически подключен к линии 238 второго выбора (S5). Другая сторона канала сток-исток транзистора 414 электрически подключена к одной стороне канала сток-исток транзистора 412 и затвору транзистора 328. Другая сторона канала сток-исток и затвор транзистора 412 электрически подключены к линии 236 первого выбора (S4).

[0064] Затвор транзистора 436 электрически подключен к линии 142 ID. Одна сторона канала сток-исток транзистора 436 электрически подключена к общему узлу или узлу 152 заземления. Другая сторона канала сток-исток транзистора 436 электрически подключена к одной стороне канала сток-исток транзистора 434, одной стороне канала сток-исток транзистора 438, одной стороне канала сток-исток транзистора 440 и одной стороне канала сток-исток транзистора 442. Другая сторона канала сток-исток каждого транзистора 438, 440 и 442 электрически подключена к общему узлу или узлу 152 заземления. Затвор транзистора 438 электрически подключен к линии 218 вторых данных. Затвор транзистора 440 электрически подключен к линии 362 сигнала адреса Ax. Затвор транзистора 442 электрически подключен к линии 364 сигнала адреса Ay. Затвор транзистора 434 электрически подключен к линии 238 второго выбора (S5). Другая сторона канала сток-исток транзистора 434 электрически подключена к одной стороне канала сток-исток транзистора 432 и затвору транзистора 358. Другая сторона канала сток-исток и затвор транзистора 432 электрически подключены к линии 236 первого выбора (S4).

[0065] Для управления соответствующими транзисторами 328 и 358, подключенными к элементу 214 памяти и устройству 352 активации текучей среды, соответственно, используются два отдельных декодера. Затвор транзистора 328 подключен к первому декодеру, который включает в себя транзисторы 412, 414, 418, 420 и 422. Затвор транзистора 358 подключен ко второму декодеру, который включает в себя транзисторы 432, 434, 438, 440 и 442. Сигнал выбора S4 может активироваться раньше по времени, чем сигнал выбора S5. Комбинация Ax, Ay, D2, S4 и S5 образует адресный вход в первый декодер и второй декодер.

[0066] Когда сигнал ID на линии 142 ID находится на первом логическом уровне (например, логически высоком), транзистор 436 включается и побуждает затвор транзистора 358 оставаться разряженным (т.е. блокирует затвор транзистора 358), благодаря чему устройство 352 активации текучей среды остается деактивированным. Кроме того, когда сигнал ID находится на первом логическом уровне (например, логически высоком), транзистор 324 включается буфером 408, а транзистор 416 отключается инвертором 410, благодаря чему, когда транзистор 328 включается на основании адресного ввода на первый декодер, доступ к элементу 214 памяти может осуществляться для операций считывания и/или записи через линию 140 возбуждения.

[0067] Когда сигнал ID на линии 142 ID находится на втором логическом уровне (например, логически низком), транзистор 436 отключается, благодаря чему, когда транзистор 358 включается на основании адресного ввода на второй декодер, устройство 352 активации текучей среды может активироваться через линию 140 возбуждения. Кроме того, когда сигнал ID находится на втором логическом уровне (например, логически низком), транзистор 324 отключается буфером 408, а транзистор 416 включается инвертором 410. При включенном транзисторе 416 затвор транзистора 328 остается разряженным (т.е. затвор транзистора 328 блокируется), благодаря чему элемент 214 памяти остается не выбранным.

[0068] Фиг. 9B представляет собой примерную схему, иллюстрирующую другой пример схемы 450, включающей в себя первую память 112, вторую память 114 и устройства 110 активации текучей среды. В одном примере схема 450 составляет часть интегральной схемы для приведения в действие множества устройств активации текучей среды. Схема 450 подобна схеме 400, ранее описанной и проиллюстрированной со ссылкой на фиг. 9A, за исключением того, что в схеме 450 вместо буфера 408 используются транзисторы 452, 454, 456, 458, 460 и 462; а вместо инвертора 410 используются транзисторы 468, 470 и 472.

[0069] Транзистор 460 и транзистор 462 электрически подключены последовательно между узлом 459 и общим узлом или узлом 152 заземления. Затвор транзистора 462 электрически подключен к линии 142 ID, а затвор транзистора 460 электрически подключен к линии 236 выбора S4. Транзистор 458 имеет канал сток-исток, электрически подключенный между линией 234 выбора S3 и узлом 459. Затвор транзистора 458 электрически подключен к линии 234 выбора S3. Транзистор 454 и транзистор 456 электрически подключены последовательно между затвором транзистора 324 и общим узлом или узлом 152 заземления. Затвор транзистора 456 электрически подключен к узлу 459. Затвор транзистора 454 электрически подключен к линии 238 выбора S5. Транзистор 452 имеет канал сток-исток, электрически подключенный между линией 236 выбора S4 и затвором транзистора 324. Затвор транзистора 452 электрически подключен к линии 236 выбора S4.

[0070] Транзистор 470 и транзистор 472 электрически подключены последовательно между затвором транзистора 416 и общим узлом или узлом 152 заземления. Затвор транзистора 472 электрически подключен к линии 142 ID. Затвор транзистора 470 электрически подключен к линии 236 выбора S4. Транзистор 468 имеет канал сток-исток, электрически подключенный между линией 234 выбора S3 и затвором транзистора 416. Затвор транзистора 468 электрически подключен к линии 234 выбора S3.

[0071] Сигнал выбора S3 может активироваться раньше по времени, чем сигнал выбора S4. Сигнал выбора S4 может активироваться раньше по времени, чем сигнал выбора S5. Когда сигнал ID на линии 142 ID находится на первом логическом уровне (например, логически высоком), второй логический уровень (например, логически низкий) фиксируется на узле 411 Vx в ответ на сигналы выбора S3 и S4. Когда сигнал ID находится на втором логическом уровне (например, логически низком), первый логический уровень (например, логически высокий) фиксируется на узле 411 Vx в ответ на сигналы выбора S3 и S4.

[0072] Когда сигнал ID на линии 142 ID находится на первом логическом уровне (например, логически высоком), второй логический уровень (например, логически низкий) фиксируется на узле 459 в ответ на сигналы выбора S3 и S4. Когда сигнал ID находится на втором логическом уровне (например, логически низком), первый логический уровень (например, логически высокий) фиксируется на узле 459 в ответ на сигналы выбора S3 и S4. При первом логическом уровне (например, логически высоком) на узле 459, второй логический уровень (например, логически низкий) фиксируется на узле 409 Vy в ответ на сигналы выбора S4 и S5. При втором логическом уровне (например, логически низком) на узле 459, первый логический уровень (например, логически высокий) фиксируется на узле 409 Vy в ответ на сигналы выбора S4 и S5. Соответственно, когда сигнал ID на линии 142 ID находится на первом логическом уровне (например, логически высоком), первый логический уровень (например, логически высокий) фиксируется на узле 409 Vy в ответ на сигналы выбора S3, S4 и S5. Когда сигнал ID находится на втором логическом уровне (например, логически низком), второй логический уровень (например, логически низкий) фиксируется на узле 409 Vy в ответ на сигналы выбора S3, S4 и S5.

[0073] Фиг. 10A и 10B представляют собой временные диаграммы, иллюстрирующие один пример работы схемы 450 по фиг. 9B. Фиг. 10A иллюстрирует временную диаграмму 500a в случае, когда элемент 214 памяти разблокирован, и фиг. 10B иллюстрирует временную диаграмму 500b в случае, когда устройство 352 активации текучей среды разблокировано. Временные диаграммы 500a и 500b включают в себя сигнал CSYNC, сигнал выбора S1, сигнал выбора S2, сигнал выбора S3 на линии 234 выбора S3, сигнал выбора S4 на линии 236 выбора S4, сигнал выбора S5 на линии 238 выбора S5, тактовый сигнал, сигнал данных D11 на линии 2161 данных D11, сигнал данных D12 на линии 2162 данных D12, сигнал данных D2 на линии 218 данных D2, сигнал ID на линии 142 ID, сигнал Vx на узле 411 Vx и сигнал возбуждения на линии 140 возбуждения.

[0074] Сигналы выбора S1 - S5 последовательно активируются. Сигналы выбора S1 и S2 могут использоваться первой памятью 112, например, для управления декодером 134 сдвигового регистра. Как показано на фиг. 10A в позиции 502, когда сигнал ID является логически высоким, когда сигнал S4 является логически высоким, Vx является логически низким. Таким образом, когда сигнал S5 является логически высоким, тракт разряда для элемента 214 памяти отключен, и элемент 214 памяти разблокирован для осуществления доступа для считывания и/или записи посредством сигнала возбуждения, как указано позицией 504. Как показано на фиг. 10B в позиции 506, когда сигнал ID является логически низким, когда сигнал S4 является логически высоким, Vx является логически высоким. Таким образом, когда сигнал S5 является логически высоким, тракт разряда для элемента 214 памяти включен, и элемент 214 памяти заблокирован. При заблокированном элементе 214 памяти устройство 352 активации текучей среды может разблокироваться и может активироваться посредством сигнала возбуждения, как указано позицией 508.

[0075] В одном примере, как показано на фиг. 10A и 10B, сигнал ID и сигнал возбуждения не могут включаться (т.е. быть логически высокими) одновременно. Соответственно, сигнал ID фиксируется для обеспечения Vx, когда сигнал S4 является логически высоким, для подготовки к сигналу возбуждения, когда S5 является логически высоким. Это также гарантирует, что, либо затвор транзистора 328 для элемента 214 памяти, либо затвор транзистора 358 для устройства 352 активации текучей среды имеет тракт разряда во избежание плавающего режима, если они не выбраны. Плавающий режим следует избегать для предотвращения искажения данных, хранящихся во второй памяти 114.

[0076] Фиг. 11A и 11B представляют собой временные диаграммы, иллюстрирующие другой пример работы схемы по фиг. 9B. Фиг. 11A иллюстрирует временную диаграмму 550a в случае, когда элемент 214 памяти разблокирован, а фиг. 11B иллюстрирует временную диаграмму 550b в случае, когда устройство 352 активации текучей среды разблокировано. Временные диаграммы 550a и 550b включают в себя сигнал CSYNC, сигнал выбора S1, сигнал выбора S2, сигнал выбора S3 на линии 234 выбора S3, сигнал выбора S4 на линии 236 выбора S4, сигнал выбора S5 на линии 238 выбора S5, тактовый сигнал, сигнал данных D11 на линии 2161 данных D11, сигнал данных D12 на линии 2162 данных D12, сигнал данных D2 на линии 218 данных D2, сигнал ID на линии 142 ID, сигнал Vy на узле 409 Vy и сигнал возбуждения на линии 140 возбуждения.

[0077] Как показано на фиг. 11A в позиции 552, когда сигнал ID является логически высоким, когда сигнал S4 является логически высоким, Vy является логически высоким, сигнал S5 является логически высоким. При логически высоком Vy элемент 214 памяти разблокируется для осуществления доступа для считывания и/или записи посредством сигнала возбуждения, как указано позицией 554. Как показано на фиг. 11B в позиции 556, когда сигнал ID является логически низким, когда сигнал S4 является логически высоким, Vy является логически низким, когда сигнал S5 является логически высоким. При логически низком Vy элемент 214 памяти блокируется и изолируется от сигнала возбуждения. При заблокированном элементе 214 памяти устройство 352 активации текучей среды может разблокироваться и может активироваться посредством сигнала возбуждения, как указано позицией 558.

[0078] В одном примере, как показано на фиг. 11A и 11B, сигнал ID и сигнал возбуждения не могут включаться (т.е. быть логически высокими) одновременно. Соответственно, сигнал ID фиксируется для обеспечения Vy, когда сигнал S4 является логически высоким, для подготовки к сигналу возбуждения, когда S5 является логически высоким. Транзистор 324 также служит в качестве изолятора между сигналом возбуждения и элементом 214 памяти, когда устройство 352 активации текучей среды активировано. Это может предохранять элемент 214 памяти от воздействия высокого напряжения на высокой частоте, что может повышать надежность элемента 214 памяти.

[0079] Фиг. 12 представляет собой блок-схему, иллюстрирующую один пример системы 600 выброса текучей среды. Система 600 выброса текучей среды включает в себя узел выброса текучей среды, такой как узел 602 печатающей головки, и узел подачи текучей среды, такой как узел 610 подачи чернил. В иллюстрируемом примере система 600 выброса текучей среды также включает в себя узел 604 станции технического обслуживания, узел 616 каретки, узел 618 транспортировки носителей печати и электронный контроллер 620. Хотя нижеследующее описание обеспечивает примеры систем и узлов для обработки текучей среды в отношении чернил, раскрытые системы и узлы также применимы к обработке текучих сред, отличных от чернил.

[0080] Узел 602 печатающей головки включает в себя по меньшей мере одну печатающую головку или одну матрицу 606 выброса текучей среды, такую(ой) как устройство 106 выброса текучей среды по фиг. 1, которое выбрасывает капли чернил или текучей среды через множество дюз или сопел 608. В одном примере капли направляются к носителю, такому как носитель 624 печати, для печати на носителях 624 печати. В одном примере носитель 624 печати включает в себя любой тип подходящего листового материала, такой как бумага, стопка карточек, диапозитивы, майлар, ткань и пр. В другом примере носители 624 печати включают в себя носители для трехмерной (3D) печати, такие как порошковую подушку или носители для биопечати и/или тестирования для поиска новых лекарств, такие как сосуд или резервуар. В одном примере сопла 608 располагаются в по меньшей мере одном столбце или массиве, благодаря чему надлежащим образом упорядоченный выброс чернил из сопел 608 обеспечивает печать знаков, символов и/или других графических объектов или изображений на носителях 624 печати, когда узел 602 печатающей головки и носители 624 печати перемещаются относительно друг друга.

[0081] Узел 610 подачи чернил подает чернила на узел 602 печатающей головки и включает в себя сосуд 612 для хранения чернил. Таким образом, в одном примере чернила текут из сосуда 612 в узел 602 печатающей головки. В одном примере узел 602 печатающей головки и узел 610 подачи чернил совместно заключены в картридже или пере струйной или жидкостно-струйной печати. В другом примере узел 610 подачи чернил отделен от узла 602 печатающей головки и подает чернила на узел 602 печатающей головки через сопрягающее соединение 613, такое как трубка и/или клапан для подачи.

[0082] Узел 616 каретки позиционирует узел 602 печатающей головки относительно узла 618 транспортировки носителей печати, а узел 618 транспортировки носителей печати позиционирует носители 624 печати относительно узла 602 печатающей головки. Таким образом, зона 626 печати задается рядом с соплами 608 в области между узлом 602 печатающей головки и носителями 624 печати. В одном примере узел 602 печатающей головки является узлом печатающей головки сканирующего типа, благодаря чему узел 616 каретки перемещает узел 602 печатающей головки относительно узла 618 транспортировки носителей печати. В другом примере узел 602 печатающей головки является узлом печатающей головки несканирующего типа, благодаря чему узел 616 каретки фиксирует узел 602 печатающей головки в предписанном положении относительно узла 618 транспортировки носителей печати.

[0083] Узел 604 станции технического обслуживания обеспечивает промывку под давлением (продувку), протирку, закупоривание и/или заправку узла 602 печатающей головки для поддержания функциональных возможностей узла 602 печатающей головки и, в частности, сопел 608. Например, узел 604 станции технического обслуживания может включать в себя резиновый нож или скребок для очистки, который периодически проходит по узлу 602 печатающей головки, протирая и очищая сопла 608 от избытка чернил. Кроме того, узел 604 станции технического обслуживания может включать в себя колпачок, который закрывает узел 602 печатающей головки, защищая сопла 608 от пересыхания в периоды простоя. Кроме того, узел 604 станции технического обслуживания может включать в себя контейнер для сбора излишков чернил, в который узел 602 печатающей головки выбрасывает чернила в ходе промывок под давлением, гарантируя, что сосуд 612 поддерживает надлежащий уровень давления и текучести, и гарантируя, что сопла 608 не засорены и не текут. Функции узла 604 станции технического обслуживания могут включать в себя относительное перемещение между узлом 604 станции технического обслуживания и узлом 602 печатающей головки.

[0084] Электронный контроллер 620 осуществляет связь с узлом 602 печатающей головки через канал 603 связи, узлом 604 станции технического обслуживания через канал 605 связи, узлом 616 каретки через канал 617 связи и узлом 618 транспортировки носителей печати через канал 619 связи. В одном примере, когда узел 602 печатающей головки установлен в узле 616 каретки, электронный контроллер 620 и узел 602 печатающей головки могут осуществлять связь с помощью узла 616 каретки через канал 601 связи. Электронный контроллер 620 также может осуществлять связь с узлом 610 подачи чернил, благодаря чему в одной реализации можно обнаружить новый (или использованный) источник чернил.

[0085] Электронный контроллер 620 принимает данные 628 от главной системы, такой как компьютер, и может включать в себя память для временного хранения данных 628. Данные 628 могут отправляться в систему 600 выброса текучей среды по электронному, инфракрасному, оптическому или другому каналу передачи информации. Данные 628 представляют, например, документ и/или файл, подлежащий печати. Таким образом, данные 628 образуют задание на печать для системы 600 выброса текучей среды и включают в себя по меньшей мере одну команду и/или параметр команды задания на печать.

[0086] В одном примере электронный контроллер 620 обеспечивает управление узлом 602 печатающей головки, в том числе управление привязкой по времени выброса капель чернил из сопел 608. Таким образом электронный контроллер 620 задает рисунок выбрасываемых капель чернил, которые образуют знаки, символы и/или другие графические объекты или изображения на носителях 624 печати. Управление привязкой по времени, а значит рисунок выбрасываемых капель чернил определяется командами и/или параметрами команд задания на печать. В одном примере логическая и возбуждающая схема, образующая часть электронного контроллера 620, располагается на узле 602 печатающей головки. В другом примере логическая и возбуждающая схема, образующая часть электронного контроллера 620, располагается вне узла 602 печатающей головки.

[0087] Фиг. 13A-13D представляют собой блок-схемы последовательности операций, иллюстрирующие один пример способа 700 осуществления доступа к первой памяти и второй памяти устройства выброса текучей среды. В одном примере способ 700 может осуществляться системой 100 выброса текучей среды по фиг. 1. Как показано на фиг. 13A, на этапе 702 способ 700 включает в себя последовательное генерирование первого сигнала выбора и второго сигнала выбора. На этапе 704 способ 700 включает в себя разблокирование первого элемента памяти в ответ на первый сигнал выбора и первые данные на множестве линий первых данных. На этапе 706 способ 700 включает в себя разблокирование второго элемента памяти в ответ на второй сигнал выбора и вторые данные на линии вторых данных.

[0088] Как показано на фиг. 13B, на этапе 708 способ 700 может дополнительно включать в себя генерирование сигнала адреса. В этом случае разблокирование второго элемента памяти может включать в себя разблокирование второго элемента памяти в ответ на второй сигнал выбора, вторые данные на линии вторых данных и сигнал адреса.

[0089] Как показано на фиг. 13C, на этапе 710 способ 700 может дополнительно включать в себя генерирование сигнала на линии ID. На этапе 712 способ 700 может дополнительно включать в себя разблокирование устройства активации текучей среды в ответ на второй сигнал выбора и первый логический уровень на линии ID. В этом случае разблокирование второго элемента памяти может включать в себя разблокирование второго элемента памяти в ответ на второй сигнал выбора и второй логический уровень на линии ID.

[0090] Как показано на фиг. 13D, на этапе 714 способ 700 может дополнительно включать в себя осуществление доступа к первому элементу памяти через линию ID, когда первый элемент памяти разблокирован. На этапе 716 способ 700 может дополнительно включать в себя осуществление доступа ко второму элементу памяти через линию возбуждения, когда второй элемент памяти разблокирован.

[0091] Фиг. 14A-14B представляют собой блок-схемы последовательности операций, иллюстрирующие один пример способа 800 осуществления доступа к памяти устройства выброса текучей среды. В одном примере способ 800 может осуществляться системой 100 выброса текучей среды по фиг. 1. Как показано на фиг. 14A, на этапе 802 способ 800 включает в себя электрическое подключение, через первый переключатель, первой стороны каждого элемента памяти из множества элементов памяти к линии возбуждения в ответ на первый логический уровень на линии ID и электрическое отключение, через первый переключатель, первой стороны каждого элемента памяти из множества элементов памяти от линии возбуждения в ответ на второй логический уровень на линии ID. На этапе 804 способ 800 включает в себя электрическое подключение, через соответствующий второй переключатель из множества вторых переключателей, второй стороны соответствующего элемента памяти из множества элементов памяти к общему узлу в ответ на сигнал адреса.

[0092] В одном примере первый переключатель включает в себя первый транзистор, а множество вторых переключателей включает в себя множество вторых транзисторов. Как показано на фиг. 14B, на этапе 806 способ 800 может дополнительно включать в себя осуществление доступа к соответствующему элементу памяти из множества элементов памяти через линию возбуждения, когда соответствующий элемент памяти электрически подключен между линией возбуждения и общим узлом.

[0093] Фиг. 15A-15B представляют собой блок-схемы последовательности операций, иллюстрирующие другой пример способа 900 для осуществления доступа к памяти устройства выброса текучей среды. В одном примере способ 900 может быть реализован системой 100 выброса текучей среды по фиг. 1. Как показано на фиг. 15A, на этапе 902 способ 900 включает в себя генерирование сигнала ID на линии ID. На этапе 904 способ 900 включает в себя последовательное генерирование первого сигнала выбора и второго сигнала выбора. На этапе 906 способ 900 включает в себя фиксацию сигнала ID в ответ на первый сигнал выбора. На этапе 908 способ 900 включает в себя разблокирование элемента памяти в ответ на фиксированный сигнал ID, имеющий первый логический уровень. На этапе 910 способ 900 включает в себя осуществление доступа к элементу памяти через линию возбуждения в ответ на второй сигнал выбора, когда этот элемент памяти разблокирован.

[0094] В одном примере разблокирование элемента памяти включает в себя электрическое подключение элемента памяти к линии возбуждения в ответ на фиксированный сигнал ID, имеющий первый логический уровень. В другом примере фиксация сигнала ID включает в себя инвертирование сигнала ID и фиксацию инвертированного сигнала ID в ответ на первый сигнал выбора; а разблокирование элемента памяти включает в себя отключение тракта разряда, подключенного к элементу памяти, в ответ на фиксированный инвертированный сигнал ID, имеющий второй логический уровень.

[0095] Как показано на фиг. 15B, на этапе 912 способ 900 может дополнительно включать в себя разблокирование устройства активации текучей среды в ответ на сигнал ID, имеющий второй логический уровень. На этапе 914 способ 900 может дополнительно включать в себя активацию устройства активации текучей среды через линию возбуждения в ответ на второй сигнал выбора, когда устройство активации текучей среды разблокировано.

[0096] Хотя здесь были проиллюстрированы и описаны конкретные примеры, показанные и описанные, конкретные примеры могут быть замещены разнообразием альтернативных и/или эквивалентных реализаций без выхода за рамки объема настоящего раскрытия. Эта заявка предназначена охватывать любые адаптации или вариации рассмотренных здесь конкретных примеров. Поэтому предполагается, что это раскрытие ограничивается только формулой изобретения и ее эквивалентами.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОРЫ ДЛЯ ФОРСУНОК И ЭЛЕМЕНТОВ ПАМЯТИ | 2017 |

|

RU2747446C1 |

| ПЕЧАТАЮЩИЙ КОМПОНЕНТ СО СХЕМОЙ ПАМЯТИ | 2019 |

|

RU2778211C1 |

| ВХОДНЫЕ УПРАВЛЯЮЩИЕ СИГНАЛЫ, ПРОХОДЯЩИЕ ПО СИГНАЛЬНЫМ ПУТЯМ | 2016 |

|

RU2710691C1 |

| ПЕЧАТАЮЩИЙ КОМПОНЕНТ С МАТРИЦЕЙ ПАМЯТИ, ИСПОЛЬЗУЮЩИЙ ПУЛЬСИРУЮЩИЙ ТАКТОВЫЙ СИГНАЛ | 2019 |

|

RU2780707C1 |

| УСТРОЙСТВО ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ СО ВСТРОЕННЫМ ДАТЧИКОМ УРОВНЯ ЧЕРНИЛ | 2012 |

|

RU2635080C2 |

| ИНТЕГРАЛЬНЫЕ СХЕМЫ, ВКЛЮЧАЮЩИЕ В СЕБЯ ЗАПОМИНАЮЩИЕ ЯЧЕЙКИ | 2019 |

|

RU2779793C1 |

| КРИСТАЛЛ ДЛЯ ПЕЧАТАЮЩЕЙ ГОЛОВКИ | 2019 |

|

RU2778376C1 |

| ДОСТУП К БЛОКАМ ПАМЯТИ В БАНКЕ ПАМЯТИ | 2017 |

|

RU2748727C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА С АДРЕСНЫМИ ФОРМИРОВАТЕЛЯМИ ДЛЯ СТРУЙНОЙ МАТРИЦЫ | 2019 |

|

RU2780403C1 |

| ОСУЩЕСТВЛЕНИЕ ДОСТУПА К РЕГИСТРАМ УСТРОЙСТВ ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ | 2019 |

|

RU2776431C1 |

Интегральная схема для приведения в действие множества устройств активации текучей среды включает в себя множество линий первых данных, линию вторых данных, первый элемент памяти и второй элемент памяти. Первый элемент памяти разблокируется в ответ на первые данные на множестве линий первых данных. Второй элемент памяти разблокируется в ответ на вторые данные на линии вторых данных. 2 н. и 11 з.п. ф-лы, 15 ил.

1. Струйный картридж, содержащий матрицу печатающей головки, включающую в себя интегральную схему для приведения в действие множества устройств активации текучей среды, при этом интегральная схема содержит:

линию идентификации (ID);

линию первого выбора;

линию второго выбора;

множество линий первых данных;

линию вторых данных;

первый элемент памяти, разблокируемый в ответ на первый логический уровень на линии первого выбора и первые данные на множестве линий первых данных;

второй элемент памяти, разблокируемый в ответ на вторые данные на линии вторых данных, первый логический уровень на линии второго выбора и первый логический уровень на линии ID;

устройство активации текучей среды, разблокируемое в ответ на первый логический уровень на линии второго выбора и второй логический уровень на линии ID; и

линию возбуждения, электрически подключенную ко второму элементу памяти и устройству активации текучей среды;

при этом доступ к первому элементу памяти осуществляется через линию ID при разблокированном первом элементе памяти;

при этом доступ ко второму элементу памяти осуществляется через линию возбуждения при разблокированном втором элементе памяти; и

при этом устройство активации текучей среды активируется через линию возбуждения при разблокированном устройстве активации текучей среды.

2. Струйный картридж по п. 1, дополнительно содержащий тракт разряда, электрически подключенный между вторым элементом памяти и общим узлом или узлом заземления, причем тракт разряда блокируется в ответ на первый логический уровень на линии ID и разблокируется в ответ на второй логический уровень на линии ID.

3. Струйный картридж по п. 1 или 2, в котором первый элемент памяти содержит элемент стираемой программируемой постоянной памяти, а второй элемент памяти содержит программируемую плавкую перемычку.

4. Струйный картридж по любому из пп. 1-3, дополнительно содержащий:

декодер сдвигового регистра для разблокирования первого элемента памяти в ответ на первые данные на множестве линий первых данных.

5. Струйный картридж по любому из пп. 1-4, дополнительно содержащий:

транзистор для разблокирования второго элемента памяти в ответ на вторые данные на линии вторых данных.

6. Струйный картридж по п. 5, дополнительно содержащий:

дополнительный транзистор для разблокирования второго элемента памяти в ответ на первый логический уровень на линии ID, причем упомянутый транзистор расположен с первой стороны второго элемента памяти, а упомянутый дополнительный транзистор расположен со второй стороны второго элемента памяти, противоположной первой стороне второго элемента памяти.

7. Струйный картридж по любому из пп. 1-6, в котором первый элемент памяти содержит энергонезависимый элемент памяти, и второй элемент памяти содержит энергонезависимый элемент памяти.

8. Струйный картридж по любому из пп. 1-7, дополнительно содержащий:

генератор адресов для генерирования сигнала адреса;

при этом второй элемент памяти должен разблокироваться в ответ на сигнал адреса.

9. Струйный картридж по любому из пп. 1-8, дополнительно содержащий:

множество транзисторов для разблокирования первого элемента памяти в ответ на первые данные на множестве линий первых данных.

10. Струйный картридж по любому из пп. 1-9, дополнительно содержащий:

транзистор, соединенный с линией второго выбора и с трактом разряда, для разблокирования и блокирования тракта разряда в ответ на различные логические уровни на линии второго выбора.

11. Струйный картридж по любому из пп. 1-10, в котором первые данные и вторые данные полностью независимы друг от друга.

12. Способ осуществления доступа к первой памяти и второй памяти устройства выброса текучей среды у матрицы печатающей головки струйного принтера, содержащий:

последовательное генерирование первого сигнала выбора и второго сигнала выбора;

генерирование сигнала на линии ID;

разблокирование первого элемента памяти в ответ на первый сигнал выбора и первые данные на множестве линий первых данных;

разблокирование устройства активации текучей среды в ответ на второй сигнал выбора и первый логический уровень на линии ID;

разблокирование второго элемента памяти в ответ на второй сигнал выбора, второй логический уровень на линии ID и вторые данные на линии вторых данных;

осуществление доступа к первому элементу памяти через линию ID при разблокированном первом элементе памяти;

осуществление доступа ко второму элементу памяти через линию возбуждения при разблокированном втором элементе памяти; и

активирование устройства активации текучей среды через линию возбуждения при разблокированном устройстве активации текучей среды.

13. Способ по п. 12, дополнительно содержащий:

генерирование сигнала адреса,

причем разблокирование второго элемента памяти содержит разблокирование второго элемента памяти в ответ на второй сигнал выбора, вторые данные на линии вторых данных и сигнал адреса.

| WO 2019009903 A1, 10.01.2019 | |||

| WO 2019009904 A1, 10.01.2019 | |||

| US 2014320558 A1, 30.10.2014. |

Авторы

Даты

2022-08-31—Публикация

2019-04-19—Подача