Уровень техники

[0001] Струйная печатающая система, в качестве одного примера системы выброса текучей среды, может включать в себя печатающую головку, компонент подачи чернил, который подает жидкие чернила в печатающую головку, и электронный контроллер, который управляет печатающей головкой. Печатающая головка, в качестве одного примера устройства выброса текучей среды, выбрасывает капли чернил через множество сопел или отверстий и к носителю для печати, такому как лист бумаги, с тем чтобы печатать на носителе для печати. В некоторых примерах, отверстия размещаются в по меньшей мере одной колонке или массиве таким образом, что надлежащим образом упорядоченный выброс чернил из отверстий приводит к тому, что знаки или другие изображения печатаются на носителе для печати по мере того, как печатающая головка и носитель для печати перемещаются относительно друг друга.

Краткое описание чертежей

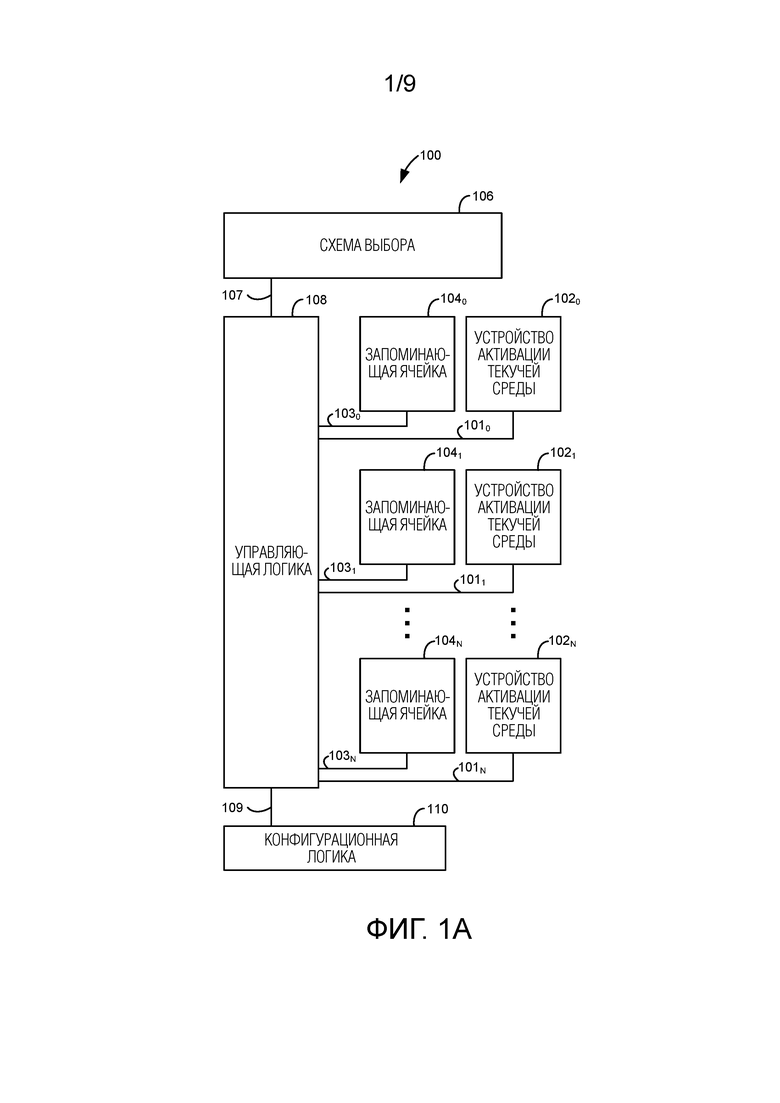

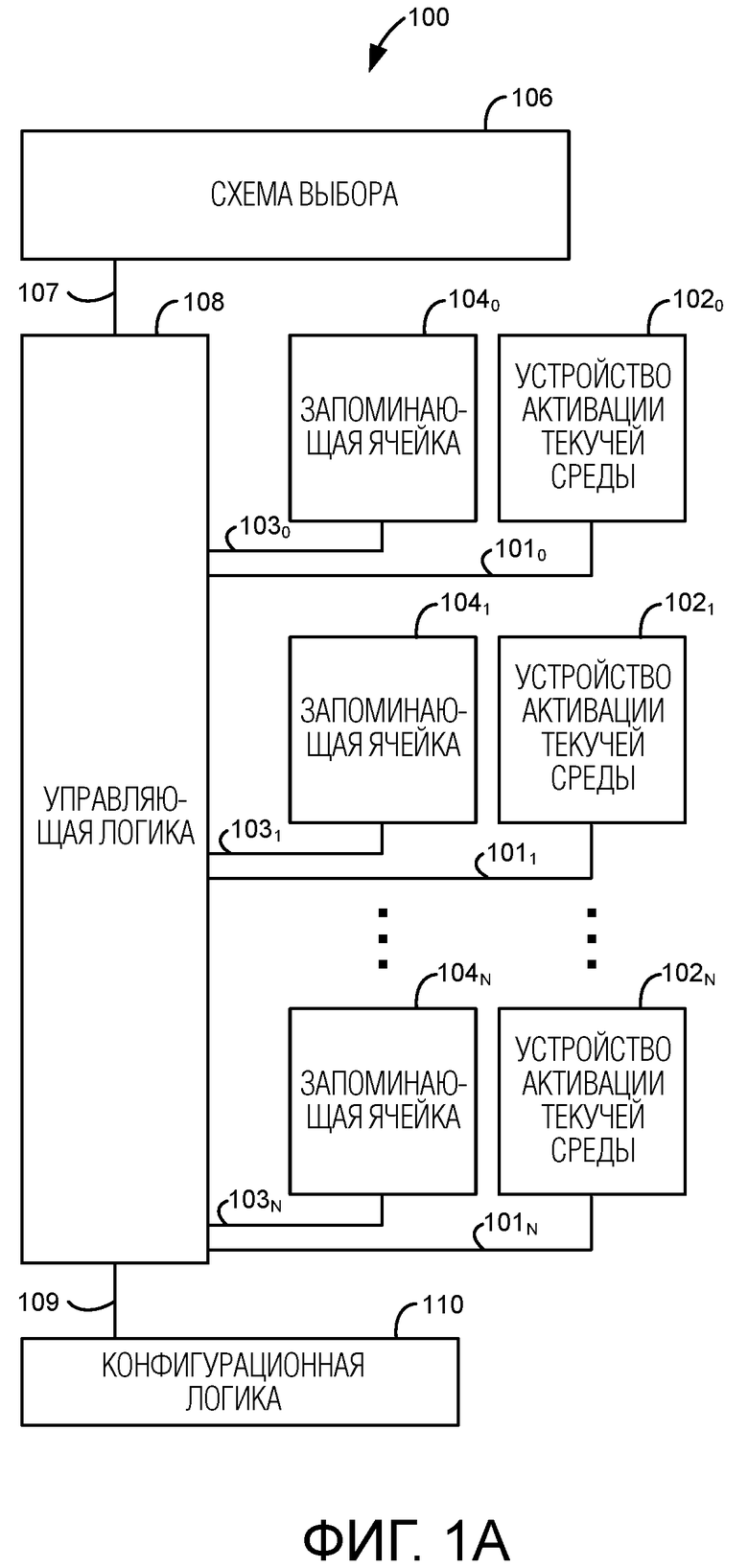

[0002] Фиг. 1A является блок-схемой, иллюстрирующей один пример интегральной схемы для возбуждения множества устройств активации текучей среды.

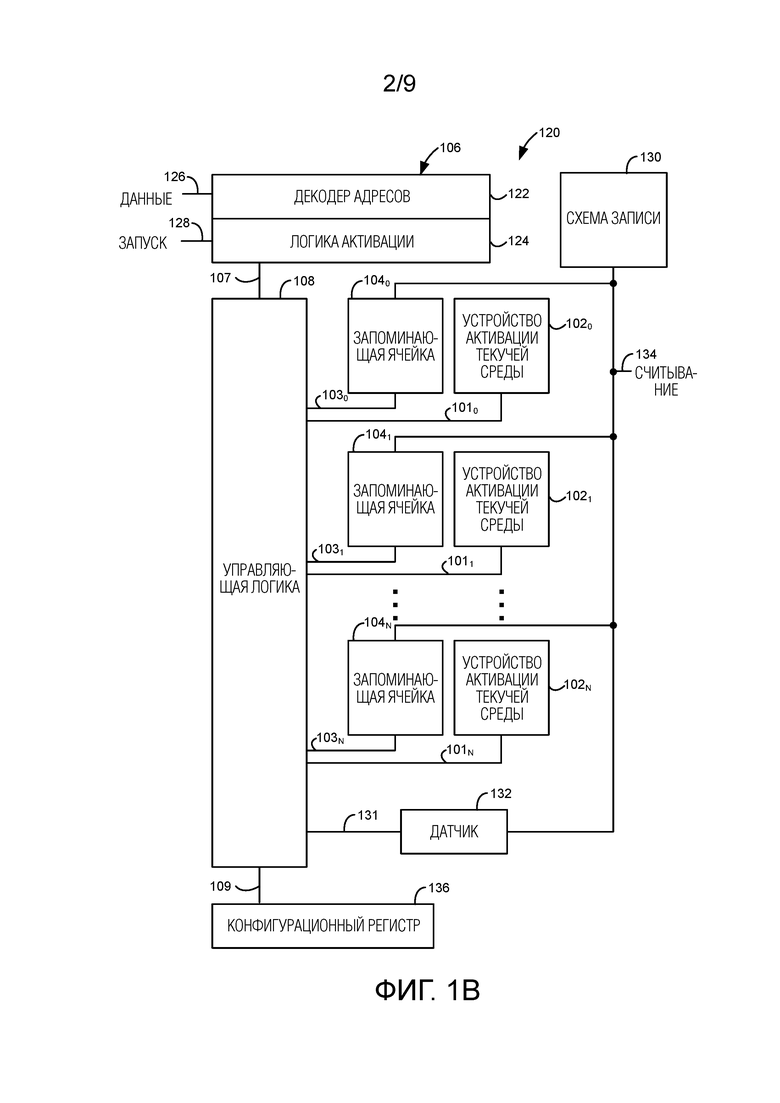

[0003] Фиг. 1B является блок-схемой, иллюстрирующей другой пример интегральной схемы для возбуждения множества устройств активации текучей среды.

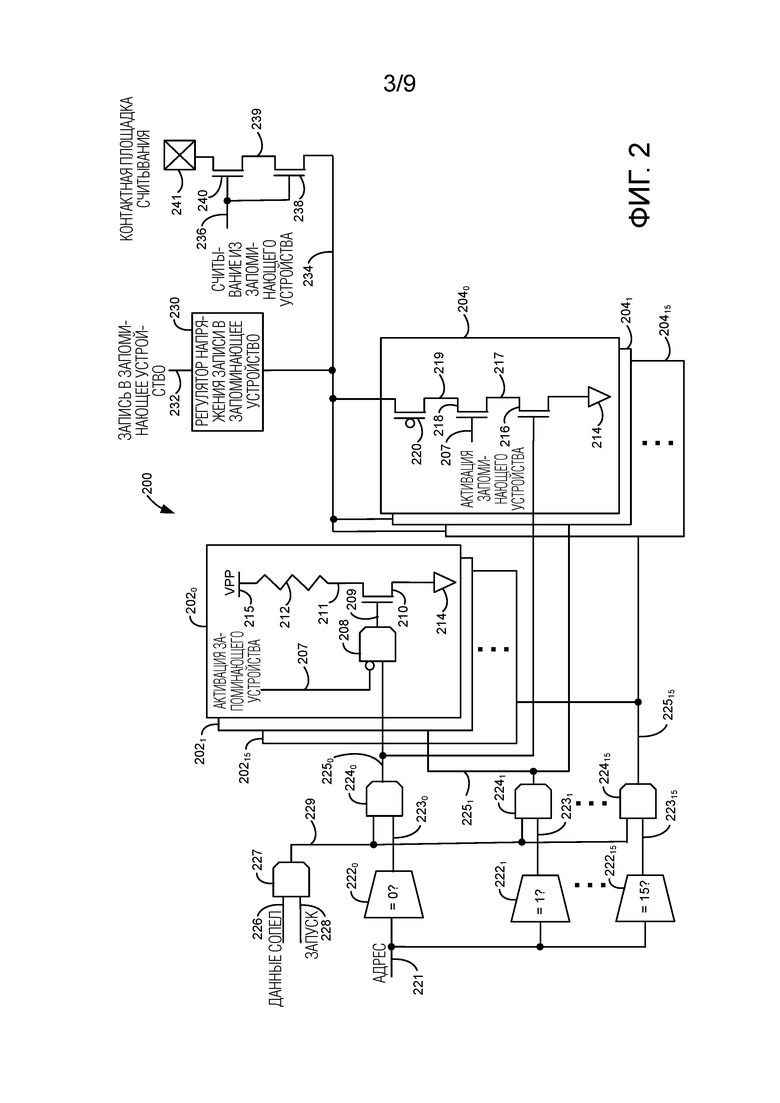

[0004] Фиг. 2 является принципиальной схемой, иллюстрирующей один пример схемы для возбуждения множества устройств активации текучей среды или осуществления доступа к соответствующим запоминающим ячейкам.

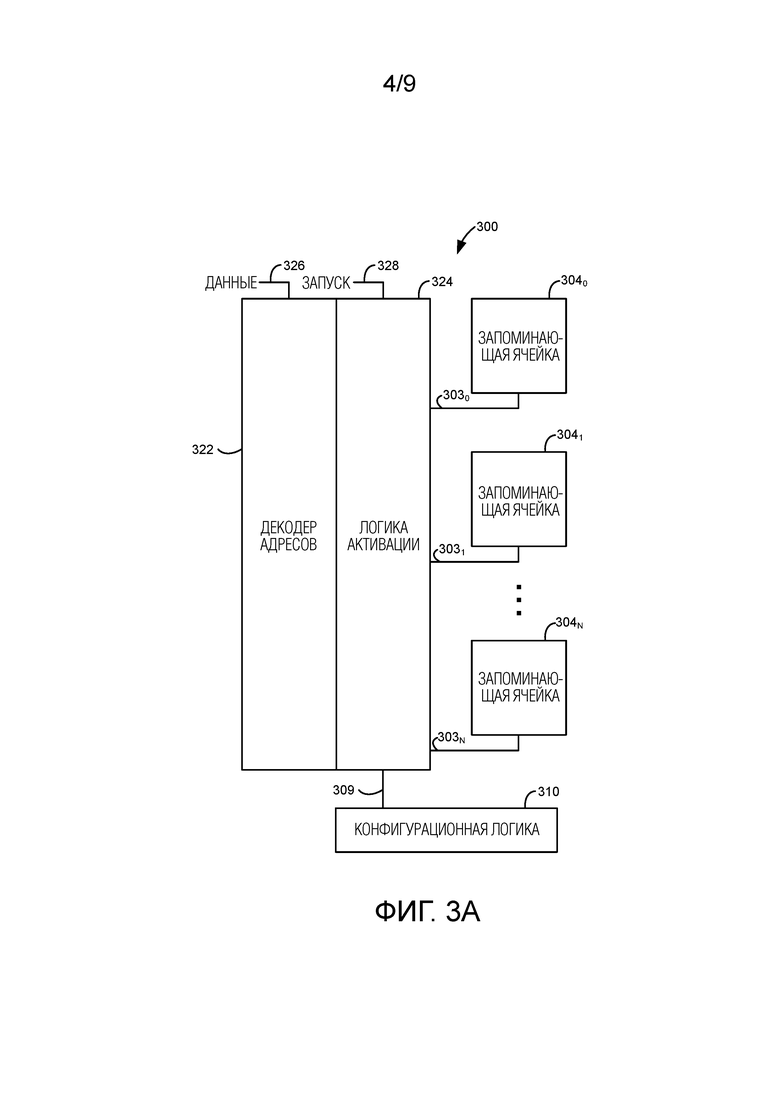

[0005] Фиг. 3A является блок-схемой, иллюстрирующей один пример интегральной схемы для осуществления доступа к запоминающему устройству, ассоциированному с устройством выброса текучей среды.

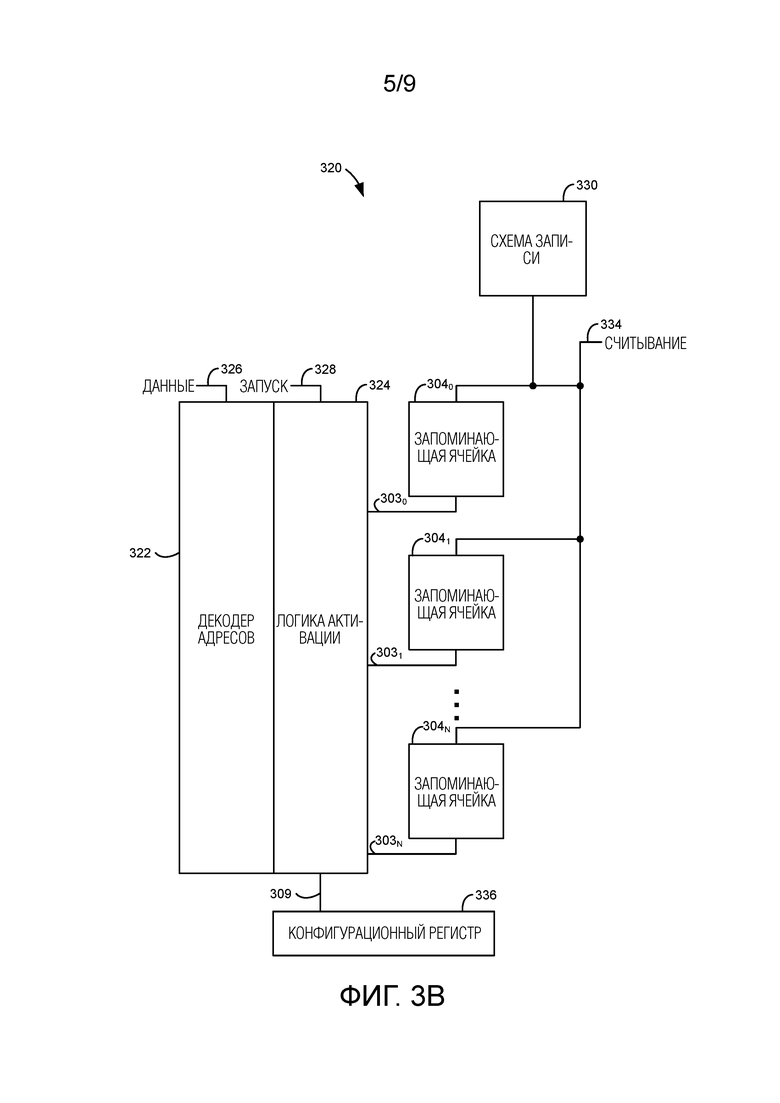

[0006] Фиг. 3B является блок-схемой, иллюстрирующей другой пример интегральной схемы для осуществления доступа к запоминающему устройству, ассоциированному с устройством выброса текучей среды.

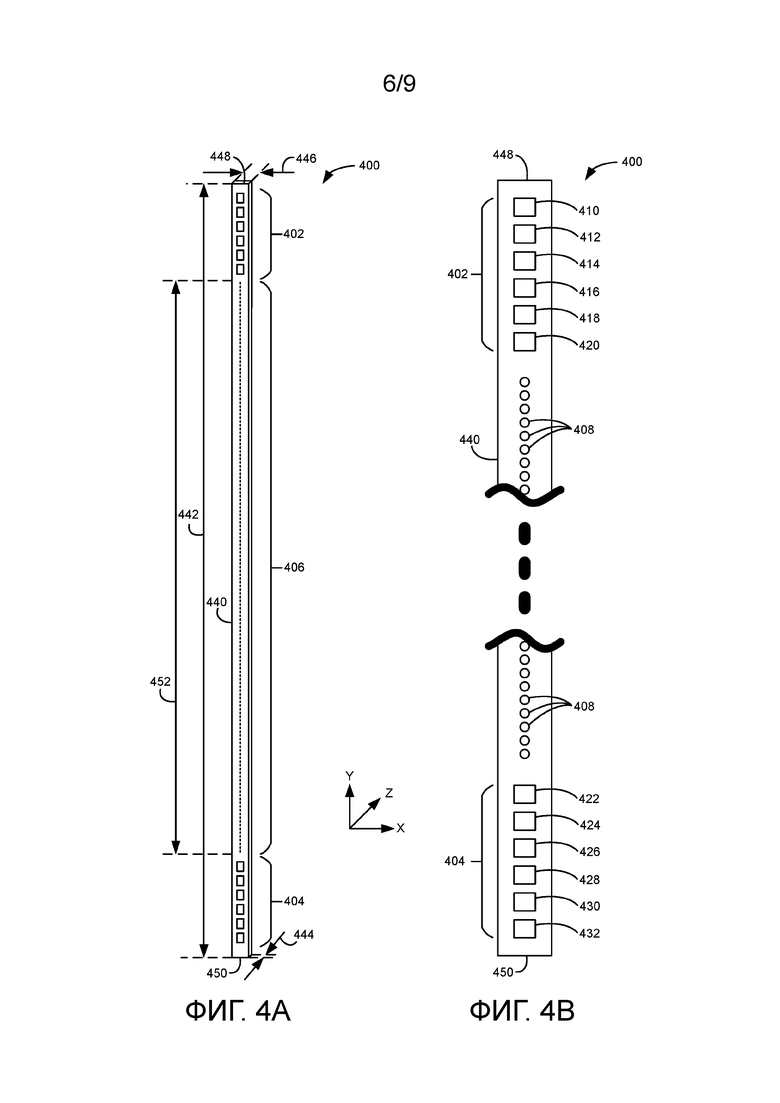

[0007] Фиг. 4A и 4B иллюстрируют один пример матрицы выброса текучей среды.

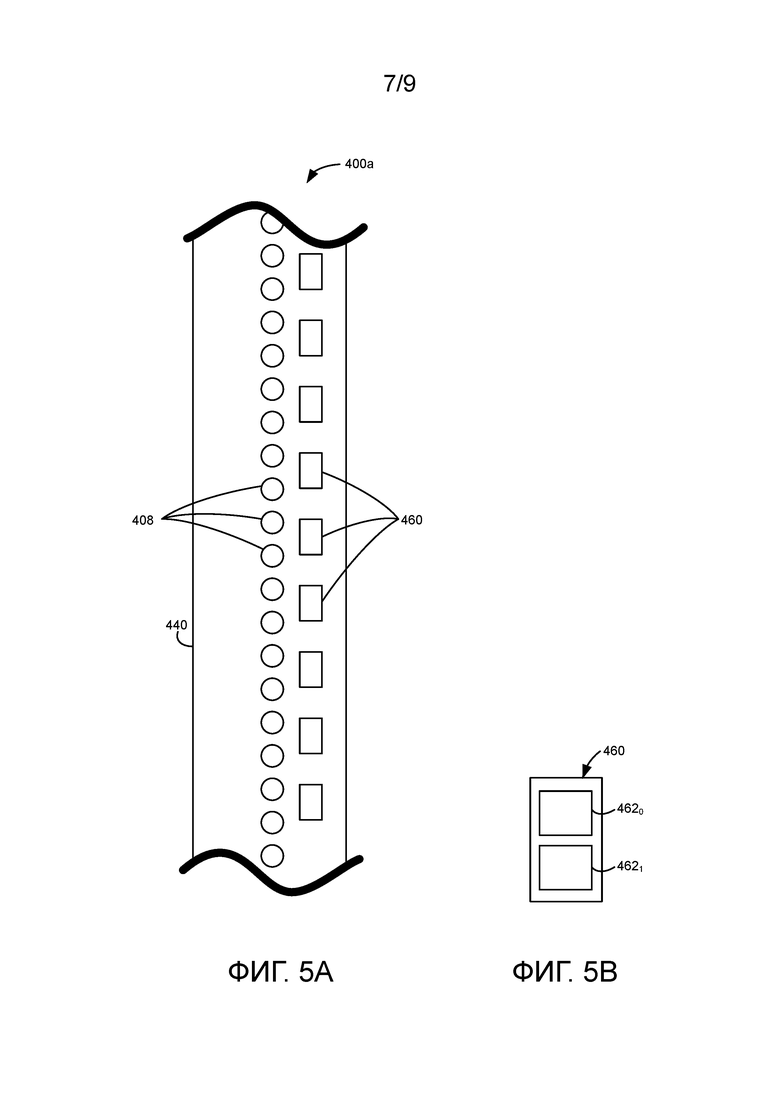

[0008] Фиг. 5A иллюстрирует укрупненный вид одного примера участка матрицы выброса текучей среды.

[0009] Фиг. 5B является блок-схемой, иллюстрирующей один пример группы запоминающих ячеек матрицы выброса текучей среды по фиг. 5A.

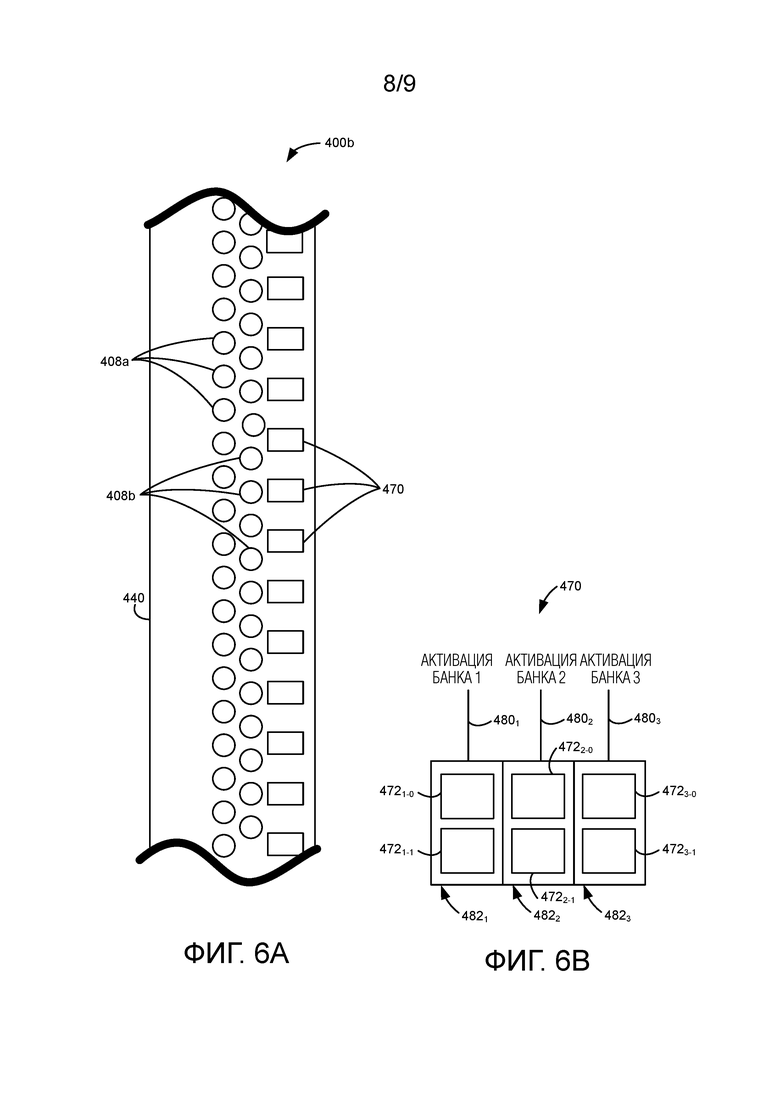

[0010] Фиг. 6A иллюстрирует укрупненный вид другого примера участка матрицы выброса текучей среды.

[0011] Фиг. 6B является блок-схемой, иллюстрирующей один пример группы запоминающих ячеек матрицы выброса текучей среды по фиг. 6A.

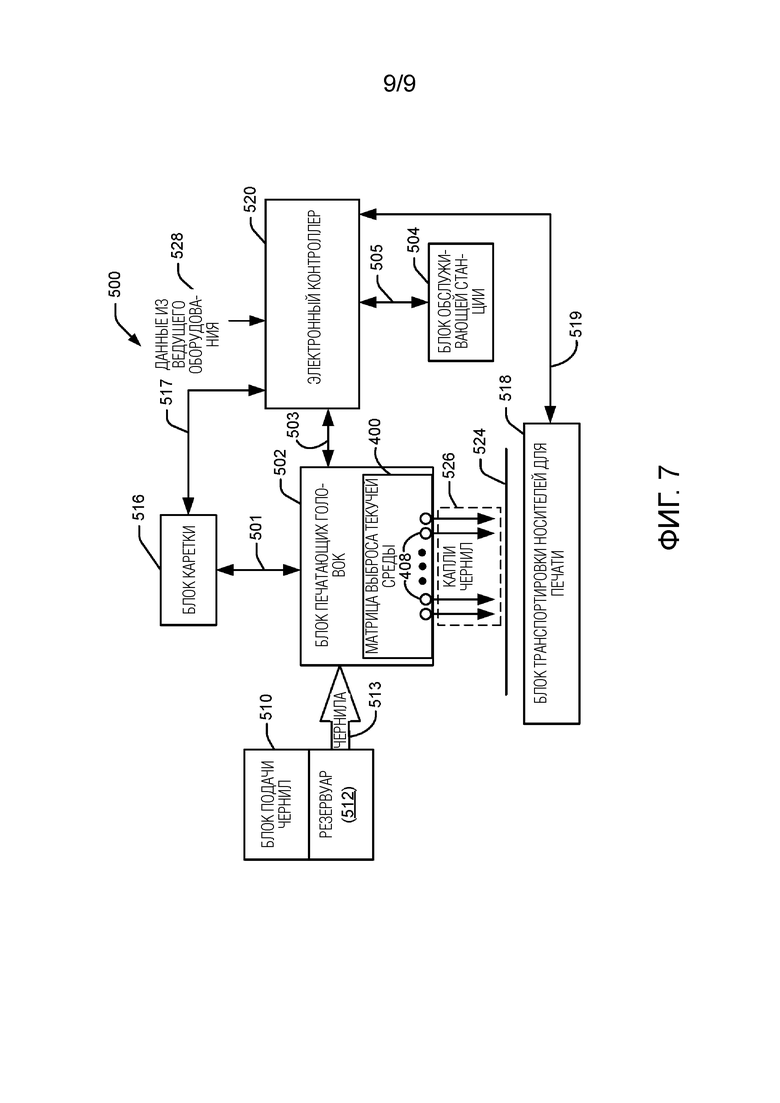

[0012] Фиг. 7 является блок-схемой, иллюстрирующей один пример системы выброса текучей среды.

Подробное описание изобретения

[0013] В нижеприведенном подробном описании следует обратиться к прилагаемым чертежам, которые составляют часть настоящего документа, и на которых показаны в качестве иллюстрации конкретные примеры, в которых может осуществляться на практике раскрытие. Следует понимать, что другие примеры могут использоваться, и что структурные или логические изменения могут вноситься без отступления от объема настоящего раскрытия. В силу этого нижеприведенное подробное описание не должно рассматриваться в ограничивающем смысле, и объем настоящего раскрытия задается только посредством прилагаемой формулы изобретения. Следует понимать, что признаки различных примеров, описанных в данном документе, могут комбинироваться, частично или полностью, между собой, если прямо не указано иное.

[0014] Матрицы выброса текучей среды, к примеру термографические струйные (TIJ) матрицы, могут представлять собой узкие и длинные фрагменты кремния. Площадь кремния, используемая матрицей, связана с затратами на матрицу таким образом, что любая функциональность, которая может удаляться из матрицы, должна удаляться или модифицироваться, чтобы иметь несколько целей, если это возможно. Энергонезависимое запоминающее устройство (NVM) может использоваться на матрице, чтобы переносить информацию из матрицы в принтер, такую как тепловое поведение, смещения, информация региона, цветовая карта, число сопел и т.д. Помимо этого, NVM также может использоваться для того, чтобы переносить информацию из принтера в матрицу, к примеру, измеритель расхода чернил, информация работоспособности сопел и т.д. Запоминающие устройства могут состоять из элементов хранения данных, считывающих/записывающих мультиплексоров и схем активации/адресации. Для небольших запоминающих устройств, схемы, не связанные с хранением данных, могут составлять большой процент от общей площади, используемой посредством запоминающего устройства, что обуславливает то, что небольшие запоминающие устройства являются очень неэффективными в отношении площади.

[0015] Соответственно, в данном документе раскрываются интегральные схемы (например, матрицы выброса текучей среды), включающие в себя запоминающие ячейки, соответствующие устройствам активации текучей среды. Идентичная схемная логика используется для того, чтобы либо активировать выбранные устройства активации текучей среды, либо осуществлять доступ к выбранным соответствующим запоминающим ячейкам на основе принимаемых адресов и данных сопел. Данные, сохраненные в каждой запоминающей ячейке, могут считываться из интегральной схемы через единственную контактную площадку. Запоминающие ячейки могут распределяться по длине интегральной схемы рядом с соответствующими устройствами активации текучей среды.

[0016] При использовании в данном документе, сигнал "высоким с логическим уровнем" представляет собой логическую "единицу" или сигнал "включения" либо сигнал, имеющий напряжение, примерно равное логической электроэнергии, подаваемой в интегральную схему (например, приблизительно между 1,8 В и 15 В, к примеру, 5,6 В). При использовании в данном документе, сигнал "низким с логическим уровнем" представляет собой логический "нуль" или сигнал "выключения" либо сигнал, имеющий напряжение, примерно равное возврату через землю логической электроэнергии для логической электроэнергии, подаваемой в интегральную схему (например, приблизительно 0 В).

[0017] Фиг. 1A является блок-схемой, иллюстрирующей один пример интегральной схемы 100 для возбуждения множества устройств активации текучей среды. Интегральная схема 100 включает в себя множество устройств 1020-102N активации текучей среды, где "N" является любым подходящим числом устройств активации текучей среды. Интегральная схема 100 также включает в себя множество запоминающих ячеек 1040-104N, схему 106 выбора, управляющую логику 108 и конфигурационную логику 110. Каждое устройство 1020-102N активации текучей среды электрически соединяется с управляющей логикой 108 через тракт 1010-101N передачи сигналов, соответственно. Каждая запоминающая ячейка 1040-104N электрически соединяется с управляющей логикой 108 через тракт 1030-103N передачи сигналов, соответственно. Управляющая логика 108 электрически соединяется со схемой 106 выбора через тракт 107 передачи сигналов и с конфигурационной логикой 110 через тракт 109 передачи сигналов.

[0018] В одном примере, каждое устройство 1020-102N активации текучей среды включает в себя сопло или насос текучей среды, чтобы выбрасывать капли текучей среды. Каждая запоминающая ячейка 1040-104N соответствует устройству 1020-102N активации текучей среды, соответственно. В одном примере, каждая запоминающая ячейка 1040-104N включает в себя энергонезависимую запоминающую ячейку (например, транзистор с плавающим затвором, программируемую ячейку с плавкой перемычкой и т.д.). Схема 106 выбора выбирает устройства 1020-102N активации текучей среды и запоминающие ячейки 1040-104N, соответствующие выбранным устройствам 1020-102N активации текучей среды. Схема 106 выбора может включать в себя декодер адресов, логику активации и/или другие подходящие логические схемы для выбора устройств 1020-102N активации текучей среды и соответствующих запоминающих ячеек 1040-104N в ответ на сигнал адреса и сигнал данных сопел. Конфигурационная логика 110 активирует или деактивирует доступ ко множеству запоминающих ячеек 1040-104N. Конфигурационная логика 110 может включать в себя запоминающее устройство или другие подходящие логические схемы для активации или деактивации доступа ко множеству запоминающих ячеек 1040-104N.

[0019] Управляющая логика 108 либо активирует выбранные устройства 1020-102N активации текучей среды, либо осуществляет доступ к запоминающим ячейкам 1040-104N, соответствующим выбранным устройствам активации текучей среды, на основе состояния конфигурационной логики 110. Управляющая логика 108 может включать в себя микропроцессор, специализированную интегральную схему (ASIC) или другие подходящие логические схемы для управления работой интегральной схемы 100. Хотя схема 106 выбора, управляющая логика 108 и конфигурационная логика 110 проиллюстрированы как отдельные блоки на фиг. 1A, в других примерах, схема 106 выбора, управляющая логика 108 и/или конфигурационная логика 110 могут комбинироваться в единый блок или в другое число блоков.

[0020] Фиг. 1B является блок-схемой, иллюстрирующей другой пример интегральной схемы 120 для возбуждения множества устройств активации текучей среды. Интегральная схема 120 включает в себя множество устройств 1020-102N активации текучей среды, множество запоминающих ячеек 1040-104N, схему 106 выбора и управляющую логику 108. Помимо этого, интегральная схема 120 включает в себя схему 130 записи, датчик 132 и конфигурационный регистр 136. В одном примере, конфигурационная логика 110 интегральной схемы 100 по фиг. 1A включает в себя конфигурационный регистр 136.

[0021] В этом примере, схема 106 выбора включает в себя декодер 122 адресов и логику 124 активации. Декодер 122 адресов принимает адреса и данные через интерфейс 126 данных. Декодер 122 адресов электрически соединяется с логикой 124 активации. Логика 124 активации принимает сигнал запуска через интерфейс 128 запуска. Каждая запоминающая ячейка 1040-104N электрически соединяется со схемой 130 записи через интерфейс 134 считывания. Датчик 132 электрически соединяется с управляющей логикой 108 через тракт 131 передачи сигналов и с интерфейсом 134 считывания.

[0022] Декодер 122 адресов выбирает устройства 1020-102N активации текучей среды и запоминающие ячейки 1040-104N, соответствующие выбранным устройствам 1020-102N активации текучей среды, в ответ на адрес. Адрес может приниматься через интерфейс 126 данных. Логика 124 активации активирует выбранные устройства 1020-102N активации текучей среды и запоминающие ячейки 1040-104N, соответствующие выбранным устройствам 1020-102N активации текучей среды, на основе сигнала данных и сигнала запуска. Сигнал данных может включать в себя данные сопел, указывающие то, какое устройство(а) активации текучей среды для предоставленного адреса должно выбираться. Сигнал данных может приниматься через интерфейс 126 данных. Сигнал запуска указывает то, когда выбранные устройства активации текучей среды должны активироваться (т.е. запускаться), либо то, когда к соответствующим запоминающим ячейкам должен осуществляться доступ. Сигнал запуска может приниматься через интерфейс 128 запуска. Каждый из интерфейса 126 данных, интерфейса 128 запуска и интерфейса 134 считывания может представлять собой контактную площадку, штырьковый вывод, контактный столбик, провод или другой подходящий электрический интерфейс для передачи сигналов в и/или из интегральной схемы 120. Каждый из интерфейсов 126, 128 и 134 может электрически соединяться с системой выброса текучей среды (например, ведущим печатающим оборудованием, таким как система 500 выброса текучей среды, которая описывается ниже со ссылкой на фиг. 7).

[0023] Конфигурационный регистр 136 сохраняет данные для того, чтобы активировать или деактивировать доступ ко множеству запоминающих ячеек 1040-104N. Управляющая логика 108 либо активирует выбранные устройства 1020-102N активации текучей среды, либо осуществляет доступ к запоминающим ячейкам 1040-104N, соответствующим выбранным устройствам 1020-102N активации текучей среды, на основе данных, сохраненных в конфигурационном регистре 136. В одном примере, конфигурационный регистр 136 также сохраняет данные для того, чтобы активировать доступ для записи или доступ для считывания ко множеству запоминающих ячеек 1040-104N. В другом примере, конфигурационный регистр 136 также сохраняет данные для того, чтобы активировать или деактивировать датчик 132.

[0024] Конфигурационный регистр 136 может представлять собой запоминающее устройство (например, энергонезависимое запоминающее устройство, сдвиговый регистр и т.д.) и может включать в себя любое подходящее число битов (например, 4-24 бита, к примеру, 12 битов). В определенных примерах, конфигурационный регистр 136 также может сохранять конфигурационные данные для тестирования интегральной схемы 120, обнаружения трещин внутри подложки интегральной схемы 120, активации таймеров интегральной схемы 120, задания аналоговых задержек интегральной схемы 120, признания допустимыми операций интегральной схемы 120 либо для конфигурирования других функций интегральной схемы 120.

[0025] Данные, сохраненные в запоминающих ячейках 1040-104N, могут считываться через интерфейс 134 считывания, когда к выбранным запоминающим ячейкам 1040-104N осуществлен доступ посредством управляющей логики 108. Помимо этого, схема 130 записи может записывать данные в выбранные запоминающие ячейки, когда к выбранным запоминающим ячейкам 1040-104N осуществлен доступ посредством управляющей логики 108. Датчик 132 может представлять собой прибор с p-n-переходом (например, тепловой диод), резистивное устройство (например, детектор трещин) или другое подходящее устройство для считывания состояния интегральной схемы 120. Датчик 132 может считываться через интерфейс 134 считывания.

[0026] Фиг. 2 является принципиальной схемой, иллюстрирующей один пример схемы 200 для возбуждения множества устройств активации текучей среды или осуществления доступа к соответствующим запоминающим ячейкам. В одном примере, схема 200 представляет собой часть интегральной схемы 100 по фиг. 1A или интегральной схемы 120 по фиг. 1B. Схема 200 иллюстрирует одну группу 16 устройств активации текучей среды и соответствующую группу 16 запоминающих ячеек. Интегральная схема, к примеру, интегральная схема 100 по фиг. 1A или интегральная схема 120 по фиг. 1B, может включать в себя любое подходящее число групп устройств активации текучей среды и соответствующих запоминающих ячеек. Хотя группа из 16 устройств активации и соответствующих запоминающих ячеек проиллюстрирована на фиг. 2, в других примерах число устройств активации текучей среды и соответствующих запоминающих ячеек в каждой группе может варьироваться.

[0027] Схема 200 включает в себя множество устройств 2020-20215 активации текучей среды, множество запоминающих ячеек 2040-20415, декодер адресов, включающий в себя логические вентили 2220-22215, логику активации, включающую в себя логические вентили 227 и 2240-22415, схему записи, включающую в себя регулятор 230 напряжения записи в запоминающее устройство, транзисторы 238 и 240 и контактную (т.е. считывания) площадку 241. Первый ввод логического вентиля 227 принимает данные сопел через тракт 226 передачи сигналов данных сопел. Второй ввод логического вентиля 227 принимает сигнал запуска через тракт 228 передачи сигналов запуска. Вывод логического вентиля 227 электрически соединяется с первым вводом каждого логического вентиля 2240-22415 через тракт 229 передачи сигналов. Ввод каждого логического вентиля 2220-22215 принимает сигнал адреса через тракт 221 передачи сигналов адреса. Вывод каждого логического вентиля 2220-22215 электрически соединяется со вторым вводом каждого логического вентиля 2240-22415 через тракт 2230-22315 передачи сигналов, соответственно. Вывод каждого логического вентиля 2240-22415 электрически соединяется с устройством 2020-20215 активации текучей среды и с запоминающей ячейкой 2040-20415 через тракт 2250-22515 передачи сигналов, соответственно.

[0028] Каждое устройство 2020-20215 активации текучей среды включает в себя логический вентиль 208, транзистор 210 и запускающий резистор 212. Хотя устройство 2020 активации текучей среды проиллюстрировано и описано в данном документе, другие устройства 2021-20215 активации текучей среды включают в себя аналогичную схему. Первый ввод логического вентиля 208 электрически соединяется с трактом 2250 передачи сигналов. Второй ввод (инвертированный) логического вентиля 208 принимает сигнал активации запоминающего устройства через тракт 207 передачи сигналов активации запоминающего устройства. Вывод логического вентиля 208 электрически соединяется с затвором транзистора 210 через тракт 209 передачи сигналов. Одна сторона тракта "исток-сток" транзистора 210 электрически соединяется с общим или заземляющим узлом 214. Другая сторона тракта "исток-сток" транзистора 210 электрически соединяется с одной стороной запускающего резистора 212 через тракт 211 передачи сигналов. Другая сторона запускающего резистора 212 электрически соединяется с узлом 215 питающего напряжения (например, VPP).

[0029] Каждая запоминающая ячейка 2040-20415 включает в себя транзисторы 216 и 218 и транзистор 220 с плавающим затвором. Хотя запоминающая ячейка 2040 проиллюстрирована и описана в данном документе, другие запоминающие ячейки 2041-20415 включают в себя аналогичную схему. Затвор транзистора 216 электрически соединяется с трактом 2250 передачи сигналов. Одна сторона тракта "исток-сток" транзистора 216 электрически соединяется с общим или заземляющим узлом 214. Другая сторона тракта "исток-сток" транзистора 216 электрически соединяется с одной стороной тракта "исток-сток" транзистора 218 через тракт 217 передачи сигналов. Затвор транзистора 218 принимает сигнал активации запоминающего устройства через тракт 207 передачи сигналов активации запоминающего устройства. Другая сторона тракта "исток-сток" транзистора 218 электрически соединяется с одной стороной тракта "исток-сток" транзистора 220 с плавающим затвором через тракт 219 передачи сигналов. Другая сторона тракта "исток-сток" транзистора 220 с плавающим затвором электрически соединяется с регулятором 230 напряжения записи в запоминающее устройство и одной стороной тракта "исток-сток" транзистора 238 через тракт 234 передачи сигналов.

[0030] Регулятор 230 напряжения записи в запоминающее устройство принимает сигнал записи в запоминающее устройство через тракт 232 передачи сигналов записи в запоминающее устройство. Затвор транзистора 238 и затвор транзистора 240 принимают сигнал считывания из запоминающего устройства через тракт 236 передачи сигналов считывания из запоминающего устройства. Другая сторона тракта "исток-сток" транзистора 238 электрически соединяется с одной стороной тракта "исток-сток" транзистора 240 через тракт 239 передачи сигналов. Другая сторона тракта "исток-сток" транзистора 240 электрически соединяется с площадкой 241 считывания.

[0031] Сигнал данных сопел на тракте 226 передачи сигналов данных сопел, сигнал запуска на тракте 228 передачи сигналов запуска и сигнал адреса на тракте 221 передачи сигналов адреса используются для того, чтобы активировать устройство 2020-20215 активации текучей среды или соответствующую запоминающую ячейку 2040-20415. Сигнал активации запоминающего устройства на тракте 207 передачи сигналов активации запоминающего устройства определяет то, активируется или нет устройство 2020-20215 активации текучей среды, либо то, осуществляется или нет к соответствующей запоминающей ячейке 2040-20415 доступ. В ответ на сигнал активации запоминающего устройства с высоким логическим уровнем, транзистор 218 включается, чтобы обеспечивать доступ к запоминающим ячейкам 2040-20415. Помимо этого, в ответ на сигнал активации запоминающего устройства с высоким логическим уровнем, логический вентиль 208 выводит сигнал с низким логическим уровнем, чтобы выключать транзистор 210 для того, чтобы предотвращать запуск устройств 2020-20215 активации текучей среды в ответ на сигнал запуска, передаваемый в тракты 2250-22515 передачи сигналов. В ответ на сигнал активации запоминающего устройства с низким логическим уровнем, транзистор 218 выключается, чтобы деактивировать доступ к запоминающим ячейкам 2040-20415. Помимо этого, в ответ на сигнал активации запоминающего устройства с низким логическим уровнем, логический вентиль 208 обеспечивает возможность сигналам запуска, передаваемым в тракты 2250-22515 передачи сигналов, запускать устройства 2020-20215 активации текучей среды. В одном примере, сигнал активации запоминающего устройства основан на бите данных, сохраненном в конфигурационном регистре, таком как конфигурационный регистр 136 по фиг. 1B. В другом примере, сигнал активации запоминающего устройства основан на бите данных, принимаемом посредством схемы 200, наряду с адресом и данными сопел, которые используются посредством конфигурационной логики, такой как конфигурационная логика 110 по фиг. 1A, для того, чтобы активировать или деактивировать запоминающие ячейки 2040-20415.

[0032] Сигнал данных сопел указывает то, должны ли выбираться устройства 2020-20215 активации текучей среды или соответствующие запоминающие ячейки 2040-20415. В одном примере, сигнал данных сопел включает в себя сигнал с высоким логическим уровнем, чтобы выбирать устройства 2020-20215 активации текучей среды или соответствующие запоминающие ячейки 2040-20415 и сигнал с низким логическим уровнем, чтобы отменять выбор устройств 2020-20215 активации текучей среды или соответствующих запоминающих ячеек 2040-20415. В ответ на сигнал данных сопел с высоким логическим уровнем, логический вентиль 227 передает сигнал с высоким логическим уровнем в тракт 229 передачи сигналов в ответ на сигнал запуска с высоким логическим уровнем. В ответ на сигнал данных сопел с низким логическим уровнем или сигнал запуска с низким логическим уровнем, логический вентиль 227 передает сигнал с низким логическим уровнем в тракт 229 передачи сигналов.

[0033] Сигнал адреса выбирает одно из устройств 2020-20215 активации текучей среды или соответствующих запоминающих ячеек 2040-20415. В ответ на сигнал адреса, один из логических вентилей 2220-22215 передает сигнал с высоким логическим уровнем в соответствующий тракт 2230-22315 передачи сигналов. Другие логические вентили 2220-22215 передают сигнал с низким логическим уровнем в соответствующие тракты 2230-22315 передачи сигналов.

[0034] Каждый логический вентиль 2240-22415 передает сигнал с высоким логическим уровнем в соответствующий тракт 2250-22515 передачи сигналов в ответ на сигнал с высоким логическим уровнем на тракте 229 передачи сигналов и сигнал с высоким логическим уровнем на соответствующем тракте 2230-22315 передачи сигналов. Каждый логический вентиль 2240-22415 передает сигнал с низким логическим уровнем в соответствующий тракт 2250-22515 передачи сигналов в ответ на сигнал с низким логическим уровнем на тракте 229 передачи сигналов или сигнал с низким логическим уровнем на соответствующем тракте 2230-22315 передачи сигналов. Соответственно, в ответ на сигнал активации запоминающего устройства с низким логическим уровнем и сигнал с высоким логическим уровнем на тракте 2250-22515 передачи сигналов, соответствующее устройство 2020-20215 активации текучей среды запускается посредством активации соответствующего запускающего резистора 212. В ответ на сигнал активации запоминающего устройства с высоким логическим уровнем и сигнал с высоким логическим уровнем на тракте 2250-22515 передачи сигналов, соответствующая запоминающая ячейка 2040-20415 выбирается для доступа.

[0035] С запоминающей ячейкой 2040-20415, выбранной для доступа, регулятор 230 напряжения записи в запоминающее устройство может активироваться посредством сигнала записи в запоминающее устройство на тракте 232 передачи сигналов записи в запоминающее устройство таким образом, чтобы прикладывать напряжение к тракту 234 передачи сигналов, чтобы записывать бит данных в транзистор 220 с плавающим затвором. Помимо этого, с запоминающей ячейкой 2040-20415, выбранной для доступа, транзисторы 238 и 240 могут включаться в ответ на сигнал считывания из запоминающего устройства на тракте 236 передачи сигналов считывания из запоминающего устройства. С включенными транзисторами 238 и 240, бит данных, сохраненный в транзисторе 220 с плавающим затвором, может считываться через площадку 241 считывания (например, посредством ведущего печатающего оборудования, соединенного с площадкой 241 считывания). В одном примере, сигнал записи в запоминающее устройство и сигнал считывания из запоминающего устройства основаны на данных, сохраненных в конфигурационном регистре, таком как конфигурационный регистр 136 по фиг. 1B. В другом примере, сигнал записи в запоминающее устройство и сигнал считывания из запоминающего устройства основаны на данных, принимаемых посредством схемы 200, наряду с адресом и данными сопел, которые используются посредством конфигурационной логики, такой как конфигурационная логика 110 по фиг. 1A, для того, чтобы активировать сигнал считывания или сигнал записи.

[0036] Фиг. 3A является блок-схемой, иллюстрирующей один пример интегральной схемы 300 для того, чтобы осуществлять доступ к запоминающему устройству, ассоциированному с устройством выброса текучей среды. В этом примере, устройства активации текучей среды могут быть расположены на интегральной схеме, отдельной от запоминающего устройства. Интегральная схема 300 включает в себя множество запоминающих ячеек 3040-304N, декодер 322 адресов, логику 324 активации и конфигурационную логику 310. Каждая запоминающая ячейка 3040-304N электрически соединяется с логикой 324 активации через тракт 3030-303N передачи сигналов, соответственно. Логика 324 активации электрически соединяется с декодером 322 адресов, с конфигурационной логикой 310 через тракт 309 передачи сигналов и принимает сигнал запуска через интерфейс 328 запуска. Декодер 322 адресов принимает сигнал данных через интерфейс 326 данных. Каждый из интерфейса 326 данных и интерфейса 328 запуска может представлять собой контактную площадку, штырьковый вывод, контактный столбик, провод или другой подходящий электрический интерфейс для передачи сигналов в и/или из интегральной схемы 300. Каждый из интерфейсов 326 и 328 может электрически соединяться с системой выброса текучей среды (например, с ведущим печатающим оборудованием).

[0037] В одном примере, каждая запоминающая ячейка 3040-304N включает в себя энергонезависимую запоминающую ячейку (например, транзистор с плавающим затвором, программируемую ячейку с плавкой перемычкой и т.д.). Декодер 322 адресов выбирает запоминающие ячейки 3040-304N в ответ на адрес, который может приниматься через интерфейс 326 данных. Логика 324 активации активирует выбранные запоминающие ячейки 3040-304N на основе сигнала данных в интерфейсе 326 данных и сигнала запуска в интерфейсе 328 запуска. Конфигурационная логика 310 активирует или деактивирует доступ ко множеству запоминающих ячеек 3040-304N.

[0038] Фиг. 3B является блок-схемой, иллюстрирующей другой пример интегральной схемы 320 для того, чтобы осуществлять доступ к запоминающему устройству, ассоциированному с устройством выброса текучей среды. Интегральная схема 320 включает в себя множество запоминающих ячеек 3040-304N, декодер 322 адресов и логику 324 активации. Помимо этого, интегральная схема 320 включает в себя схему 330 записи и конфигурационный регистр 336. В одном примере, конфигурационная логика 310 интегральной схемы 300 по фиг. 3A включает в себя конфигурационный регистр 336. Каждая запоминающая ячейка 3040-304N электрически соединяется со схемой 330 записи через интерфейс 334 считывания.

[0039] Конфигурационный регистр 336 может сохранять данные для того, чтобы активировать или деактивировать доступ ко множеству запоминающих ячеек 3040-304N. Помимо этого, конфигурационный регистр 336 может сохранять данные для того, чтобы активировать доступ для записи или доступ для считывания ко множеству запоминающих ячеек 3040-304N. Интерфейс 334 считывания предоставляет один интерфейс, соединенный с каждой из множества запоминающих ячеек 3040-304N, чтобы соединять с одиночным контактом ведущего печатающего оборудования. В одном примере, интерфейс 334 считывания включает в себя одну контактную площадку.

[0040] Данные, сохраненные в запоминающих ячейках 3040-304N, могут считываться через интерфейс 334 считывания, когда к выбранным запоминающим ячейкам 3040-304N осуществлен доступ посредством декодера 322 адресов и логики 324 активации. Помимо этого, схема 330 записи может записывать данные в выбранные запоминающие ячейки 3040-304N, когда к выбранным запоминающим ячейкам 3040-304N осуществлен доступ посредством декодера 322 адресов и логики 324 активации.

[0041] Фиг. 4A иллюстрирует один пример матрицы 400 выброса текучей среды, и фиг. 4B иллюстрирует укрупненный вид концов матрицы 400 выброса текучей среды. В одном примере, матрица 400 выброса текучей среды включает в себя интегральную схему 100 по фиг. 1A, интегральную схему 120 по фиг. 1B или схему 200 по фиг. 2. Матрица 400 включает в себя первую колонку 402 контактных площадок, вторую колонку 404 контактных площадок и колонку 406 устройств 408 активации текучей среды. Вторая колонка 404 контактных площадок совмещается с первой колонкой 402 контактных площадок и находится на расстоянии (т.е. вдоль оси Y) от первой колонки 402 контактных площадок. Колонка 406 устройств 408 активации текучей среды располагается продольно к первой колонке 402 контактных площадок и второй колонке 404 контактных площадок. Колонка 406 устройств 408 активации текучей среды также размещается между первой колонкой 402 контактных площадок и второй колонкой 404 контактных площадок. В одном примере, устройства 408 активации текучей среды представляют собой сопла или насосы текучей среды, которые выбрасывают капли текучей среды.

[0042] В одном примере, первая колонка 402 контактных площадок включает в себя шесть контактных площадок. Первая колонка 402 контактных площадок может включать в себя следующие контактные площадки по порядку: контактная площадка 410 данных, контактная площадка 412 синхросигналов, контактная площадка 414 возврата через землю логической электроэнергии, контактная площадка 416 многоцелевых сигналов ввода-вывода (т.е. считывания), первая контактная площадка 418 подачи электроэнергии высокого напряжения и первая контактная площадка 420 возврата через землю электроэнергии высокого напряжения. Следовательно, первая колонка 402 контактных площадок включает в себя контактную площадку 410 данных в верхней части первой колонки 402, первую контактную площадку 420 возврата через землю электроэнергии высокого напряжения в нижней части первой колонки 402 и первую контактную площадку 418 подачи электроэнергии высокого напряжения непосредственно выше первой контактной площадки 420 возврата через землю электроэнергии высокого напряжения. Хотя контактные площадки 410, 412, 414, 416, 418 и 420 проиллюстрированы в конкретном порядке, в других примерах контактные площадки могут быть размещены в другом порядке.

[0043] В одном примере, вторая колонка 404 контактных площадок включает в себя шесть контактных площадок. Вторая колонка 404 контактных площадок может включать в себя следующие контактные площадки по порядку: вторая контактная площадка 422 возврата через землю электроэнергии высокого напряжения, вторая контактная площадка 424 подачи электроэнергии высокого напряжения, контактная площадка 426 логического сброса, контактная площадка 428 подачи логической электроэнергии, контактная площадка 430 режима и контактная площадка 432 запуска. Следовательно, вторая колонка 404 контактных площадок включает в себя вторую контактную площадку 422 возврата через землю электроэнергии высокого напряжения в верхней части второй колонки 404, вторую контактную площадку 424 подачи электроэнергии высокого напряжения непосредственно ниже второй контактной площадки 422 возврата через землю электроэнергии высокого напряжения и контактную площадку 432 запуска в нижней части второй колонки 404. Хотя контактные площадки 422, 424, 426, 428, 430 и 432 проиллюстрированы в конкретном порядке, в других примерах контактные площадки могут быть размещены в другом порядке.

[0044] Контактная площадка 410 данных (например, интерфейс 126 данных по фиг. 1B) может использоваться для того, чтобы вводить последовательные данные в матрицу 400 для выбора устройств активации текучей среды (например, через схему 106 выбора по фиг. 1B), битов запоминающего устройства (например, через схему 106 выбора по фиг. 1B), термических датчиков, режимов конфигурирования (например, через конфигурационный регистр 136 по фиг. 1B) и т.д. Контактная площадка 410 данных также может использоваться для того, чтобы выводить последовательные данные из матрицы 400 считывания битов запоминающего устройства, режимов конфигурирования, информации состояния и т.д. Контактная площадка 412 синхросигналов может использоваться для того, чтобы вводить синхросигнал в матрицу 400 для того, чтобы перемещать последовательные данные на контактной площадке 410 данных в матрицу или перемещать последовательные данные из матрицы в контактную площадку 410 данных. Контактная площадка 414 возврата через землю логической электроэнергии предоставляет тракт возврата через землю для логической электроэнергии (например, приблизительно 0 В), подаваемой в матрицу 400. В одном примере, контактная площадка 414 возврата через землю логической электроэнергии электрически соединяется с полупроводниковой (например, кремниевой) подложкой 440 матрицы 400. Контактная площадка 416 многоцелевых сигналов ввода-вывода (например, интерфейс 134 считывания по фиг. 1B или площадка 241 считывания по фиг. 2) может использоваться для аналоговых считывающих и/или цифровых тестовых режимов матрицы 400. В одном примере, контактная площадка 416 многоцелевых сигналов ввода-вывода может электрически соединяться с каждой запоминающей ячейкой 1040-104N, схемой 130 записи и датчиком 132 по фиг. 1B.

[0045] Первая контактная площадка 418 подачи электроэнергии высокого напряжения и вторая контактная площадка 424 подачи электроэнергии высокого напряжения могут использоваться для того, чтобы подавать высокое напряжение (например, приблизительно 32 В) в матрицу 400. Первая контактная площадка 420 возврата через землю электроэнергии высокого напряжения и вторая контактная площадка 422 возврата через землю электроэнергии высокого напряжения могут использоваться для того, чтобы предоставлять возврат через землю электроэнергии (например, приблизительно 0 В) для подачи электроэнергии высокого напряжения. Контактные площадки 420 и 422 возврата через землю электроэнергии высокого напряжения непосредственно электрически не соединяются с полупроводниковой подложкой 440 матрицы 400. Конкретный порядок контактных площадок с контактными площадками 418 и 424 подачи электроэнергии высокого напряжения и контактными площадками 420 и 422 возврата через землю электроэнергии высокого напряжения в качестве крайних внутренних контактных площадок может улучшать доставку электроэнергии в матрицу 400. Наличие контактных площадок 420 и 422 возврата через землю электроэнергии высокого напряжения в нижней части первой колонки 402 и в верхней части второй колонки 404, соответственно, может повышать надежность для изготовления и может улучшать защиту от коротких замыканий вследствие попадания чернил.

[0046] Контактная площадка 426 логического сброса может использоваться в качестве ввода логического сброса, чтобы управлять рабочим состоянием матрицы 400. Контактная площадка 428 подачи логической электроэнергии может использоваться для того, чтобы подавать логическую электроэнергию (например, приблизительно между 1,8 В и 15 В, к примеру, 5,6 В) в матрицу 400. Контактная площадка 430 режима может использоваться в качестве логического ввода, чтобы управлять доступом, чтобы активировать/деактивировать режимы конфигурирования (т.е. функциональные режимы) матрицы 400. Контактная площадка 432 запуска (например, интерфейс 128 запуска по фиг. 1B) может использоваться в качестве логического ввода, чтобы запирать загружаемые данные из контактной площадки 410 данных и активировать устройства активации текучей среды или запоминающие элементы матрицы 400.

[0047] Матрица 400 включает в себя удлиненную подложку 440, имеющую длину 442 (вдоль оси Y), толщину 444 (вдоль оси Z) и ширину 446 (вдоль оси X). В одном примере, длина 442 в по меньшей мере двадцать раз превышает ширину 446. Ширина 446 может составлять 1 мм или меньше, и толщина 444 может составлять меньше 500 микронов. Устройства 408 активации текучей среды (например, логика активации текучей среды) и контактные площадки 410-432 предоставляются на удлиненной подложке 440 и размещаются по длине 442 удлиненной подложки. Устройства 408 активации текучей среды имеют длину 452 охвата, меньшую длины 442 удлиненной подложки 440. В одном примере, длина 452 охвата составляет по меньшей мере 1,2 см. Контактные площадки 410-432 могут электрически соединяться с логикой активации текучей среды. Первая колонка 402 контактных площадок может быть размещена около первого продольного конца 448 удлиненной подложки 440. Вторая колонка 404 контактных площадок может быть размещена около второго продольного конца 450 удлиненной подложки 440 напротив первого продольного конца 448.

[0048] Фиг. 5A иллюстрирует укрупненный вид центрального участка матрицы 400a выброса текучей среды, в качестве дополнительного примера матрицы 400 выброса текучей среды по фиг. 4A и 4B. Как описано выше со ссылкой на фиг. 4A и 4B, матрица 400a выброса текучей среды включает в себя множество сопел 408, размещенных в колонке вдоль длины удлиненной подложки 440. Помимо этого, матрица 400 выброса текучей среды включает в себя множество запоминающих ячеек, размещенных в группах 460 рядом с множеством сопел 408. Как проиллюстрировано на фиг. 5B, каждая группа 460 запоминающих ячеек может включать в себя первую запоминающую ячейку 4620 и вторую запоминающую ячейку 4621. Каждая запоминающая ячейка 462 соответствует соплу 408. Как описано выше, логика активации текучей среды матрицы 400 выброса текучей среды либо выбрасывает текучую среду из выбранных сопел 408, либо осуществляет доступ к запоминающим ячейкам 462, соответствующим выбранным соплам 408.

[0049] В одном примере, каждое сопло 408 из множества сопел имеет соответствующую запоминающую ячейку 462. В другом примере, каждое второе сопло 408 из множества сопел имеет соответствующую запоминающую ячейку 462. В другом примере, множество запоминающих ячеек могут включать в себя единственную запоминающую ячейку 462, соответствующую каждому соплу 408. В другом примере, множество запоминающих ячеек включают в себя по меньшей мере две запоминающих ячейки 462, соответствующие каждому соплу 408. Множество запоминающих ячеек 462 могут быть размещено во множестве групп 460, причем каждая группа 460 включает в себя по меньшей мере две запоминающих ячейки 462. Множество групп 460 разнесены друг от друга вдоль удлиненной подложки 440.

[0050] Фиг. 6A иллюстрирует укрупненный вид центрального участка матрицы 400b выброса текучей среды, в качестве дополнительного примера матрицы 400 выброса текучей среды по фиг. 4A и 4B. Матрица 400b выброса текучей среды включает в себя множество сопел 408a, размещенных в первой колонке вдоль удлиненной подложки 440, и множество сопел 408b, размещенных во второй колонке вдоль удлиненной подложки 440. Первая колонка находится рядом со второй колонкой. Сопла 408a в первой колонке могут смещаться относительно сопел 408b во второй колонке. Помимо этого, матрица 400b выброса текучей среды включает в себя множество запоминающих ячеек, размещенных в группах 470 рядом с множеством сопел 408a и 408b. Группы 470 разнесены друг от друга вдоль удлиненной подложки 440.

[0051] Как проиллюстрировано на фиг. 6B, каждая группа 470 может включать в себя шесть запоминающих ячеек, размещенных в трех банках 4821-4823. Первый банк 4821 включает в себя первую запоминающую ячейку 4721-0 и вторую запоминающую ячейку 4721-1. Второй банк 4822 включает в себя первую запоминающую ячейку 4722-0 и вторую запоминающую ячейку 4722-1. Третий банк 4823 включает в себя первую запоминающую ячейку 4723-0 и вторую запоминающую ячейку 4723-1. Каждый банк 4821-4823 может выбираться в ответ на сигнал активации банка в тракте 4801-4803 передачи сигналов активации банков, соответственно.

[0052] В одном примере, множество запоминающих ячеек включают в себя три запоминающих ячейки 472, соответствующие каждому соплу 408a и/или 408b. Первая запоминающая ячейка (например, запоминающая ячейка 4721-0), соответствующая каждому соплу, размещается в первом банке (например, в банке 4821) запоминающих ячеек, вторая запоминающая ячейка (например, запоминающая ячейка 4722-0) соответствующая каждому соплу, размещается во втором банке (например, в банке 4822) запоминающих ячеек, и третья запоминающая ячейка (например, запоминающая ячейка 4723-0) соответствующая каждому соплу, размещается в третьем банке (например, в банке 4823) запоминающих ячеек. Логика активации текучей среды либо выбрасывает текучую среду из выбранных сопел 408a и/или 408b, либо осуществляет доступ к запоминающим ячейкам 472, соответствующим выбранным соплам и выбранному банку запоминающих ячеек.

[0053] В одном примере, сигналы активации банка один, банка два и банка три основаны на данных, сохраненных в конфигурационном регистре, таком как конфигурационный регистр 136 по фиг. 1B. В другом примере, сигналы активации банка один, банка два и банка три основаны на данных, принимаемых посредством матрицы 400b выброса текучей среды, наряду с адресом и данными сопел, которые используются посредством конфигурационной логики, такой как конфигурационная логика 110 по фиг. 1A, для того, чтобы активировать выбранный банк 4821-4823.

[0054] Фиг. 7 является блок-схемой, иллюстрирующей один пример системы 500 выброса текучей среды. Система 500 выброса текучей среды включает в себя блок выброса текучей среды, такой как блок 502 печатающих головок, и блок подачи текучей среды, такой как блок 510 подачи чернил. В проиллюстрированном примере, система 500 выброса текучей среды также включает в себя блок 504 обслуживающей станции, блок 516 каретки, блок 518 транспортировки носителей для печати и электронный контроллер 520. Хотя нижеприведенное описание предоставляет примеры систем и блоков для обращения с текучими средами относительно чернил, раскрытые системы и блоки также являются применимыми к обращению с текучими средами, отличными от чернил.

[0055] Блок 502 печатающих головок включает в себя по меньшей мере одну печатающую головку или матрицу 400 выброса текучей среды, описанную выше и проиллюстрированную со ссылкой на фиг. 4A и 4B, которая выбрасывает капли чернил или текучей среды через множество отверстий или сопел 408. В одном примере, капли направляются к носителю, к примеру, к носителям 524 для печати, с тем чтобы печатать на носителях 524 для печати. В одном примере, носители 524 для печати включают в себя любой тип подходящего листового материала, такого как бумага, стопка карточек, диапозитивы, майлар, ткань и т.п. В другом примере, носители 524 для печати включают в себя носители для трехмерной печати, такие как порошковая подушка, либо носители для биопечати и/или тестирования при изыскании новых лекарственных средств, такие как резервуар или контейнер. В одном примере, сопла 408 размещаются в по меньшей мере одной колонке или массиве таким образом, что надлежащим образом упорядоченный выброс чернил из сопел 408 приводит к тому, что знаки, символы и/или другие графические элементы или изображения печатаются на носителях 524 для печати по мере того, как блок 502 печатающих головок и носители 524 для печати перемещаются относительно друг друга.

[0056] Блок 510 подачи чернил подает чернила в блок 502 печатающих головок и включает в себя резервуар 512 для хранения чернил. В связи с этим, в одном примере, чернила протекают из резервуара 512 в блок 502 печатающих головок. В одном примере, блок 502 печатающих головок и блок 510 подачи чернил размещаются вместе в струйном или жидкостно-струйном печатающем картридже или печатающем элементе. В другом примере, блок 510 подачи чернил является отдельным от блока 502 печатающих головок и подает чернила в блок 502 печатающих головок через интерфейсное соединение 513, такое как подводящая трубка и/или клапан.

[0057] Блок 516 каретки позиционирует блок 502 печатающих головок относительно блока 518 транспортировки носителей для печати, и блок 518 транспортировки носителей для печати позиционирует носители 524 для печати относительно блока 502 печатающих головок. Таким образом, зона 526 печати задается рядом с соплами 408 в области между блоком 502 печатающих головок и носителями 524 для печати. В одном примере, блок 502 печатающих головок представляет собой блок печатающих головок сканирующего типа таким образом, что блок 516 каретки перемещает блок 502 печатающих головок относительно блока 518 транспортировки носителей для печати. В другом примере, блок 502 печатающих головок представляет собой блок печатающих головок несканирующего типа таким образом, что блок 516 каретки закрепляет блок 502 печатающих головок в предписанной позиции относительно блока 518 транспортировки носителей для печати.

[0058] Блок 504 обслуживающей станции предоставляет сбор излишков чернил, вытирание, закупоривание и/или заправку блока 502 печатающих головок, чтобы поддерживать функциональность блока 502 печатающих головок и, более конкретно, сопла 408. Например, блок 504 обслуживающей станции может включать в себя резиновое лезвие или вытиратель, который периодически проходит по блоку 502 печатающих головок, чтобы вытирать и очищать сопла 408 от лишних чернил. Помимо этого, блок 504 обслуживающей станции может включать в себя заглушку, которая закрывает блок 502 печатающих головок, чтобы защищать сопла 408 от высыхания в течение периодов неиспользования. Помимо этого, блок 504 обслуживающей станции может включать в себя контейнер для сбора излишков чернил, в который блок 502 печатающих головок выбрасывает чернила в ходе сбора излишков чернил, чтобы обеспечивать то, что резервуар 512 поддерживает надлежащий уровень давления и текучести, и обеспечивать то, что сопла 408 не засоряются или не дают утечку. Функции блока 504 обслуживающей станции могут включать в себя относительное движение между блоком 504 обслуживающей станции и блоком 502 печатающих головок.

[0059] Электронный контроллер 520 обменивается данными с блоком 502 печатающих головок через тракт 503 связи, блоком 504 обслуживающей станции через тракт 505 связи, блоком 516 каретки через тракт 517 связи и блоком 518 транспортировки носителей для печати через тракт 519 связи. В одном примере, когда блок 502 печатающих головок устанавливается в блоке 516 каретки, электронный контроллер 520 и блок 502 печатающих головок могут обмениваться данными через блок 516 каретки через тракт 501 связи. Электронный контроллер 520 также может обмениваться данными с блоком 510 подачи чернил таким образом, что, в одной реализации, подача новых (или используемых) чернил может обнаруживаться.

[0060] Электронный контроллер 520 принимает данные 528 из ведущей системы, такой как компьютер, и может включать в себя запоминающее устройство для временного сохранения данных 528. Данные 528 могут отправляться в систему 500 выброса текучей среды вдоль электронного, инфракрасного, оптического или другого тракта передачи информации. Данные 528 представляют, например, документ и/или файл, который должен печататься. В связи с этим, данные 528 формируют задание печати для системы 500 выброса текучей среды и включают в себя по меньшей мере одну команду задания печати и/или параметр команды.

[0061] В одном примере, электронный контроллер 520 предоставляет управление блоком 502 печатающих головок, включающее в себя управление согласно временной синхронизации для выброса капель чернил из сопел 408. В связи с этим, электронный контроллер 520 задает рисунок выбрасываемых капель чернил, которые формируют знаки, символы и/или другие графические элементы или изображения на носителях 524 для печати. Управление согласно временной синхронизации и в силу этого рисунок выбрасываемых капель чернил определяется посредством команд задания печати и/или параметров команд. В одном примере, логические и возбуждающие схемы, формирующие участок электронного контроллера 520, расположены на блоке 502 печатающих головок. В другом примере, логические и возбуждающие схемы, формирующие участок электронного контроллера 520, расположены за пределами блока 502 печатающих головок.

[0062] Хотя конкретные примеры проиллюстрированы и описаны в данном документе, множество альтернативных и/или эквивалентных реализаций могут использоваться вместо показанных и описанных конкретных примеров, без отступления от объема настоящего раскрытия. Эта заявка имеет намерение охватывать все адаптации или варьирования конкретных примеров, поясненных в данном документе. Следовательно, подразумевается, что это раскрытие ограничено только формулой изобретения и ее эквивалентами.

Интегральная схема для возбуждения множества устройств активации текучей среды включает в себя множество запоминающих ячеек, схему выбора, конфигурационную логику и управляющую логику. Каждая запоминающая ячейка соответствует устройству активации текучей среды. Схема выбора выбирает устройства активации текучей среды и запоминающие ячейки, соответствующие выбранным устройствам активации текучей среды. Конфигурационная логика активирует или деактивирует доступ ко множеству запоминающих ячеек. Управляющая логика либо активирует выбранные устройства активации текучей среды, либо осуществляет доступ к запоминающим ячейкам, соответствующим выбранным устройствам активации текучей среды, на основе состояния конфигурационной логики. 14 з.п. ф-лы, 12 ил.

1. Интегральная схема для возбуждения множества устройств активации текучей среды, причем интегральная схема содержит:

множество запоминающих ячеек, причем каждая запоминающая ячейка соответствует устройству активации текучей среды;

схему выбора для выбора устройств активации текучей среды и запоминающих ячеек, соответствующих выбранным устройствам активации текучей среды;

конфигурационную логику для активации или деактивации доступа ко множеству запоминающих ячеек; и

управляющую логику для либо активации выбранных устройств активации текучей среды, либо осуществления доступа к запоминающим ячейкам, соответствующим выбранным устройствам активации текучей среды, на основе состояния конфигурационной логики.

2. Интегральная схема по п. 1, в которой схема выбора содержит декодер адресов для выбора устройств активации текучей среды и запоминающих ячеек, соответствующих выбранным устройствам активации текучей среды, в ответ на адрес.

3. Интегральная схема по п. 1 или 2, в которой схема выбора содержит логику активации для активации выбранных устройств активации текучей среды и запоминающих ячеек, соответствующих выбранным устройствам активации текучей среды, на основе сигнала данных и сигнала запуска.

4. Интегральная схема по любому из пп. 1-3, дополнительно содержащая:

схему записи, соединенную с множеством запоминающих ячеек.

5. Интегральная схема по любому из пп. 1-4, в которой конфигурационная логика содержит конфигурационный регистр, сохраняющий данные для того, чтобы активировать или деактивировать доступ ко множеству запоминающих ячеек, и

при этом управляющая логика выполнена с возможностью либо активации выбранных устройств активации текучей среды, либо осуществления доступа к запоминающим ячейкам, соответствующим выбранным устройствам активации текучей среды, на основе данных, сохраненных в конфигурационном регистре.

6. Интегральная схема по п. 5, в которой конфигурационный регистр сохраняет данные для того, чтобы активировать доступ для записи или доступ для считывания ко множеству запоминающих ячеек.

7. Интегральная схема по п. 5 или 6, дополнительно содержащая:

датчик,

при этом конфигурационный регистр сохраняет данные для того, чтобы активировать или деактивировать датчик.

8. Интегральная схема по любому из пп. 1-7, содержащая:

удлиненную подложку, имеющую длину, толщину и ширину, причем длина в по меньшей мере двадцать раз превышает ширину, при этом на удлиненной подложке обеспечено:

множество устройств активации текучей среды, размещенных в колонке вдоль длинны удлиненной подложки, и

множество запоминающих ячеек, размещенных рядом с множеством устройств активации текучей среды, причем каждая запоминающая ячейка соответствует устройству активации текучей среды.

9. Интегральная схема по п. 8, в которой каждое второе устройство активации текучей среды из множества устройств активации текучей среды имеет соответствующую запоминающую ячейку.

10. Интегральная схема по любому из пп. 8 или 9, в которой множество запоминающих ячеек содержит единственную запоминающую ячейку, соответствующую каждому устройству активации текучей среды.

11. Интегральная схема по любому из пп. 8-10, в которой множество запоминающих ячеек размещены во множестве групп, причем каждая группа включает в себя по меньшей мере две запоминающих ячейки, и множество групп разнесены друг от друга.

12. Интегральная схема по п. 8, в которой множество запоминающих ячеек содержит по меньшей мере две запоминающих ячейки, соответствующие каждому устройству активации текучей среды.

13. Интегральная схема по п. 12, в которой первая запоминающая ячейка, соответствующая каждому устройству активации текучей среды, размещена в первом банке запоминающих ячеек, и вторая запоминающая ячейка, соответствующая каждому устройству активации текучей среды, размещена во втором банке запоминающих ячеек.

14. Интегральная схема по п. 8, в которой множество запоминающих ячеек содержит три запоминающих ячейки, соответствующие каждому устройству активации текучей среды.

15. Интегральная схема по п. 14, в которой первая запоминающая ячейка, соответствующая каждому устройству активации текучей среды, размещена в первом банке запоминающих ячеек, вторая запоминающая ячейка, соответствующая каждому устройству активации текучей среды, размещена во втором банке запоминающих ячеек, и третья запоминающая ячейка, соответствующая каждому устройству активации текучей среды, размещена в третьем банке запоминающих ячеек.

| US 2010302293 A1, 02.12.2010 | |||

| US 2014320558 A1, 30.10.2014 | |||

| US 2008055366 A1, 06.03.2008 | |||

| US 2017120590 A1, 04.05.2017 | |||

| US 2018236762 A1, 23.08.2018 | |||

| US 2017259568 A1, 14.09.2017. |

Авторы

Даты

2022-09-13—Публикация

2019-02-06—Подача