Предпосылки изобретения

[0001] Система печати может содержать печатающую головку, которая имеет форсунки для распределения печатающей текучей среды по мишени. В системе двухмерной (2D) печати мишень представляет собой носитель печати, такой как бумага или подложка другого типа, на которой можно формировать печатные изображения. Примеры систем 2D-печати включают системы струйной печати, которые способны распределять капельки чернил. В системе трехмерной (3D) печати мишень может представлять собой слой или несколько слоев модельного материала, наносимых для формирования 3D-объекта.

Краткое описание чертежей

[0002] Некоторые реализации настоящего раскрытия описаны в отношении следующих чертежей.

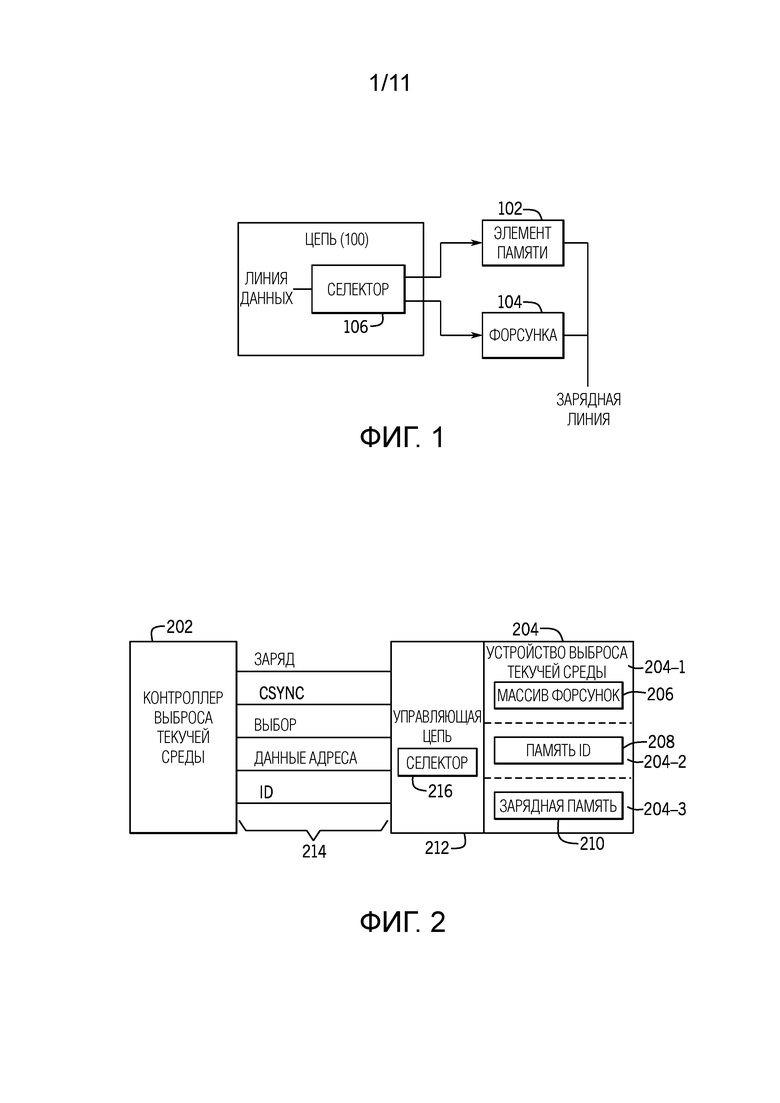

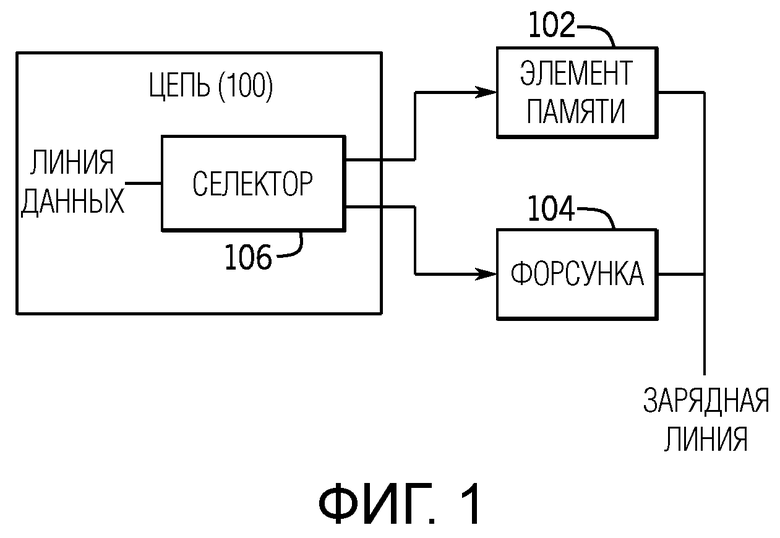

[0003] Фиг. 1 представляет собой блок-схему компоновки, содержащей цепь, элемент памяти и форсунку, в соответствии с некоторыми примерами.

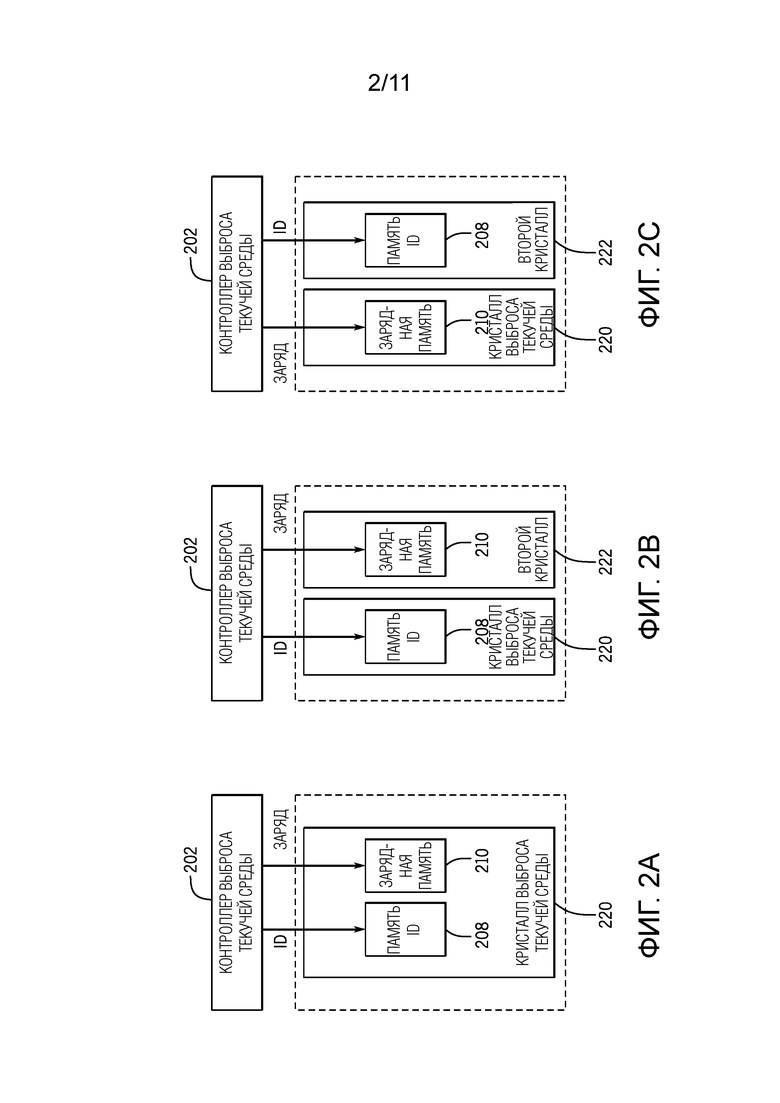

[0004] Фиг. 2 представляет собой блок-схему системы в соответствии с дополнительными примерами.

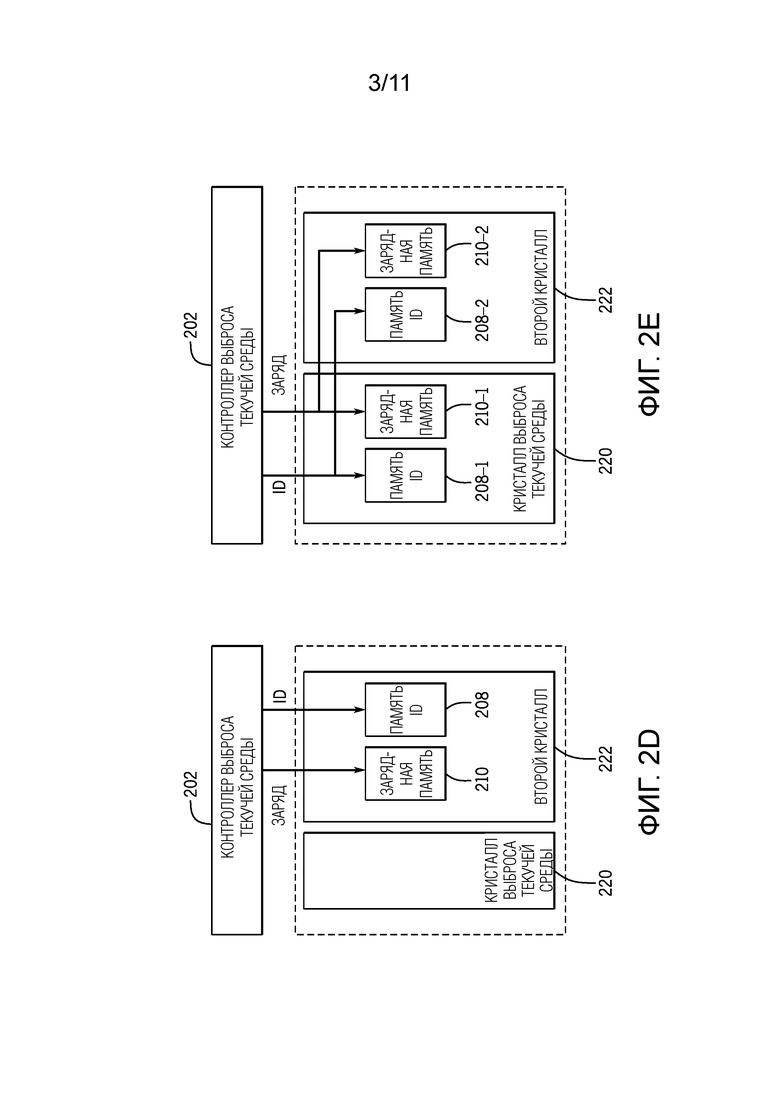

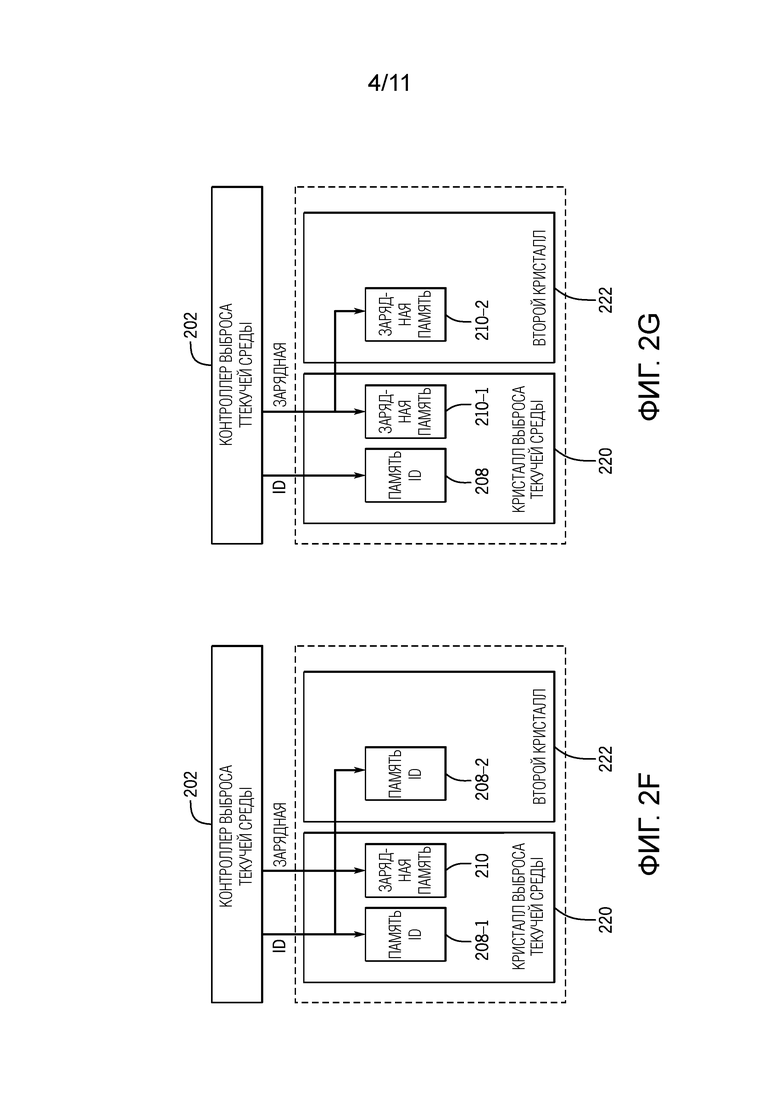

[0005] Фиг. 2A-2G представляют собой блок-схемы различных систем в соответствии с различными примерами.

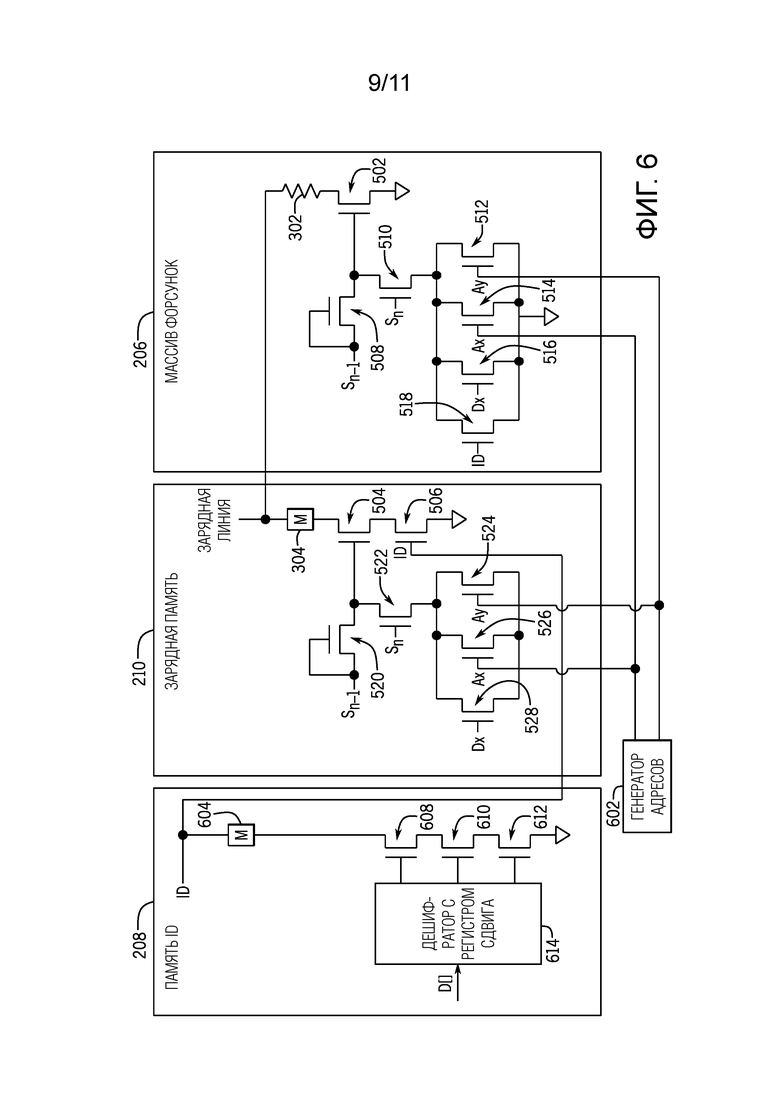

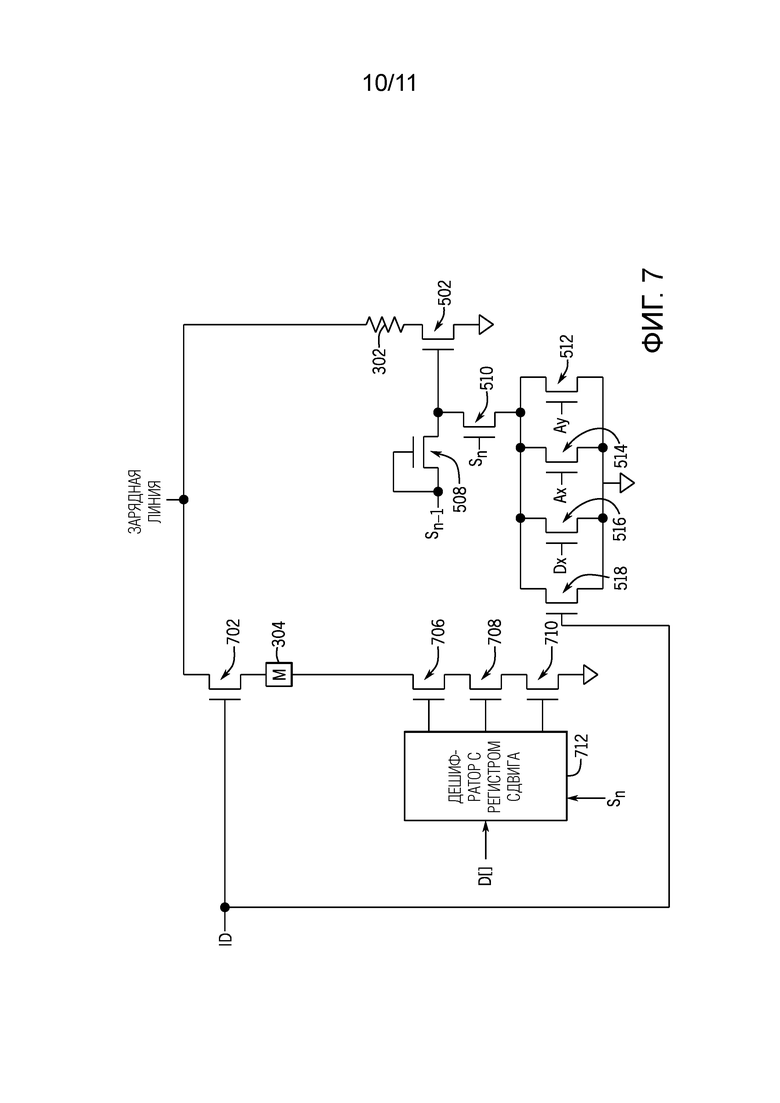

[0006] Фиг. 3, 4, 5, 5A, 5B, 6 и 7 представляют собой схематические диаграммы цепей, которые содержат элемент активации форсунки, элемент памяти и схему выбора в соответствии с различными примерами.

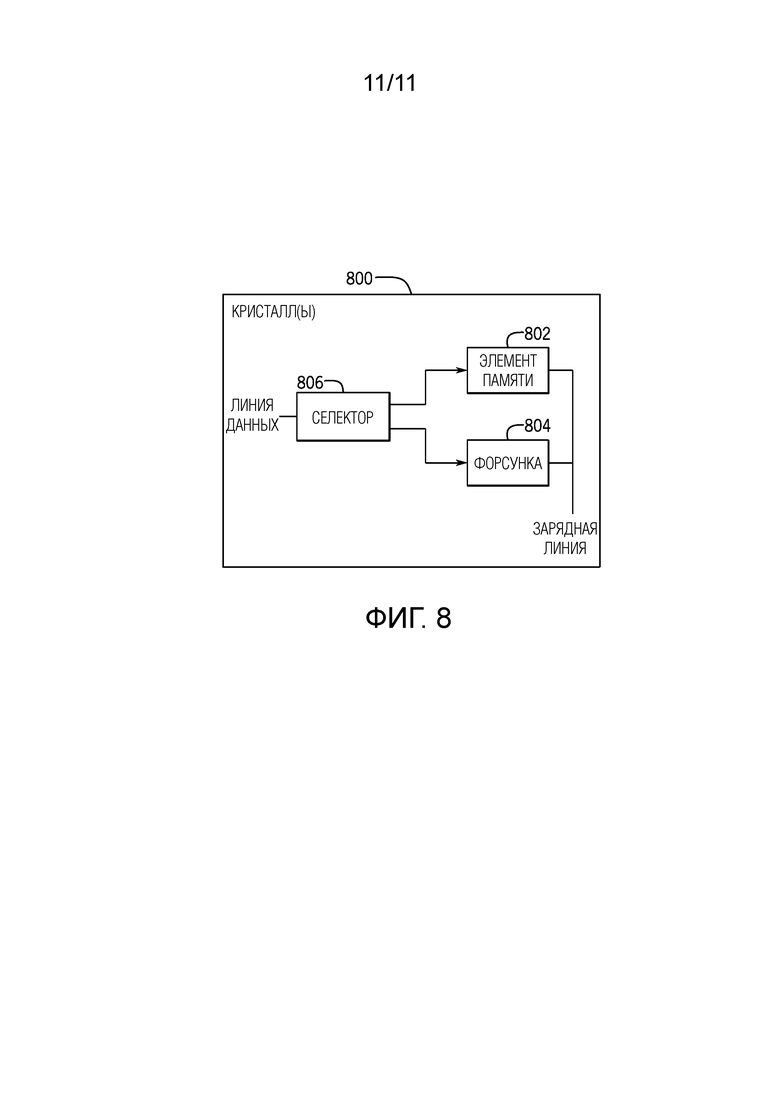

[0007] Фиг. 8 представляет собой блок-схему одного или более кристаллов, содержащих селектор, элемент памяти и форсунку, в соответствии с дополнительными примерами.

[0008] На всех чертежах идентичные ссылочные позиции обозначают схожие, но не обязательно идентичные, элементы. Фигуры не обязательно выполнены в масштабе, и размер некоторых частей может быть преувеличен для более ясной иллюстрации показанного примера. Кроме того, на чертежах предоставлены примеры и/или реализации в соответствии с описанием; однако описание не ограничено примерами и/или реализациями, предоставленными на чертежах.

Подробное описание

[0009] В настоящем раскрытии подразумевается, что использование термина в единственном числе включает также множественные формы, пока контекст явно не указывает на иное. Кроме того, термин «включает», «включающий», «содержит», «содержащий», «имеет» или «имеющий» при использовании в этом раскрытии конкретизирует присутствие указанных элементов, но не исключает присутствия или добавления других элементов.

[0010] Печатающая головка для использования в системе печати может содержать форсунки, которые приводят в действие, обуславливая выброс капелек печатающей текучей среды из соответствующих форсунок. Каждая форсунка содержит элемент активации форсунки. Элемент активации форсунки при приведении в действие вызывает выброс капельки печатающей текучей среды соответствующей форсункой. В некоторых примерах элемент активации форсунки содержит нагревательный элемент (например, терморезистор), который при приведении в действие генерирует тепло, испаряющее печатающую текучую среду в зарядной камере форсунки. Испарение печатающей текучей среды вызывает выпуск капельки печатающей текучей среды из форсунки. В других примерах элемент активации форсунки содержит пьезоэлектрический элемент. При приведении в действие пьезоэлектрический элемент прикладывает усилие, выбрасывая капельку печатающей текучей среды из форсунки. В дополнительных примерах можно использовать элементы активации форсунок других типов.

[0011] Система печати может представлять собой систему двухмерной (2D) или трехмерной (3D) печати. Система 2D-печати распределяет печатающую текучую среду, такую как чернила, формируя изображения на носителях печати, таких как бумажные носители или носители печати других типов. Система 3D-печати формирует 3D-объект путем нанесения последовательных слоев модельного материала. Печатающие текучие среды, распределяемые из системы 3D-печати, могут включать чернила, а также агенты, используемые для сплавления порошков слоя модельного материала, детализации слоя модельного материала (такой как путем ограничения кромок или геометрических форм слоя модельного материала) и т.д.

[0012] В последующем обсуждении термином «печатающая головка» может называться в целом кристалл печатающей головки или общий узел, который содержит несколько кристаллов, установленных на несущей конструкции. Кристалл (также называемый «кристалл интегральной схемы (IC)») содержит подложку, на которой предусмотрены различные слои, образующие форсунки и/или управляющую схему (цепь) для управления выбросом текучей среды форсунками.

[0013] Несмотря на то, что в некоторых примерах ссылка выполнена на печатающую головку для использования в системе печати, следует отметить, что методы или механизмы по настоящему раскрытию применимы к устройствам выброса текучей среды других типов, используемым в непечатных применениях, которые позволяют распределять текучие среды через форсунки. Примеры таких устройств выброса текучей среды других типов включают те, которые используют в системах измерения текучей среды, медицинских системах, транспортных средствах, системах управления потоком текучей среды и т.д.

[0014] В некоторых примерах устройство выброса текучей среды можно реализовать с одним кристаллом. В дополнительных примерах устройство выброса текучей среды может содержать несколько кристаллов.

[0015] Поскольку устройства, содержащие кристаллы печатающей головки или кристаллы выброса текучей среды других типов, продолжают уменьшаться в размерах, число сигнальных линий, используемых для управления схемой устройства, может влиять на общий размер устройства. Большое число сигнальных линий может приводить к использованию большого числа сигнальных контактных площадок (называемых «контактные столбики»), которые используют для электрического подключения сигнальных линий с внешними линиями. Добавление элементов в устройства выброса текучей среды может приводить к использованию увеличенного числа сигнальных линий (и соответствующих контактных столбиков), что может, например, занимать полезное пространство кристалла. Примеры дополнительных элементов, которые можно добавлять в устройство выброса текучей среды, включают запоминающие устройства.

[0016] В соответствии с некоторыми реализациями настоящего раскрытия, в другой схеме устройства выброса текучей среды (которая содержит один кристалл или несколько кристаллов) можно совместно использовать управляющие линии и линии данных, обеспечивая уменьшение числа сигнальных линий устройства выброса текучей среды, которые необходимо соединять с внешней линией. Как используют здесь, термин «линия» может относиться к электрическому проводнику (или альтернативно нескольким (множественным) электрическим проводникам), которые можно использовать для переноса сигнала (или нескольких сигналов).

[0017] Как показано на фиг. 1, в некоторых примерах, цепь 100 для использования с элементом 102 памяти и форсункой 104 содержит линию данных, зарядную линию и селектор 106. Элемент 102 памяти может содержать ячейку памяти (или группу ячеек памяти), которая может хранить данные. Элемент 102 памяти может быть частью массива/матрицы (или другой совокупности) элементов памяти, которые образуют часть памяти. Форсунка 104 может содержать элемент активации форсунки, камеру для текучей среды и выпускное отверстие (сопло) для текучей среды, причем элемент активации форсунки при приведении в действие вызывает выброс текучей среды в камере для текучей среды через сопло для текучей среды в окружающую среду снаружи форсунки 104.

[0018] В примерах, где устройство выброса текучей среды связано с несколькими различными единицами памяти, линию данных можно использовать для обмена (передачи) данных первой памяти с несколькими различными единицами памяти. Элемент 102 памяти может быть частью второй памяти из нескольких различных единиц памяти. Например, первая память может представлять собой память ID, которую используют для хранения идентификационных (ID) данных (и возможно другой информации) устройства выброса текучей среды (для уникальной идентификации устройства выброса текучей среды). Память ID также может хранить другие данные. В таких примерах линия данных может называться линией ID, которую используют для передачи данных (записи данных или считывания данных) памяти ID.

[0019] Вторая память может хранить данные о выбросе, которые можно использовать для задействования или выведения из действия определенных форсунок. В других примерах вторая память может хранить другие данные.

[0020] В некоторых примерах различные единицы памяти могут находиться на кристалле выброса текучей среды, который также содержит форсунки для выпуска (распределения) текучей среды. В других примерах различные единицы памяти могут находится на кристалле (или нескольких кристаллах), который отделен от кристалла выброса текучей среды. Например, первая память и вторая память могут быть частью кристалла, который отделен от кристалла выброса текучей среды, или первая память и вторая память могут быть частью соответствующих кристаллов, которые отделены от кристалла выброса текучей среды.

[0021] Селектор 106 реагирует на значение линии данных с выбором элемента 102 памяти или форсунки 104. Следует отметить, что линию данных используют для обмена данными, в отличие от линий данных адресов, которые используют для переноса адреса. Конкретный пример линии данных представляет собой линию ID (дополнительно объясненную ниже). Селектор 106 выбирает элемент 102 памяти в случае линии данных, имеющей первое значение, и выбирает форсунку 104 в случае линии данных, имеющей второе значение, отличное от первого значения. Зарядная линия управляет приведением в действие форсунки 104 в случае выбор форсунки 104 селектором 106 и осуществляет передачу данных (записывает данные или считывает данные) элемента 102 памяти в случае выбора элемента 102 памяти селектором 106.

[0022] В некоторых примерах цепь 100 может быть частью того же кристалла, что и элемент 102 памяти и форсунка 104. Например, кристалл выброса текучей среды может содержать цепь 100, элемент 102 памяти и форсунка 104. В других примерах цепь 100 может быть отделена от кристалла(ов), который содержит элемент 102 памяти и/или форсунку 104. Например, цепь 100 можно формировать на гибком кабеле, монтажной плате, кристалле или любой другой структуре, которая отделена от кристалла(ов), который содержит элемент 102 памяти и/или форсунку 104.

[0023] Фиг. 2 представляет собой блок-схему примерной системы, которая может содержать систему печати или систему распределения текучей среды другого типа. Система содержит контроллер 202 выброса текучей среды и устройство 204 выброса текучей среды. Контроллер 202 выброса текучей среды отделен от устройства 204 выброса текучей среды. Например, в системе печати контроллер 202 выброса текучей среды представляет собой контроллер привода печатающей головки, который представляет собой часть системы печати, тогда как устройство 204 выброса текучей среды представляет собой кристалл печатающей головки, который является частью печатного картриджа (который содержит чернила или другой агент), или может располагаться на другой структуре.

[0024] Устройство 204 выброса текучей среды содержит соответствующие части 204-1, 204-2 и 204-3. Часть 204-1 содержит массив 206 форсунок, который содержит массив форсунок, которыми можно управлять выборочно, распределяя текучую среду. Часть 204-2 содержит память 208 ID, такую, чтобы хранить идентификационные данные устройства 204 выброса текучей среды. Часть 204-3 содержит зарядную память 210, которую можно использовать для хранения данных, относящихся к массиву 206 форсунок, причем данные могут включать любую или некоторую комбинацию из следующего, в качестве примеров: местоположение кристалла, информация о регионе, кодирующая массу капли информация, аутентификационная информация, данные для задействования или выведения из действия выбранных форсунок и т.д. Элемент 102 памяти по фиг. 1 в некоторых примерах может быть частью зарядной памяти 210 по фиг. 2.

[0025] В некоторых примерах память 208 ID и зарядную память 210 можно реализовать с использованием единиц памяти различных типов, образуя компоновку гибридной памяти. Память 208 ID можно реализовать, например, с использованием электрически программируемого постоянного запоминающего устройства (EPROM). Зарядную память 210 можно реализовать с использованием памяти на плавких перемычках, причем память на плавких перемычках содержит массив плавких перемычек, которые можно выборочно разрушать (или не разрушать), чтобы программировать данные в зарядной памяти 210. Несмотря на то, что выше перечислены конкретные примеры типов единиц памяти, следует отметить, что в других примерах память 208 ID и зарядную память 210 можно реализовать с использованием единиц памяти других типов. В некоторых случаях память 208 ID и зарядную память 210 можно реализовать с использованием памяти одного и того же типа.

[0026] Кроме того, несмотря на то, в качестве хранимых памятью 208 ID и зарядной памятью 210 указаны данные конкретных типов, следует отметить, что в других примерах единицы памяти 208 и 210 могут хранить данные других или дополнительных типов.

[0027] В некоторых примерах части 204-1, 204-2 и 204-3 устройства 204 выброса текучей среды можно формировать на общем кристалле (т.е. кристалле выброса текучей среды) так, что массив 206 форсунок, память 208 ID и зарядную память 210 формируют на одном кристалле. В других примерах часть 204-1 можно реализовать на одном кристалле (кристалле выброса текучей среды, который содержит массив 206 форсунок), тогда как части 204-2 и 204-3 реализуют на отдельном кристалле (или соответствующих отдельных кристаллах). Например, память 208 ID и зарядную память 210 можно формировать на втором кристалле, который отделен от кристалла выброса текучей среды, или, альтернативно, память 208 ID и зарядную память 210 можно формировать на соответствующих различных кристаллах, отделенных от кристалла выброса текучей среды. В дополнительных примерах память 208 ID и массив 206 форсунок могут быть частью одного кристалла, тогда как зарядная память 210 представляет собой часть другого кристалла. В других примерах зарядная память 210 и массив 206 форсунок могут быть частью одного кристалла, а память 208 ID представляет собой часть другого кристалла. В дополнительных примерах часть памяти 208 ID может быть на одном кристалле, а другая часть памяти 208 ID может быть на другом кристалле. В других дополнительных примерах часть зарядной памяти 210 может быть частью одного кристалла, а другая часть памяти 208 ID может быть частью другого кристалла.

[0028] Далее приведены дополнительные примеры различных компоновок. В первой компоновке, как показано на фиг. 2A, как память 208 ID, так и зарядная память 210 могут быть на кристалле 220 выброса текучей среды. Линию ID используют для передачи данных между контроллером 202 выброса текучей среды и памятью 208 ID на кристалле выброса текучей среды, а зарядную линию используют для передачи данных между контроллером 202 выброса текучей среды и зарядной памятью 210 на кристалле выброса текучей среды.

[0029] Во второй компоновке, как показано на фиг. 2B, память 208 ID представляет собой часть кристалла 220 выброса текучей среды, а зарядная память 210 представляет собой часть второго кристалла 222. Линию ID используют для передачи данных между контроллером 202 выброса текучей среды и памятью 208 ID на кристалле 220 выброса текучей среды, а зарядную линию используют для передачи данных между контроллером 202 выброса текучей среды и зарядной памятью 210 на втором кристалле 222.

[0030] В третьей компоновке, как показано на фиг. 2C, зарядная память 210 представляет собой часть кристалла 220 выброса текучей среды, а память 208 ID представляет собой часть второго кристалла 222. Линию ID используют для передачи данных между контроллером 202 выброса текучей среды и памятью 208 ID на втором кристалле 222, а зарядную линию используют для передачи данных между контроллером 202 выброса текучей среды и зарядной памятью 210 на кристалле 220 выброса текучей среды.

[0031] В четвертой компоновке, как показано на фиг. 2D, память 208 ID и зарядная память 210 находятся на втором кристалле 220, отделенном от кристалла 220 выброса текучей среды. Линию ID используют для передачи данных между контроллером 202 выброса текучей среды и памятью 208 ID на втором кристалле 222, а зарядную линию используют для передачи данных между контроллером 202 выброса текучей среды и зарядной памятью 210 на втором кристалле 222.

[0032] В пятой компоновке, как показано на фиг. 2E, как первая часть 208-1 памяти ID, так и первая часть 210-1 зарядной памяти могут находиться на кристалле 220 выброса текучей среды, а вторая часть 208-2 памяти ID и вторая часть 210-2 зарядной памяти могут находиться на втором кристалле 222. Линию ID используют для передачи данных между контроллером 202 выброса текучей среды и частями 208-1 и 208-2 памяти ID на кристалле 220 выброса текучей среды и втором кристалле 222, а зарядную линию используют для передачи данных между контроллером 202 выброса текучей среды и частями 210-1 и 210-2 зарядной памяти на кристалле 220 выброса текучей среды и втором кристалле 222.

[0033] В шестой компоновке, как показано на фиг. 2F, первая часть 208-1 памяти ID и зарядная память 210 могут находиться на кристалле 220 выброса текучей среды, а вторая часть 208-2 памяти ID может находиться на втором кристалле 222. Линию ID используют для передачи данных между контроллером 202 выброса текучей среды и частями 208-1 и 208-2 памяти ID на кристалле 220 выброса текучей среды и втором кристалле 222, а зарядную линию используют для передачи данных между контроллером 202 выброса текучей среды и зарядной памятью 210 на кристалле 220 выброса текучей среды.

[0034] В седьмой компоновке, как показано на фиг. 2G, память 208 ID и первая часть 210-1 зарядной память могут находиться на кристалле 220 выброса текучей среды, а вторая часть 210-2 зарядной памяти может находиться на втором кристалле 222. Линию ID используют для передачи данных между контроллером 202 выброса текучей среды и памятью 208 ID на кристалле 220 выброса текучей среды, а зарядную линию используют для передачи данных между контроллером 202 выброса текучей среды и частями 210-1 и 210-2 зарядной памяти на кристалле 220 выброса текучей среды и втором кристалле 222.

[0035] В других примерных компоновках в дополнение к кристаллу выброса текучей среды можно использовать более одного второго кристалла, причем часть(и) памяти ID и/или часть(и) зарядной памяти можно распределять по нескольким вторым кристаллам.

[0036] Кроме того, несмотря на то, что фиг. 2 показывает пример, где имеются памяти двух различных типов, следует отметить, что в других примерах в устройстве 204 выброса текучей среды может содержаться только один тип памяти.

[0037] Устройство 204 выброса текучей среды связывают с управляющей цепью 212, которая реагирует на различные управляющие сигналы, передаваемые по управляющим линиям 214, управляя приведением в действие или доступом к массиву 206 форсунок, памяти 208 ID и зарядной памяти 210. Управляющие линии 214 включают зарядную линию, линию CSYNC (Composite synchronization, т.е. линию синхронизации композитного сигнала), линию выбора, линию данных адресов, линию ID и другие линии. В других примерах могут иметься несколько зарядных линий и/или несколько линий выбора и/или несколько линий данных адресов.

[0038] Управляющая цепь 212 содержит селектор 216 (который схож с селектором 106 по фиг. 1). Селектор 216 может выбирать одно из массива 206 форсунок и зарядной памяти 210 на основе значения линии данных (которая на фиг. 2 представляет собой линию ID, которую используют для записи и считывания идентификационных данных из памяти 208 ID).

[0039] Зарядную линию используют для управления приведением в действие массива 206 форсунок, когда массив 206 форсунок выбирается селектором 216 в случае первого значения линии ID. Зарядный сигнал, переносимый зарядной линией, при задании первого состояния, вызывает приведение в действие соответствующей форсунки (или форсунок), если к такой форсунке (или форсункам) обращаются (осуществляют адресацию) на основе значений линий выбора и данных адресов. Если зарядный сигнал имеет второе значение, отличное от первого значения, тогда форсунку (или форсунки) не приводят в действие.

[0040] Сигнал CSYNC используют для инициирования адреса (называемого Ax и Ay в текущем обсуждении) в устройстве 204 выброса текучей среды. Линию выбора можно использовать для выбора определенных форсунок или элементов памяти. Линию данных адресов используют для переноса бита адреса (или битов адреса) для осуществления адресации к конкретной форсунке или элементу памяти (или конкретной группе форсунок или группе элементов памяти).

[0041] В соответствии с некоторыми реализациями по настоящему раскрытию, для улучшения гибкости и снижения числа площадок ввода/вывода (I/O), которые должны предусматриваться на устройстве 204 выброса текучей среды, каждая из зарядной линии и линии ID (или в более общем случае - линии данных) выполняет как первичные, так и вторичные задачи. Как указано выше, первичная задача зарядной линии состоит в приведении в действие выбранной форсунки(ок). Вторичная задача зарядной линии состоит в передаче данных зарядной памяти 210. Таким образом, тракт передачи данных можно предусматривать между контроллером 202 выброса текучей среды и зарядной памятью 210 (поверх зарядной линии), без необходимости предусматривать отдельную линию данных между контроллером 202 выброса текучей среды и устройством 204 выброса текучей среды.

[0042] Первичная задача линии ID состоит в передаче данных памяти 208 ID. Вторичная задача линии ID состоит в побуждении селектора 216 выбирать одно из массива 206 форсунок и зарядной памяти 210. Таким образом, общую зарядную линию можно использовать для управления приведением в действие массива 206 форсунок и передачи данных зарядной памяти 210, причем линию ID используют для выбора того, когда массивом 206 форсунок управляют с помощью зарядной линии и когда зарядную линию можно использовать для передачи данных зарядной памяти 210.

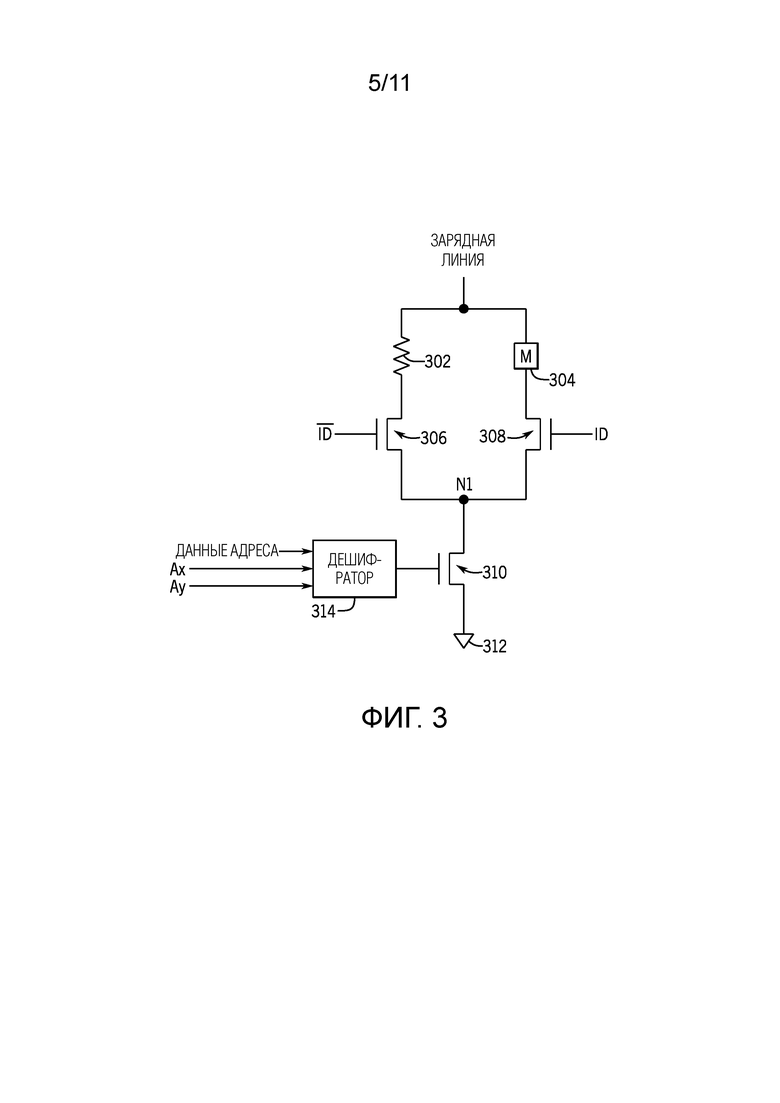

[0043] Фиг. 3 представляет собой примерную схему цепи, которая содержит элемент 302 активации форсунки и элемент 304 памяти. В некоторых примерах элемент 302 активации форсунки выполнен в виде терморезистора, который при приведении в действие нагревает текучую среду в камере для текучей среды форсунки, вызывая выброс текучей среды из сопла для текучей среды в форсунке. В других примерах элемент активации форсунки может содержать пьезоэлектрический элемент или элемент активации форсунки другого типа. В некоторых примерах элемент 304 памяти может быть частью зарядной память 210 по фиг. 2.

[0044] На фиг. 3 первый переключатель (который можно реализовать с использованием транзистора 306) последовательно соединен с элементом 302 активации форсунки между зарядной линией и узлом N1. Второй переключатель (который можно реализовать с использованием транзистора 308) последовательно соединен с элементом 304 памяти между зарядной линией и узлом N1. Транзистор 306 имеет затвор, управляемый с помощью  , а транзистор 308 имеет затвор, управляемый с помощью ID.

, а транзистор 308 имеет затвор, управляемый с помощью ID.  представляет обратную величину относительно ID. Например, ID можно подавать на ввод инвертора, который выдает

представляет обратную величину относительно ID. Например, ID можно подавать на ввод инвертора, который выдает  .

.

[0045] Таким образом, когда транзистор 308 включается с помощью ID (задают активное значение, такое как высокое значение), транзистор 306 выключается при выключении  (поскольку для

(поскольку для  задают неактивное значение, такое как низкое значение). С другой стороны, когда транзистор 306 включается с помощью

задают неактивное значение, такое как низкое значение). С другой стороны, когда транзистор 306 включается с помощью  (задают активное значение, такое как высокое значение), транзистор 308 выключается.

(задают активное значение, такое как высокое значение), транзистор 308 выключается.

[0046] Таким образом, транзисторы 306 и 308 могут выбирать или элемент 302 активации форсунки или элемент 304 памяти. Транзисторы 306 и 308 в компоновке по фиг. 3 представляют собой часть селектора 106 (фиг. 1) или селектора 216 (фиг. 2).

[0047] Фиг. 3 дополнительно изображает переключатель (реализованный в виде транзистора 310) между узлом N1 и опорным напряжением 312, таким как земля. Затвор транзистора 310 соединен с выводом средства 314 декодирования (дешифратора), который принимает ввод адреса (входной сигнал выборки адреса). Дешифратор 314 может быть частью управляющей цепи 212, показанной на фиг. 2.

[0048] Ввод адреса включает адрес, предоставляемый с помощью бита(ов) адреса линии данных адресов и сигналов Ax и Ay. Сигналы Ax и Ay в некоторых примерах выводят с помощью генератора адресов (не показан на фиг. 3) в ответ на линию выбора и линию CSYNC. Несмотря на то, что на фиг. 3 изображен ввод конкретного адреса, следует отметить, что дешифратор 314 в целом принимает адрес в виде входного сигнала и управляет приведением в действие транзистора 310 на основе этого адреса. Дешифратор может эффективно приводить в действие или поддерживать выведенным из действия элемент 302 активации форсунки или элемент 304 памяти (которые выбраны линией ID) в ответ на ввод адреса.

[0049] В целом, в соответствии с фиг. 3, цепь для использования с элементом памяти и форсункой для выпуска текучей среды содержит линию данных, зарядную линию и селектор. Селектор содержит первый переключатель, реагирующий на первое значение линии данных с выбором элемента памяти, и содержит второй переключатель, реагирующий на второе значение линии данных с выбором форсунки. Зарядная линия управляет приведением в действие форсунки в ответ на выбор форсунки селектором и передавая данные элемента памяти в ответ на выбор элемента памяти селектором. Цепь дополнительно содержит дешифратор, реагирующий на ввод адреса с выбором элемента памяти или форсунки.

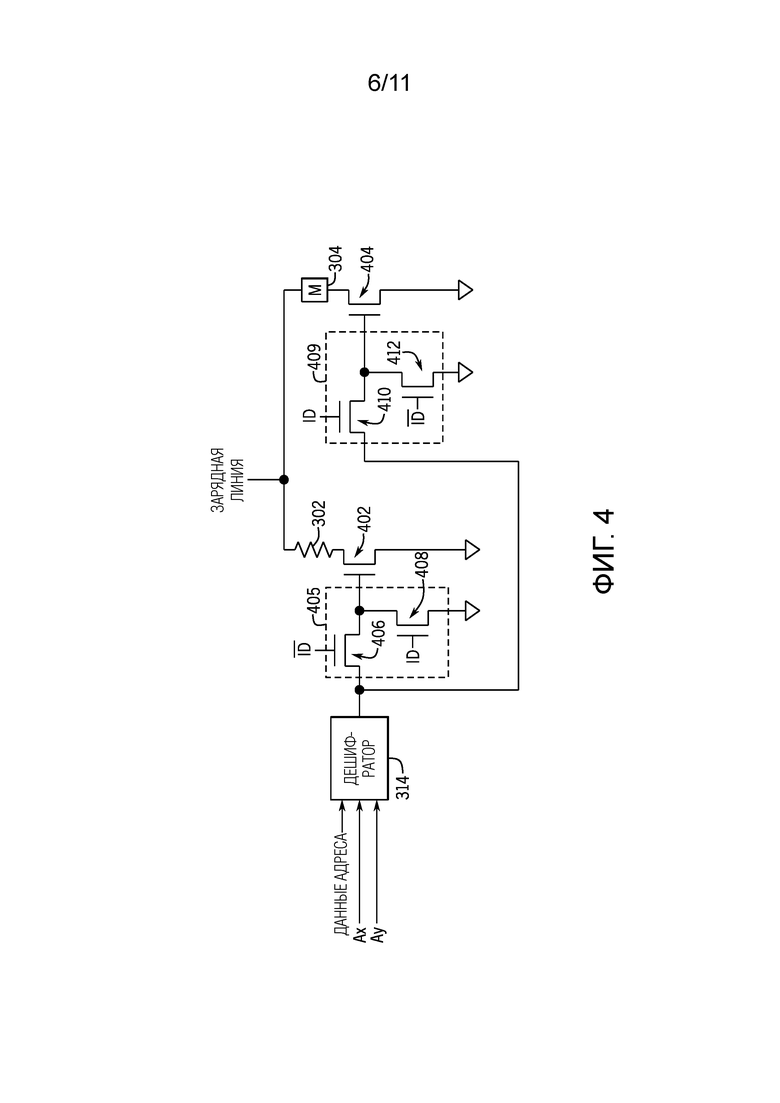

[0050] Фиг. 4 представляет собой схематическую диаграмму другой примерной компоновки для выборочного приведения в действие/доступа к элементу 302 активации форсунки и элементу 304 памяти. На фиг. 4 первый транзистор 402 последовательно соединен с элементом 302 активации форсунки между зарядной линией и опорным напряжением, а второй транзистор 404 последовательно соединен с элементом 304 памяти между зарядной линией и опорным напряжением.

[0051] Затвор транзистора 402 соединен с первым блоком 405 переключателей, которые содержат транзистор 406 (управляемый с помощью  ) и транзистор 408 (управляемый с помощью ID). Транзистор 406 при включении с помощью

) и транзистор 408 (управляемый с помощью ID). Транзистор 406 при включении с помощью  соединяет вывод дешифратора 314 с затвором транзистора 402. Транзистор 408 присоединен между затвором транзистора 402 и опорным напряжением.

соединяет вывод дешифратора 314 с затвором транзистора 402. Транзистор 408 присоединен между затвором транзистора 402 и опорным напряжением.

[0052] Затвор транзистора 404 соединен со вторым блоком 409 переключателей, содержащих транзистор 410 и транзистор 412. Затвор транзистора 410 соединен с ID, а затвор транзистора 412 соединен с  . При включении транзистор 410 соединяет вывод дешифратора 314 с затвором транзистора 404, а транзистор 412 подсоединен между затвором транзистора 404 и опорным напряжением.

. При включении транзистор 410 соединяет вывод дешифратора 314 с затвором транзистора 404, а транзистор 412 подсоединен между затвором транзистора 404 и опорным напряжением.

[0053] Основываясь на чередующихся соединениях ID и  с затворами соответствующих транзисторов 406, 408, 410 и 412, первый блок 405 переключателей, содержащих транзисторы 406 и 408, приводится в действие, когда

с затворами соответствующих транзисторов 406, 408, 410 и 412, первый блок 405 переключателей, содержащих транзисторы 406 и 408, приводится в действие, когда  находится в активном состоянии, с соединением вывода дешифратора с затвором транзистора 402. С другой стороны, второй блок 409 переключателей, содержащих транзисторы 410 и 412, приводится в действие в ответ на ID, находящийся в активном состоянии, с соединением вывода дешифратора с затвором транзистора 404.

находится в активном состоянии, с соединением вывода дешифратора с затвором транзистора 402. С другой стороны, второй блок 409 переключателей, содержащих транзисторы 410 и 412, приводится в действие в ответ на ID, находящийся в активном состоянии, с соединением вывода дешифратора с затвором транзистора 404.

[0054] Каждый блок 405 или 409 переключателей при выведении из действия изолирует вывод дешифратора от соответствующего затвора транзистора 402 или 404.

[0055] В компоновке по фиг. 4, блоки 405 и 409 переключателей представляют собой часть селектора 106 (фиг. 1) или селектора 216 (фиг. 2). Дешифратор 314 представляет собой часть управляющей цепи 212 по фиг. 2.

[0056] В целом, в соответствии по фиг. 4, цепь для использования с элементом памяти и форсункой для выпуска текучей среды содержит линию данных, зарядную линию и селектор. Селектор содержит первый блок переключателей, реагирующий на первое значение линии данных с выбором элемента памяти, и содержит второй блок переключателей, реагирующий на второе значение линии данных с выбором форсунки. Зарядная линия управляет приведением в действие форсунки в ответ на выбор форсунки селектором и передавая данные элемента памяти в ответ на выбор элемента памяти селектором. Цепь дополнительно содержит дешифратор, реагирующий на ввод адреса с выбором элемента памяти или форсунки.

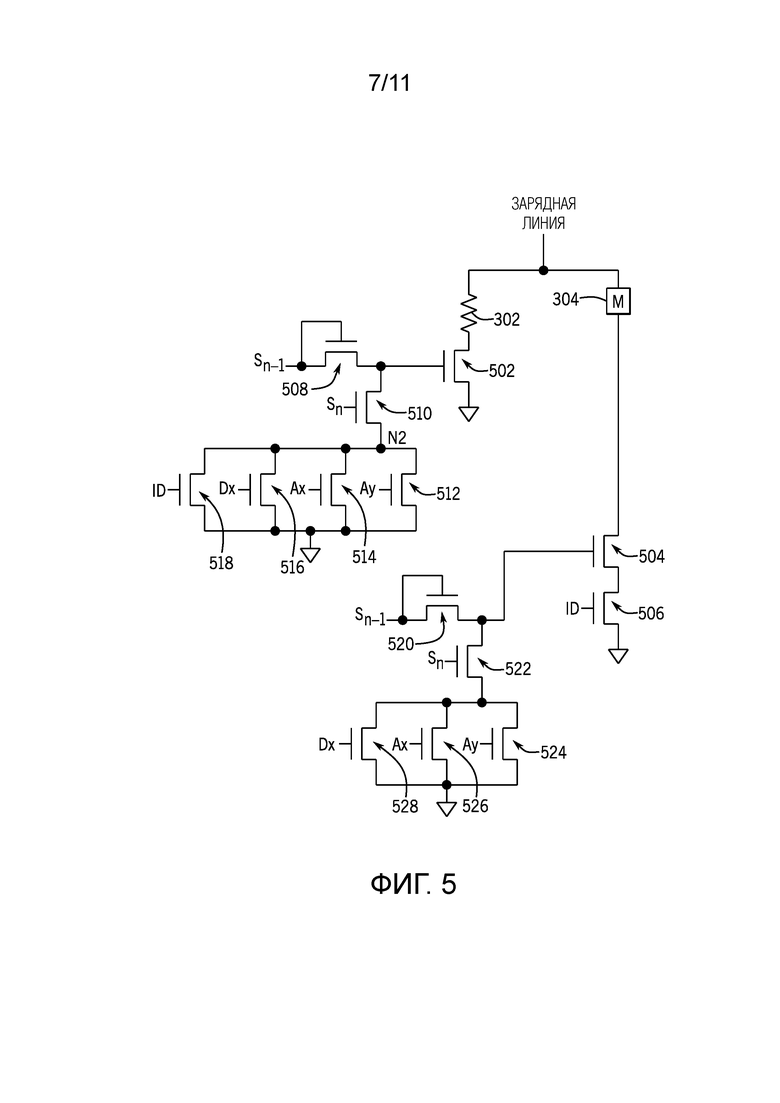

[0057] Фиг. 3 и 4 изображают примерные компоновки, где для осуществления адресации к элементу 302 активации памяти и элементу 304 памяти используют только один дешифратор. В альтернативных примерах для осуществления адресации соответственно к элементу 302 активации памяти и элементу 304 памяти можно использовать несколько дешифраторов. Пример такой двойной компоновки дешифраторов показан на фиг. 5.

[0058] На фиг. 5 элемент 302 активации памяти и транзистор 502 последовательно соединены между зарядной линией и опорным напряжением. Элемент 304 памяти последовательно соединен с транзисторами 504 и 506 между зарядной линией и опорным напряжением.

[0059] Затвором транзистора 502 управляют с помощью первого дешифратора, который содержит транзисторы 508, 510, 512, 514 и 516. Sn представляет сигнал выбора, тогда как Sn-1 представляет другой сигнал выбора. Сигналы выбора Sn и Sn-1 передают по линии(ям) выбора. Сигнал выбора Sn-1 можно активировать раньше по времени, чем сигнал выбора Sn.

[0060] Транзистор 508 выполнен в виде диода и представляет собой транзистор предварительной зарядки для предварительной зарядки затвора транзистора 508, соединенного с истоком транзистора 508. Сигнал выбора Sn-1 передают через транзистор 508 предварительной зарядки на затвор транзистора 502.

[0061] Транзистор 510 подсоединен между затвором транзистора 502 и узлом N2. Транзисторы 512, 514 и 516 соединены параллельно между узлом N2 и опорным напряжением. Затвор транзистора 512 соединен с Ay, затвор транзистора 514 соединен с Ax и затвор транзистора 516 соединен с битом Dx данных адреса. Комбинация Ax, Ay, Dx, Sn и Sn-1 образует ввод (входной сигнал) адреса на первый дешифратор.

[0062] На фиг. 5 другой транзистор 518 соединен параллельно с транзисторами 512, 514 и 516. Затвор транзистора 518 соединен с ID. Транзистор 518 представляет собой часть селектора (106 или 216), тогда как первый дешифратор (включая транзисторы 508, 510, 512, 514 и 516) представляет собой часть управляющей цепи 212.

[0063] Затвор транзистора 504 соединен со вторым дешифратором, который содержит транзисторы 520, 522, 524, 526 и 528. Транзисторы 520, 522, 524, 526 и 528 второго дешифратора соединены аналогичным образом, как соответствующие транзисторы 508, 510, 512, 514 и 516 первого дешифратора.

[0064] Как дополнительно показано на фиг. 5, затвор транзистора 506 соединен с ID. Транзистор 506 представляет собой часть селектора (106 или 216), тогда как второй дешифратор, содержащий транзисторы 520, 522, 524, 526 и 528, представляет собой часть управляющей цепи 212.

[0065] Как показано на фиг. 5, два отдельных дешифратора используют для управления соответствующими транзисторами 502 и 504, которые соединены соответственно с элементом 302 активации форсунки и элементом 304 памяти.

[0066] Когда ID находится в активном состоянии (например, состоянии с высоким уровнем), транзистор 518 побуждает затвор транзистора 502 оставаться разряженным (т.е. деактивирует затвор транзистора 502), так что элемент 302 активации форсунки поддерживается выведенным из действия. С другой стороны, когда ID находится в активном состоянии (например, состоянии с высоким уровнем), устанавливают тракт сигнала через транзистор 506, так что когда транзистор 504 включается на основе ввода адреса во второй дешифратор, данные элемента 304 памяти можно передавать по зарядной линии.

[0067] С другой стороны, когда ID находится в неактивном состоянии (например, состоянии с низким уровнем), транзистор 506 остается выключенным, так что отменяется выбор элемента 304 памяти. Однако, когда ID находится в неактивном состоянии (например, состоянии с низким уровнем), транзистор 518 выключается, так что затвор транзистора 502 может заряжаться до активного состояния (т.е. транзистор 518 обеспечивает предварительную зарядку затвора транзистора 502) для включения транзистора 502, когда вводом адреса в первый дешифратор побуждают первый дешифратор приводить в действие затвор транзистора 502.

[0068] В целом, в соответствии по фиг. 5, цепь для использования с элементом памяти и форсункой для выпуска текучей среды содержит линию данных, зарядную линию и селектор. Селектор содержит первый переключатель, реагирующий на первое значение линии данных с выбором элемента памяти, и содержит второй переключатель, реагирующий на второе значение линии данных с выбором форсунки. Зарядная линия управляет приведением в действие форсунки в ответ на выбор форсунки селектором и передавая данные элемента памяти в ответ на выбор элемента памяти селектором. Цепь дополнительно содержит первый дешифратор, реагирующий на ввод адреса с выбором элемента памяти, и содержит второй дешифратор, реагирующий на ввод адреса с выбором форсунки.

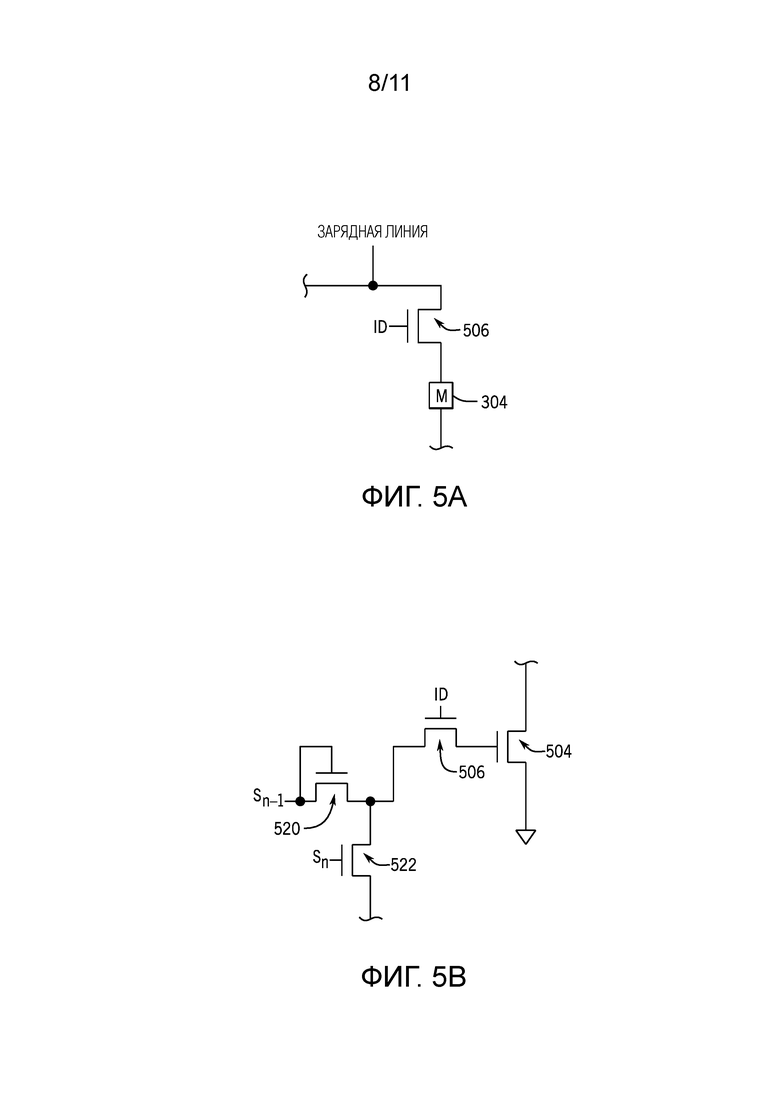

[0069] На фиг. 5 транзистор 506, управляемый с помощью линии ID, подсоединен между транзистором 504 и опорным напряжением. В других вариантах транзистор 506, управляемый с помощью линии ID, можно перемещать в другую часть цепи. В одном таком варианте, как показано на фиг. 5A, транзистор 506 подсоединен между зарядной линией и элементом 304 памяти. Альтернативно, в другом варианте, показанном на фиг. 5B, транзистор 506, управляемый с помощью линии ID, соединен в качестве запускающего включателя с затвором транзистора 504, т.е. сток транзистора 506 соединен с общим узлом, который соединяет исток транзистора 520 и сток транзистора 522, а исток транзистора 506 соединен с затвором транзистора 504.

[0070] На фиг. 6 изображена примерная компоновка, в которой используют цепь по фиг. 5. Компоновка по фиг. 6 содержит память 208 ID, зарядную память 210 и массив 206 форсунок. На фиг. 6 зарядная память 210 содержит элемент 304 памяти и транзисторы 504, 506, 520, 522, 524, 526 и 528. Следует отметить, что компоновку цепей в зарядной памяти 210, показанную на фиг. 6, можно повторять для других элементов памяти в зарядной памяти 210.

[0071] Массив 206 форсунок содержит элемент 302 активации форсунки и транзисторы 502, 508, 510, 512, 514, 516 и 518. Компоновку цепи, показанную на фиг. 6 для массива 206 форсунок, можно повторять для других элементов активации форсунок массива 206 форсунок.

[0072] Как показано на фиг. 6, Ax и Ay выводят с помощью генератора 602 адресов, например, так, как в ответ на сигнал выбора в линии выбора и сигнал CSYNC в линии CSYNC.

[0073] Память 208 ID содержит элемент 604 памяти и транзисторы 608, 610 и 612, соединенные последовательно между линией ID и опорным напряжением. При включении транзисторов 608, 610 и 612 осуществляется адресация к элементу 604 памяти, так что данные элемента 604 памяти могут быть переданы по линии ID. Затворы транзисторов 608, 610 и 612 соединены с выводами дешифратора 614 с регистром сдвига, который принимает биты D[ ] данных адреса (и также линиями выбора).

[0074] Дешифратор 614 с регистром сдвига содержит регистры сдвига, соединенные с каждым из битов D[ ] данных адреса, которые вводят в дешифратор 614 с регистром сдвига. Каждый регистр сдвига содержит последовательность ячеек регистра сдвига, которую можно реализовать в виде триггеров, других запоминающих элементов или любых цепей выборки и хранения (таких как цепи для предварительной зарядки и оценки битов данных адреса), которые могут сохранять свои значения до следующего выбора запоминающих элементов. Вывод одной ячейки регистра сдвига в последовательности можно предоставлять на ввод следующей ячейки регистра сдвига для осуществления сдвига данных через регистр сдвига. Биты данных адреса, предоставляемые с помощью каждого регистра сдвига, соединяют с затвором соответствующего одного из транзисторов 608, 610 и 612. Используя регистры сдвига в дешифраторе 614 с регистром сдвига, небольшое число битов данных адреса D[ ] можно использовать для выбора в большем пространстве адресов. Например, каждый регистр сдвига может содержать 8 (или любое другое число) ячеек регистра сдвига. Полагая, что три бита данных адреса вводят в дешифратор 614 с регистром сдвига, который содержит три регистра сдвига, каждый длиной 8, пространство адресов, к которому можно осуществлять адресацию с помощью дешифратора 614 с регистром сдвига, составляет 512 битов (вместо просто 8 битов, если три бита адреса D[ ] применяют без использования регистров сдвига дешифратор 614 с регистром сдвига).

[0075] Хронированием различных сигналов, показанных на фиг. 6, управляют с тем, чтобы не происходила порча данных в ходе программирования элемента 604 памяти в памяти 208 ID, программирования элемента 304 памяти в зарядной памяти 210 и приведения в действие элемента 302 активации форсунки из массива 206 форсунок. Другими словами, при осуществлении доступа к памяти 208 ID, зарядной памятью 210 и массивом 206 форсунок управляют, чтобы они были неактивными. С другой стороны, при осуществлении доступа к зарядной памяти 210, памятью 208 ID в массиве 206 форсунок управляют для того, чтобы она была неактивной. При приведении в действие массива 206 форсунок, памятью 208 ID и зарядной памятью 210 управляют, чтобы они были неактивными.

[0076] В дополнительных примерах, если используют несколько зарядных линий, то данные можно считывать из элементов памяти зарядной памяти 210 параллельно, увеличивая эффективность доступа к зарядной памяти 210 по зарядным линиям.

[0077] Фиг. 7 представляет собой схематическую диаграмму другой примерной компоновки, в которой используют дешифратор, схожий с первым дешифратором по фиг. 5 (включающий в себя транзисторы 508, 510, 512, 514 и 516), чтобы управлять затвором транзистора 502, который соединен последовательно с элементом 302 активации форсунки и опорным напряжением. Кроме того, транзистором 518 (соединенным параллельно с транзисторами 508, 510, 512, 514 и 516) управляют с помощью ID.

[0078] Элемент 304 памяти соединен последовательно с транзисторами 702, 706, 708 и 710. Транзистором 702 управляют с помощью ID, а затворы транзисторов 706, 708 и 710 соединены с выводами дешифратора 712 с регистром сдвига. Дешифратор 712 с регистром сдвига выполнен подобно дешифратору 614 с регистром сдвига по фиг. 6. Дешифратор 712 с регистром сдвига содержит несколько регистров сдвига для приема соответствующих битов D[ ] данных адреса. Кроме того, дешифратор 712 с регистром сдвига также содержит ввод выбора для приема сигнала выбора Sn; если Sn активен, регистры сдвига дешифратора 712 с регистром сдвига могут принимать соответствующие биты D[ ] данных адреса и сдвигать биты адреса по соответствующим ячейкам регистра сдвига.

[0079] Когда ID находится в активном состоянии (например, состоянии с высоким уровнем), выбирают элемент 304 памяти, если биты D[ ] данных адреса и сигнал выбора Sn соответствуют элементу 304 памяти. Когда ID находится в неактивном состоянии (например, состоянии с низким уровнем), память элемент 302 активации форсунки выбирают, если биты D[ ] данных адреса и сигнал выбора Sn соответствуют элементу 302 активации форсунки.

[0080] Транзисторы 702 и 518 на фиг. 7 представляют собой часть селектора 106 или 216, а дешифратор (содержащий транзисторы 508, 510, 512, 514 и 516) и дешифратор 712 с регистром сдвига представляют собой часть управляющей цепи 212 по фиг. 2.

[0081] В целом, в соответствии по фиг. 7, цепь для использования с элементом памяти и форсункой для выпуска текучей среды содержит линию данных, зарядную линию и селектор. Селектор содержит первый переключатель, реагирующий на первое значение линии данных с выбором элемента памяти, и содержит второй переключатель, реагирующий на второе значение линии данных с выбором форсунки. Зарядная линия управляет приведением в действие форсунки в ответ на выбор форсунки селектором и передавая данные элемента памяти в ответ на выбор элемента памяти селектором. Цепь дополнительно содержит дешифратор, реагирующий на ввод адреса с выбором форсунки, содержит дешифратор с регистром сдвига, реагирующий на ввод адреса с выбором элемента памяти.

[0082] На фиг. 8 изображено устройство (например, картридж или устройство другого типа), которое имеет один или более кристаллов 800, содержащих элемент 802 памяти, форсунку 804, зарядную линию, соединенную с форсункой 804, и элемент 802 памяти, и линию данных. Устройство дополнительно содержит селектор 806, реагирующий на линию данных с выбором элемента 802 памяти или форсунки 804, причем селектор 806 выбирает элемент 802 памяти в случае линии данных, имеющей первое значение, и выбирает форсунку 804 в случае линии данных, имеющей второе значение, отличное от первого значения. Зарядная линия управляет приведением в действие форсунки 804 в ответ на выбор форсунки 804 селектором 806, и осуществляет передачу данных элемента 802 памяти в ответ на выбор элемента 802 памяти селектором 806.

[0083] В вышеприведенном описании для обеспечения раскрытого здесь предмета изложены многочисленные детали. Однако реализации могут быть осуществлены на практике без некоторых из этих деталей. Другие реализации могут включать модификации и вариации из обсужденных выше деталей. Подразумевается, что приложенная формула изобретения охватывает такие модификации и вариации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВА ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ, ВКЛЮЧАЮЩИЕ В СЕБЯ ПЕРВУЮ ПАМЯТЬ И ВТОРУЮ ПАМЯТЬ | 2019 |

|

RU2779068C1 |

| ВХОДНЫЕ УПРАВЛЯЮЩИЕ СИГНАЛЫ, ПРОХОДЯЩИЕ ПО СИГНАЛЬНЫМ ПУТЯМ | 2016 |

|

RU2710691C1 |

| ПЕЧАТАЮЩИЙ КОМПОНЕНТ СО СХЕМОЙ ПАМЯТИ | 2019 |

|

RU2778211C1 |

| УСТРОЙСТВО ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ СО ВСТРОЕННЫМ ДАТЧИКОМ УРОВНЯ ЧЕРНИЛ | 2012 |

|

RU2635080C2 |

| ДОСТУП К БЛОКАМ ПАМЯТИ В БАНКЕ ПАМЯТИ | 2017 |

|

RU2748727C2 |

| ИНТЕГРАЛЬНЫЕ СХЕМЫ, ВКЛЮЧАЮЩИЕ В СЕБЯ ЗАПОМИНАЮЩИЕ ЯЧЕЙКИ | 2019 |

|

RU2779793C1 |

| ПЕЧАТАЮЩИЙ КОМПОНЕНТ С МАТРИЦЕЙ ПАМЯТИ, ИСПОЛЬЗУЮЩИЙ ПУЛЬСИРУЮЩИЙ ТАКТОВЫЙ СИГНАЛ | 2019 |

|

RU2780707C1 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА С АДРЕСНЫМИ ФОРМИРОВАТЕЛЯМИ ДЛЯ СТРУЙНОЙ МАТРИЦЫ | 2019 |

|

RU2780403C1 |

| СИСТЕМА И СПОСОБ ДЛЯ МАЛОМОЩНОЙ ЛОГИКИ ЧИСЛОВОЙ ШИНЫ В ПАМЯТИ | 2007 |

|

RU2424586C2 |

Заявленное изобретение относится к области систем печати, которые содержат печатающую головку, которая имеет форсунки для распределения печатающей текучей среды по мишени. Цепь для использования с элементом памяти и форсункой для выпуска текучей среды содержит линию данных, зарядную линию и селектор, реагирующий на линию данных с выбором элемента памяти или форсунки. Селектор предназначен для выбора элемента памяти в случае линии данных, имеющей первое значение, и для выбора форсунки в случае линии данных, имеющей второе значение, отличное от первого значения. Зарядная линия предназначена для управления приведением в действие форсунки в ответ на выбор форсунки селектором и для передачи данных элемента памяти в ответ на выбор элемента памяти селектором. В цепи совместно используются линии управления и линии данных, обеспечивая уменьшение числа сигнальных линий устройства выброса текучей среды, увеличивая площадь свободного полезного пространства в упомянутом устройстве. 3 н. и 14 з.п. ф-лы, 17 ил.

1. Цепь для использования с первым элементом памяти и форсункой для выпуска текучей среды, содержащая:

линию данных;

зарядную линию; и

селектор, реагирующий на линию данных выбором первого элемента памяти или форсунки, при этом селектор предназначен для выбора первого элемента памяти в случае линии данных, имеющей первое значение, и для выбора форсунки в случае линии данных, имеющей второе значение, отличное от первого значения, при этом линия данных предназначена для передачи данных второго элемента памяти, при этом второй элемент памяти представляет собой тип памяти, отличный от первого элемента памяти,

при этом зарядная линия предназначена для управления приведением в действие форсунки в ответ на выбор форсунки селектором и для передачи данных первого элемента памяти в ответ на выбор первого элемента памяти селектором.

2. Цепь по п. 1, дополнительно содержащая:

дешифратор для приема адреса и обеспечения доступа к первому элементу памяти в ответ на адрес.

3. Цепь по п. 2, в которой дешифратор предназначен для обеспечения приведения в действие форсунки в ответ на адрес.

4. Цепь по п. 3, в которой селектор содержит:

первый переключатель для соединения с первым элементом памяти, при этом первый переключатель приводится в действие, когда линия данных имеет первое значение; и

второй переключатель для соединения с элементом активации форсунки для форсунки, при этом второй переключатель приводится в действие, когда линия данных имеет второе значение.

5. Цепь по п. 4, в которой первый переключатель содержит первый транзистор для соединения последовательно с первым элементом памяти, а второй переключатель содержит второй транзистор для соединения последовательно с элементом активации форсунки, и

при этом затвор первого транзистора соединен с линией данных, а затвор второго транзистора соединен с обратной величиной линии данных.

6. Цепь по п. 3, в которой селектор содержит:

первый переключатель для соединения вывода дешифратора с первым транзистором последовательно с первым элементом памяти в случае линии данных, имеющей первое значение; и

второй переключатель для соединения вывода дешифратора со вторым транзистором последовательно с элементом активации форсунки для форсунки в случае линии данных, имеющей второе значение.

7. Цепь по п. 2, в которой дешифратор представляет собой первый дешифратор, а цепь дополнительно содержит:

второй дешифратор для приема адреса и обеспечения приведения в действие элемента активации форсунки для форсунки в ответ на адрес.

8. Цепь по любому из пп. 1-7, в которой линия данных предназначена для передачи данных второго элемента памяти в ответ на обеспечение доступа ко второму элементу памяти.

9. Цепь по п. 1, дополнительно содержащая:

дешифратор для приема адреса и для обеспечения приведения в действие элемента активации форсунки для форсунки в ответ на адрес.

10. Цепь по п. 9, дополнительно содержащая:

регистры сдвига для приема вводов адреса и обеспечения доступа к первому элементу памяти в ответ на вводы адреса.

11. Цепь для использования с первым элементом памяти и форсункой для выпуска текучей среды, содержащая:

селектор, содержащий:

первый транзистор для выбора первого элемента памяти для доступа в ответ на установку линии данных на первое значение;

второй транзистор для выбора элемента активации форсунки для форсунки для приведения в действие в ответ на установку линии данных на второе значение, отличное от первого значения, при этом линия данных предназначена для передачи данных второго элемента памяти, при этом второй элемент памяти представляет собой тип памяти, отличный от первого элемента памяти; и

зарядную линию для передачи данных первого элемента памяти в ответ на выбор первым транзистором первого элемента памяти для доступа и для приведения в действие элемента активации форсунки в ответ на выбор вторым транзистором для приведения в действие элемента активации форсунки для форсунки.

12. Цепь по п. 11, в которой первый транзистор предназначен для последовательного соединения с первым элементом памяти и третьим транзистором, управляемым транзистором предварительной зарядки, который подает сигнал выбора на затвор третьего транзистора.

13. Цепь по п. 12, в которой второй транзистор предназначен для:

деактивации затвора третьего транзистора, соединенного последовательно с элементом активации форсунки, в ответ на установку линии данных на первое значение, и

обеспечения предварительной зарядки затвора третьего транзистора в ответ на установку линии данных на второе значение.

14. Устройство выброса текучей среды, содержащее:

один или более кристаллов, которые содержат:

форсунку для выпуска печатающей текучей среды;

первый элемент памяти;

зарядную линию, соединенную с форсункой и первым элементом памяти;

линию данных; и

селектор, реагирующий на линию данных выбором первого элемента памяти или форсунки, при этом селектор предназначен для выбора первого элемента памяти в случае линии данных, имеющей первое значение, и для выбора форсунки в случае линии данных, имеющей второе значение, отличное от первого значения, при этом линия данных предназначена для передачи данных второго элемента памяти, при этом второй элемент памяти представляет собой тип памяти, отличный от первого элемента памяти,

при этом зарядная линия предназначена для управления приведением в действие форсунки в ответ на выбор форсунки селектором и для передачи данных первого элемента памяти в ответ на выбор первого элемента памяти селектором.

15. Устройство по п. 14, в котором упомянутые один или более кристаллов содержат:

память первого типа, содержащую первый элемент памяти;

память второго, другого типа, содержащую второй элемент памяти.

16. Устройство по п. 14 или 15, в котором упомянутые один или более кристаллов содержат кристалл выброса текучей среды, который содержит форсунку.

17. Устройство по п. 16, в котором упомянутые один или более кристаллов содержат другой кристалл, отдельный от кристалла выброса текучей среды, содержащий первый элемент памяти.

| US 8864260 B1, 21.10.2014 | |||

| US 20070153030 A1, 05.07.2007 | |||

| US 20140320541 A1, 30.10.2014 | |||

| US 2007097745 A1, 03.05.2007. |

Авторы

Даты

2021-05-05—Публикация

2017-07-06—Подача