Изобретение относится к импульсной технике и предназначено для формирования периодической последовательности импульсов с настраиваемой длительностью импульсов, периода следования и задержки начала формирования относительно стартового импульса, кратными периоду непрерывной периодической последовательности импульсов, подаваемых на ее вход с выхода внешнего кварцевого генератора.

Известны генераторы, обеспечивающие формирование необходимых серий импульсов, содержащие кварцевый резонатор, работающий в непрерывном режиме, устройство синхронизации и выходное устройство, временные параметры которых определяются временными параметрами импульсов, подаваемых на вход (Тактовый генератор. А. С. СССР №307502. - Б. И. №20, 21.06.1971; Тактовый генератор. А. С. СССР №354544. - Б. И. №30, 09.11.1972).

Недостаток известных устройств - ограниченные функциональные возможности, обусловленные настройкой на фиксированный режим временных параметров выходной последовательности импульсов.

Наиболее близким по технической сути и достигаемому техническому результату, принятым за прототип, является формирователь тактовых импульсов (Формирователь тактовых импульсов. А. С. Украины №53542 - Б. И. №19, 11.10.2010), который содержит общий источник питания (±Е); первый и второй реверсивные двоичные счетчики, настроенные на режим вычитания, с входом разрешения синхронной параллельной загрузки и входами подачи настроечных переменных, входом разрешения режима счета и входом асинхронной установки в нулевое состояние, выходами переполнения; первый; конденсатор, триггер с входом асинхронной установки нуля; первый и второй двухвходовые элементы И, двухвходовый элемент ИЛИ; трехвходовый элемент ИЛИ; инвертор. При этом последовательно соединенные резистор и конденсатор подключены к общему источнику питания, а их общая точка соединена с первыми входами первого и второго элементов И, выход первого элемента И соединен с входом асинхронной установки триггера в нулевое состояние, второй вход второго элемента И соединен с выходом трехвходового элемента ИЛИ, выход переполнения первого счетчика соединен с входом инвертора, с первым входом двухвходового элемента ИЛИ и с первым входом трехвходового элемента ИЛИ, второй вход трехвходового элемента ИЛИ соединен с выходом триггера, второй вход двухвходового элемента ИЛИ соединен с выходом переполнения второго счетчика, выход второго элемента И соединен с входами асинхронной установки счетчиков в нулевое состояние; выход двухвходового элемента ИЛИ соединен с входом разрешения загрузки первого счетчика; выход инвертора соединен с входом разрешения режима счета первого счетчика; тактовые входы первого и второго счетчиков соединены между собой, образуя вход формирователя, на который поступает непрерывная периодическая последовательность импульсов с выхода внешнего кварцевого генератора.

С существенными признаками изобретения совпадает следующая совокупность признаков прототипа: общий источник питания (±Е); первый и второй реверсивные двоичные счетчики, настроенные на режим вычитания, с входом разрешения синхронной параллельной загрузки и входами подачи настроечных переменных, входом разрешения режима счета и входом асинхронной установки в нулевое состояние, выходами переполнения; резистор; конденсатор, триггер с входом асинхронной установки нуля; первый и второй двухвходовые элементы И; двухвходовый элемент ИЛИ; трехвходовый элемент ИЛИ; инвертор. При этом последовательно соединенные резистор и конденсатор подключены к общему источнику питания, а их общая точка соединена с первыми входами первого и второго элементов И, выход первого элемента И соединен с входом асинхронной установки триггера в нулевое состояние, второй вход второго элемента И соединен с выходом трехвходового элемента ИЛИ, выход переполнения первого счетчика соединен с входом инвертора, с первым входом двухвходового элемента ИЛИ и с первым входом трехвходового элемента ИЛИ, второй вход трехвходового элемента ИЛИ соединен с выходом триггера, второй вход двухвходового элемента ИЛИ соединен с выходом переполнения второго счетчика, выход второго элемента И соединен с входами асинхронной установки счетчиков в нулевое состояние; выход двухвходового элемента ИЛИ соединен с входом разрешения загрузки первого счетчика; выход инвертора соединен с входом разрешения режима счета первого счетчика; тактовые входы первого и второго счетчиков соединены между собой, образуя вход формирователя, на который поступает непрерывная периодическая последовательность импульсов с выхода внешнего кварцевого генератора.

Недостаток прототипа - ограниченные функциональные возможности, обусловленные фиксированным режимом временных параметров генерируемой последовательности импульсов.

Изобретение направлено на расширение функциональных возможностей формирователя за счет возможности менять временные параметры генерируемых импульсов.

Это достигается тем, что формирователь периодической последовательности импульсов содержит общий источник питания, первый и второй реверсивные двоичные счетчики, настроенные на режим вычитания, с входом разрешения синхронной параллельной загрузки и входами подачи настроечных переменных, входом разрешения режима счета и входом асинхронной установки в нулевое состояние, выходами переполнения, резистор, конденсатор, триггер с входом асинхронной установки нуля, первый и второй двухвходовые элементы И, двухвходовый элемент ИЛИ, трехвходовый элемент ИЛИ, инвертор. При этом, последовательно соединенные резистор и конденсатор подключены к общему источнику питания, а их общая точка соединена с первыми входами первого и второго элементов И. Выход первого элемента И соединен с входом асинхронной установки триггера в нулевое состояние. Второй вход второго элемента И соединен с выходом трехвходового элемента ИЛИ. Выход переполнения первого счетчика соединен с входом инвертора, с первым входом двухвходового элемента ИЛИ и с первым входом трехвходового элемента ИЛИ. Второй вход трехвходового элемента ИЛИ соединен с выходом триггера. Второй вход двухвходового элемента ИЛИ соединен с выходом переполнения второго счетчика, выход второго элемента И соединен с входами асинхронной установки счетчиков в нулевое состояние. Выход двухвходового элемента ИЛИ соединен с входом разрешения загрузки первого счетчика; выход инвертора соединен с входом разрешения режима счета первого счетчика. Тактовые входы первого и второго счетчиков соединены между собой, образуя вход формирователя, на который поступает непрерывная периодическая последовательность импульсов с выхода внешнего кварцевого генератора. В предложенном решении введены: четырехразрядный цифровой компаратор, задатчик уровня логической единицы, два четырехвходовых элемента ИЛИ, второй, третий и четвертый инверторы, первая и вторая кнопки, работающие на замыкание, второй, третий и четвертый резисторы, первые выводы которых соединены с плюсом источника питания. Второй вывод второго резистора образует вывод уровня логической единицы. Второй вывод третьего резистора соединен с входом асинхронной установки триггера в единичное состояние и первым контактом первой кнопки. Второй вывод четвертого резистора соединен с вторым входом первого элемента И и первым контактом второй кнопки. Вторые контакты кнопок соединены с общей точкой источника питания. Выход переполнения второго счетчика соединен с входом второго инвертора, выход которого соединен с входом разрешения режима счета второго счетчика. Вход третьего инвертора соединен с выходом младшего разряда первого счетчика. Вход четвертого инвертора соединен с выходом младшего разряда второго счетчика. Выход третьего инвертора соединен с первым входом первого четырехвходового элемента ИЛИ. Выход четвертого инвертора соединен с первым входом второго четырехвходового элемента ИЛИ. Выходы второго, третьего и четвертого разрядов первого счетчика соединены соответственно с вторым, третьим и четвертым входами первого четырехвходового элемента ИЛИ. Выходы второго, третьего и четвертого разрядов второго счетчика соединены соответственно с вторым, третьим и четвертым входами второго четырехвходового элемента ИЛИ. Выход первого четырехвходового элемента ИЛИ соединен с первым входом третьего элемента И. Выход второго четырехвходового элемента ИЛИ соединен с вторым входом третьего элемента И. Выход третьего элемента И соединен с входом разрешения загрузки второго счетчика. Первая группа входов компаратора A3A2A1A0 соединена с выходами соответствующих разрядов Q3Q2Q1Q0 второго счетчика. Выход А>В цифрового компаратора, образующий выход F формирователя, соединен с третьим входом второго элемента ИЛИ. При настройке формирователя на формирование периодической последовательности с периодом следования, равным одиннадцати периодам тактовых импульсов, длительностью, равной четырем периодам тактовых импульсов и задержкой начала формирования относительно стартового импульса на три периода тактовых импульсов, первый и второй входы параллельной загрузки первого счетчика соединены с уровнем логической единицы, третий и четвертый входы параллельной загрузки первого счетчика соединены с уровнем логического нуля, первый, второй и четвертый входы параллельной загрузки второго счетчика соединены с уровнем логической единицы, третий вход параллельной загрузки второго счетчика соединен с уровнем логического нуля, первый, второй и третий входы второй группы B3B2B1B0 входов компаратора соединены с уровнем логической единицы, четвертый вход второй группы входов компаратора соединен с уровнем логического нуля; управляющие входы компаратора А> и А< соединены с уровнем логического нуля, управляющий вход А= соединен с уровнем логической единицы.

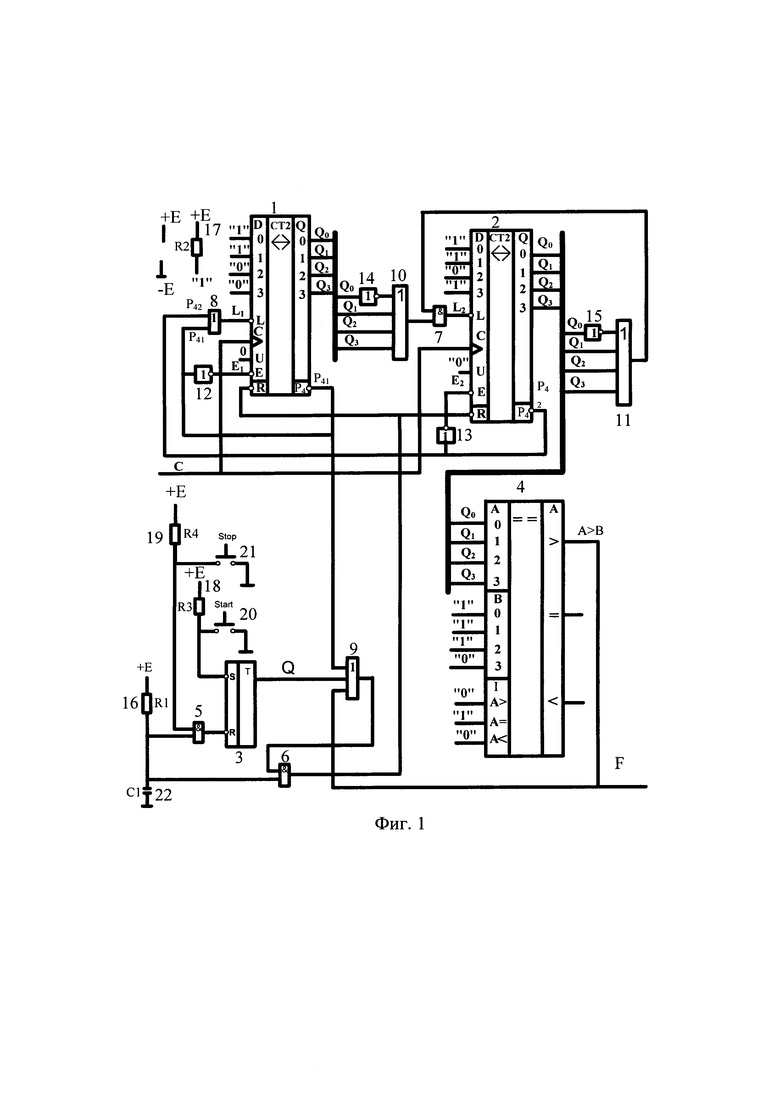

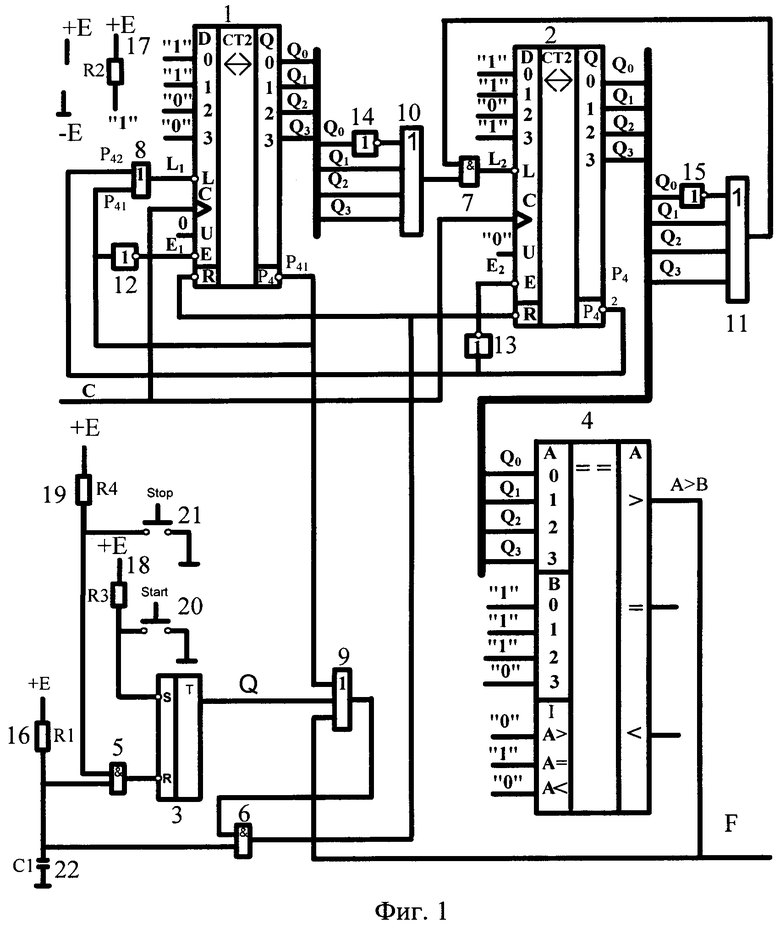

Изобретение поясняется чертежами, где фиг. 1 представлена схема формирователя, фиг. 2 - граф переходов формирователя, фиг. 3 - эпюры, иллюстрирующие работу формирователя.

Формирователь содержит общий источник питания (±Е), два реверсивных двоичных счетчика (1, 2), каждый из которых имеет вход подачи тактовых импульсов (С), вход настройки на режим суммирования/вычитания (U), вход разрешения синхронной параллельной загрузки (L) и входы (D) подачи загружаемых данных D0-D3, вход разрешения режима счета (Е), вход асинхронной установки в нулевое состояние (R), выход переполнения (Р4) триггер (3) с входами асинхронной установки нуля (R) и единицы (S); четырехразрядный цифровой компаратор (4); первый (5), второй (6), и третий (7) двухвходовые элементы И: двухвходовый элемент ИЛИ (8); трехвходовый элемент И (9); первый (10) и второй (11) четырехвходовые элементы ИЛИ; первый (12), второй (13), третий (14) и четвертый (15) инверторы; первый (16), второй (17), третий (18) и четвертый (19) резисторы; первая (20) и вторая кнопки (21); конденсатор С1 (22).

Цепочка, состоящая из последовательно соединенных резистора 16 и конденсатора 22, подключена к источнику питания (±Е); общая точка резистора 16 и конденсатора 22 соединена с первыми входами элементов 5, 6; выход элемента 5 соединен с входом асинхронной установки триггера в нулевое состояние; второй вход элемента 6 соединен с выходом элемента 9, первый вход которого соединен с выходом Q триггера; выход элемента 5 соединен с входами асинхронной установки счетчиков в нулевое состояние. Выход переполнения P41 счетчика 1 соединен с входом инвертора 12 и первым входом элемента 8, второй вход которого соединен с выходом переполнения Р42 счетчика 2. Выход элемента 8 соединен с входом разрешения загрузки L счетчика 1. Тактовые входы (С) счетчиков соединены между собой, образуя вход формирователя (С), на который поступает непрерывная периодическая последовательность импульсов с выхода внешнего кварцевого генератора. Первые выводы резисторов 17-19 соединены с плюсом источника питания (+Е), второй вывод резистора 17 образует задатчик уровня логической единицы ("1"). Второй вывод резистора 18 соединен с входом S и первым контактом кнопки 20 (Start), второй вывод резистора 19 соединен с вторым входом элемента 5 первым контактом кнопки 21 (Stop), Первая группа входов (А) компаратора 4 (A3A2A1A0) соединена с выходами соответствующих разрядов (Q3Q2Q1Q0) счетчика 2. Выход Р42 счетчика 2 соединен с входом инвертора 13. Выход инвертора 13. соединен с входом разрешения режима счета (Е). счетчика. Выход инвертора 14 соединен с первым входом элемента 10. Вход инвертора 14 соединен с выходом Q0 счетчика 1. Выходы Q3Q2Q1 счетчика 1 соединены с остальными входами элемента 10, выход которого соединен с первым входом элемента 7, Второй вход элемента 7 соединен с выходом элемента 11. Вход инвертора 15 соединен с выходом Q0 счетчика 2. Выходы второго, третьего и четвертого разрядов (Q1Q2Q3) счетчика 2 соединены с остальными входами элемента 11. Выход А>В компаратора 4, образующий выход F формирователя, соединен с третьим входом элемента 9. При настройке формирователя на формирование периодической последовательности, временные параметры которых (длительность импульса - tи=4Т, длительность паузы - tи=7T, длительность задержки начала формирования относительно стартового импульса на три периода тактовых импульсов tз=3Т, период следования Ти=11Т определяются значениями настроечных переменных, установленных на входах параллельной загрузки счетчиков и компаратора. Входы D1D0 параллельной загрузки первого счетчика соединены с уровнем логической единицы ("1") (с вторым выводом второго резистора), входы D3D2 с уровнем логического нуля ("0") (с общей точкой - минусом источника питания). Аналогично, первый, второй и четвертый входы (D0D1 D2D3) параллельной загрузки счетчика 2 соединены с уровнем логической единицы ("1"), вход D2 соединен с уровнем логического нуля ("0"). Подобным же образом входы В2 В]В0 компаратора соединены с уровнем логической единицы ("1"), вход В3 компаратора соединен с уровнем логического нуля ("0"), управляющие входы I (А>), I (А<) соединены с уровнем логического нуля ("0"), управляющий вход I (А=) соединен с уровнем логической единицы ("1").

Наличие цепочки, состоящей из соединенных последовательно резистора 16 и конденсатора 22, подключенной к шине питающего напряжения (±Е), при включении источника питания в течение некоторого промежутка времени (определяемого постоянной времени цепи R1C1) формирует уровень логического нуля на входах элементов 5, 6 обеспечивая формирование уровня логического нуля на их выходах, подсоединенных к входам асинхронной установки в нулевое состояние триггера 3 и счетчиков 1, 2. По окончании переходного процесса, связанного с включением источника питания, формируется уровень логической единицы на выходе резисторов 17, 18 и 19, триггер и оба счетчика переходят в нулевое состояние, формируя уровень логического нуля соответственно на выходе триггера и на выходах переполнения счетчиков 1, 2, что ведет к формированию уровня логического нуля на выходе элемента 9, подсоединенного к входу элемента 6, что обеспечивает подтверждение (блокировку) уровня логического нуля на его выходе и по окончанию переходного процесса, связанного с зарядом конденсатора 22, когда напряжение на нем превысит уровень логического нуля, что обеспечивает уровень логического нуля на входах (R) асинхронной установки счетчиков 1, 2 в нулевое состояние. Поскольку режим асинхронной установки счетчиков в нулевое состояние имеет приоритет по отношению ко всем остальным режимам, то до тех пор, пока на входе элемента ИЛИ 9 (а, следовательно, и на его выходе) будет сохраняться уровень логического нуля, нулевое состояние счетчиков будет оставаться неизменным.

При нажатии кнопки 20 (Start) происходит переход триггера 3 в единичное состояние (Q=1), формируя уровень логической единицы на выходе элемента 9, а, следовательно, на входе и выходе элемента 6, что обеспечивает уровень логической единицы на входах R счетчиков, снимая блокировку нулевого состояния счетчиков, и тогда активное значение (уровень логического нуля) на выходе элемента 8 и входе разрешения синхронной параллельной загрузки счетчика 1, подготавливая его к приему информации с входов D3D2D1D0=0011.

При поступлении первого (после окончания переходного процесса, связанного с запуском) тактирующего импульса (С), по его фронту происходит параллельная загрузка, счетчик 1 переходит в состояние Q3Q2Q1Q0=0011. В результате этого перехода на выходе переполнения счетчика 1 и выходе элемента 7 формируется единичное, а на выходе инвертора 12 - нулевое значения, что ведет к запрету параллельной загрузки и разрешению режима счета счетчика 1. Исходное (нулевое) состояние счетчика 2 и нулевое значение сигнала на выходе формирователя осталось неизменным.

При поступлении второго тактового импульса содержимое счетчика 1 становится равным 0010. При поступлении третьего тактового импульса содержимое счетчика 1 становится равным 0001, на выходе инвертора 14 появляется нулевое значение, в результате чего на выходе элемента 10 формируется уровень логического нуля, что ведет к формированию уровня логического нуля на входе элемента 7 (на входе разрешения загрузки счетчика 2).

И тогда при поступлении следующего (четвертого) тактового импульса счетчик 1 переходит в нулевое состояние, а счетчик 2 - в состояние, определяемое значением сигналов на его входах параллельной загрузки (D3D2D1D0=1011), что ведет к формированию единичного значения на выходе формирователя и нулевого значения на выходе инвертора 13. При этом до тех пор, пока содержимое счетчика 2 будет превышать (больше) значения, установленного на входах второй группы компаратора 4 (0111), значение сигнала на выходе формирователя будет оставаться, равным 1. Как только содержимое счетчика 2 станет равным 0111, значение сигнала на выходе формирователя станет равным 0. При поступлении следующих тактовых импульсов содержимое счетчика 2 продолжает уменьшаться, а значение сигнала на выходе будет оставаться равным 0, до тех пор, пока содержимое счетчика 2 не станет равным 0001. Как только счетчик 2 перейдет в состояние 0001 на выходе элементов 11,7, 15 и на входе разрешения загрузки счетчика 2 формируется уровень логического нуля. При поступлении следующего тактового импульса счетчик 2 снова переходит в состояние 1011, формируя единичное значение на выходе. При поступлении следующих тактовых импульсов процессы повторяются.

Таким образом, по окончании переходного процесса, связанного с запуском, при поступлении на вход формирователя периодической последовательности импульсов (с периодом, равным Т) на выходе формирователя генерируется периодическая последовательность импульсов, кратных периоду тактовых импульсов, временные параметры которых (длительность импульса - tи=4Т, длительность паузы - tп=7Т, длительность задержки начала формирования относительно стартового импульса на три периода тактовых импульсов tз=3Т, период следования Ти=ИТ определяются значениями настроечных переменных, установленных на входах параллельной загрузки счетчиков и компаратора 4.

Остановка режима формирования выходной последовательности осуществляется нажатием кнопки 21 (Stop), формируя уровень нуля на входе асинхронной установки (R) триггера 7, что приводит к переходу его в нулевое состояние (Q=0). Момент нажатия кнопки 21 (Stop) асинхронен по отношению к импульсам тактового генератора и к состоянию счетчиков.

Если в момент нажатия кнопки содержимое счетчика 2 меньше или равно 0111, то, то при переходе триггера в нулевое состояние на входах элемента 9 и его выходе будет сформирован уровень логического нуля, обуславливая уровень нуля на входе и выходе элемента 6, что произведет к блокировке нулевого состояния первого счетчика и к переходу второго в нулевое состояние, следовательно, к прекращению режима генерации.

Если в момент нажатия кнопки содержимое счетчика 2 больше 0111, то при переходе триггера в нулевое состояние единичное значение на выходе элемента 9 останется неизменным, поскольку на выходе компаратора 4, соединенного с третьим входом элемента 9, уровень логической единицы. Отсюда следует, что в этом случае в момент нажатия кнопки прекращения генерации не произойдет, обуславливая тем самым предотвращение искажения последнего импульса в формируемой выходной последовательности. При поступлением следующих тактовых импульсов (С) на вход формирователя будет происходить переход второго счетчика в соответствии с алгоритмом до тех пор, пока его содержимое не станет, равным 0111, обуславливая уровень логического нуля на входе и выходе элемента 6, что приведет к переходу счетчика 2 в нулевое состояние, следовательно, к прекращению режима генерации. При следующем нажатии кнопки 20 (Start) процессы повторяются.

Поскольку момент нажатия кнопки 21 (Stop) асинхронен по отношению к импульсам тактового генератора, то длительность задержки начала формирования относительно стартового импульса находится в диапазоне больше 3Т и меньше 4Т.

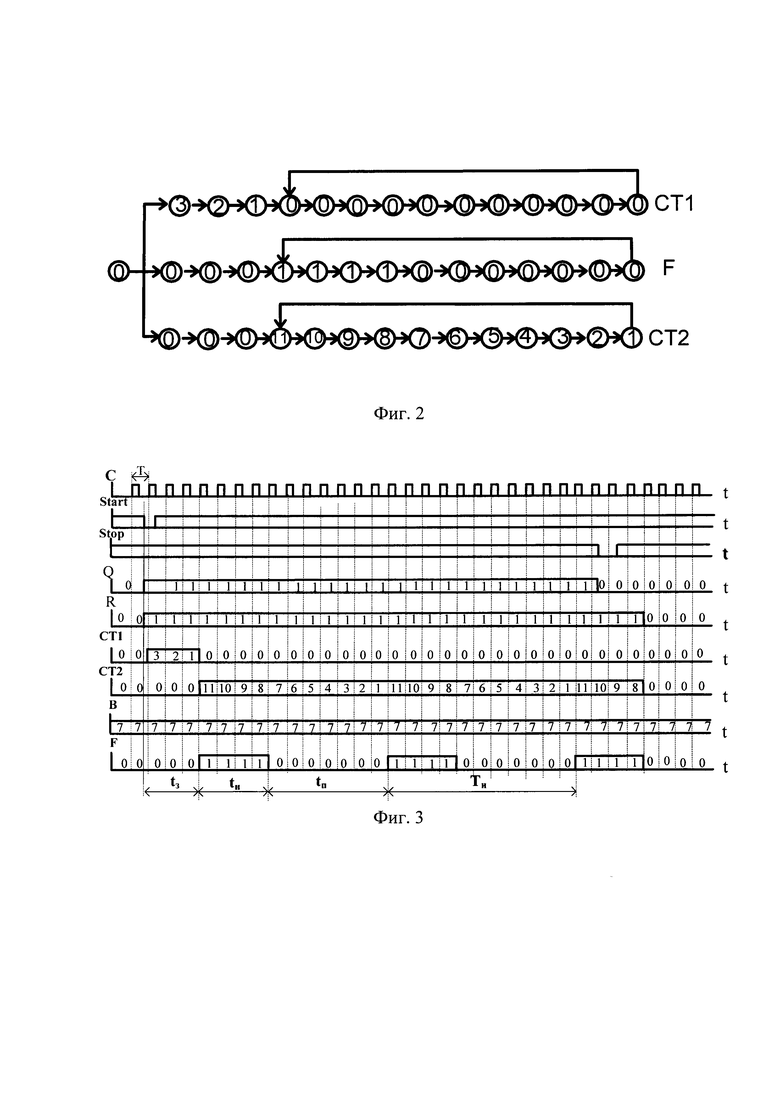

Граф переходов формирователя, состоящий из трех колец с общей вершиной, соответствующей нулевому состоянию счетчиков приведен на фиг. 2.

Независимая настройка формирователя на заданную длительность импульсов и паузы, задержки начала формирования относительно стартового импульса, а также предотвращение возможного укорочения последнего выходного импульса при нажатии кнопки 21 (Stop), расширяет его функциональные возможности и область использования.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Цифровое устройство для управления вентильным преобразователем | 1984 |

|

SU1239806A1 |

| Устройство для регулирования подачи волокна к группе чесальных машин | 1989 |

|

SU1730235A1 |

| МАТРИЧНЫЙ КОММУТАТОР С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ | 2003 |

|

RU2251792C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| Устройство для проверки N счетчиков | 1980 |

|

SU944112A1 |

Изобретение относится к области вычислительной техники. Технический результат заключается в расширении функциональных возможностей формирователя за счет обеспечения возможности менять временные параметры генерируемых импульсов. Технический результат достигается за счет формирователя периодической последовательности импульсов, содержащего общий источник питания; первый и второй реверсивные двоичные счетчики, настроенные на режим вычитания, с входом разрешения синхронной параллельной загрузки и входами подачи настроечных переменных, входом разрешения режима счета и входом асинхронной установки в нулевое состояние, выходами переполнения; резистор; конденсатор; триггер с входом асинхронной установки нуля; первый и второй двухвходовые элементы И; двухвходовый элемент ИЛИ; трехвходовый элемент ИЛИ; инвертор; вход формирователя, на который поступает непрерывная периодическая последовательность импульсов с выхода внешнего кварцевого генератора, при этом введены четырехразрядный цифровой компаратор; задатчик уровня логической единицы; два четырехвходовых элемента ИЛИ; второй, третий и четвертый инверторы; первая и вторая кнопки, работающие на замыкание; второй, третий и четвертый резисторы. 3 ил.

Формирователь периодической последовательности импульсов, содержащий общий источник питания; первый и второй реверсивные двоичные счетчики, настроенные на режим вычитания, с входом разрешения синхронной параллельной загрузки и входами подачи настроечных переменных, входом разрешения режима счета и входом асинхронной установки в нулевое состояние, выходами переполнения; резистор; конденсатор; триггер с входом асинхронной установки нуля; первый и второй двухвходовые элементы И; двухвходовый элемент ИЛИ; трехвходовый элемент ИЛИ; инвертор, при этом последовательно соединенные резистор и конденсатор подключены к общему источнику питания, а их общая точка соединена с первыми входами первого и второго элементов И, выход первого элемента И соединен с входом асинхронной установки триггера в нулевое состояние, второй вход второго элемента И соединен с выходом трехвходового элемента ИЛИ, выход переполнения первого счетчика соединен с входом инвертора, с первым входом двухвходового элемента ИЛИ и с первым входом трехвходового элемента ИЛИ, второй вход трехвходового элемента ИЛИ соединен с выходом триггера, второй вход двухвходового элемента ИЛИ соединен с выходом переполнения второго счетчика, выход второго элемента И соединен с входами асинхронной установки счетчиков в нулевое состояние; выход двухвходового элемента ИЛИ соединен с входом разрешения синхронной параллельной загрузки первого счетчика; выход инвертора соединен с входом разрешения режима счета первого счетчика; тактовые входы первого и второго счетчиков соединены между собой, образуя вход формирователя, на который поступает непрерывная периодическая последовательность импульсов с выхода внешнего кварцевого генератора, отличающийся тем, что введены четырехразрядный цифровой компаратор; задатчик уровня логической единицы; два четырехвходовых элемента ИЛИ; второй, третий и четвертый инверторы, первая и вторая кнопки, работающие на замыкание; второй, третий и четвертый резисторы, первые выводы которых соединены с плюсом источника питания, второй вывод второго резистора образует вывод уровня логической единицы; второй вывод третьего резистора соединен с входом асинхронной установки триггера в единичное состояние и первым контактом первой кнопки; второй вывод четвертого резистора соединен с вторым входом первого элемента И и первым контактом второй кнопки; вторые контакты кнопок соединены с общей точкой источника питания; выход переполнения второго счетчика соединен с входом второго инвертора, выход которого соединен с входом разрешения режима счета второго счетчика; вход третьего инвертора соединен с выходом младшего разряда первого счетчика; вход четвертого инвертора соединен с выходом младшего разряда второго счетчика; выход третьего инвертора соединен с первым входом первого четырехвходового элемента ИЛИ; выход четвертого инвертора соединен с первым входом второго четырехвходового элемента ИЛИ; выходы второго, третьего и четвертого разрядов первого счетчика соединены соответственно с вторым, третьим и четвертым входами первого четырехвходового элемента ИЛИ; выходы второго, третьего и четвертого разрядов второго счетчика соединены соответственно с вторым, третьим и четвертым входами второго четырехвходового элемента ИЛИ; выход первого четырехвходового элемента ИЛИ соединен с первым входом третьего элемента И; выход второго четырехвходового элемента ИЛИ соединен с вторым входом третьего элемента И; выход третьего элемента И соединен с входом разрешения синхронной параллельной загрузки второго счетчика; первая группа входов компаратора А3А2А1А0 соединена с выходами соответствующих разрядов Q3Q2Q1Q0 второго счетчика; выход А>В цифрового компаратора, образующий выход F формирователя, соединен с третьим входом второго элемента ИЛИ; при настройке формирователя на формирование периодической последовательности с периодом следования, равным одиннадцати периодам тактовых импульсов, длительностью, равной четырем периодам тактовых импульсов и задержкой начала формирования относительно стартового импульса на три периода тактовых импульсов, первый и второй входы параллельной загрузки первого счетчика соединены с уровнем логической единицы, третий и четвертый входы параллельной загрузки первого счетчика соединены с уровнем логического нуля, первый, второй и четвертый входы параллельной загрузки второго счетчика соединены с уровнем логической единицы, третий вход параллельной загрузки второго счетчика соединен с уровнем логического нуля, первый, второй и третий входы второй группы B3B2B1B0 входов компаратора соединены с уровнем логической единицы, четвертый вход второй группы входов компаратора соединен с уровнем логического нуля; управляющие входы компаратора А> и А< соединены с уровнем логического нуля, управляющий вход А= соединен с уровнем логической единицы.

| Способ приготовления зубопротезной оттисковой массы | 1938 |

|

SU53542A1 |

| Приспособление для строгания на шепинге поверхности спиральных зубцов у конических шестерен методом обкатай | 1944 |

|

SU65284A1 |

| Станок для изготовления гибких шлангов из металлической ленты | 1940 |

|

SU63194A1 |

| US 6417707 B1, 09.07.2002 | |||

| US 10234845 B2, 19.03.2019 | |||

| US 10180448 B2, 15.01.2019 | |||

| УСТРОЙСТВО ВЫДЕЛЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 2006 |

|

RU2305365C1 |

Авторы

Даты

2020-04-21—Публикация

2019-07-30—Подача