Область техники, к которой относится изобретение

Настоящая заявка относится к области технологий связи и, в частности, к способу и устройству кодирования.

Уровень техники

В системе связи кодирование каналов обычно выполняется для повышения надежности передачи данных и гарантии качества связи. В настоящее время мобильная система связи 5G содержит три основных сценария применения: расширенный мобильный широкополосный (Enhanced Mobile Broad Band, eMBB), сверхнадежная связь с низкой задержкой (ultra-reliable low-latency communications, URLLC) и массивная связь машинного типа (Massive Machine-Type Communications, mMTC). Для передачи данных выдвигаются новые требования и полярный (polar) код является первым способом канального кодирования, который может считаться строго доказавшим, что обладает "достигнутой" производительностью канала и может применяться в системе связи 5G и в будущей системе связи.

Сущность изобретения

Настоящая заявка представляет способ и устройство кодирования.

В соответствии с первым подходом, настоящая заявка обеспечивает способ кодирования, содержащий этапы, на которых:

выполняют на передающем конце, основываясь на полиноме циклической проверки избыточности (cyclic redundancy check, CRC), кодирование с CRC А подлежащих кодированию информационных битов, чтобы получить первую битовую последовательность, где первая битовая последовательность содержит L битов CRC и A информационных битов, причем L и A являются положительными целыми числами, L=11, и полином CRC является одним из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

выполняют полярное кодирование первой битовой последовательности.

Используя такой способ кодирования, могут быть удовлетворены требования FAR, чтобы гарантировать, что связь осуществляется нормально.

В возможной реализации полином CRC реализуется, используя регистр сдвига.

В возможной реализации L битов CRC в первой битовой последовательности располагаются после A подлежащих кодированию информационных битов.

В возможной реализации передающая сторона передает первую полярно кодированных битовую последовательность.

В возможной реализации способ кодирования может быть реализован, используя аппаратные средства, например, используя какую-либо схему или одну или более интегральных схем. Способ кодирования альтернативно может быть реализован, используя программное обеспечение. Например, один или более процессоров выполняют способ кодирования, считывая команду, хранящуюся в памяти. Один или более процессоров могут быть интегрированы в микросхему или могут быть распределены по множеству микросхем. Способ кодирования альтернативно может быть частично реализован, используя аппаратные средства, и частично реализован, используя программное обеспечение. Например, процессор выполняет этап, на котором "выполняют, основываясь на полиноме циклической проверки избыточности (cyclic redundancy check, CRC), кодирование с CRC A подлежащих кодированию информационных битов, чтобы получить первую битовую последовательность", считывая команду, хранящуюся в памяти, и этап, на котором "выполняют полярное кодирование первой битовой последовательности", реализуется, используя логическую схему или ускоритель. Конечно, при конкретной реализации специалисты в данной области техники могут альтернативно использовать сочетание описанных выше способов.

В возможной реализации передающей стороной является базовая станция или терминал.

В соответствии со вторым подходом, настоящая заявка представляет устройство кодирования, содержащее:

первый модуль кодирования, выполненный с возможностью осуществления, основываясь на полиноме циклической проверки избыточности (CRC), кодирования с CRC A подлежащих кодированию информационных битов, чтобы получить первую битовую последовательность, где первая битовая последовательность содержит L битов CRC и A информационных битов, причем L и A - положительные целые числа, L=11, и полином CRC является одним из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

второй модуль кодирования, выполненный с возможностью осуществления полярного кодирования первой битовой последовательности.

В возможной реализации полином CRC реализуется, используя регистр сдвига.

В возможной реализации L битов CRC в первой битовой последовательности располагаются после A подлежащих кодированию информационных битов.

В возможной реализации устройство дополнительно содержит передающий модуль, выполненный с возможностью передачи первой полярно кодированной битовой последовательности.

В возможной реализации устройство является базовой станцией или терминалом.

В соответствии с третьим подходом, настоящая заявка представляет устройство кодирования, содержащее процессор. Процессор выполнен с возможностью:

осуществления, основываясь на полиноме циклической проверки избыточности (CRC), кодирования с CRC A подлежащих кодированию информационных битов, чтобы получить первую битовую последовательность, где первая битовая последовательность содержит L битов CRC и A информационных битов, причем, L и A - положительные целые числа, L=11 и полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

выполнения полярного кодирования первой битовой последовательности.

В возможной реализации устройство кодирования дополнительно содержит память и память выполнена с возможностью хранения программных команд.

В возможной реализации полином CRC реализуется, используя регистр сдвига.

В возможной реализации L битов CRC в первой битовой последовательности располагаются после A подлежащих кодированию информационных битов.

В возможной реализации устройство является базовой станцией или терминалом.

Память может находиться внутри процессора или снаружи процессора. Процессор может быть интегрирован в терминал или в базовую станцию.

Процессор может быть схемой, одной или более интегральными схемами или одним или более специализированными чипами. Альтернативно, процессор может быть универсальным чипом и, когда программные команды, используемые для реализации способа кодирования, загружаются в процессор, вышеупомянутая функция кодирования может быть реализована. Альтернативно, процессор может быть сочетанием одной или более схем, интегральной схемой, специализированным чипом и универсальным чипом.

В соответствии с четвертым подходом, настоящая заявка представляет устройство кодирования, содержащее:

входной интерфейс, выполненный с возможностью получения подлежащей кодированию битовой последовательности;

логическую схему, выполненную с возможностью реализации способа согласно первому подходу или его возможным реализациям, основываясь на полученной подлежащей кодированию битовой последовательности, чтобы получить кодированные биты;

выходной интерфейс, выполненный с возможностью вывода кодированных битов.

В возможной реализации устройство является базовой станцией или терминалом.

В соответствии с пятым подходом, настоящая заявка представляет устройство связи, содержащее устройство кодирования, представленное в третьем подходе, и возможные реализации третьего подхода и приемопередатчик, где

приемопередатчик выполнен с возможностью передачи битов, кодированных устройством кодирования.

В возможной реализации устройство связи является базовой станцией или терминалом.

В соответствии с шестым подходом, настоящая заявка представляет считываемый носитель запоминающего устройства содержащий компьютерную программу. Компьютерная программа используется для реализации способа кодирования, представленного при первом подходе или при возможной реализации первого подхода.

В соответствии с седьмым подходом, настоящая заявка представляет программный продукт. Компьютерная программа хранится на считываемом носителе запоминающего устройства. По меньшей мере один процессор устройства кодирования может считывать компьютерную программу со считываемого носителя запоминающего устройства, и по меньшей мере один процессор исполняет компьютерную программу, так чтобы устройство кодирования выполняло способ кодирования, представленный при первом подходе, и возможные реализации первого подхода.

После того, как полином CRC, представленный в этой заявке, использован, требования FAR к системе могут быть удовлетворены, чтобы гарантировать, что связь нормально осуществляется.

Краткое описание чертежей

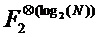

Фиг. 1(a) и 1(b) - архитектура системы связи, применяемая к варианту осуществления настоящей заявки;

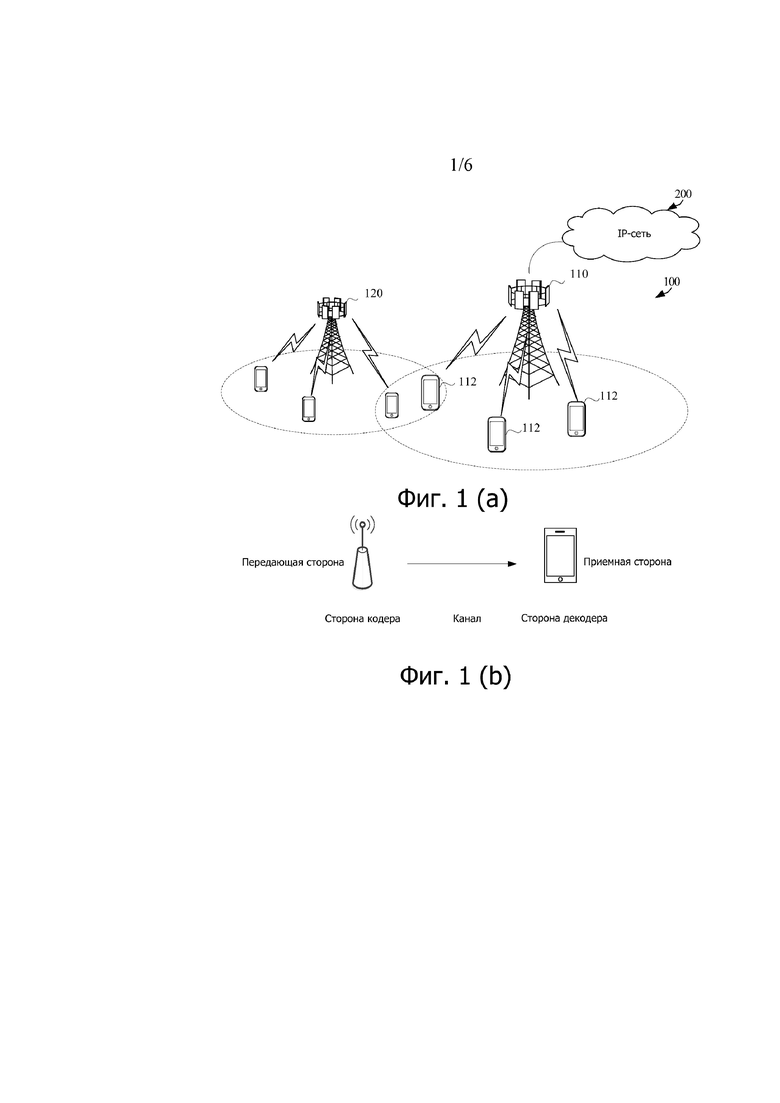

фиг. 2 - блок-схема последовательности выполнения операций системы связи;

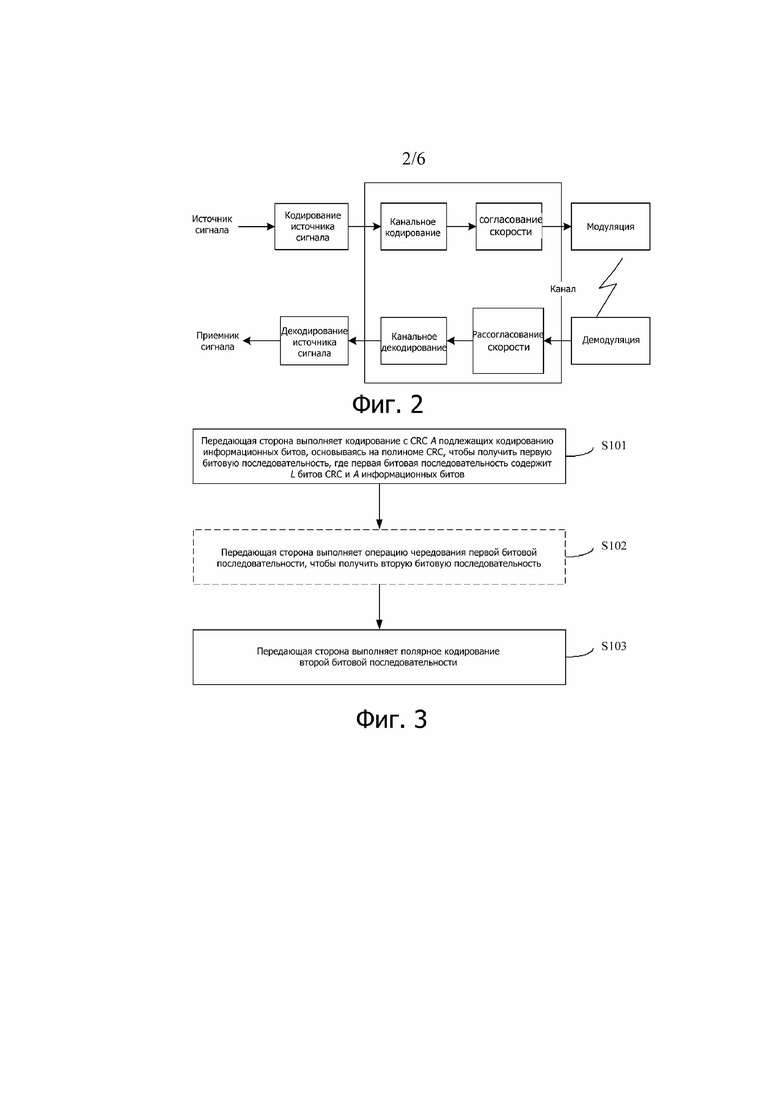

фиг. 3 - блок-схема последовательности выполнения операций способа кодирования, соответствующего настоящей заявке;

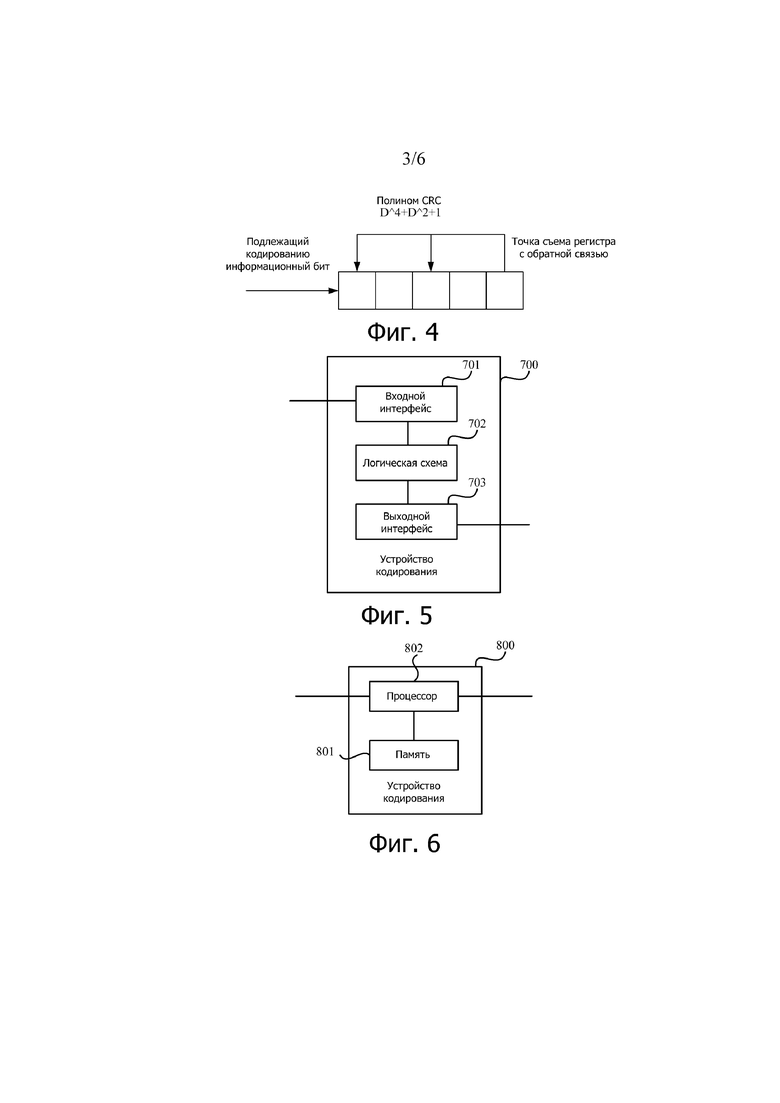

фиг. 4 - диаграмма способа кодирования с CRC;

фиг. 5 - первая структурная схема устройства кодирования, соответствующего варианту осуществления настоящей заявки;

фиг. 6 - вторая структурная схема устройства кодирования, соответствующего варианту осуществления настоящей заявки;

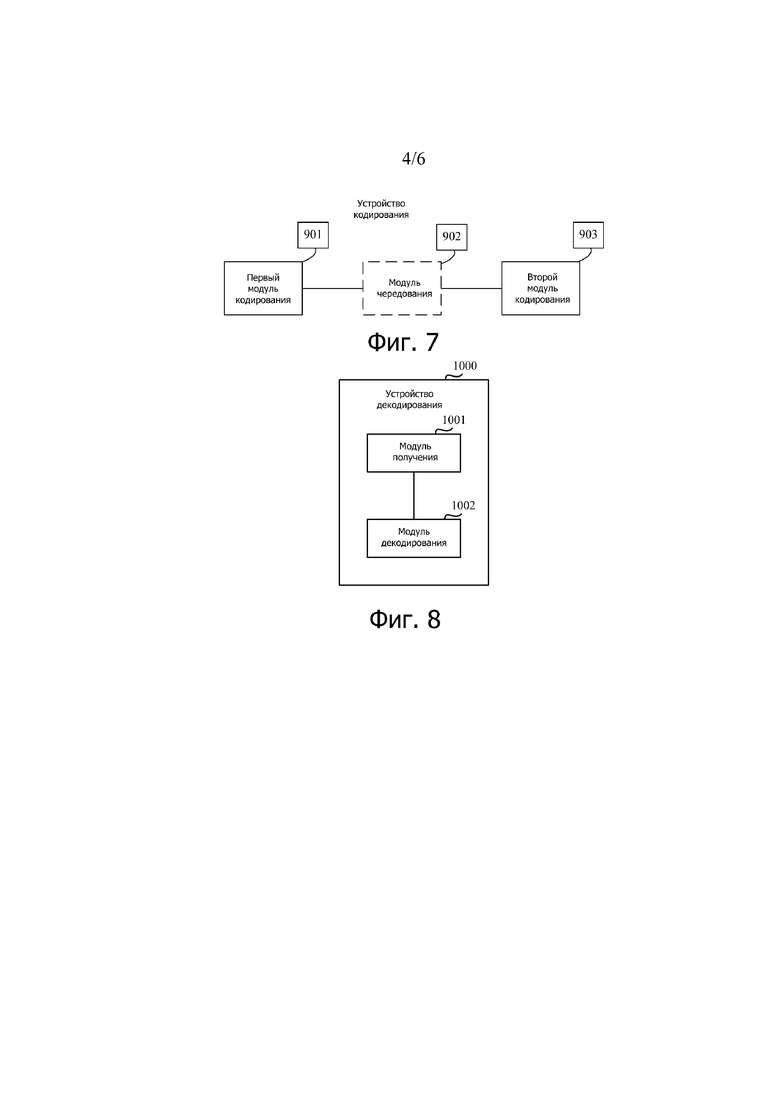

фиг. 7 - третья структурная схема устройства кодирования, соответствующего варианту осуществления настоящей заявки;

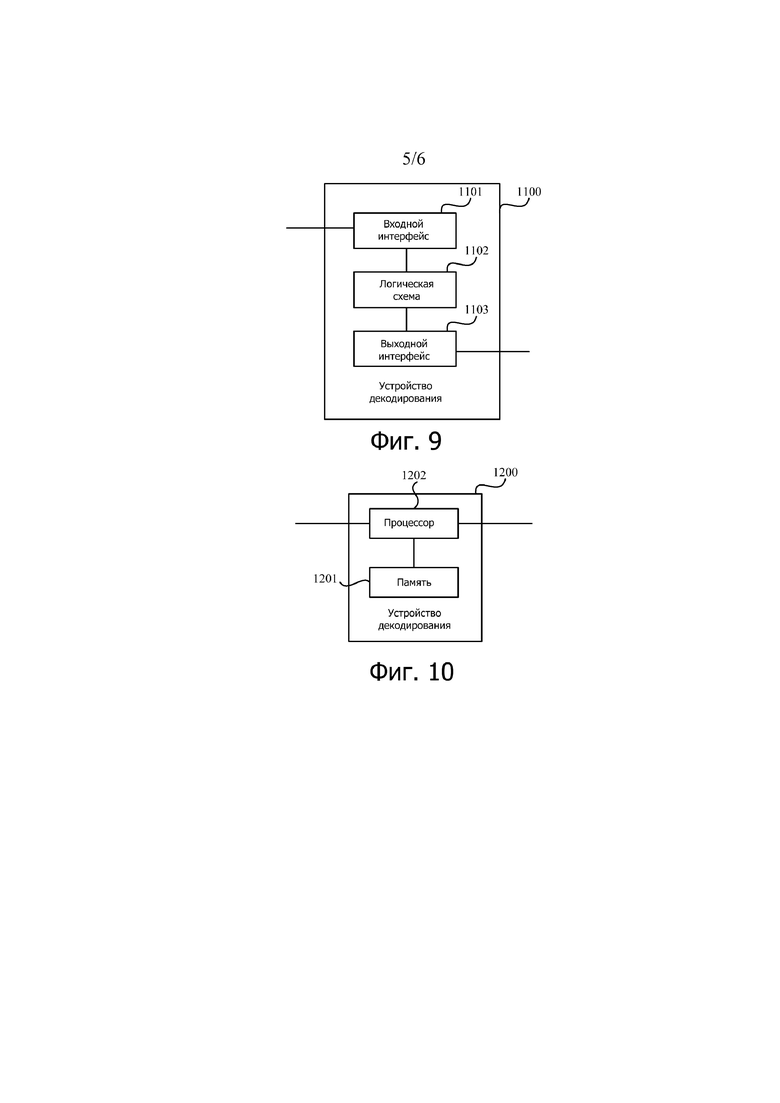

фиг. 8 - первая структурная схема устройства декодирования, соответствующего варианту осуществления настоящей заявки;

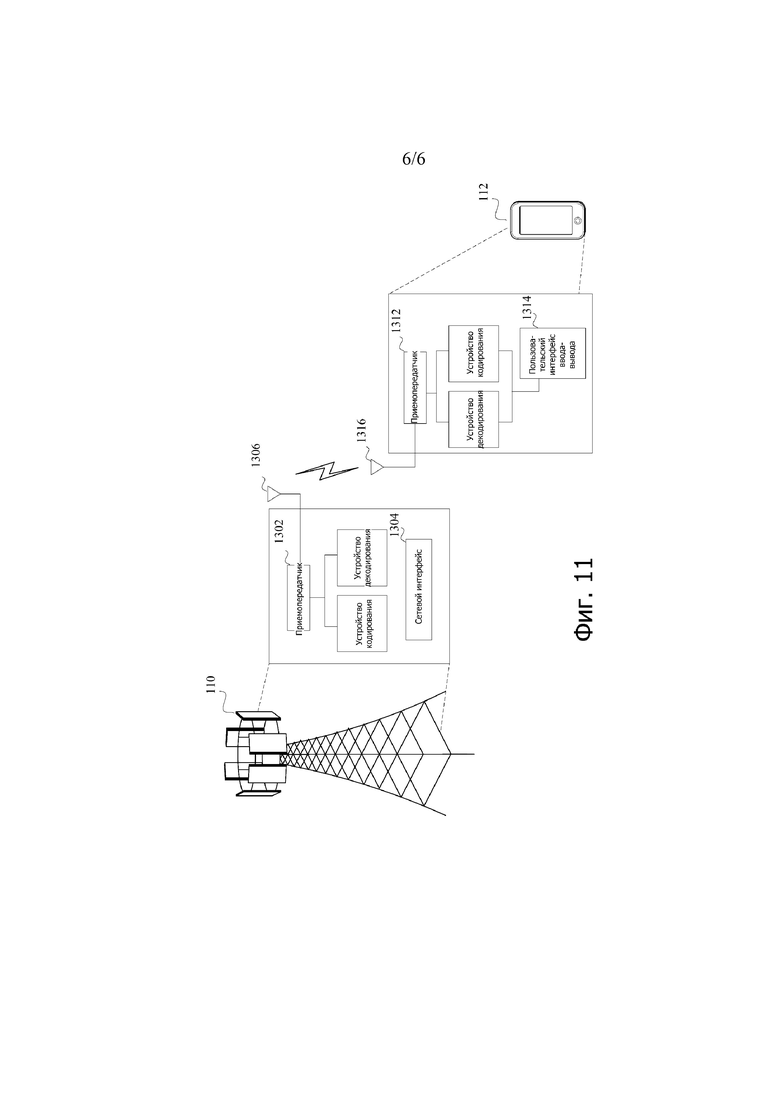

фиг. 9 - вторая структурная схема устройства декодирования, соответствующего варианту осуществления настоящей заявки;

фиг. 10 - третья структурная схема устройства декодирования, соответствующего варианту осуществления настоящей заявки; и

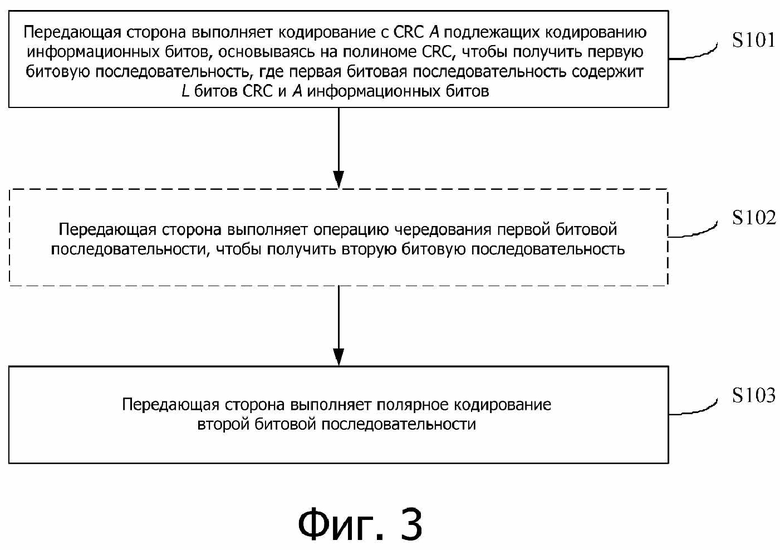

фиг. 11 - структурная схема сетевого устройства и терминала, соответствующих варианту осуществления настоящей заявки.

Описание вариантов осуществления

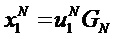

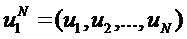

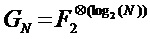

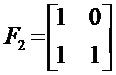

Полярный код является линейным блочным кодом. Матрицей генератора полярных кодов является GN. Процессом кодирования полярного кода является

Чтобы дополнительно улучшить характеристики кодирования системы, выходной код, имеющий возможность проверки, например, код с циклической проверкой избыточности (на английском: Cyclic Redundancy Check, CRC), может объединяться с полярным кодом. когда используется такой способ декодирования, как список последовательной отмены (Serial Cancellation List), выбор обычно производится на путях остающихся, основываясь на циклической проверке избыточности после окончания кодирования, с тем, чтобы улучшить характеристики канального кодирования системы. Когда для канала управления используется полярный код, в добавление к коэффициенту блочных ошибок (block error rate, BLER), который является нормотехническим индикатором, дополнительно для удовлетворения требований необходим индикатор коэффициента ложных тревог (false alarm rate, сокращённо, FAR). Например, если количество битов CRC равно L, используется такой способ декодирования, как декодирование списка последовательной отмены, циклическая проверка кодом избыточности используется после окончания декодирования, и проверяются T путей из остающихся путей, обычно требуется, чтобы FAR был меньше, чем (2^(-L+log2(T))). Следует заметить, что выбор для значения T не зависит от полинома и длины проверки циклическим кодом избыточности, а зависит от сложности реализации декодирования, характеристик декодирования и т.п. Следовательно, необходимо рассмотреть, как находить соответствующий способ объединения кода проверки с CRC и полярного кода, соответствующего требованиям FAR. Настоящая заявка делает упор на определение соответствующего полинома CRC, основанного на значении L, так чтобы удовлетворить системному требованию и гарантировать, что связь нормально осуществляется.

Варианты осуществления настоящей заявки могут применяться к системе беспроводной связи. Следует заметить, что система беспроводной связи, упомянутая в вариантах осуществления настоящей заявки, содержит, но не ограничиваясь только этим, систему долгосрочной эволюции (Long Term Evolution, LTE) и три основных сценария применения системы мобильной связи следующего поколения 5G: улучшенная мобильная широкополосная связь (Enhanced Mobile Broad Band, eMBB), URLLC и массивная связь машинного типа (Massive Machine-Type Communications, mMTC). Альтернативно, система беспроводной связи может быть системой связи типа "устройство-устройство" (Device to Device, D2D), другой системой связи, будущей системой связи и т. п.

Устройство связи, связанное с настоящей заявкой, может быть выполнено с возможностью осуществления в виде устройства связи и устройство связи, главным образом, содержит сетевое устройство или оконечное устройство. Если передающей стороной в этой заявке является сетевое устройство, то приемной стороной является оконечное устройство; или, если передающей стороной в этой заявке является оконечное устройство, то приемной стороной является сетевое устройство.

В варианте осуществления настоящей заявки, как показано на фиг. 1(a), система 100 связи содержит сетевое устройство 110 и терминал 112. Когда сеть 100 беспроводной связи содержит базовую сеть, сетевое устройство 110 может дополнительно соединяться с базовой сетью. Сетевое устройство 110 может дополнительно быть связано с IP-сетью 200, такой как Интернет (Internet), частная IP-сеть или другая сеть передачи данных. Сетевое устройство предоставляет услуги для терминала внутри зоны покрытия. Например, обращаясь к фиг. 1(a), сетевое устройство 110 предоставляет беспроводной доступ для одного или более терминалов внутри зоны покрытия сетевого устройства 110. Кроме того, внутри зоны покрытия сетевых устройств, таких как сетевое устройство 110 и сетевое устройство 120, может существовать область перекрытия. Сетевые устройства могут дополнительно осуществлять связь друг с другом. Например, сетевое устройство 110 может осуществлять связь с сетевым устройством 120.

Когда сетевое устройство 110 или терминал 112 передает информацию или данные, может использоваться способ кодирования, описанный в вариантах осуществления настоящей заявки. Поэтому для удобства описания в этом варианте осуществления настоящей заявки система 100 связи упрощена до системы, которая содержит передающую сторону 101 и приемную сторону 102, как показано на фиг. 1(b). Передающая сторона 101 может быть сетевым устройством 110, а приемная сторона 102 является терминалом 112; или передающая сторона 101 является терминалом 112, а приемная сторона 102 является сетевым устройством 110. Сетевое устройство 110 может быть устройством, выполненным с возможностью осуществления связи с оконечным устройством. Например, сетевым устройством 110 может быть усовершенствованным NodeB (Evolved Node В, eNB или eNodeB) в системе LTE, устройство на сетевой стороне в сети 5G, устройство на сетевой стороне, осуществляющее связь с терминалом в другой сети, или устройство на сетевой стороне в будущей сети. Альтернативно, сетевое устройство может быть релейной станцией, точкой доступа, бортовым устройством и т.п. В системе связи типа "устройство-устройство" (Device to Device, D2D), сетевое устройство может быть терминалом, играющим роль базовой станции. Терминал может содержать различные переносные устройства, бортовые устройства, носимые устройства или вычислительные устройства, имеющие функцию беспроводной связи, или другое процессорное устройство, соединенное с беспроводным модемом, и различные формы оборудования пользователя (user equipment, UE), мобильных станций (mobile station, MS) и т.п.

Процесс кодирования, связанный с настоящей заявкой, примерно представляется следующим образом: выполняют CRC-проверку для информации, которая должна кодироваться; при необходимости, выполняют такую операцию, как чередование проверенной с помощью CRC битовой последовательности; и затем выполняют полярное кодирование. Кроме того, для кодированных битов, полученных после полярного кодирования, дополнительно может выполняться один или более, не ограничиваясь только этим, из таких процессов, как согласование скорости, модуляция, цифро-аналоговое преобразование и преобразование частоты, основываясь на целевой длине М кода.

На фиг. 2 представлена блок-схема последовательности выполнения операций системы связи. Как показано на фиг. 2, на передающей стороне исходный сигнал последовательно подвергается кодированию исходного сигнала, канальному кодированию, согласованию скорости (необязательный этап), модуляции и затем передаче. На приемной стороне исходный сигнал последовательно подвергается демодуляции, рассогласованию скорости (необязательный этап), канальному декодированию и декодированию исходного сигнала и выводится к приемнику сигнала. Варианты осуществления настоящей заявки связаны, главным образом, с кодированием канала и декодированием канала (кратко упоминаемые как кодирование и декодирование канала), и описываются ниже, используя конкретные примеры. Полярный код, связанный с CRC-проверкой, может использоваться для кодирования и декодирования канала в вариантах осуществления настоящей заявки.

Настоящая заявка обеспечивает способ и устройство кодирования для удовлетворения требования FAR. Способ и устройство, связанные с настоящей заявкой, применимы как к каналу управления, так и к каналу передачи данных, и могут применяться к восходящему каналу и к нисходящему каналу. Способ и устройство кодирования, представленные в настоящей заявке, ниже описываются подробно со ссылкой на сопроводительные чертежи.

На фиг. 3 представлена блок-схема последовательности осуществления операций варианта осуществления способа кодирования в соответствии с настоящей заявкой. Как показано на фиг. 3, это вариант осуществления выполняется на передающей стороне и способ этого варианта осуществления может содержать нижеследующие этапы.

S101. Передающая сторона выполняет кодирование с CRC А подлежащих кодированию информационных битов, основываясь на CRC-полиноме, чтобы получить первую битовую последовательность, где первая битовая последовательность содержит L битов CRC и А информационных битов, причем L и A являются положительными целыми числами. L также обычно упоминается как длина CRC.

С учетом требования FAR, когда L=11, полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1.

Конкретный процесс выполнения кодирования CRC, основанный на выбранном полиноме, совпадает с текущим обычным кодированием с CRC.

А именно, после приема А подлежащих кодированию информационных битов передающая сторона добавляет L битов CRC, основываясь на полиноме CRC, для получения первой битовой последовательности.

А подлежащих кодированию информационных битов могут быть получены путем сортировки подлежащих кодированию информационных битов в порядке возрастания или убывания или могут быть получены путем выполнения обработки информационных битов. Это здесь не ограничивается.

Реализация кодирования с CRC имеет форму регистра сдвига. Например, на фиг. 4 показан наиболее часто используемый способ реализации кодирования с CRC в форме регистра сдвига (кратко называемого регистром). Точка съема регистра с обратной связью определяется полиномом CRC D^4+D^2+1 и содержание регистра инициализируется с предварительно установленного значения. Во время кодирования подлежащие кодированию информационные биты сдвигаются в регистр поразрядно и битовая операция "исключающее ИЛИ" выполняется в точке съема регистра с обратной связью и в соответствующем состоянии регистра, так чтобы состояние регистра изменилось. После того, как все подлежащие кодированию биты сдвинуты в регистр, биты 0, количество которых равно количеству битов длины CRC, смещаются в регистр, затем состояние регистра считывается и состояние регистра используется в качестве бита CRC и используется в качестве кодового слова кодирования с CRC. L битов CRC в первой битовой последовательности могут располагаться после А подлежащих кодированию информационных битов, могут располагаться перед А подлежащих кодированию информационных битов или могут быть располагаются в любом месте, которое согласуют приемная сторона и передающая сторона.

S102. Передающая сторона чередует первую последовательность битов, чтобы получить вторую битовую последовательность.

На этапе чередования в первой битовой последовательности могут чередоваться некоторые биты или в первой битовой последовательности могут чередоваться все биты. Следует заметить, что этот этап является необязательным: этот этап необходим, только когда должно быть скорректировано местоположение информационного бита и/или контрольного бита CRC; а если местоположение информационного бита и/или контрольного бита CRC не должно корректироваться, этот этап в процессе реального кодирования может быть пропущен и в этом случае вторая битовая последовательность на этапе S103 является первой битовой последовательностью. Конкретная схема чередования не является предметом этой заявки и подробности не описываются.

S103. Передающая сторона выполняет полярное кодирование второй битовой последовательности для получения третьей битовой последовательности. Когда этап S102 пропускается, то на этом этапе передающая сторона выполняет полярное кодирование первой битовой последовательности для получения третьей битовой последовательности.

Существующий способ полярного кодирования может использоваться в качестве способа кодирования для выполнения передающей стороной полярного кодирования второй битовой последовательности. Подробности здесь не описываются.

S104 (на чертеже не показан). Передающая сторона выполняет некоторые или все этапы, в том числе, но не ограничиваясь только этим, согласование скорости, модуляцию, аналого-цифровое преобразование и преобразование частоты для третьей битовой последовательности и затем передает третью битовую последовательность.

Следует заметить, что этап согласования скорости на этапе S104 является необязательным. Если длина кода при кодировании совпадает с длиной кода для целевого кода, согласование скорости не требуется. Это вариант осуществления настоящего изобретения не придает особого значения этапу S104. Поэтому подробности здесь не описываются. Например, в возможной реализации специалисты в данной области техники могут обратиться к практике, имеющей место на предшествующем уровне техники.

Основываясь на способе кодирования, представленном в этом варианте осуществления, передающая сторона выполняет кодирование CRC А подлежащих кодированию информационных битов на основе CRC-полинома, представленного в настоящей заявке, чтобы получить первую битовую последовательность, а затем выполняет чередование (при необходимости) и полярное кодирование первой битовой последовательности. Поэтому после того, как CRC объединяется, используемый способ полярного кодирования может удовлетворять требованиям FAR.

Следует заметить, что после приема подлежащих декодированию информационных битов, приемная сторона (сторона декодера) также должен выполнить проверку CRC на основе того же самого полинома CRC. Подробности здесь не описываются.

В этом варианте осуществления настоящей заявки, операция декодирования на стороне декодера является примерно следующей: принимают подлежащую декодированию последовательность и выполняют полярное декодирование полученной подлежащей декодированию последовательности, основываясь на полиноме CRC.

Основанный на той же самой идее изобретения, что и способ кодирования, показанный на фиг. 3, вариант осуществления настоящей заявки, показанный на фиг. 5, дополнительно обеспечивает устройство 700. Устройство 700 кодирования 700 выполнено с возможностью осуществления способа кодирования, показанного на фиг. 3. Некоторые или все этапы способа кодирования, показанного на фиг. 3, могут выполняться, используя аппаратные средства или программное обеспечение. Когда некоторые или все этапы способа кодирования, показанного на фиг. 3, выполняются, используя аппаратные средства, устройство 700 кодирования содержит: входной интерфейс 701, выполненный с возможностью получения подлежащей кодированию битовой последовательности; логическую схему 702, выполненную с возможностью осуществления способа кодирования, показанного на фиг. 3, для которого подробности можно получить, обратившись к описанию предшествующего варианта осуществления способа, и подробности которого повторно здесь не приводятся; и выходной интерфейс 703, выполненный с возможностью вывода кодированной битовой последовательности.

Как вариант, во время конкретной реализации, устройство кодирования 700 может быть чипом или интегральной схемой.

Как вариант, когда с помощью программного обеспечения выполняются некоторые или все этапы способа кодирования предыдущего варианта осуществления, как показано на фиг. 6, устройство 800 кодирования содержит: память 801, выполненную с возможностью хранения программы; и процессор 802, выполненный с возможностью исполнения программы, хранящейся в памяти 801. Когда программа исполняется, устройство 800 кодирования выполняет способ кодирования, представленный в варианте осуществления, показанном на фиг. 3.

Как вариант, память 801 может быть физически независимым блоком или может быть интегрирована вместе с процессором 802.

Как вариант, когда некоторые или все этапы способа кодирования варианта осуществления, показанного на фиг. 3, выполняются при помощи программного обеспечения, устройство 800 кодирования может содержать только процессор 802. Память 801, выполненная с возможностью хранения программы, располагается вне устройства 800 кодирования и процессор 802 соединяется с памятью 801 при помощи схемы или проводника и конфигурируется для считывания и исполнения программы, хранящейся в памяти 801.

Процессор 802 может быть центральным процессором (central processing unit, CPU), сетевым процессором (network processor, NP) или сочетанием CPU и NP.

Процессор 802 может дополнительно содержать аппаратный чип. Аппаратный чип может быть специализированной прикладной интегральной схемой (application-specific integrated circuit, ASIC), программируемым логическим устройством (programmable logic device, PLD) или их сочетанием. PLD может быть сложным программируемым логическим устройством (complex programmable logic device, CPLD), программируемой логической интегральной схемой (field-programmable gate array, FPGA), типовой матричной логикой (generic array logic, GAL) или любым их сочетанием.

Память 801 может содержать энергозависимую память (volatile memory), например, оперативную память (random-access memory, RAM). Альтернативно, память 801 может содержать энергонезависимую память (non-volatile memory), например, флэш-память (flash memory), жесткий диск (hard disk drive, HDD) или твердотельный диск (solid-state drive, SSD). Альтернативно, память 801 может содержать сочетание перечисленных выше типов памятей.

Основанный на той же самой идее изобретения, что и способ кодирования, показанный на фиг. 3, вариант осуществления настоящей заявки, показанный на фиг. 7, дополнительно представляет структурную схему варианта осуществления устройства кодирования. Устройство может содержать: первый модуль 901 кодирования, модуль 902 чередования и второй модуль 903 кодирования. Первый модуль 901 кодирования выполнен с возможностью осуществления на основе полинома CRC кодирования с циклической проверкой избыточности (CRC) А подлежащих кодированию информационных битов, чтобы получить первую битовую последовательность, где первая битовая последовательность содержит L CRC-битов и А информационных битов, причем L и A являются положительными целыми числами, L=11 и CRC-полином является одним из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1.

Обычно, полином CRC, используемый для кодирования с CRC, реализуется, используя регистр сдвига. L битов CRC в первой битовой последовательности могут располагаться после А подлежащих кодированию информационных битов, могут располагаться перед А подлежащих кодированию информационных битов или могут располагаться в любом месте, согласованном между приемной стороной и передающей стороной. Модуль 902 чередования является необязательным модулем и выполнен с возможностью осуществления операции чередования для первой битовой последовательности, чтобы получить вторую битовую последовательность. Этот модуль необходим, только когда местоположение информационного бита и/или контрольного бита CRC должно корректироваться таким способом, как при распределенной CRC. Если местоположение информационного бита и/или контрольного бита CRC не должно корректироваться, этот модуль может отсутствовать в фактическом процессе кодирования и в этом случае вторая битовая последовательность является первой битовой последовательностью. Второй модуль 903 кодирования выполнен с возможностью осуществления полярного кодирования второй битовой последовательности и, когда модуль 902 чередования отсутствует, второй модуль 903 кодирования конфигурируется для выполнения полярного кодирования первой битовой последовательности.

Следует заметить, что, такие модули, как модуль согласования скорости, модулирующий модуль и передающий модуль, на фиг. 7 не показаны. Передающий модуль выполнен с возможностью передачи кодированной последовательности и, конечно, прежде чем кодированная последовательность будет передана, необходимо дополнительно выполнить такие операции, как согласование скорости (при необходимости) и модуляция.

Основанный на той же самой идее изобретения, что и способ декодирования, предоставленный в предшествующем варианте осуществления, как показано на фиг. 8, вариант осуществления настоящей заявки дополнительно обеспечивает устройство 1000 декодирования. Устройство 1000 декодирования может быть выполнено с возможностью осуществления способа декодирования, представленного в варианте осуществления настоящей заявки, и устройство 1000 декодирования содержит:

модуль 1001 получения, выполненный с возможностью получения битовой последовательности, подлежащей декодированию; и

модуль 1002 декодирования, выполненный с возможностью осуществления операции декодирования битовой последовательности, подлежащей декодированию, в соответствии со способом декодирования, где способ декодирования определяется, основываясь на полиноме CRC и способе полярного кодирования.

Основанный на такой же идее изобретения, как и способ декодирования, представленный в предшествующем варианте осуществления, как показано на фиг. 9, вариант осуществления этой заявки дополнительно представляет устройство 1100 декодирования. Устройство 1100 декодирования выполнено с возможностью осуществления предшествующего способа декодирования. Некоторые или все этапы предшествующего способа декодирования могут быть выполнены при помощи аппаратных средств или при помощи программного обеспечения. Когда некоторые или все этапы предшествующего способа декодирования выполняются при помощи аппаратных средств, устройство 1100 декодирования содержит: входной 1101 интерфейс, выполненный с возможностью получения подлежащей декодированию битовой последовательности; логическую схему 1102, выполненную с возможностью осуществления предшествующего способа декодирования; и выходной интерфейс 1103, выполненным с возможностью вывода декодированной последовательности.

Как вариант, во время конкретной реализации устройство 1100 декодирования может быть чипом или интегральной схемой.

Как вариант, когда некоторые или все этапы способа декодирования предшествующего варианты осуществления выполняются при помощи программного обеспечения, как показано на фиг. 10, устройство 1200 декодирования содержит: память 1201, выполненную с возможностью хранения программы; и процессор 1202, выполненный с возможностью исполнения программы, хранящейся в памяти 1201. При исполнении программы устройство 1200 декодирования выполняет способ декодирования, представленный в предшествующем варианте осуществления.

Как вариант, память 1201 может быть физически независимым блоком или может быть интегрирована с процессором 1202.

Как вариант, когда некоторые или все этапы способа декодирования предшествующего варианта осуществления выполняются при помощи программного обеспечения, устройство 1200 декодирования может содержать только процессор 1202. Память 1201, выполненная с возможностью хранения программы, располагается вне устройства 1200 декодирования и процессор 1202 соединяется с памятью 1201 при помощи схемы или проводника и выполнен с возможностью считывания и исполнения программы, хранящейся в памяти 1201.

Процессор 1202 может быть центральным процессором (central processing unit, CPU), сетевым процессором (network processor, NP) или сочетанием CPU и NP.

Процессор 1202 может дополнительно содержать аппаратный чип. Аппаратный чип может быть специализированной прикладной интегральной схемой (application-specific integrated circuit, ASIC), программируемым логическим устройством (programmable logic device, PLD) или их сочетанием. PLD может быть сложным программируемым логическим устройством (complex programmable logic device, CPLD), программируемой логической интегральной схемой (field-programmable gate array, FPGA), типовой матричной логикой (generic array logic, GAL) или любым их сочетанием.

Память 1201 может содержать энергозависимую память (volatile memory), например, оперативную память (random-access memory, RAM). Альтернативно, память 1201 может содержать энергонезависимую память (non-volatile memory), например, флэш-память (flash memory), жесткий диск (hard disk drive, HDD) или твердотельный диск (solid-state drive, SSD). Альтернативно, память 1201 может содержать сочетание перечисленных выше типов памятей.

Память 1201 может содержать энергозависимую память (энергозависимая память), например, оперативная память (оперативная память, RAM). С другой стороны, память 1201 может содержать энергонезависимую память (энергонезависимая память), например, флэш-память (флэш-память), жесткий диск (жесткий диск, жесткий диск), или твердотельный диск (твердотельный диск, SSD). С другой стороны, память 1201 может содержать комбинацию предшествующих типов памятей.

Вариант осуществления этой заявки приложения дополнительно обеспечивает сетевое устройство. Как показано на фиг. 11, предшествующее устройство кодирования и/или устройство декодирования могут быть установлены в сетевом устройстве 110. В дополнение к предшествующим устройству кодирования и устройству декодирования, сетевое устройство 110 может дополнительно содержать приемопередатчик 1302. Битовая последовательность, кодированная устройством кодирования, подвергается последующим изменениям или обработке и затем передается приемопередатчиком 1302 терминалу 112 или приемопередатчик 1302 дополнительно выполняется с возможностью приема информации или данных от терминала 112. Информация или данные подвергаются последовательности обработки и преобразуются в подлежащую декодированию последовательность, и подлежащая декодированию последовательность обрабатывается устройством декодирования для получения декодированной последовательности. Сетевое устройство 110 может дополнительно содержать сетевой интерфейс 1304, выполненный с возможностью связи с другим сетевым устройством.

Аналогично, вышеупомянутое устройство кодирования и/или устройство декодирования может быть конфигурировано в терминале 112. В дополнение к описанному выше устройству кодирования и/или устройству декодирования, терминал 112 может дополнительно содержать приемопередатчик 1312. Битовая последовательность, кодированная устройством кодирования, подвергается последующим изменениям или обработке (в том числе, но не ограничиваясь только некоторыми или всеми из таких процессов как согласование скорости, модуляция, цифро-аналоговое преобразование и преобразование частоты) и затем передается приемопередатчиком 1312 сетевому устройству 110, или приемопередатчик 1312 дополнительно выполняется с возможностью приема информации или данных от сетевого устройства 110. Информация или данные подвергаются последовательности обработки (в том числе, но не ограничиваясь только некоторыми или всеми из таких процессов как преобразование частоты, аналого-цифровое преобразование, демодуляция и рассогласование скорости) и преобразуются в подлежащую декодированию последовательность, и подлежащая декодированию последовательность обрабатывается устройством декодирования для получения декодированной последовательности. Терминал 112 может дополнительно содержать пользовательский интерфейс 1314 ввода-вывода, выполненный с возможностью приема информации, вводимой пользователем. Информация, которую необходимо передать сетевому устройству 110, нуждается в обработке кодером и затем передаче приемопередатчиком 1312 сетевому устройству 110. После проведения последующей обработки данные, декодированные декодером, могут быть предоставлены пользователю при помощи интерфейса 1314 ввода-вывода.

Вариант осуществления настоящей заявки дополнительно обеспечивает компьютерный носитель для хранения, на котором хранится компьютерная программа. Компьютерная программа используется для выполнения способа кодирования, показанного на фиг. 3, и представленного выше варианта осуществления и способа декодирования, представленных в описанном выше варианте осуществления.

Вариант осуществления этой заявки дополнительно обеспечивает устройство полярного кодирования, содержащее любое из устройств кодирования, показанных на фиг. 5-7, и любое из устройств декодирования, показанных на фиг. 8-10.

Вариант осуществления настоящей заявки дополнительно обеспечивает компьютерный программный продукт, содержащий команды. Когда команды работают на компьютере, компьютер выполняет способ кодирования, показанный на фиг. 3, и способ декодирования, представленном в описанном выше варианте осуществления.

Специалисты в данной области техники должны понимать, что варианты осуществления настоящей заявки могут быть обеспечены как способ, система или компьютерный программный продукт. Поэтому настоящая заявка может использовать форму только вариантов осуществления в виде аппаратных средств, только вариантов обеспечения в виде программного обеспечения или вариантов осуществления, сочетающих программное обеспечение и аппаратные средства. Кроме того, настоящая заявка может использовать форму компьютерного программного продукта, который реализуется на одном или более используемых компьютером носителях (в том числе, но не ограничиваясь только этим, память на дисках, CD-ROM и оптическая память), которые содержат используемую компьютером управляющую программу.

Настоящая заявка описывается со ссылкой на блок-схемы последовательности выполнения операций и/или блок-схемы способа, устройства (системы) и компьютерный программный продукт, соответствующие вариантам осуществлениям настоящей заявки. Следует понимать, что команды компьютерной программы могут использоваться для реализации каждого процесса и/или каждого блока на блок-схемах последовательности выполнения операций и/или на блок-схемах и сочетаний процесса и/или блока на блок-схемах последовательности выполнения операций и/или на блок-схемах. Эти команды компьютерной программы могут предоставляться для универсального компьютера, специализированного компьютера, встроенного процессора или процессора любого другого программируемого устройства обработки данных для формирования машины, так чтобы команды, исполняемые компьютером или процессором любого другого программируемого устройства обработки данных, образовывали устройство для реализации определенной функции в одном или более процессах, представленных на блок-схемах последовательности выполнения операций и/или в одном или более блоках на блок-схемах.

Эти команды компьютерной программы могут быть сохранены в считываемой компьютером памяти, которая может давать команду компьютеру или любому другому программируемому устройству обработки данных работать определенным способом, так чтобы команды, хранящиеся в считываемой компьютером памяти, формировали артефакт, содержащий управляющее устройство. Управляющее устройство реализует определенную функцию в одном или более процессах, представленных на блок-схемах последовательности выполнения операций, и/или в одном или более блоках, представленных на блок-схемах.

Эти команды компьютерной программы могут быть загружены на компьютер или на другое программируемое устройство обработки данных так, чтобы на компьютере или на другом программируемом устройстве выполнялась последовательность операций и этапов, формируя реализуемую компьютером обработку. Поэтому команды, исполняемые на компьютере или на другом программируемом устройстве, обеспечивают этапы реализации определенной функции в одном или более процессах, показанных на блок-схемах последовательности выполнения операций, и/или в одном или более блоках, показанных на блок-схемах.

Хотя здесь были описаны некоторые варианты осуществления настоящей заявки, специалисты в данной области техники, могут вносить в эти варианты осуществления изменения и модификации после того, как изучают основную концепцию изобретения. Поэтому нижеследующие пункты формулы изобретения предназначены истолковываться так, чтобы охватывать предпочтительные варианты осуществления и все изменения и модификации, попадающие в рамки объема защиты настоящей заявки.

Очевидно, что специалисты в данной области техники могут производить различные модификации и изменения в вариантах осуществления настоящей заявки, не отступая от сущности и объема защиты настоящей заявки. Настоящая заявка предназначена охватывать эти модификации и изменения при условии, что они попадают в рамки объема защиты, определенного нижеследующими пунктами формулы изобретения и их эквивалентными технологиями.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ | 2018 |

|

RU2735857C1 |

| CRC-БИТЫ ДЛЯ ОБЪЕДИНЕННОГО ДЕКОДИРОВАНИЯ И ВЕРИФИКАЦИИ УПРАВЛЯЮЩЕЙ ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ ПОЛЯРНЫХ КОДОВ | 2017 |

|

RU2733282C1 |

| СПОСОБЫ И УСТРОЙСТВА ДЛЯ ПЕРЕДАЧИ И ОБРАБОТКИ ДАННЫХ, УСТРОЙСТВО СЕТЕВОЙ СТОРОНЫ И ТЕРМИНАЛ | 2018 |

|

RU2743100C1 |

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО СВЯЗИ | 2019 |

|

RU2782241C1 |

| КОНКАТЕНИРОВАННЫЙ ПОЛЯРНЫЙ КОД С ПЕРЕМЕЖЕНИЕМ | 2017 |

|

RU2755398C2 |

| МНОГОУРОВНЕВЫЙ КОД ЦИКЛИЧЕСКОЙ ПРОВЕРКИ ИЗБЫТОЧНОСТЬЮ В СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 2008 |

|

RU2481702C2 |

| СПОСОБ КОДИРОВАНИЯ И УСТРОЙСТВО КОДИРОВАНИЯ ДЛЯ ПОЛЯРНОГО КОДА | 2018 |

|

RU2782234C2 |

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 2007 |

|

RU2408979C2 |

| МНОГОРЕЖИМНОЕ КАНАЛЬНОЕ КОДИРОВАНИЕ | 2020 |

|

RU2793198C2 |

| СПОСОБ И УСТРОЙСТВО СОГЛАСОВАНИЯ СКОРОСТИ ПОЛЯРНОГО КОДА И УСТРОЙСТВО БЕСПРОВОДНОЙ СВЯЗИ | 2014 |

|

RU2663351C1 |

Изобретение относится к средствам для кодирования и декодирования данных. Технический результат заключается в повышении эффективности кодирования. Выполняют кодирование с CRC A подлежащих кодированию информационных битов, основываясь на полиноме CRC, чтобы получить первую битовую последовательность, где первая битовая последовательность содержит L битов CRC и A информационных битов. Выполняют полярное кодирование первой битовой последовательности. Основываясь на улучшенном полиноме CRC, реализуется кодирование, удовлетворяющее требованиям FAR. При этом полином CRC может быть реализован при помощи регистра сдвига, а L битов CRC в кодированной с CRC битовой последовательности располагаются после А подлежащих кодированию информационных битов. Кроме того, передают посредством устройства кодирования полярно кодированную битовую последовательность, а перед передачей полярно кодированной битовой последовательности устройство кодирования выполняет согласование уровней полярно кодированной битовой последовательности, основываясь на длине целевого кода. 10 н. и 30 з.п. ф-лы, 12 ил.

1. Способ кодирования, содержащий этапы, на которых:

выполняют посредством устройства кодирования, основываясь на полиноме контроля циклическим избыточным кодом (cyclic redunancy check, CRC), кодирование с CRC А подлежащих кодированию информационных битов для получения кодированной с CRC битовой последовательности, где кодированная с CRC битовая последовательность содержит L битов CRC и А подлежащих кодированию информационных битов, причем L и A являются положительными целыми числами, L=11, и полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

выполняют посредством устройства кодирования полярное кодирование кодированной с CRC битовой последовательности для получения полярно кодированной битовой последовательности.

2. Способ по п. 1, в котором полином CRC реализуется при помощи регистра сдвига.

3. Способ по п. 1 или 2, в котором L битов CRC в кодированной с CRC битовой последовательности располагаются после А подлежащих кодированию информационных битов.

4. Способ по любому из пп. 1-3, в котором способ дополнительно содержит этап, на котором:

передают посредством устройства кодирования полярно кодированную битовую последовательность.

5. Способ по п. 4, в котором перед передачей полярно кодированной битовой последовательности устройство кодирования выполняет согласование уровней полярно кодированной битовой последовательности, основываясь на длине целевого кода.

6. Способ по любому из пп. 1-5, в котором устройство кодирования является базовой станцией или терминалом.

7. Устройство кодирования, содержащее:

первый модуль кодирования, выполненный с возможностью осуществления, основываясь на полиноме контроля циклическим избыточным кодом (CRC), кодирования А подлежащих кодированию CRC информационных битов, чтобы получить кодированную с CRC битовую последовательность, в которой кодированная с CRC битовая последовательность содержит L битов CRC и А подлежащих кодированию информационных битов, причем L и A являются положительными целыми числами, L=11, и полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

второй модуль кодирования, выполненный с возможностью осуществления полярного кодирования кодированной с CRC битовой последовательности для получения полярно кодированной битовой последовательности.

8. Устройство по п. 7, в котором устройство дополнительно содержит регистр сдвига и полином CRC реализуется посредством регистра сдвига.

9. Устройство по п. 7 или 8, в котором L битов CRC в кодированной с CRC битовой последовательности располагаются после А подлежащих кодированию информационных битов.

10. Устройство по любому из пп. 7-9, в котором устройство дополнительно содержит передающий модуль, выполненный с возможностью передачи полярно кодированной битовой последовательности.

11. Устройство по п. 10, в котором, прежде чем передать полярно кодированную битовую последовательность, устройство конфигурируется для выполнения согласования уровней полярно кодированной битовой последовательности, основываясь на длине целевого кода.

12. Устройство по любому из пп. 7-11, где устройство является базовой станцией или терминалом.

13. Устройство кодирования, содержащее процессор, в котором процессор выполнен с возможностью:

осуществления, основываясь на полиноме контроля циклическим избыточным кодом (CRC), кодирования с CRC А подлежащих кодированию информационных битов для получения кодированной с CRC битовой последовательности, где кодированная с CRC битовая последовательность содержит L битов CRC и А подлежащих кодированию информационных битов, причем L и A являются положительными целыми числами, L=11, и полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

выполнения полярного кодирования кодированной с CRC битовой последовательности для получения полярно кодированной битовой последовательности.

14. Устройство по п. 13, в котором устройство кодирования дополнительно содержит память и память выполнена с возможностью хранения программных команд.

15. Устройство по п. 13 или 14, в котором полином CRC реализуется, используя регистр сдвига.

16. Устройство по любому из пп. 13-15, в котором L битов CRC кодированной с CRC битовой последовательности располагаются после А подлежащих кодированию информационных битов.

17. Устройство по любому из пп. 13-16, где устройство дополнительно содержит приемопередатчик, выполненный с возможностью передачи полярно кодированной битовой последовательности.

18. Устройство по п. 17, в котором, прежде чем приемопередатчик передает полярно кодированную битовую последовательность, процессор дополнительно конфигурируется для выполнения согласования уровней полярно кодированной битовой последовательности, основываясь на целевой длине кода.

19. Устройство по любому из пп. 13-18, где устройство является базовой станцией или терминалом.

20. Устройство кодирования, содержащее:

входной интерфейс, выполненный с возможностью получения А подлежащих кодированию информационных битов;

логическую схему, выполненную с возможностью осуществления, на основе полинома контроля циклическим избыточным кодом (CRC), кодирования с CRC А подлежащих кодированию информационных битов для получения кодированной с CRC битовой последовательности, где кодированная с CRC битовая последовательность содержит L битов CRC и А подлежащих кодированию информационных битов, причем L и A являются положительными целыми числами, L=11, и полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

выполнения полярного кодирования кодированной с CRC битовой последовательности для получения полярно кодированной битовой последовательности; и

выходной интерфейс, выполненный с возможностью вывода полярно кодированной битовой последовательности.

21. Устройство по п. 20, в котором полином CRC реализуется, используя регистр сдвига.

22. Устройство по п. 20 или 21, в котором L битов CRC в кодированной с CRC битовой последовательности располагаются после А подлежащих кодированию информационных битов.

24. Считываемый компьютером носитель запоминающего устройства, где носитель запоминающего устройства выполнен с возможностью хранения компьютерной программы и, когда компьютерная программа работает на устройстве связи, выполняется способ по любому из пп. 1-5.

25. Способ декодирования, содержащий этапы, на которых:

принимают посредством устройства декодирования подлежащую декодированию последовательность;

выполняют посредством устройства декодирования полярное декодирование подлежащей декодированию последовательности, основываясь на полиноме проверки циклическим избыточным кодом (CRC), чтобы получить полярно декодированную битовую последовательность, где полярно декодированная битовая последовательность содержит L битов CRC и А информационных битов, причем L и A являются положительными целыми числами, L=11, и полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

выводят посредством устройства декодирования полярно декодированную битовую последовательность.

26. Способ по п. 25, в котором L битов CRC в подлежащей декодированию последовательности располагаются после А информационных битов.

27. Способ по п. 25 или 26, в котором, перед тем как устройство декодирования принимает подлежащую декодированию последовательность, устройство декодирования дополнительно конфигурируется для приема информации или данных от передающей стороны и выполнения рассогласования уровней для информации или данных, передаваемых от передающей стороны, чтобы получить подлежащую декодированию последовательность.

28. Способ по любому из пп. 25-27, в котором устройство декодирования является базовой станцией или терминалом.

29. Устройство декодирования, содержащее:

модуль получения, выполненный с возможностью получения подлежащей декодированию последовательности, где подлежащая декодированию последовательность содержит L битов проверки избыточным циклическим кодом (CRC) и А информационных битов, причем L и A является положительными целыми числами, L=11, и

модуль декодирования, выполненный с возможностью осуществления полярного декодирования, основываясь на полиноме CRC, чтобы получить полярно декодированную битовую последовательность, в которой полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1.

30. Устройство по п. 29, в котором L битов CRC в подлежащей декодированию последовательности располагаются после А информационных битов.

31. Устройство по п. 29 или 30, в котором перед тем, как модуль получения принимает подлежащую декодированию последовательность, модуль получения дополнительно конфигурируется для приема информации или данных от передающей стороны и выполнения рассогласования уровней для информации или данных, получаемой от передающей стороны, чтобы получить подлежащую декодированию последовательность.

32. Устройство по любому из пп. 29-31, где устройство является базовой станцией или терминалом.

33. Устройство декодирования, содержащее процессор, в котором процессор выполнен с возможностью:

получения подлежащей декодированию последовательности, где подлежащая декодированию последовательность содержит L битов проверки циклическим избыточным кодом (CRC) и А информационных битов, L=11; и

выполнения полярного декодирования подлежащей декодированию последовательности, основанной на полиноме CRC, чтобы получить полярно декодированную битовую последовательность, где полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1.

34. Устройство по п. 33, где устройство декодирования дополнительно содержит память и память выполнена с возможностью хранения программных команд.

35. Устройство по п. 33 или 34, в котором L битов CRC в подлежащей декодированию последовательности располагаются после А подлежащих кодированию информационных битов.

36. Устройство по любому из пп. 33-35, в котором, прежде чем процессор принимает подлежащую декодированию битовую последовательность, процессор дополнительно конфигурируется для приема информации или данных от передающей стороны и выполняет рассогласование уровней для информации или данных, поступающих от передающей стороны, для получения подлежащей декодированию последовательности.

37. Устройство по любому из пп. 33-36, где устройство является базовой станцией или терминалом.

38. Устройство декодирования, содержащее:

входной интерфейс, выполненный с возможностью получения подлежащей декодированию последовательности;

логическую схему, выполненную с возможностью осуществления полярного декодирования подлежащей декодированию последовательности, основываясь на полиноме проверки циклическим избыточным кодом (CRC), чтобы получить полярно декодированную битовую последовательность, где полярно декодированная битовая последовательность содержит L битов CRC и А информационных битов, причем L и A являются положительными целыми числами, L=11, и полином CRC является любым из следующих полиномов:

D^11+D^10+D^9+D^5+1;

D^11+D^7+D^6+D^2+1;

D^11+D^10+D^9+D^6+D^4+D^2+1;

D^11+D^10+D^9+D^7+D^5+D+1;

D^11+D^9+D^8+D^6+D^5+D+1;

D^11+D^10+D^9+D^8+D^7+D^5+D^4+D+1;

D^11+D^10+D^3+D+1;

D^11+D^5+D^3+D+1;

D^11+D^10+D^9+D^8+D^6+D^5+D^3+D+1;

D^11+D^10+D^8+D^7+D^6+D^5+D^3+D+1;

D^11+D^9+D^7+D^6+D^5+D^4+D^3+D+1;

D^11+D^10+D^9+D^7+D^6+D^3+D^2+D+1; или

D^11+D^8+D^6+D^5+D^4+D^3+D^2+D+1; и

выходной интерфейс, выполненный с возможностью вывода полярно декодированной битовой последовательности.

39. Устройство по п. 38, в котором L битов CRC в подлежащей декодированию последовательности располагаются после А информационных битов.

40. Считываемый компьютером носитель запоминающего устройства, где носитель запоминающего устройства выполнен с возможностью хранения компьютерной программы и при работе на устройстве связи выполняется способ по любому из пп. 25-27.

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| CN 107026656 A, 08.08.2017 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| CN 107124188 A, 01.09.2017 | |||

| CN 107040262 A, 11.08.2017 | |||

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| СПОСОБ И УСТРОЙСТВО ГЕНЕРИРОВАНИЯ ГИБРИДНОГО ПОЛЯРНОГО КОДА | 2013 |

|

RU2610251C2 |

Авторы

Даты

2020-07-30—Публикация

2018-05-04—Подача