Настоящее изобретение относится к области технологий связи и, в частности, к способу и устройству для кодирования.

Уровень техники

В системе связи для повышения надежности передачи данных и обеспечения качества связи обычно выполняют кодирование канала. В настоящее время 5G системы мобильной связи включает в себя три основных сценариев применения: усовершенствованная мобильная широкополосная связь (Enhanced Mobile Broad Band, eMBB), сверхнадежная связь с низкой задержкой URLLC и массовая связь машинного типа (Massive Machine-Type Communications, mMTC) и для передачи данных предъявлены новые требования, и полярный (polar) код является первым способом кодирования канала, который может быть строго подтвержден, что «была достигнута» пропускную способность канала, и может быть применим к 5G системе связи и перспективным системам связи.

Сущность изобретения

Настоящее приложение обеспечивает способ и устройство для кодирования.

В соответствии с первым аспектом, настоящее изобретение обеспечивает способ кодирования, включающий в себя:

выполнение стороной передачи, на основании полинома циклического избыточного кода (CRC), CRC кодирования А информационных бит, подлежащих кодированию, для получения первой битовой последовательности, где первая битовая последовательность включает в себя L CRC биты и А информационные биты, L и А являются положительными целыми числами, L = 6 и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+1;

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

выполнение полярного кодирования на первой битовой последовательности.

Посредством использования этого способа кодирования, может быть удовлетворено FAR требование, что гарантирует нормальные условия связи.

В возможной реализации CRC полином реализуют с использованием регистра сдвига.

В возможной реализации L CRC биты в первой битовой последовательности расположены после А информационных бит, подлежащих кодированию.

В возможной реализации сторона передачи отправляет первую полярно-кодированную битовую последовательность.

В возможной реализации способ кодирования может быть реализован с использованием аппаратных средств, например, реализован с помощью схемы или одной или нескольких интегральных схем. Способ кодирования может быть альтернативно реализован с помощью программного обеспечения. Так, например, один или несколько процессоров выполняют способ кодирования путем считывания инструкции, хранящейся в памяти. Один или более процессоров могут быть интегрированы в микросхеме или могут быть распределены в виде множества микросхем. Способ кодирования может альтернативно быть частично реализован с помощью аппаратных средств и частично реализован с помощью программного обеспечения. Например, процессор выполняет этап «выполнения, на основании полинома циклического избыточного кода (CRC), CRC кодирования А информационных бит, подлежащих кодированию, для получения первой битовой последовательности» путем считывания инструкции, хранящейся в памяти, и этап «выполнения полярного кодирования первой битовой последовательности» реализуют с использованием логической схемы или акселератора. Конечно, в конкретной реализации специалисты в данной области техники могут альтернативно использовать комбинацию из указанных выше способов.

В возможной реализации сторона передачи представляет собой базовую станцию или оконечное устройство.

В соответствии со вторым аспектом данное изобретение обеспечивает устройство для кодирования, включающее в себя:

первый модуль кодирования, выполненный с возможностью выполнять, на основании полинома циклического избыточного кода (CRC), CRC кодирование А информационных бит, подлежащих кодированию, для получения первой битовой последовательности, где первая последовательность бит включает в себя L CRC биты и A информационные биты, L и A являются положительными целыми числами, L = 6 и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+1;

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

второй модуль кодирования, выполненный с возможностью выполнять полярное кодирование первой битовой последовательности.

В возможной реализации CRC полином реализуют с использованием регистра сдвига.

В возможной реализации L CRC биты в первой битовой последовательности расположены после А информационных бит, подлежащих кодированию.

В возможной реализации устройство дополнительно включает в себя модуль отправки, выполненный с возможностью отправлять первую полярно-кодированную битовую последовательность.

В возможной реализации устройство является базовой станцией или оконечным устройством.

В соответствии с третьим аспектом, настоящее изобретение обеспечивает устройство для кодирования, включающее в себя процессор. Процессор выполнен с возможностью:

выполнять, на основании полинома циклического избыточного кода (CRC), CRC кодирования А информационных бит, подлежащих кодированию, для получения первой битовой последовательности, где первая битовая последовательность включает в себя L CRC биты и А информационные биты, L и А являются положительными целыми числами, L = 6 и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+1;

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

выполнять полярное кодирование первой битовой последовательности.

В возможной реализации устройство для кодирования дополнительно включает в себя память, и память выполнена с возможностью хранить программную инструкцию.

В возможной реализации CRC полином реализуют с использованием регистра сдвига.

В возможной реализации L CRC биты в первой битовой последовательности расположены после А информационных бит, подлежащих кодированию.

В возможной реализации устройство является базовой станцией или оконечным устройством.

Память может быть установлена внутри процессора или вне процессора. Процессор может быть встроен в оконечное устройство или базовую станцию.

Процессор может быть схемой, одной или более интегральными схемами, или одной или более специальными микросхемами. В качестве альтернативы, процессор может представлять собой микросхему общего назначения, и когда используемая для реализации способа кодирования программная инструкция загружается в процессор, может быть реализована функция вышеизложенного кодирования. В качестве альтернативы, процессор может представлять собой сочетание одной или нескольких схем, интегральной схемы, специальной микросхемы и микросхемы общего назначения.

В соответствии с четвертым аспектом, настоящее изобретение обеспечивает устройство для кодирования, включающее в себя:

интерфейс ввода, выполненный с возможностью получать битовую последовательность, подлежащую кодированию;

логическую схему, выполненную с возможностью выполнять способ по любому одному из первого аспекта и возможных реализаций первого аспекта, на основании полученной битовой последовательности, подлежащей кодированию, для получения кодированных бит; и

интерфейс вывода, выполненный с возможностью выводить кодированные биты.

В возможной реализации устройство является базовой станцией или оконечным устройством.

В соответствии с пятым аспектом, настоящее изобретение обеспечивает устройство связи, включающее в себя устройство для кодирования, представленное в третьем аспекте и возможных реализациях третьего аспекта, и приемопередатчик, где

приемопередатчик выполнен с возможностью отправлять биты, закодированные устройством для кодирования.

В возможной реализации устройство связи представляет собой базовую станцию или оконечное устройство.

В соответствии с шестым аспектом, настоящее изобретение обеспечивает машиночитаемый носитель информации, включающий в себя компьютерную программу. Компьютерная программа используется для реализации способа кодирования, представленного в соответствии с первым аспектом и возможными реализациями первого аспекта.

В соответствии с седьмым аспектом, настоящее изобретение обеспечивает программный продукт. Программный продукт включает в себя компьютерную программу. Компьютерная программа хранится на машиночитаемом носителе информации. По меньшей мере, один процессор устройства для кодирования может считывать компьютерную программу из машиночитаемого носителя информации и, по меньшей мере, один процессор выполняет компьютерную программу, таким образом, что устройство для кодирования выполняет способ кодирования в первом аспекте и возможных реализациях первого аспекта.

После использования CRC полинома, предоставленного в настоящем изобретении, может быть удовлетворено FAR требование системы, чтобы гарантировать надлежащее обеспечение связи.

Краткое описание чертежей

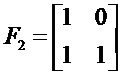

Фиг. 1 (а) и фиг. 1 (b) представляют собой схематические архитектурные схемы системы связи применительно к варианту осуществления настоящего изобретения;

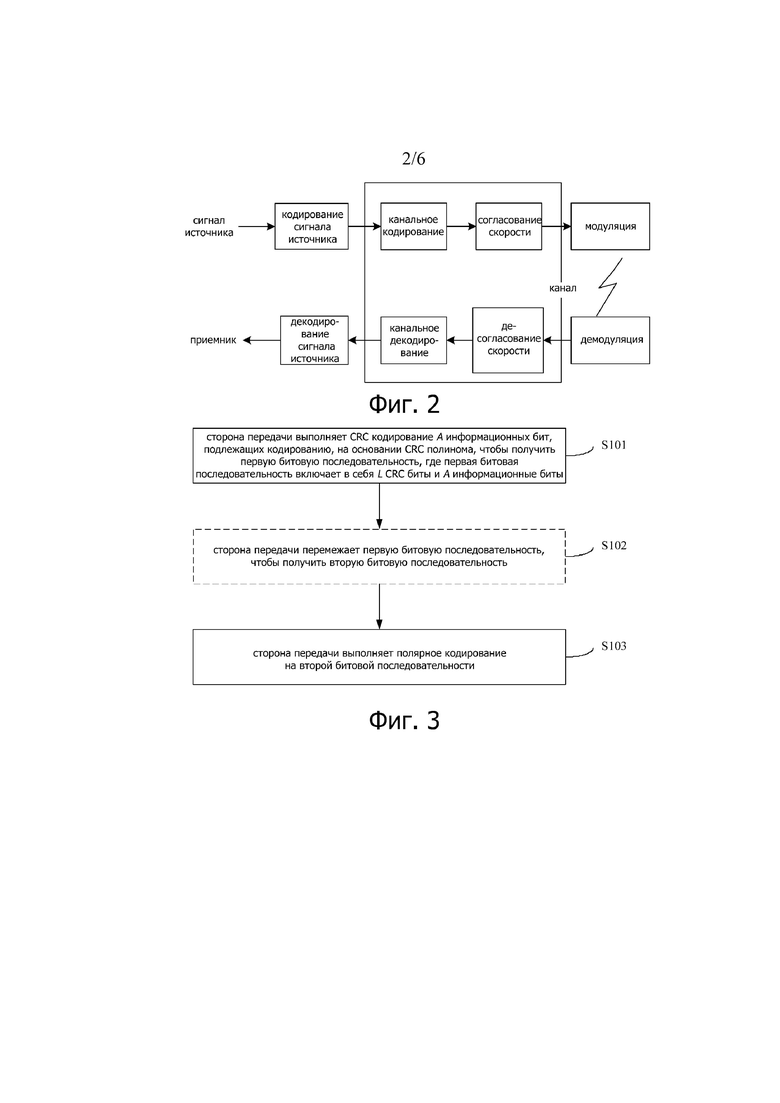

фиг. 2 является блок-схемой последовательности операций системы связи;

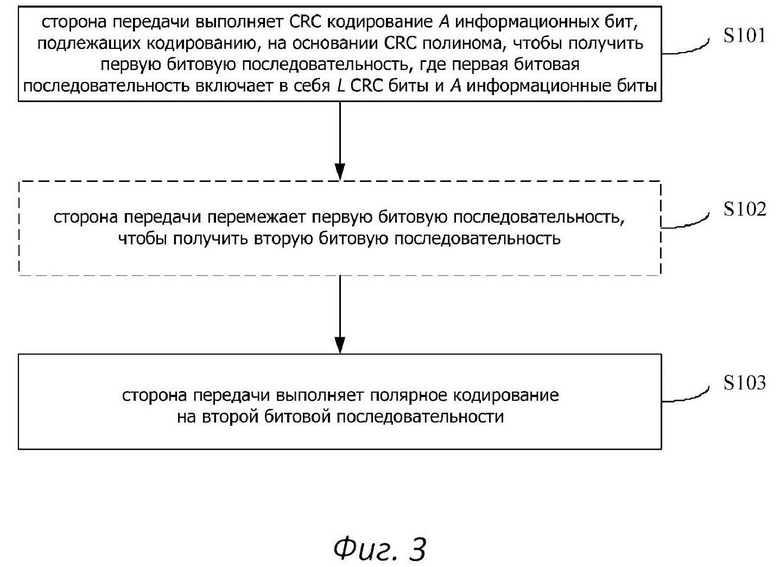

фиг. 3 является блок-схемой алгоритма варианта осуществления способа кодирования в соответствии с настоящим изобретением;

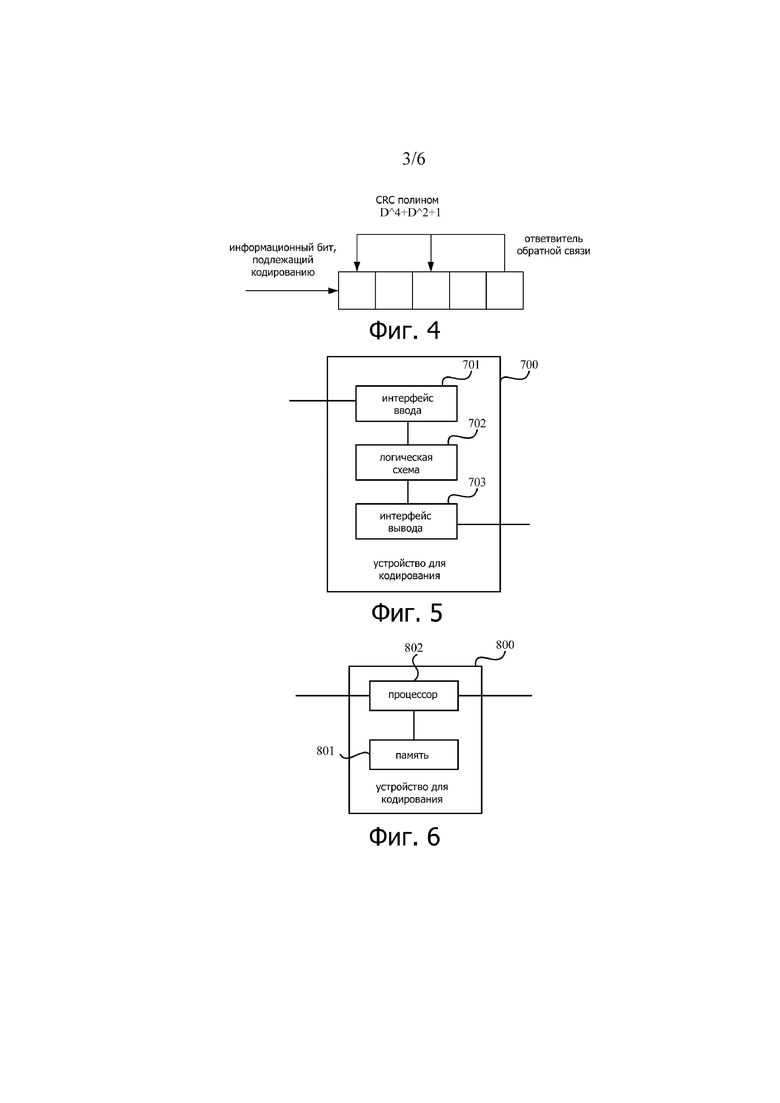

фиг. 4 представляет собой схему CRC способа кодирования;

фиг. 5 представляет собой первую структурную схему устройства для кодирования согласно варианте осуществления настоящего изобретения;

фиг. 6 представляет собой вторую структурную схему устройства для кодирования согласно варианту осуществления настоящего изобретения;

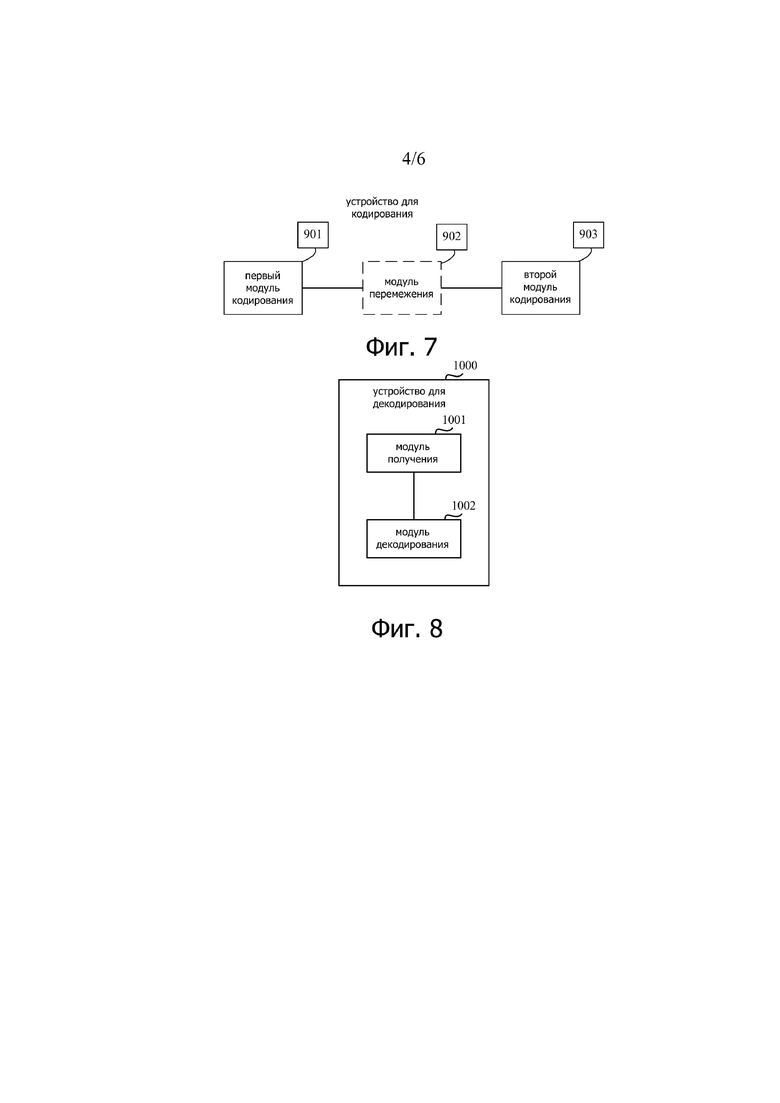

фиг. 7 является третьей структурной схемой устройства для кодирования согласно варианте осуществления настоящего изобретения;

фиг. 8 представляет собой первую структурную схему устройства для декодирования согласно варианте осуществления настоящего изобретения;

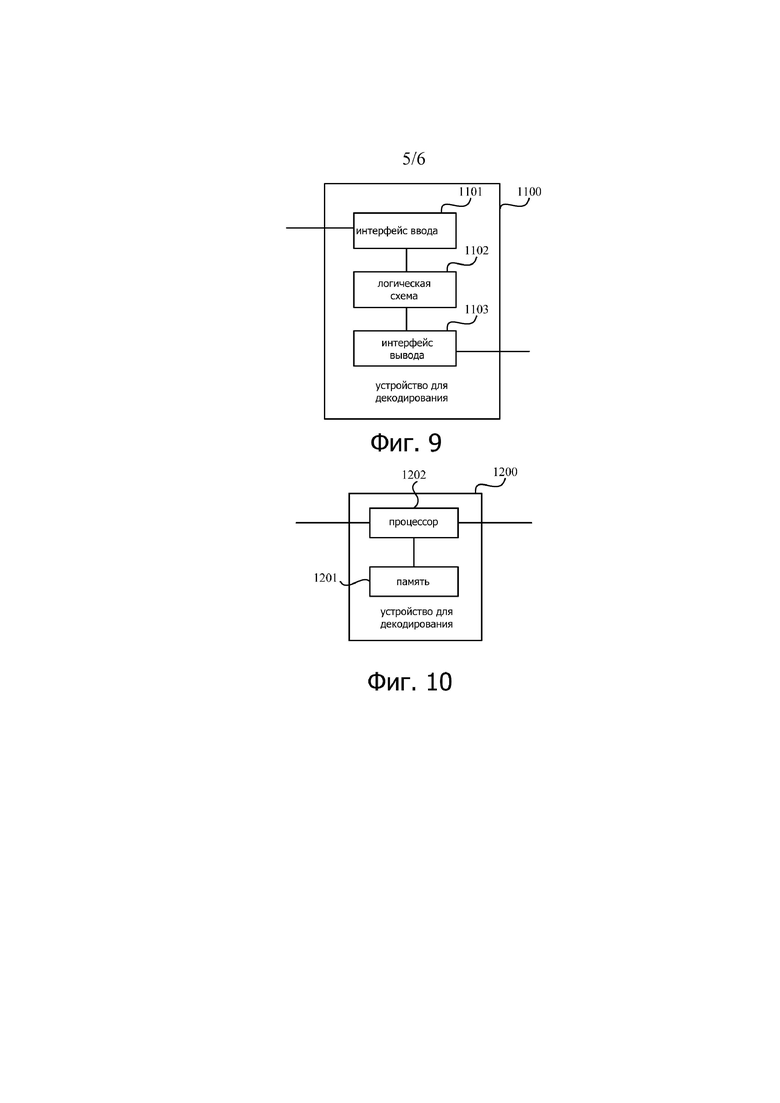

фиг. 9 представляет собой вторую структурную схему устройства для декодирования согласно варианту осуществления настоящего изобретения;

фиг. 10 представляет собой третью структурную схему устройства для декодирования согласно варианту осуществления настоящего изобретения; и

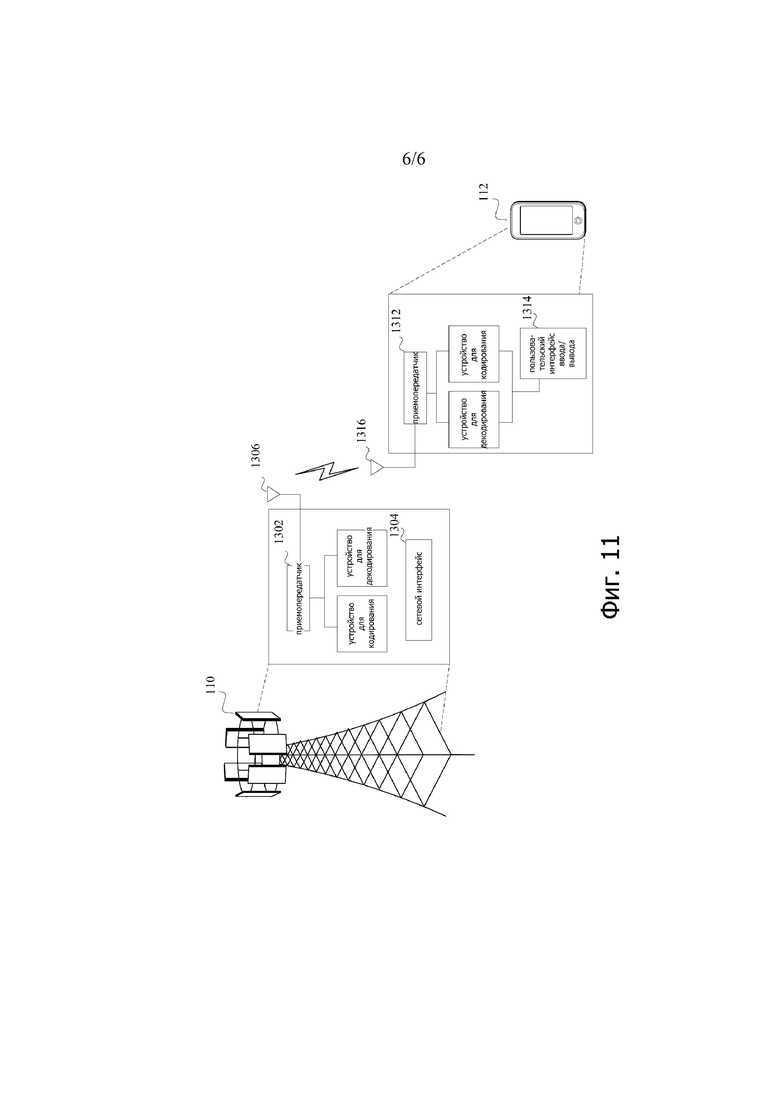

фиг. 11 представляет собой структурную схему сетевого устройства и оконечного устройства в соответствии с вариантом осуществления настоящего изобретения.

Описание вариантов осуществления

Полярный код представляет собой линейный блочный код. Порождающая матрица полярного кода представляет собой

является вектором двоичной строки, длина которого

является вектором двоичной строки, длина которого

Для дополнительного повышения производительности кодирования системы, внешний код, имеющий возможность проверки, например, циклический избыточный код (на английском языке: Cyclic Redundancy Check, CRC), может быть объединен с полярным кодом. При использовании способа декодирования, такого как последовательный список аннулирования (Serial Cancellation List), обычно, после окончания декодирования на выбранных путях осуществляют выбор на основе циклического избыточного кода, таким образом, повышают производительность канального кодирования системы. Когда полярный код используется для канала управления, в дополнение к частоте блочных ошибок (block error rate, BLER), что является нормальным техническим индикатором, дополнительно должен быть удовлетворен индикатор частоты ложной тревоги (false alarm rate, FAR для краткости). Например, если количество CRC битов является L, то используют способ декодирования, такой как последовательный список аннулирования декодирования, после окончания декодирования используют циклический избыточный код, и проверяют Т пути выбранных путей, обычно требуется, чтобы FAR быть меньше, чем (2^(-L+log2(Т))). Следует отметить, что выбор значения Т не зависит от полинома циклического избыточного кода и длины, но зависит от сложности реализации декодирования, производительности декодирования и тому подобные. Поэтому, необходимо решить техническую задачу определения подходящего способа конкатенации CRC проверки кода и полярного кода в соответствии с FAR требованиями. Настоящее изобретение относится к способу определения соответствующего CRC полинома на основании значения L для удовлетворения требования системы и обеспечения нормальных условий связи.

Варианты осуществления настоящего изобретения могут быть применены к системе беспроводной связи. Следует отметить, что система беспроводной связи, упомянутая в вариантах осуществления настоящего изобретения, включает в себя, но не ограничиваются ими: системы «Долгосрочное развитие» (Long Term Evolution, LTE) и три основные сценария применения 5G мобильных система связи следующего поколения: усовершенствованная мобильная широкополосная связь (Enhanced Mobile Broad Band, eMBB), URLLC и массовая связь машинного типа (Massive Machine-Type Communications, mMTC). Альтернативно, система беспроводной связи может быть системой связи «устройство-устройство» (Device to Device, D2D), другой системой связи, перспективной системой связи или тому подобное.

Устройство связи по настоящему изобретению может быть сконфигурировано в устройстве связи, и устройство связи, главным образом, включает в себя сетевое устройство или оконечное устройство. Если сторона передачи в настоящем изобретении является сетевым устройством, то сторона приема является оконечным устройством; или если, сторона передачи в настоящем изобретении представляет собой оконечное устройство, то сторона приема является сетевым устройством.

В одном варианте осуществления настоящего изобретения, как показано на фиг. 1 (а), система 100 связи включает в себя сетевое устройство 110 и оконечное устройство 112. Когда сеть 100 беспроводной связи включает в себя базовую сеть, сетевое устройство 110 может быть дополнительно соединено с базовой сетью. Сетевое устройство 110 может дополнительно взаимодействовать с IP-сетью 200, такой как интернет (internet), частной IP-сетью или другой сетью передачи данных. Сетевое устройство предоставляет услугу для оконечного устройства в пределах покрытия. Например, со ссылкой на фиг. 1 (а), сетевое устройство 110 обеспечивает беспроводной доступ для одного или более оконечных устройств в пределах области покрытия сетевого устройства 110. Дополнительно, перекрывающиеся области могут присутствовать в пределах области покрытия сетевых устройств, таких как сетевое устройство 110 и сетевое устройство 120. Сетевые устройства могут также взаимодействовать друг с другом. Например, сетевое устройство 110 может осуществлять связь с сетевым устройством 120.

Когда сетевое устройство 110 или оконечное устройство 112 передают информацию или данные, может быть использован способ кодирования, описанный в вариантах осуществления настоящего изобретения. Таким образом, для удобства описания, в этом варианте осуществления настоящего изобретения, система 100 связи упрощается до системы, которая включает в себя сторону 101 передачи и сторону 102 приема, как показано на фиг. 1 (b). Сторона 101 передачи может быть сетевым устройством 110 и сторона 102 приема может быть оконечным устройством 112; или сторона 101 передачи может быть оконечным устройством 112 и сторона 102 приема может быть сетевым устройством 110. Сетевое устройство 110 может быть устройством, выполненное с возможностью обмена данными с оконечным устройством. Например, сетевое устройство 110 может быть усовершенствованным NodeB (Evolved Node В, eNB или eNodeB) в LTE системе, сетевым устройством в 5G сети, сетевым устройством для установления связи с оконечным устройством в другой сети или сетевым устройством в сети в будущих поколений. В качестве альтернативы, сетевое устройство может быть ретрансляционной станцией, точкой доступа, устройством, установленным в транспортном средстве или тому подобное. В системе связи «устройство-устройство» (Device to Device, D2D) сетевое устройство может быть оконечным устройством, функционирующим в качестве базовой станции. Оконечное устройство может включать в себя различные портативные устройства, устройства, установленные в транспортном средстве, носимые устройства или вычислительные устройства, имеющие функцию беспроводной связи, или другое устройство обработки, соединенное с беспроводным модемом, а также различные формы устройства пользователя (user equipment, UE), мобильные станции (mobile station, MS) и тому подобное.

Процесс кодирования по настоящему изобретению в общих чертах представляет собой: выполнение CRC проверки информации, подлежащей кодированию; в случае необходимости, выполнение операции, такой как перемежения на CRC проверенной битовой последовательности; и затем выполнение полярного кодирования. Дополнительно, может быть дополнительно выполнено одно или более, включающее в себя, но не ограничиваясь ими, согласование скорости, модуляция, цифро-аналоговое преобразование и преобразование частоты, на основании целевой длины М кода, на кодированных битах, полученных после полярного кодирования.

Фиг. 2 представляет собой блок-схему алгоритма функционирования системы связи. Как показано на фиг. 2, на стороне передачи источник сигнала последовательно подвергается кодированию сигнала, канальному кодированию, согласованию скорости (возможный этап) и модуляции и затем отправке. На стороне приема источник сигнала последовательно подвергается демодуляции, де-согласованию скорости (возможный этап), канальному декодированию и декодированию источника сигнала и выводят в приемник сигнала. Варианты осуществления настоящего изобретения, главным образом, относятся к канальному кодированию и канальному декодированию (кратко упоминается как канальное кодирование и декодирование), и описаны ниже с помощью конкретных примеров. Полярный код, объединенный с CRC проверкой, может использоваться для канального кодирования и декодирования в вариантах осуществления настоящего изобретения.

Настоящее изобретение обеспечивает способ и устройство для кодирования, таким образом, чтобы удовлетворить FAR требование. Способ и устройство по настоящему изобретению применимы как к каналу управления, так и к каналу передачи данных, и применимы как к восходящей линии связи, так и к нисходящей линии связи. Далее приведено подробное описание способа кодирования и устройства по настоящему изобретению со ссылкой на прилагаемые чертежи.

На фиг. 3 показана блок-схема алгоритма варианта осуществления способа кодирования в соответствии с настоящим изобретением. Как показано на фиг. 3, этот вариант осуществления выполняется посредством стороны передачи и способ согласно этому варианту осуществления может включать в себя следующие этапы.

S101. Сторона передачи выполняет CRC кодирование А информационных бит, подлежащих кодированию, на основании CRC полинома, чтобы получить первую битовую последовательность, где первая битовая последовательность включает в себя L CRC биты и А информационные биты, и L и А являются положительными целыми числами. L также обычно называют CRC длиной.

Принимая во внимание FAR требования, когда L = 6, CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+1;

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1.

Конкретный процесс выполнения CRC кодирования на основании выбранного полинома является таким же, как текущее обычное CRC кодирование.

В частности, после приема А информационных бит, подлежащих кодированию, сторона передачи добавляет L CRC биты на основании CRC полинома, чтобы получить первую битовую последовательность.

А информационные биты, подлежащие кодированию, могут быть получены путем сортировки информационных бит, подлежащих кодированию, в порядке возрастания или убывания, или могут быть получены путем выполнения другой обработки информационных битов. Это не ограничивается в настоящем документе.

Реализация CRC кодирования представлено в виде регистра сдвига. Так, например, на фиг. 4 показывает широко используемый способ реализации CRC кодирования в виде регистра сдвига (кратко упоминается как регистр). Определяют ответвитель обратной связи регистра CRC полином D^4+D^2+1 и содержимое регистра инициализируется на заданное значение. При кодировании, информационные биты, подлежащие кодированию, сдвигаются из стороны в регистр бит за битом, и выполняют операцию поразрядного исключающего ИЛИ на ответвителе обратной связи и соответствующего состояния регистра, так что состояние регистра изменяется. После сдвига всех бит, подлежащих кодированию, в регистр, биты 0 количество которых равно количеству бит CRC длины, сдвигаются в регистр, и считывается состояние регистра, и используются в качестве CRC биты состояние регистра, и используется в качестве кодового слова CRC кодирования. L CRC биты в первой битовой последовательности могут быть расположены после А информационных бит, подлежащие кодированию, могут быть расположены перед А информационными битами, подлежащие кодированию, или могут быть расположены в любом месте, на котором согласуют сторона приема и сторона передачи.

S102. Сторона передачи перемежает первую битовую последовательность, чтобы получить вторую битовую последовательность.

На этапе перемежения, некоторые биты в первой битовой последовательности могут перемежаться или все биты в первой битовой последовательности могут перемежаться. Следует отметить, что этот этап является возможным этапом: этот этап необходим только тогда, когда расположение информационного бита и/или CRC проверка бит должно быть скорректировано; и, если местоположение информационного бита и/или CRC бита проверки не должно быть скорректировано, то этот этап может быть пропущен в фактическом процессе кодирования и, в этом случае, второй битовой последовательностью на этапе S103 является первая битовая последовательность. Конкретная схема перемежения не относится к настоящему изобретению, и детали не описаны.

S103. Сторона передачи выполняет полярное кодирование на второй битовой последовательности, чтобы получить третью битовую последовательность. Когда этап S102 опущен, то этот этап представляет собой: сторона передачи выполняет полярное кодирование на первой битовой последовательности, чтобы получить третью битовую последовательность.

Существующий способ полярного кодирования может быть использован в качестве способа кодирования для выполнения стороной передачи полярного кодирования на второй битовой последовательности. Подробности здесь не описаны.

S104 (не показан на фиг.). Сторона передачи выполняет некоторые или все этапы, включающие в себя, но не ограничиваясь, согласование скорости, модуляцию, аналого-цифровое преобразование и преобразование частоты на третьей битовой последовательности и затем отправляет третью битовую последовательность.

Следует отметить, что, этап согласования скорости на этапе S104 является возможным. Если длина кода кодирования является такой же, как целевая длина кода, то согласование скорости не требуется. Этот вариант осуществления настоящего изобретения не придает особого значения этапу S104. Таким образом, детали здесь не описаны. Например, в возможной реализации, специалисты в данной области техники может сделать ссылку на практику в предшествующем уровне техники.

На основании способа кодирования, представленном в данном варианте осуществления, сторона передачи выполняет CRC кодирование А информационных бит, подлежащих кодированию, на основании CRC полинома, предусмотренного в настоящем изобретении, для получения первой битовой последовательности, и затем выполняют перемежение (при необходимости) и полярное кодирование на первой битовой последовательности. Поэтому, после объединения CRC, используемый способ полярного кодирования может удовлетворить FAR требование.

Следует отметить, что, после приема информационных бит, подлежащих кодированию, сторона приема (на стороне декодера) также должна выполнять CRC проверку на основании того же CRC полинома. Подробности здесь не описаны.

В этом варианте осуществления настоящего изобретения операция декодирования на стороне декодера примерно представляет собой: прием последовательности, подлежащей кодированию, и выполнение полярного декодирования полученной последовательности, подлежащей кодированию, на основании CRC полинома.

На основании идеи изобретения, такой же, как в способе кодирования, показанного на фиг. 3, на фиг. 5 показан вариант осуществления настоящего изобретения, который дополнительно предусматривает устройство 700. Устройство 700 для кодирования выполнено с возможностью выполнять способ кодирования, показанный на фиг. 3. Некоторые или все этапы способа кодирования, показанного на фиг. 3, могут быть выполнены с использованием аппаратных средств или с помощью программного обеспечения. Когда некоторые или все этапы способа кодирования, показанного на фиг. 3, выполняют с использованием аппаратных средств, устройство 700 для кодирования включает в себя: интерфейс 701 ввода, выполненный с возможностью получать битовую последовательность, подлежащую кодированию; логическую схему 702, выполненную с возможностью выполнять способ кодирования, показанный на фиг. 3, где для получения дополнительной информации обратитесь к описанию в приведенном выше варианте осуществления способа, и детали не описаны здесь снова; и интерфейс 703 вывода, выполненный с возможностью выводить кодированную битовую последовательность.

Возможно, в ходе конкретной реализации, устройство 700 для кодирования может представлять собой микросхему или интегральную схему.

Возможно, когда некоторые или все этапы способа кодирования предшествующего варианта выполняют с помощью программного обеспечения, как показано на фиг. 6, устройство 800 для кодирования включает в себя: память 801, выполненную с возможностью хранить программу; и процессор 802, выполненный с возможностью выполнения программы, хранящейся в памяти 801. Когда программа выполняется, устройство 800 для кодирования выполняет способ кодирования, предусмотренный в варианте осуществления на фиг. 3.

Возможно, память 801 может быть физически независимым блоком или может быть интегрирована с процессором 802.

Возможно, когда некоторые или все этапы способа кодирования согласно варианту осуществления на фиг. 3 выполняется с помощью программного обеспечения, устройство 800 для кодирования может включать в себя только процессор 802. Память 801, выполненную с возможностью хранить программу, расположена вне устройства 800 для кодирования, и процессор 802, подключенный к памяти 801 с помощью схемы или провода, и выполненный с возможностью считывать и выполнять программу, хранящуюся в памяти 801.

Процессор 802 может представлять собой центральный блок обработки (central processing unit, CPU), сетевой процессор (network processor, NP) или сочетание процессора и NP.

Процессор 802 может дополнительно включать в себя аппаратную микросхему. Аппаратная микросхема может быть специализированной интегральной схемой (application-specific integrated circuit, ASIC), программируемым логическим устройством (programmable logic device, PLD) или их комбинации. PLD может быть сложным программируемым логическим устройством (complex programmable logic device, CPLD), программируемой вентильной матрицей (field-programmable gate array, FPGA), типовой матричной логикой (generic array logic, GAL) или любую их комбинацию.

Память 801 может включать в себя энергонезависимую память (volatile memory), например, оперативное запоминающее устройство (random-access memory, RAM). В качестве альтернативы, память 801 может включать в себя энергонезависимую память (non-volatile memory), например, флэш-память (flash memory), жесткий диск (hard disk drive, HDD) или твердотельный накопитель (solid-state drive, SSD). В качестве альтернативы, память 801 может включать в себя комбинацию из указанных выше типов памяти.

На основе идеи изобретения такой же, как в способе кодирования, показанного на фиг. 3, на фиг. 7 показан вариант осуществления настоящего изобретения, который дополнительно обеспечивает схему варианта осуществления устройства для кодирования. Устройство может включать в себя: первый модуль 901 кодирования, модуль 902 перемежения и второй модуль 903 кодирования. Первый модуль 901 кодирования выполнен с возможностью выполнять кодирование циклическим избыточным кодом CRC А информационных бит, подлежащих кодированию, на основании CRC полинома, чтобы получить первую битовую последовательность, где первая битовая последовательность включает в себя L CRC биты и А информационные биты, L и A являются положительными целыми числами, L = 6, и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+1;

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1.

Как правило, CRC полином, используемый для CRC кодирования, реализуют с помощью регистра сдвига. L CRC биты в первой битовой последовательности могут быть расположены после А информационных бит, подлежащих кодированию, могут быть расположены перед А информационными битами, подлежащие кодированию, или могут быть расположены в любом месте, на котором согласует сторона приема и сторона передачи. Модуль 902 перемежения является дополнительным модулем, и выполнен с возможностью выполнять операцию перемежения на первой битовой последовательности, чтобы получить вторую битовую последовательность. Этот модуль необходим только тогда, когда расположение информационного бита и/или биты CRC проверки должно быть скорректировано способом распределенной CRC. Если местоположение информационного бита и/или бита CRC проверки не должно быть скорректировано, то этот модуль может быть опущен в реальном процессе кодирования и, в этом случае, второй битовой последовательностью является первая битовая последовательность. Второй модуль 903 кодирования выполнен с возможностью выполнять полярное кодирование на второй битовой последовательности, и при отсутствии модуля 902 перемежения, второй модуль 903 кодирования выполнен с возможностью выполнять полярное кодирование на первой битовой последовательности.

Следует отметить, что, модули, такие как модуль согласования скорости, модуль модуляции и модуль отправки на фиг. 7 не показаны. Модуль отправки выполнен с возможностью отправлять кодированную последовательность и, конечно, перед отправкой кодированной последовательности, необходимо выполнить дополнительные операции, такие как согласование скорости (при необходимости) и модуляции.

На основании идеи изобретения способ декодирования, представленный в предшествующем варианте осуществления, как показано на фиг. 8, является таким же как способ варианта осуществления настоящего изобретения, который дополнительно обеспечивает устройство 1000 для декодирования. Устройство 1000 для декодирования может быть выполнено с возможностью выполнять способ декодирования, представленный в варианте осуществления настоящего изобретения, и устройство 1000 для декодирования включает в себя:

модуль 1001 получения, выполненный с возможностью получать битовую последовательность, подлежащую декодированию; и

модуль 1002 декодирования, выполненный с возможностью выполнять операцию декодирования битовой последовательности, подлежащей декодированию, в соответствии со способом декодирования, при этом способ декодирования определяют на основании CRC полинома и способа полярного кодирования.

На основании идеи изобретения такой же, как способ декодирования, представленный в предшествующем варианте осуществления, как показано на фиг. 9, где показан вариант осуществления настоящего изобретения, дополнительно предоставляет устройство 1100 для декодирования. Устройство 1100 для декодирования выполнено с возможностью выполнять представленный выше способ декодирования. Некоторые или все этапы вышеизложенного способа декодирования могут быть выполнены с использованием аппаратных средств или с помощью программного обеспечения. Когда некоторые или все этапы упомянутого способа декодирования выполняют с использованием аппаратных средств, устройство 1100 для декодирования включает в себя: интерфейсе 1101 ввода, выполненный с возможностью получать битовую последовательность, подлежащую декодированию; логическую схему 1102, выполненную с возможностью выполнять вышеизложенный способ декодирования; и интерфейс 1103 вывода, выполненный с возможностью выводить декодированную последовательность.

Возможно, в ходе конкретной реализации, устройство 1100 для декодирования может быть микросхемой или интегральной схемой.

Возможно, когда некоторые или все этапы способа декодирования предшествующего варианта выполняются с помощью программного обеспечения, как показано на фиг. 10, устройство 1200 для декодирования включает в себя: память 1201, выполненную с возможностью хранить программу; и процессор 1202, выполненный с возможностью выполнения программы, хранящейся в памяти 1201. Когда программа выполняется, устройство 1200 для декодирования выполняет способ декодирования, предоставленный в вышеприведенном варианте осуществления.

Возможно, память 1201 может быть физически независимым блоком или может быть объединена с процессором 1202.

Возможно, когда некоторые или все этапы способа декодирования предшествующего варианта выполняется с помощью программного обеспечения, устройство 1200 для декодирования может включать в себя только процессор 1202. Память 1201, выполненная с возможностью хранения программы, находится за пределами устройства 1200 для декодирования, и процессор 1202 соединен с памятью 1201 с помощью схемы или проводки, и выполненный с возможностью считывать и выполнять программу, хранящуюся в памяти 1201.

Процессор 1202 может представлять собой центральный блок обработки (central processing unit, CPU), сетевой процессор (network processor, NP) или сочетание процессора и NP.

Процессор 1202 может дополнительно включать в себя аппаратную микросхему. Аппаратная микросхема может быть специализированной интегральной схемой (application-specific integrated circuit, ASIC), программируемым логическим устройством (programmable logic device, PLD) или их комбинации. PLD может быть сложным программируемым логическим устройством (complex programmable logic device, CPLD), программируемой вентильной матрицей (field-programmable gate array, FPGA), типовой матричной логикой (generic array logic, GAL) или любую их комбинацию.

Память 1201 может включать в себя энергонезависимую память (volatile memory), например, оперативное запоминающее устройство (random-access memory, RAM). В качестве альтернативы, память 801 может включать в себя энергонезависимую память (non-volatile memory), например, флэш-память (flash memory), жесткий диск (hard disk drive, HDD) или твердотельный накопитель (solid-state drive, SSD). В качестве альтернативы, память 801 может включать в себя комбинацию из указанных выше типов памяти.

Вариант осуществления настоящего изобретения дополнительно обеспечивает сетевое устройство. Со ссылкой на фиг. 11, предшествующее устройство для кодирования и/или устройство для декодирования может быть установлено в сетевом устройстве 110. В дополнение к вышеизложенному, устройство для кодирования и устройство для декодирования, сетевое устройство 110 может дополнительно включать в себя приемопередатчик 1302. Битовая последовательность, кодированная устройством для кодирования, претерпевает последующим изменениям или обработке, и затем отправляют приемопередатчиком 1302 в оконечное устройство 112, или приемопередатчик 1302 дополнительно выполнен с возможностью принимать информацию или данные из оконечного устройства 112. Информация или данные претерпевают последовательную обработку и преобразуются в последовательность, подлежащая декодированию, последовательность, подлежащая декодированию, обрабатывают устройством для декодирования, чтобы получить декодированную последовательность. Сетевое устройство 110 может дополнительно включать в себя сетевой интерфейс 1304, выполненный с возможностью установления соединения с другим сетевым устройством.

Кроме того, устройство для кодирования и/или устройство для декодирования может быть выполнено в оконечном устройстве 112. В дополнение к вышеизложенному устройство для кодирования и/или устройство для декодирования, оконечное устройство 112 могут дополнительно включать в себя приемопередатчик 1312. Битовая последовательность, кодируемая устройством для кодирования, претерпевает последующие изменения или обработку (включающую в себя, но не ограничиваясь этим, некоторые или все согласование скорости, модуляцию, цифроаналоговое преобразование и преобразование частоты), а затем отправляют посредством приемопередатчика 1312 в сетевое устройство 110, или приемопередатчик 1312 также выполнен с возможностью принимать информацию или данные от сетевого устройства 110. Информация или данные претерпевают последовательную обработку (включающую в себя, но не ограничиваясь этим, некоторые или все преобразование частоты, аналого-цифровое преобразование, демодуляцию и де-согласование скорости) и преобразуют в декодированную последовательность, и последовательность, подлежащая декодированию, обрабатывают устройством для декодирования, чтобы получить декодированную последовательность. Оконечное устройство 112 может дополнительно включать в себя пользовательский интерфейс 1314 ввода/вывода, выполненный с возможностью принимать информацию, вводимую пользователем. Информация, которая должна быть отправлена на сетевое устройство 110, должна быть обработана с помощью кодера, а затем отправлена приемопередатчиком 1312 в сетевое устройство 110. После прохождения последующей обработки, данные, декодированные посредством декодера, могут быть представлены пользователю, используя интерфейс 1314 ввода/вывода.

Вариант осуществления настоящего изобретения дополнительно обеспечивает машиночитаемый носитель данных, который хранит компьютерную программу. Компьютерная программа используется для выполнения способа кодирования, показанного на фиг. 3, и упомянутый вариант осуществления и способ декодирования, предоставленный в вышеупомянутом варианте осуществления.

Вариант осуществления настоящего изобретения дополнительно предоставляет устройство для полярного кодирования, включающее в себя любое из устройств для кодирования на фиг. 5 - фиг. 7 и любое из устройств для декодирования на фиг. 8 - фиг. 10.

Вариант осуществления настоящего изобретения дополнительно предусматривает компьютерный программный продукт, включающий в себя инструкции. При запуске инструкции на компьютере, компьютер выполняет способ кодирования, показанный на фиг. 3, и способ декодирования, предоставленный в вышеприведенном варианте осуществления.

Специалистам в данной области техники должно быть понятно, что варианты осуществления настоящего изобретения могут быть предусмотрены в качестве способа, системы или компьютерного программного продукта. Таким образом, настоящее изобретение может использовать форму только аппаратных вариантов осуществления, только вариантов осуществления программного обеспечения или вариантов осуществления с комбинацией программных и аппаратных средств. Кроме того, настоящее изобретение может использовать форму компьютерного программного продукта, который реализуется на одном или нескольких машиночитаемых носителях данных (включающие в себя, но не ограничиваясь дисковой памяти, CD-ROM и оптической памяти), которые включают в себя машиночитаемый программный код.

Настоящее изобретение описано со ссылкой на блок-схему алгоритма и/или блок-схему способа, устройства (системы) и компьютерный программный продукт, в соответствии с вариантами осуществления настоящего изобретения. Следует понимать, что инструкции компьютерной программы могут быть использованы для реализации каждого процесса и/или каждого этапа в блок-схемах алгоритма и/или блок-схемах и комбинации процесса и/или этапа в блок-схемах алгоритма и/или блок-схемах. Эти инструкции компьютерной программы могут быть предоставлены для компьютера общего назначения, выделенного компьютера, встроенного процессора или процессора любого другого устройства программируемой обработки данных, чтобы сгенерировать машину, так что инструкции, исполняемые компьютером или процессором любых других программируемых устройств обработки данных генерируют устройство для реализации специфической функции в одном или нескольких процессах в блок-схемах алгоритма и/или в одном или нескольких блоках в блок-схемах.

Эти инструкции компьютерной программы могут храниться в машиночитаемой памяти, которая может инструктировать компьютер или любые другие программируемые устройства для обработки определенным образом данных, так что инструкции, сохраненные в считываемой памяти компьютера, генерировать артефакт, который включает в себя инструкцию устройства. Инструкция устройства реализует конкретную функцию, в одном или нескольких процессах в блок-схемах алгоритма и/или в одном или нескольких блоках в блок-схемах.

Эти инструкции компьютерной программы могут быть загружены в компьютер или другое программируемое устройство обработки данных, так что на компьютере или другом программируемом устройстве выполняют последовательность операций и этапов, тем самым, генерируя реализуемую компьютером обработку. Таким образом, инструкции, выполняемые на компьютере или другом программируемом устройстве, обеспечивают этапы для реализации специфической функции в одном или нескольких процессах в блок-схемах алгоритма и/или в одном или нескольких блоках в блок-схемах.

Хотя были описаны некоторые варианты осуществления настоящего изобретения, специалисты в данной области техники могут вносить изменения и модификации в эти варианты осуществления, как только они узнают основную концепцию изобретения. Таким образом, прилагаемая формула изобретения охватывает предпочтительные варианты осуществления и все изменения и модификации, входящие в объем настоящего изобретения.

Очевидно, что специалисты в данной области техники могут внести различные модификации и изменения в вариантах осуществления настоящего изобретения без отхода от объема вариантов осуществления настоящего изобретения. Настоящее изобретение охватывает эти модификации и изменения при условии, что они находятся в пределах объема защиты, определенного в следующей формуле изобретения и их эквивалентных технологий.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ | 2018 |

|

RU2728527C1 |

| CRC-БИТЫ ДЛЯ ОБЪЕДИНЕННОГО ДЕКОДИРОВАНИЯ И ВЕРИФИКАЦИИ УПРАВЛЯЮЩЕЙ ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ ПОЛЯРНЫХ КОДОВ | 2017 |

|

RU2733282C1 |

| СПОСОБЫ И УСТРОЙСТВА ДЛЯ ПЕРЕДАЧИ И ОБРАБОТКИ ДАННЫХ, УСТРОЙСТВО СЕТЕВОЙ СТОРОНЫ И ТЕРМИНАЛ | 2018 |

|

RU2743100C1 |

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО СВЯЗИ | 2019 |

|

RU2782241C1 |

| КОНКАТЕНИРОВАННЫЙ ПОЛЯРНЫЙ КОД С ПЕРЕМЕЖЕНИЕМ | 2017 |

|

RU2755398C2 |

| МНОГОУРОВНЕВЫЙ КОД ЦИКЛИЧЕСКОЙ ПРОВЕРКИ ИЗБЫТОЧНОСТЬЮ В СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 2008 |

|

RU2481702C2 |

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 2007 |

|

RU2408979C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ СОГЛАСОВАНИЯ СКОРОСТИ, СПОСОБ И УСТРОЙСТВО ДЛЯ ДЕСОГЛАСОВАНИЯ СКОРОСТИ | 2018 |

|

RU2768256C2 |

| СПОСОБ КОДИРОВАНИЯ И УСТРОЙСТВО КОДИРОВАНИЯ ДЛЯ ПОЛЯРНОГО КОДА | 2018 |

|

RU2782234C2 |

| КОНКАТЕНИРОВАННЫЙ ПОЛЯРНЫЙ КОД С АДАПТИВНЫМ ОБНАРУЖЕНИЕМ ОШИБОК | 2018 |

|

RU2733818C1 |

Изобретение относится к средствам для кодирования. Технический результат заключается в повышении эффективности кодирования. Выполнение CRC кодирования А информационных бит, подлежащих кодированию, на основании CRC полинома, для получения первой битовой последовательности, где первая последовательность битов включает в себя L CRC биты и А информационные биты, L=6; и выполнение полярного кодирования первой битовой последовательности. На основании улучшенного CRC полинома, осуществляют кодирование, удовлетворяющие FAR требованию. 18 н. и 30 з.п. ф-лы, 12 ил.

1. Способ кодирования, содержащий:

выполнение устройством для кодирования, на основании полинома циклического избыточного кода (CRC), CRC кодирования А информационных бит, подлежащих кодированию, для получения CRC-кодированной битовой последовательности, в котором CRC-кодированная битовая последовательность содержит L CRC биты и А информационные биты, подлежащие кодированию, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

выполнение устройством для кодирования полярного кодирования на CRC-кодированной битовой последовательности, чтобы получить полярно-кодированную битовую последовательность.

2. Способ кодирования, содержащий:

выполнение устройством для кодирования, на основании полинома циклического избыточного кода (CRC), CRC кодирования А информационных бит, подлежащих кодированию, для получения CRC-кодированной битовой последовательности, в котором CRC-кодированная битовая последовательность содержит L CRC биты и А информационные биты, подлежащие кодированию, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой: D^6+D^5+1; и

выполнение устройством для кодирования полярного кодирования на CRC-кодированной битовой последовательности, чтобы получить полярно-кодированную битовую последовательность.

3. Способ по п. 1 или 2, в котором CRC полином реализован с использованием регистра сдвига.

4. Способ по любому из пп. 1-3, в котором L CRC биты в CRC-кодированной битовой последовательности расположены после А информационных бит, подлежащих кодированию.

5. Способ по любому из пп. 1-4, в котором способ дополнительно содержит:

отправку устройством для кодирования полярно-кодированной битовой последовательности.

6. Способ по п. 5, в котором перед отправкой полярно-кодированной битовой последовательности, устройство для кодирования выполняет согласование скорости на полярно-кодированной битовой последовательности на основании целевой длины кода.

7. Способ по любому из пп. 1-6, в котором устройством для кодирования является базовая станция или оконечное устройство.

8. Устройство для кодирования, содержащее:

первый модуль кодирования, выполненный с возможностью выполнять, на основании полинома циклического избыточного кода (CRC), CRC кодирование А информационных бит, подлежащих кодированию, для получения CRC-кодированной битовой последовательности, в котором CRC-кодированная битовая последовательность содержит L CRC биты и А информационные биты, подлежащие кодированию, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

второй модуль кодирования, выполненный с возможностью выполнять полярное кодирование на CRC-кодированной битовой последовательности, чтобы получить полярно-кодированную битовую последовательность.

9. Устройство для кодирования, содержащее:

первый модуль кодирования, выполненный с возможностью выполнять, на основании полинома циклического избыточного кода (CRC), CRC кодирование А информационных бит, подлежащих кодированию, для получения CRC-кодированной битовой последовательности, в котором CRC-кодированная битовая последовательность содержит L CRC биты и А информационные биты, подлежащие кодированию, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой: D^6+D^5+1; и

второй модуль кодирования, выполненный с возможностью выполнять полярное кодирование на CRC-кодированной битовой последовательности, чтобы получить полярно-кодированную битовую последовательность.

10. Устройство по п. 8 или 9, в котором устройство дополнительно содержит регистр сдвига, и CRC полином выполняют с использованием регистра сдвига.

11. Устройство по любому из пп. 8-10, в котором L CRC биты в CRC-кодированной битовой последовательности расположены после А информационных бит, подлежащих кодированию.

12. Устройство по любому из пп. 8-11, в котором устройство дополнительно содержит модуль отправки, выполненный с возможностью отправлять полярно-кодированную битовую последовательность.

13. Устройство по п. 12, в котором перед отправкой полярно-кодированной битовой последовательности устройство выполняет согласование скорости на полярно-кодированной битовой последовательности на основании целевой длины кода.

14. Устройство по любому из пп. 8-13, в котором устройство является базовой станцией или оконечным устройством.

15. Устройство для кодирования, содержащее процессор, в котором процессор выполнен с возможностью:

выполнять, на основании полинома циклического избыточного кода (CRC), CRC кодирование А информационных бит, подлежащих кодированию, для получения CRC-кодированной битовой последовательности, в котором CRC-кодированная битовая последовательность содержит L CRC биты и А информационные биты, подлежащие кодированию, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

выполнять полярное кодирование на CRC-кодированной битовой последовательности, чтобы получить полярно-кодированную битовую последовательность.

16. Устройство для кодирования, содержащее процессор, в котором процессор выполнен с возможностью:

выполнять, на основании полинома циклического избыточного кода (CRC), CRC кодирование А информационных бит, подлежащих кодированию, для получения CRC-кодированной битовой последовательности, в котором CRC-кодированная битовая последовательность содержит L CRC биты и А информационные биты, подлежащие кодированию, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой: D^6+D^5+1; и

выполнять полярное кодирование на CRC-кодированной битовой последовательности, чтобы получить полярно-кодированную битовую последовательность.

17. Устройство по п. 15 или 16, в котором устройство для кодирования дополнительно содержит память, и память выполнена с возможностью хранить программную инструкцию.

18. Устройство по любому из пп. 15-17, в котором CRC полином реализован с использованием регистра сдвига.

19. Устройство по любому из пп. 15-18, в котором L CRC биты в CRC-кодированной битовой последовательности расположены после А информационных бит, подлежащих кодированию.

20. Устройство по любому из пп. 15-19, в котором устройство дополнительно содержит приемопередатчик, выполненный с возможностью отправлять полярно-кодированную битовую последовательность.

21. Устройство по п. 20, в котором перед отправкой приемопередатчиком полярно-кодированной битовой последовательности, процессор дополнительно выполнен с возможностью выполнять согласование скорости на полярно-кодированной битовой последовательности на основании целевой длины кода.

22. Устройство по любому из пп. 15-21, в котором устройство является базовой станцией или оконечным устройством.

23. Устройство для кодирования, содержащее:

интерфейс ввода, выполненный с возможностью получать А информационные биты, подлежащие кодированию;

логическую схему, выполненную с возможностью: выполнять, на основании полинома циклического избыточного кода (CRC), CRC кодирование А информационных бит, подлежащих кодированию, для получения CRC-кодированной битовой последовательности, в котором CRC-кодированная битовая последовательность содержит L CRC биты и А информационные биты, подлежащие кодированию, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

выполнять полярное кодирование на CRC-кодированной битовой последовательности, чтобы получить полярно-кодированную битовую последовательность; и

интерфейс вывода, выполненный с возможностью выводить полярно-кодированную битовую последовательность.

24. Устройство для кодирования, содержащее:

интерфейс ввода, выполненный с возможностью получать А информационные биты, подлежащие кодированию;

логическую схему, выполненную с возможностью: выполнять, на основании полинома циклического избыточного кода (CRC), CRC кодирование А информационных бит, подлежащих кодированию, для получения CRC-кодированной битовой последовательности, в котором CRC-кодированная битовая последовательность содержит L CRC биты и А информационные биты, подлежащие кодированию, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой: D^6+D^5+1; и

выполнять полярное кодирование на CRC-кодированной битовой последовательности, чтобы получить полярно-кодированную битовую последовательность; и

интерфейс вывода, выполненный с возможностью выводить полярно-кодированную битовую последовательность.

25. Устройство по п. 23 или 24, в котором CRC полином реализован с использованием регистра сдвига.

26. Устройство по любому из пп. 23-25, в котором L CRC биты в CRC-кодированной битовой последовательности расположены после А информационных бит, подлежащих кодированию.

27. Устройство по п. 23 или 24, в котором логическая схема дополнительно выполнена с возможностью: до того, как интерфейс вывода выводит полярно-кодированную битовую последовательность, выполнять согласование скорости на полярно-кодированной битовой последовательности на основании целевой длины кода.

28. Машиночитаемый носитель данных, в котором носитель выполнен с возможностью хранить компьютерную программу, и, когда компьютерную программу выполняют устройством связи, реализуют способ по любому из пп. 1-6.

29. Способ декодирования, содержащий:

прием устройством для декодирования последовательности, подлежащей декодированию;

выполнение устройством для декодирования полярного декодирования на последовательности, подлежащей декодированию, на основании полинома циклического избыточного кода (CRC), чтобы получить полярно-декодируемую битовую последовательность, в котором полярно-декодируемая битовая последовательность содержит L CRC биты и А информационные биты, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

вывод устройством для декодирования полярно-декодированную битовую последовательность.

30. Способ декодирования, содержащий:

прием устройством для декодирования последовательности, подлежащей декодированию;

выполнение устройством для декодирования полярного декодирования на последовательности, подлежащей декодированию, на основании полинома циклического избыточного кода (CRC), чтобы получить полярно-декодируемую битовую последовательность, в котором полярно-декодируемая битовая последовательность содержит L CRC биты и А информационные биты, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой: D^6+D^5+1; и

вывод устройством для декодирования полярно-декодированную битовую последовательность.

31. Способ по п. 29 или 30, в котором L CRC биты в последовательности, подлежащей декодированию, расположены после А информационных бит.

32. Способ по любому из пп. 29-31, в котором перед приемом устройством для декодирования последовательности, подлежащей декодированию, устройство для декодирования дополнительно выполнено с возможностью принимать информацию или данные со стороны передачи и выполнять де-согласование скорости на информации или данных со стороны передачи, чтобы получить последовательность, подлежащую декодированию.

33. Способ по любому из пп. 29-32, в котором устройство для декодирования представляет собой базовую станцию или оконечное устройство.

34. Устройство для декодирования, содержащее:

модуль получения, выполненный с возможностью получать последовательность, подлежащую декодированию, в котором последовательность, подлежащая декодированию, содержит L биты циклического избыточного кода (CRC) и А информационные биты, L и А являются положительными целыми числами, и L = 6; и

модуль декодирования, выполненный с возможностью выполнять полярное декодирование на последовательности, подлежащей декодированию, на основании CRC полинома, чтобы получить полярно-декодируемую битовую последовательность, в котором CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1.

35. Устройство для декодирования, содержащее:

модуль получения, выполненный с возможностью получать последовательность, подлежащую декодированию, в котором последовательность, подлежащая декодированию, содержит L биты циклического избыточного кода (CRC) и А информационные биты, L и А являются положительными целыми числами, и L = 6; и

модуль декодирования, выполненный с возможностью выполнять полярное декодирование на последовательности, подлежащей декодированию, на основании CRC полинома, чтобы получить полярно-декодируемую битовую последовательность, в котором CRC полином представляет собой: D^6+D^5+1.

36. Устройство по п. 34 или 35, в котором L CRC биты последовательности, подлежащей декодированию, расположены после А информационных бит.

37. Устройство по любому из пп. 34-36, в котором до приема модулем получения битовой последовательности, подлежащей декодированию, модуль получения дополнительно выполнен с возможностью принимать информацию или данные со стороны передачи и выполнять де-согласование скорости на информации или данных со стороны передачи, для получения последовательности, подлежащей декодированию.

38. Устройство по любому пп. 34-37, в котором устройство является базовой станцией или оконечным устройством.

39. Устройство для декодирования, содержащее процессор, в котором процессор выполнен с возможностью:

получать последовательность, подлежащую декодированию, в котором последовательность, подлежащая декодированию, содержит L биты циклического избыточного кода (CRC) и А информационные биты и L = 6; и

выполнять полярное декодирование последовательности, подлежащей декодированию, на основании CRC полинома, чтобы получить полярно-декодируемую битовую последовательность, в котором CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1.

40. Устройство для декодирования, содержащее процессор, в котором процессор выполнен с возможностью:

получать последовательность, подлежащую декодированию, в котором последовательность, подлежащая декодированию, содержит L биты циклического избыточного кода (CRC) и А информационные биты и L = 6; и

выполнять полярное декодирование последовательности, подлежащей декодированию, на основании CRC полинома, чтобы получить полярно-декодируемую битовую последовательность, в котором CRC полином представляет собой: D^6+D^5+1.

41. Устройство по п. 39 или 40, в котором устройство для декодирования дополнительно содержит память, и память выполнена с возможностью хранить инструкцию программы.

42. Устройство по любому из пп. 39-41, в котором L CRC биты в последовательности, подлежащей декодированию, расположены после А информационных бит.

43. Устройство по любому пп. 39-42, в котором перед приемом процессором битовой последовательности, подлежащей декодированию, процессор дополнительно выполнен с возможностью принимать информацию или данные со стороны передачи и выполнять де-согласование скорости на информации или данных со стороны передачи, чтобы получить последовательность, подлежащую декодированию.

44. Устройство по любому пп. 39-43, в котором устройство является базовой станцией или оконечным устройством.

45. Устройство для декодирования, содержащее:

интерфейс ввода, выполненный с возможностью получать последовательность, подлежащую декодированию;

логическую схему, выполненную с возможностью выполнять полярное декодирование последовательности, подлежащей декодированию, на основании полинома циклического избыточного кода (CRC), для получения полярно-декодируемой битовой последовательности, в котором полярно-декодируемая битовая последовательность содержит L CRC биты и А информационные биты, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой любой один из следующих полиномов:

D^6+D^5+D^4+D^3+1;

D^6+D^4+D^3+D+1;

D^6+D^3+D^2+D+1;

D^6+D^5+D^2+1;

D^6+D^5+D^4+D^2+1;

D^6+D^3+D^2+1;

D^6+D^5+D^3+D^2+1;

D^6+D^5+D^4+D^3+D^2+1;

D^6+D^5+D^4+D^3+D+1; или

D^6+D^4+D^2+D+1; и

интерфейс вывода, выполненный с возможностью выводить полярно-декодированную битовую последовательность.

46. Устройство для декодирования, содержащее:

интерфейс ввода, выполненный с возможностью получать последовательность, подлежащую декодированию;

логическую схему, выполненную с возможностью выполнять полярное декодирование последовательности, подлежащей декодированию, на основании полинома циклического избыточного кода (CRC), для получения полярно-декодируемой битовой последовательности, в котором полярно-декодируемая битовая последовательность содержит L CRC биты и А информационные биты, L и А являются положительными целыми числами, L = 6, и CRC полином представляет собой: D^6+D^5+1; и

интерфейс вывода, выполненный с возможностью выводить полярно-декодированную битовую последовательность.

47. Устройство по п. 45 или 46, в котором L CRC биты в последовательности, подлежащей декодированию, расположены после А информационных бит.

48. Машиночитаемый носитель данных, в котором носитель выполнен с возможностью хранить компьютерную программу, и при запуске устройством связи выполняют способ по любому из пп. 29-32.

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| ЗЕРНОКОРМОУБОРОЧНЫЙ КОМБАЙН | 1993 |

|

RU2075918C1 |

| CN 107040262 A, 11.08.2017 | |||

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ | 2008 |

|

RU2448417C2 |

| СПОСОБЫ И УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ CRC ДЛЯ МНОЖЕСТВА КОДОВЫХ БЛОКОВ В СИСТЕМЕ СВЯЗИ | 2008 |

|

RU2435297C2 |

Авторы

Даты

2020-11-09—Публикация

2018-05-04—Подача