Область техники, к которой относится изобретение

Настоящее изобретение относится к области связи и, в частности, к способу и устройству для отправки данных, способу и устройству для обработки данных, устройству сетевой стороны и терминалу.

Уровень техники

В системе долгосрочного развития (LTE) система предшествующего уровня техники физический широковещательный канал (PBCH) передается каждые 10 мс в течение периода 40 мс (то есть 4 раза в течение 40 мс). Пользовательское оборудование (UE) определяет, какая передача выполняется, основываясь на предположении версии избыточности, используемой для базовой станции для выполнения канального кодирования по PBCH.

Когда базовая станция LTE выполняет канальное кодирование по PBCH, для представления количества (1, или 2 или 4) антенных портов используются различные маски (например, маски CRC) при выполнении циклического контроля избыточности (CRC) по PBCH. В предшествующем уровне техники, когда базовая станция LTE передает PBCH с использованием нескольких антенн, используется способ разнесения передачи.

В течение периода передачи 80 мс физического широковещательного канала для технологии доступа новой радиосвязи (NR-PBCH) в системе мобильной связи 5-го поколения (5G) NR-PBCH может передаваться несколько раз, в то время как UE (терминал) не знает, какая передача выполняется. Поэтому необходимо предусмотреть определенный способ, позволяющий UE узнавать, какая передача выполняется. В будущем базовая станция может передавать NR-PBCH с использованием одной антенны или нескольких антенн; и базовая станция может передавать NR-PBCH, используя один луч или несколько лучей. Таким образом, UE необходимо знать количество антенн (количество антенных портов) и состояние луча, чтобы лучше принимать канал.

В настоящее время для решения вышеизложенной проблемы в 5G еще не было предложено эффективного решения.

Раскрытие сущности изобретения

В вариантах осуществления настоящего изобретения предусмотрены способ и устройство для отправки данных, способ и устройство для обработки данных, устройство сетевой стороны и терминал для того, чтобы по меньшей мере решить проблему уровня техники, связанную с тем, что терминал не может определить, в какой передаче принятые данные передаются сетевой стороной.

Способ отправки данных предусмотрен в варианте осуществления настоящего изобретения. Способ включает в себя: выполнение первой заданной обработки над данными, подлежащими передаче, для получения первого результата обработки; объединение первого результата обработки с данными, подлежащими передаче, для получения сцепленных данных; выполнение второй заданной обработки над сцепленными данными для получения обработанных данных, где обработанные данные включают в себя множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных; и передачу сегмента данных в обработанных данных, который соответствует текущей передаче данных устройства сетевой стороны.

Способ обработки данных предусмотрен в варианте осуществления настоящего изобретения. Способ включает в себя: прием данных, отправленных устройством сетевой стороны, где данные представляют собой сегмент данных среди данных, полученных из предварительно обработанных данных, которые должны быть переданы устройством сетевой стороны; и определение, согласно заданному соответствию между сегментами данных и количеством передач данных и принятых данных, количества передач данных, соответствующих принятым данным.

Устройство обработки данных предусмотрено в варианте осуществления настоящего изобретения. Устройство включает в себя модуль приема и модуль определения. Модуль приема выполнен с возможностью приема данных, отправленных устройством сетевой стороны, где данные представляют собой сегмент данных среди данных, полученных из предварительно обработанных данных, которые должны быть переданы устройством сетевой стороны. Модуль определения выполнен с возможностью определения, согласно заданному соответствию между сегментами данных и количеством передач данных и принятых данных, количества передач данных, соответствующих принятым данным.

Устройство сетевой стороны предусмотрено в варианте осуществления настоящего изобретения и включает в себя процессор и память. Процессор выполнен с возможностью выполнения первой заданной обработки над данными, подлежащими передаче, для получения первого результата обработки; объединения первого результата обработки с данными, подлежащими передаче, для получения сцепленных данных; выполнения второй заданной обработки над сцепленными данными для получения обработанных данных; и передачи сегмента данных в обработанных данных, соответствующего текущей передаче данных устройства сетевой стороны, где обработанные данные включают в себя множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных. Память подключена к процессору.

Терминал предусмотрен в варианте осуществления настоящего изобретения и включает в себя процессор и память. Процессор выполнен с возможностью приема данных, отправленных устройством сетевой стороны, и определения, согласно заданному соответствию между сегментами данных и количеством передач данных и принятых данных, количества передач данных, соответствующих принятым данным, где данные представляют собой сегмент данных среди данных, полученных из предварительно обработанных данных, которые должны быть переданы устройством сетевой стороны. Память подключена к процессору.

Другой вариант осуществления настоящего изобретения дополнительно предусматривает носитель информации. Носитель информации включает в себя хранящиеся на нем программы, которые при их исполнении выполняют способ согласно любому из описанных выше вариантов осуществления.

Другой вариант осуществления настоящего изобретения дополнительно предусматривает процессор. Процессор выполнен с возможностью исполнения программ, которые при их исполнении выполняют способ согласно любому из описанных выше вариантов осуществления.

Согласно вариантам осуществления первая заданная обработка выполняется над данными, подлежащими передаче, для получения первого результата обработки, и первый результат обработки объединяется с данными, подлежащими передаче. Вторая заданная обработка выполняется над сцепленными данными. Обработанные данные включают в себя множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных. Передается сегмент данных, соответствующих текущей передаче данных устройства сетевой стороны. То есть каждый сегмент данных соответствует передаче данных, так что терминал может определить количество передач, соответствующих данным после того, как терминал примет данные, отправленные устройством сетевой стороны, и дополнительно определить количество передач данных, переданных устройством сетевой стороны. Таким образом, может быть решена проблема, заключающаяся в том, что терминал не может определить, какая из передач принятых данных передается сетевой стороной.

Краткое описание чертежей

Чертежи, описанные в данном документе, используются для обеспечения дальнейшего понимания настоящего изобретения и составляют часть настоящей заявки. В настоящем изобретении примерные варианты осуществления и их описания используются для пояснения настоящего изобретения, а не для ограничения настоящего изобретения каким-либо ненадлежащим образом. На чертежах:

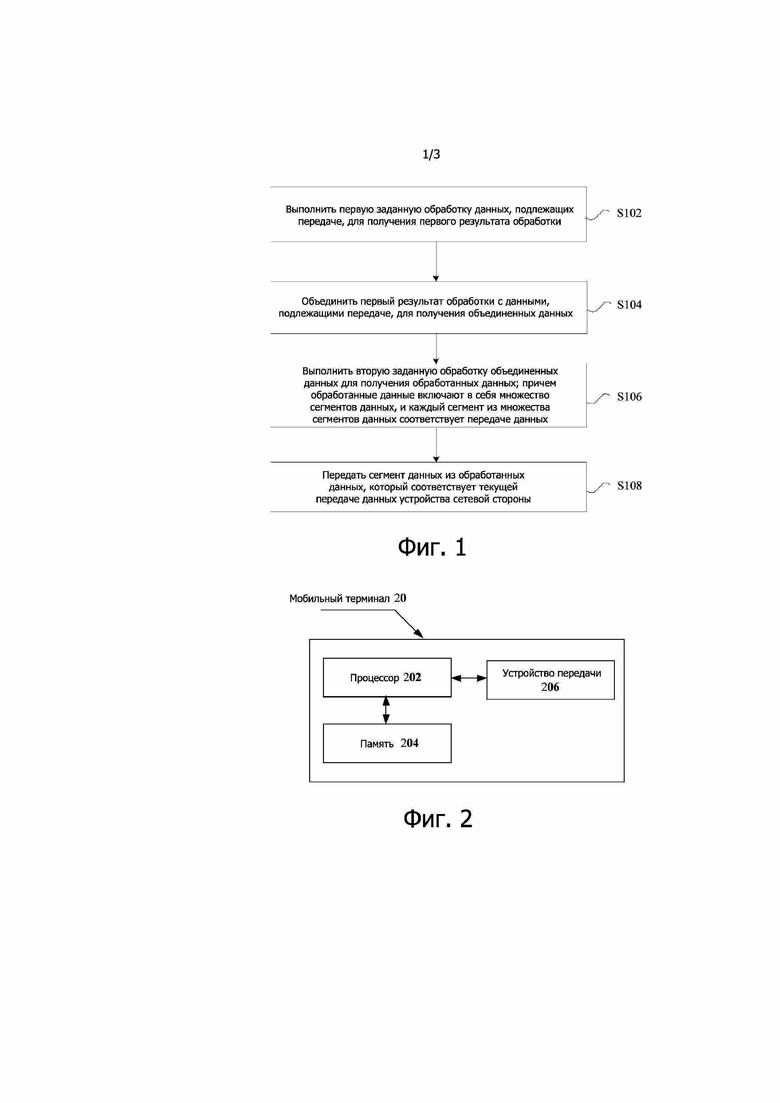

фиг.1 – блок-схема последовательности операций способа отправки данных согласно варианту осуществления настоящего изобретения;

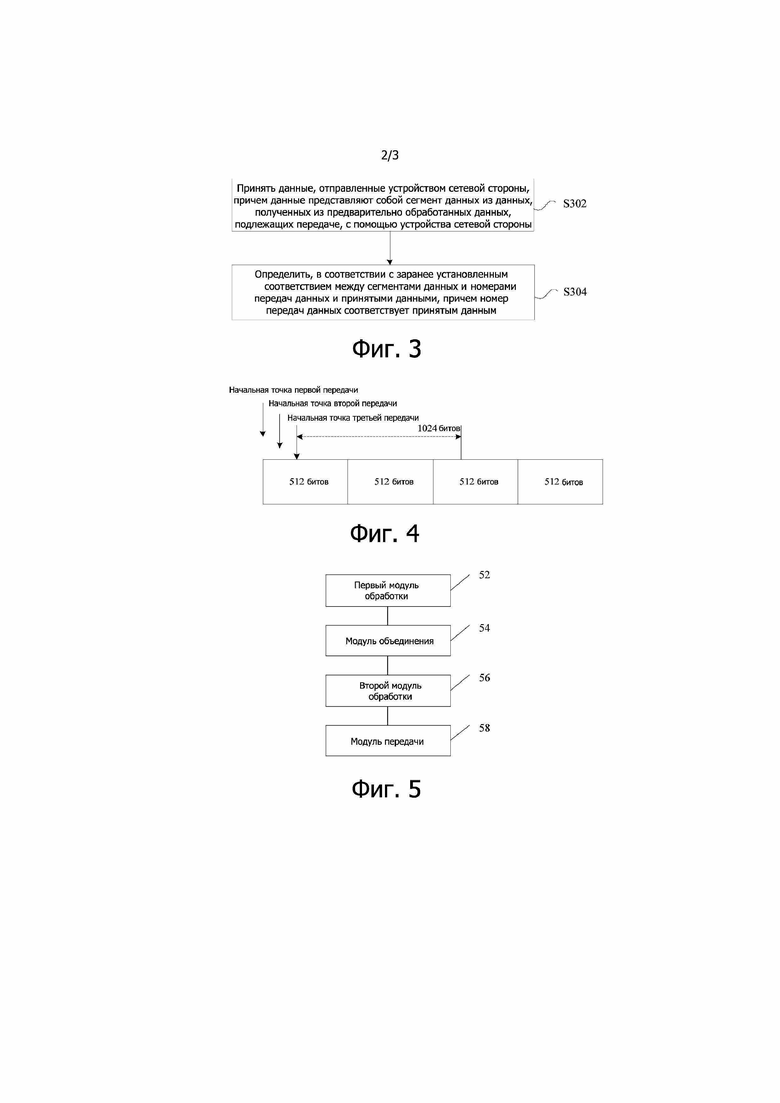

фиг.2 – структурная блок-схема аппаратных средств мобильного терминала для способа обработки данных согласно варианту осуществления настоящего изобретения;

фиг.3 – блок-схема последовательности операций способа обработки данных согласно варианту осуществления настоящего изобретения;

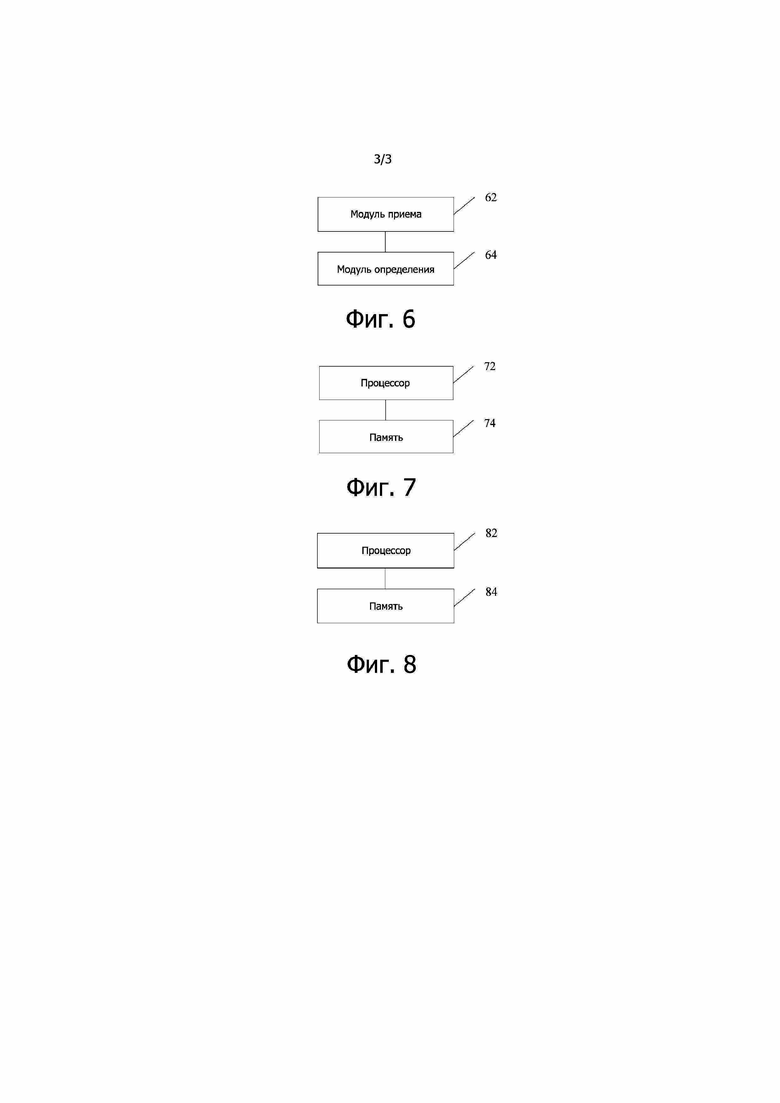

фиг.4 – схематичное представление извлеченных битов согласно варианту 1 осуществления настоящего изобретения;

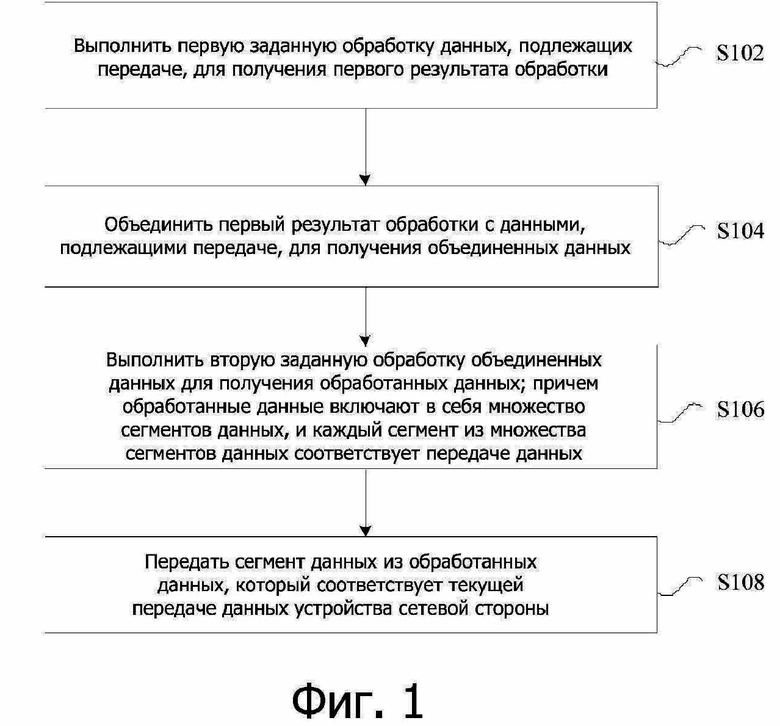

фиг.5 – структурная блок-схема устройства для отправки данных согласно варианту осуществления настоящего изобретения;

фиг.6 – структурная блок-схема устройства обработки данных согласно варианту осуществления настоящего изобретения;

фиг.7 – структурная блок-схема устройства сетевой стороны согласно варианту осуществления настоящего изобретения; и

фиг.8 – структурная блок-схема терминала согласно варианту осуществления настоящего изобретения.

Осуществление изобретения

Настоящее изобретение будет подробно описано ниже со ссылкой на чертежи совместно с вариантами осуществления. Следует отметить, что, если не возникает противоречий, в настоящей заявке варианты осуществления и признаки, представленные в них, могут быть объединены друг с другом.

Следует отметить, что термины "первый", "второй" и т.п., используемые в описании, формуле изобретения и на чертежах настоящего изобретения, используются для различения аналогичных объектов и не обязательно используются для описания конкретной очередности или последовательности.

Вариант 1 осуществления

Вариант осуществления настоящего изобретения предусматривает способ отправки данных. На фиг.1 показана блок-схема последовательности операций способа отправки данных согласно варианту осуществления настоящего изобретения. Как показано на фиг.1, способ включает в себя этапы, описанные ниже.

На этапе S102 выполняется первая заданная обработка над данными, подлежащими передаче, для получения первого результата обработки.

На этапе S104 первый результат обработки объединяется с данными, подлежащими передаче, для получения сцепленных данных.

На этапе S106 вторая заданная обработка выполняется над сцепленными данными для получения обработанных данных.

Обработанные данные включают в себя множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных.

На этапе S108 передается сегмент данных в обработанных данных, который соответствует текущей передаче данных устройства сетевой стороны.

Посредством вышеупомянутых этапов выполняется первая заданная обработка над данными, подлежащими передаче, для получения первого результата обработки, и первый результат обработки объединяется с данными, подлежащими передаче. Вторая заданная обработка выполняется над сцепленными данными. Обработанные данные включают в себя множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных. Передается сегмент данных, соответствующих текущей передаче данных устройства сетевой стороны. То есть каждый сегмент данных соответствует передаче данных, так что терминал может определить количество передач, соответствующих данным после того, как терминал примет данные, отправленные устройством сетевой стороны, и дополнительно определить количество передач данных, переданных устройством сетевой стороны. Таким образом, может быть решена проблема, заключающаяся в том, что терминал не может определить, в какой передаче принятые данные передаются сетевой стороной.

В других вариантах осуществления этап S106 может включать в себя: выполнение канального кодирования сцепленных данных для получения кодированных данных; повторение кодированных данных N раз для получения повторных данных, где N является положительным целым числом; и скремблирование повторных данных с использованием указанного идентификатора для получения скремблированных данных.

Следует отметить, что указанный выше идентификатор может, но не обязательно, включать в себя по меньшей мере одно из: идентификатора луча, идентификатора соты или набора идентификаторов терминала.

Следует отметить, что канальное кодирование выполняется над сцепленными данными по меньшей мере одним из следующих способов кодирования: полярный код, код с низкой плотностью проверок на четность и сверточный код с задаваемой концевой комбинацией битов.

Следует отметить, что этап скремблирования повторных данных с использованием указанного идентификатора для получения скремблированных данных может включать в себя: выполнение операции исключающего "или" (XOR) над скремблированной последовательностью, выработанной с использованием указанного идентификатора и повторных данных, для получения скремблированных данных.

Следует отметить, что скремблированная последовательность включает в себя по меньшей мере одно из: кода Голда, M-последовательности или последовательности Задова-Чу (ZC).

Следует отметить, что код Голда является псевдослучайным кодом, полученным из M-последовательности, и образуется путем сложения по модулю 2 для перестановки пары M-последовательности. Термин "М-последовательность" является сокращенным наименованием линейной последовательности сдвигового регистра максимальной длины и представляет собой псевдослучайную последовательность, псевдошумовой код или псевдослучайный код. ZC-последовательность представляет собой последовательность Задова-Чу.

В других вариантах осуществления вышеупомянутый этап S102 может включать в себя: выполнение циклического контроля избыточности над данным, подлежащими передаче, для получения первого результата проверки; и выполнение по меньшей мере одной из следующих операций над первым результатом проверки для получения первого результата обработки: выполнение заданной операции над первым результатом проверки с использованием маски для представления числа антенных портов; и выполнение операции XOR над временным идентификатором соты радиосети и первым результатом проверки. Этап выполнения операции XOR над временным идентификатором соты радиосети и первым результатом проверки включает в себя: выполнение операции XOR над 16-битовым временным идентификатором соты радиосети и последними 16 битами в 19 битах первого результата проверки для получения нового результата проверки. Так как эти длины являются разными, при выполнении операции последние 16 битов в 19 битах первого результата проверки выбираются для выполнения операции над 16-битовым временным идентификатором соты радиосети для получения нового результата проверки.

Следует отметить, что в случае 8 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X8 +X7 +X4 +X3 +X +1, g = X8 +X2 +X +1, g = X8 +X4 +X3 +X +1 или g = X8 +X4 +X3 +X2 +1; в случае 16 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X16 + X12 + X5 + 1, g = X16 + X2 + X + 1 или g = X16 + X14 + X + 1; в случае 17 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X17 + X3 + 1, g = X17 + X12 + X11 + X6 + X4 + X + 1 или g = X17 + X13 + X11 + X10 + X7 + X5 + X4 + X3+ X + 1; в случае 18 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X18 + X5 + X2 + X + 1, g = X18 + X16 + X15 + X13 + X8 + X5 + X4 + X3 + X2 + X + 1 или g = X18 + X16 + X11 + X10 + X9 + X8 + X6 + X5 + X4 + X + 1; в случае 19 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X19 + X5 + X2 + X + 1, g = X19 + X16 + X8 + X5 + X4 + X3 + X2 + X + 1 или g = X19 + X12 + X9 + X8 + X6 + X5 + X4 + X2 + 1; в случае 20 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X20 + X3 +1, g = X20 + X16 + X9 + X4 + X3 + X2 +1 или g = X20 + X19 + X18 + X14 + X6 + X2 +X +1; в случае 21 контрольного бита, используемого для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X21 + X2 +1, g = X21 +X20 +X13 +X11 +X7 +X4 +X3 +1 или g = X21 +X20 +X18 +X16 +X14 +X13 +X10 +X9 +X7 +X3 +1; в случае 22 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X22 + X +1; в случае 23 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X23 + X5 +1; в случае 24 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X24 + X4 + X3 + X +1, g = X24 + X23 + X6 + X5 + X + 1 или g = X24 + X23 + X18 + X17 + X14 + X11 + X10 + X7 + X6 + X5 + X4 + X3 +X+1; и в случае 32 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X32 +X7 +X5 +X3 +X2 +X +1, g = X32 +X29 +X18 +X14 +X3 +1 или g = X32 +X14 +X12 +X10 +X9 +X8 +X4 +X3 +X +1. Показатель степени X используется для указания контрольного бита, используемого при выполнении циклического контроля избыточности.

Следует отметить, что в случае, когда антенный порт является портом с одной антенной, маска включает в себя число L_CRC двоичных битов "0". В случае, когда антенный порт является портом с 2-мя антеннами, маска включает в себя число L_CRC двоичных битов "1". В случае, когда антенный порт является портом с 4-мя антеннами, маска включает в себя: число mod(L_CRC/2) двоичных цепочек "01" и число mod(L_CRC, 2) двоичных битов "0". В случае, когда антенный порт является портом с 8-ю антеннами, маска включает в себя: число mod(L_CRC/2) двоичных цепочек "10" и число mod(L_CRC, 2) двоичных битов "1". В случае, когда антенный порт является портом с 16-ю антеннами, маска включает в себя одно из: числа mod(L_CRC/4) двоичных цепочек "0110" и числа mod(L_CRC, 4) двоичных битов "1"; двоичных цепочек floor(L_CRC/4) "0110" и множества битов от первого бита до mod(L_CRC, 4)-го бита двоичных цепочек floor(L_CRC/4) "0110"; или двоичных цепочек floor(L_CRC/4) "0110" и множества битов от последнего бита до mod(L_CRC, 4)-го бита из последнего бита двоичных цепочек floor(L_CRC/4) "0110". В случае, когда антенный порт является портом с 32-мя антеннами, маска включает в себя одно из: числа mod(L_CRC/4) двоичных цепочек "1001" и числа mod(L_CRC, 4) двоичных битов "0"; двоичных цепочек floor(L_CRC/4) "1001" и множества битов от первого бита до mod(L_CRC, 4)-го бита двоичных цепочек floor(L_CRC/4) "1001"; или двоичных цепочек floor(L_CRC/4) "1001" и множества битов от последнего бита до mod(L_CRC, 4)-го бита из последнего бита двоичных цепочек floor(L_CRC/4) "1001". L_CRC включает в себя по меньшей мере одно из: количества битов циклического контроля избыточности, количества битов идентификатора соты, количества битов идентификатора луча, количества битов временного идентификатора соты радиосети или количества битов циклического контроля избыточности минус количество резервных битов. Количество резервных битов является любым целым числом от 0 до 16, floor() представляет собой операцию округления в сторону уменьшения, mod(L_CRC, 2) представляет собой операцию по модулю 2 над L_CRC, и mod(L_CRC, 4) представляет собой операцию по модулю 4 над L_CRC.

Следует отметить, что этап выполнения заданной операции над первым результатом проверки с использованием маски для представления числа антенных портов включает в себя по меньшей мере одно из: выполнения операции XOR над маской и первым результатом проверки или выполнения операции сложения по модулю 2 над маской и первым результатом проверки.

Следует отметить, что этап выполнения операции XOR над временным идентификатором соты радиосети и первым результатом проверки включает в себя по меньшей мере одно из: в случае, когда количество битов временного идентификатора соты радиосети меньше количества битов первого результата проверки, добавления заданного количества двоичных битов "0" к начальной или конечной части временного идентификатора соты радиосети для получения первого временного идентификатора соты радиосети, и выполнение операции XOR над первым временным идентификатором соты радиосети и первым результатом проверки; или в случае, когда количество битов временного идентификатора соты радиосети больше, чем количество битов первого результата проверки, добавления заданного количества двоичных битов "0" к начальной или конечной части первого результата проверки для получения второго результата проверки, и выполнение операции XOR над временным идентификатором соты радиосети и вторым результатом проверки. Заданное количество имеет абсолютное значение разности между количеством битов временного идентификатора соты радиосети и количеством битов первого результата проверки.

В других вариантах осуществления вышеупомянутый этап S104 может включать в себя по меньшей мере одно из: размещения первого результата обработки перед данными, подлежащими передаче, для получения сцепленных данных; размещения первого результата обработки среди данных, подлежащих передаче, для получения сцепленных данных; или размещения первого результата обработки после данных, подлежащих передаче, для получения сцепленных данных. Каждые М битов данных, которые должны передаваться в данных, подлежащих передаче, вставляются с битом данных первого результата обработки, и все биты первого результата обработки вставляются в данные, подлежащие передаче, для получения сцепленных данных. M является натуральным числом.

Следует отметить, что по меньшей мере два сегмента данных в множестве сегментов данных имеют перекрывающиеся данные, или перекрывающиеся данные не существуют в множестве сегментов данных, и настоящее изобретение не ограничивается этим.

Следует отметить, что вышеупомянутые этапы могут быть выполнены устройством сетевой стороны, таким как базовая станция, но это не является ограничением.

Вариант 2 осуществления

Вариант осуществления способа, представленный вариантом 2 осуществления настоящей заявки, может быть выполнен в мобильном терминале, компьютерном терминале или в других подобных вычислительных устройствах. На фиг.2, в качестве примера способа, который должен выполняться в мобильном терминале, показана структурная блок-схема аппаратных средств мобильного терминала для способа обработки данных согласно варианту осуществления настоящего изобретения. Как показано на фиг.2, мобильный терминал 20 может включать в себя один или более (на фиг.1 показан только один) процессоров 202 (процессоры 202 могут включать в себя, но не ограничиваются этим, устройство обработки, такое как блок микроконтроллера (MCU) и программируемая пользователем вентильная матрица (FPGA)), память 204, выполненную с возможностью хранения данных, и передающее устройство 206, выполненное с возможностью реализации функции связи. Специалистам в данной области должно быть понятно, что структура, показанная на фиг.2, является просто иллюстративной и не предназначена для ограничения структуры электронного устройства, описанного выше. Например, мобильный терминал 20 может дополнительно включать в себя больше или меньше компонентов, чем показано на фиг. 2, или может иметь конфигурацию, отличную от конфигурации, показанной на фиг. 2.

Память 204 может быть с возможностью хранения программ прикладного программного обеспечения и модулей, таких как программные инструкции/модули, соответствующие способу обработки данных в вариантах осуществления настоящего изобретения. Процессор 202 исполняет программы и модули программного обеспечения, хранящиеся в памяти 204, для выполнения функций приложений и обработки данных, чтобы реализовать описанный выше способ. Память 204 может включать в себя быстродействующее оперативное запоминающее устройство и может дополнительно включать в себя энергонезависимую память, такую как одно или несколько магнитных запоминающих устройств, флэш-память или энергонезависимую твердотельную память другого типа. В некоторых примерах память 204 может дополнительно включать в себя запоминающие устройства, которые расположены удаленно по отношению к процессорам 202. Эти удаленные запоминающие устройства могут поддерживать связь с мобильным терминалом 20 через сеть. Примеры вышеупомянутой сети включают в себя, но не ограничиваются ими, Интернет, интранет, локальную сеть, сеть мобильной связи и их комбинацию.

Передающее устройство 206 выполнено с возможностью приема или отправки данных через сеть. Конкретные примеры такой сети, описанные выше, могут включать в себя радиосеть, предоставляемую поставщиком связи мобильного терминала 20. В одном примере передающее устройство 206 включает в себя контроллер сетевого интерфейса (NIC), который может быть подключен к другим сетевым устройствам через базовую станцию, и, таким образом, способно поддерживать связь с Интернетом. В одном примере передающее устройство 206 может быть радиочастотным (РЧ) модулем, который используется для связи с Интернетом посредством радиосвязи.

Вариант осуществления предусматривает способ обработки данных, который будет выполняться в мобильном терминале, описанном выше. На фиг.3 показана блок-схема последовательности операций способа обработки данных согласно варианту осуществления настоящего изобретения. Как показано на фиг.3, способ включает в себя этапы, описанные ниже.

На этапе S302 принимаются данные, отправленные устройством сетевой стороны. Данные представляют собой сегмент данных среди данных, полученных из предварительно обработанных данных, которые должны быть переданы устройством сетевой стороны.

На этапе S304 определяется количество передач данных, соответствующих принятым данным, согласно заданному соответствию между сегментами данных и количеством передач данных и принятых данных.

Посредством выполнения вышеупомянутых этапов количество передач данных, соответствующих принятым данным, определяется в соответствии с предварительно установленным соответствием между сегментами данных и количеством передач данных, так что терминал знает, какая из передач принятых данных передается сетевой стороной, тем самым решая проблему, заключающуюся в том, что терминал не может определить, что принятые данные переданы сетевой стороной, на которой осуществляется передача.

Следует отметить, что соответствие может быть задано между устройством сетевой стороны и терминалом и может быть также предварительно сконфигурировано устройством сетевой стороны для терминала, но это не является ограничением.

Следует отметить, что соответствие может включать в себя: соответствие между начальными точками сегментов данных в предварительно обработанных данных и номерами передач данных.

В других вариантах осуществления вышеупомянутый этап S304 может включать в себя то, что получается начальная позиция принятых данных в предварительно обработанных данных; и соответствие находится в соответствии с начальной позицией для количества передач данных, соответствующих начальной позиции.

Следует отметить, что вышеупомянутые этапы может, но необязательно, выполнить терминал.

Из описания варианта осуществления, описанного выше, для специалистов в данной области техники будет очевидно, что способ в варианте осуществления, описанном выше, может быть реализован с помощью программного обеспечения совместно с необходимой аппаратной платформой общего назначения или, разумеется, может быть реализован с помощью аппаратных средств. Исходя из этого понимания, технические решения, предусмотренные вариантами осуществления настоящего изобретения, вносящего в значительной степени или частично вклад в предшествующий уровень техники, могут быть воплощены в виде программного продукта. Компьютерный программный продукт хранится на носителе информации (таком как ПЗУ/ОЗУ, магнитный диск или оптический диск) и включает в себя несколько инструкций для обеспечения возможности терминальному устройству (которым может быть мобильный телефон, компьютер, сервер, сетевое устройство или тому подобное) выполнять способ согласно каждому варианту осуществления настоящего изобретения.

Для лучшего понимания вариантов осуществления настоящего изобретения настоящее изобретение будет дополнительно описано ниже совместно со следующими вариантами осуществления.

Вариант 1 осуществления

Предполагается, что длина передаваемых данных составляет 23 бита, длина CRC равна 19 битам, полярный код используется для выполнения кодирования, длина материнского кода полярного кода составляет 512 битов, для передачи используется одна антенна, после кодирования выполняется 4 повторения (то есть 4 * 512 = 2048 битов), необходимо восемь передач, и в текущий момент времени выполняется 3-я передача. Затем передатчик выполняет следующие операции. 19-битовом циклический контроль избыточности над 23-битовыми данными, подлежащими передаче, выполняется с использованием следующий формулы образующего полинома для получения 19-битового результата проверки:

g = X19 + X5 + X2 + X + 1.

Затем выполняется операция XOR над 19-битовым результатом проверки с использованием маски для представления числа антенных портов для получения нового результата проверки. Так как для передачи используется одна антенна, 19-битовый результат проверки остается неизменным.

Затем новый результат проверки объединяется с данными, подлежащими передаче, битами, подлежащими передаче, (19-битовый результат проверки размещается после 23-битовых данных, подлежащих передаче).

Затем выполняется кодирование полярным кодом над новыми 42-битовыми данными с кодовой скоростью 1/12, и получаются 512-битовые кодированные данные.

512-битовые кодированные данные повторяются 4 раза для получения 2048-битовых данных.

2048-битовые данные скремблируются с использованием идентификатора луча для получения скремблированных 2048-битовых данных.

Извлекается и передается третий сегмент данных вышеупомянутых скремблированных данных.

В скремблированных данных начальной точкой каждого сегмента является mod(L_Mother * Repeat, Num_Seg) + (Seg_ID - 1) * floor(L_Mother / Num_Seg). L_Mother является длиной материнского кода, Num_Seg является общим количеством передач, и Seg_ID является текущим количеством передач. Порядковый номер начального бита третьей передачи представляет собой mod(512 * 4, 8) + (3 - 1) * floor(512 / 8) = 0 + 2 * 64 = 128, то есть 128-й бит (порядковый номер начинается с 0; и диапазон номеров представляет собой 0, 1, 2, 3,…, 2046, 2047). Количество битов, передаваемых каждый раз, составляет 512, или 1024 или 1536. На фиг.4 показано схематичное представление извлеченных битов согласно варианту 1 осуществления настоящего изобретения. Извлеченные биты показаны на фиг.4.

Вариант 2 осуществления

Предполагается, что длина передаваемых данных составляет 22 бита, длина CRC равна 20 битам, полярный код используется для выполнения кодирования, длина материнского кода полярного кода составляет 512 битов, для передачи используются восемь антенных портов, после кодирования выполняется 4 повторения (то есть, длина равна 4 * 512 = 2048 битов), необходимо восемь передач, и в текущий момент времени выполняется 3-я передача. Затем передатчик выполняет следующие операции. 20-битовый циклический контроль избыточности выполняется над 22-битовыми данными, подлежащими передаче, с использованием следующий формулы образующего полинома для получения 20-битового результата проверки:

g = X20 + X16 + X9 + X4 + X3 + X2 +1.

Затем выполняется операция XOR над 20-битовым результатом проверки с использованием маски для представления числа антенных портов для получения нового результата проверки. Так как для передачи используются восемь антенн, операция XOR должна выполняться над 20-битовым результатом проверки с использованием маски [1, 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0, 1, 0] для получения нового 20-битового результата проверки.

Затем новый 20-битовый результат проверки объединяется с данными, подлежащими передаче, битами, подлежащими передаче, (20-битовый результат проверки находится в начальной части 22-битовых данных, подлежащих передаче).

Затем выполняется кодирование полярным кодом над новыми 42-битовыми данными с кодовой скоростью 1/12, и получаются 512-битовые кодированные данные.

512-битовые кодированные данные повторяются 4 раза для получения 2048-битовых данных.

2048-битовые данные скремблируются с использованием идентификатора луча для получения скремблированных 2048-битовых данных.

Извлекается и передается третий сегмент данных вышеупомянутых скремблированных данных.

В скремблированных данных начальной точкой каждого сегмента является mod(L_Mother * Repeat, Num_Seg) + (Seg_ID - 1) * floor(L_Mother / Num_Seg). L_Mother является длиной материнского кода, Num_Seg является общим количеством передач, и Seg_ID является текущим количеством передач. Порядковый номер начального бита третьей передачи представляет собой mod(512 * 4, 8) + (3 - 1) * floor(512 / 8) = 0 + 2 * 64 = 128, то есть 128-й бит (порядковый номер начинается с 0; и диапазон номеров представляет собой 0, 1, 2, 3,…, 2046, 2047). Количество битов, передаваемых каждый раз, составляет 512, или 1024 или 1536. Извлеченные биты показаны на фиг.4.

Вариант 3 осуществления

Предполагается, что длина передаваемых данных составляет 23 бита, длина CRC равна 19 битам, полярный код используется для выполнения кодирования, длина материнского кода полярного кода составляет 512 битов, для передачи используется одна антенна, после кодирования выполняются 4 повторения (то есть 4 * 512 = 2048 битов), необходимо восемь передач, и в текущий момент времени выполняется 3-я передача. Затем передатчик выполняет следующие операции. 19-битовом циклический контроль избыточности выполняется над 23-битовыми данными, подлежащими передаче, с использованием следующий формулы образующего полинома для получения 19-битового результата проверки:

g = X19 + X5 + X2 + X + 1.

Затем выполняется операция XOR над 19-битовым результатом проверки с использованием маски для представления числа антенных портов для получения нового результата проверки. Так как для передачи используется одна антенна, 19-битовый результат проверки остается неизменным.

Затем выполняется операция XOR над 16-битовым временным идентификатором соты радиосети и 19-битовым результатом проверки. Так как длины являются разными, в операции последние 16 битов в 19-битовом результате проверки выбираются для операции, чтобы получить новый результата проверки.

В дополнение к этому, операция XOR может выполняться над старшими 3-мя битами 19-битового результата проверки и идентификатором луча.

Затем новый результат проверки объединяется с данными, подлежащими передаче, битами, подлежащими передаче, (19-битовый результат проверки размещается после 23-битовых данных, подлежащих передаче).

Затем выполняется кодирование полярным кодом над новыми 42-битовыми данными с кодовой скоростью 1/12, и получаются 512-битовые кодированные данные.

512-битовые кодированные данные повторяются 4 раза для получения 2048-битовых данных.

2048-битовые данные скремблируются с использованием идентификатора луча для получения скремблированных 2048-битовых данных.

Извлекается и передается третий сегмент данных вышеупомянутых скремблированных данных.

В скремблированных данных начальной точкой каждого сегмента является mod(L_Mother * Repeat, Num_Seg) + (Seg_ID - 1) * floor(L_Mother / Num_Seg). L_Mother является длиной материнского кода, Num_Seg является общим количеством передач, и Seg_ID является текущим количеством передач. Порядковый номер начального бита третьей передачи представляет собой mod(512 * 4, 8) + (3 - 1) * floor(512 / 8) = 0 + 2 * 64 = 128, то есть 128-й бит (порядковый номер начинается с 0; и диапазон номеров представляет собой 0, 1, 2, 3,…, 2046, 2047). Количество битов, передаваемых каждый раз, составляет 512, или 1024 или 1536. Извлеченные биты показаны на фиг.4.

Вариант 4 осуществления

Вариант осуществления дополнительно предусматривает устройство для отправки данных. Устройство выполнено с возможностью реализации приведенных выше вариантов осуществления. То, что было описано, повторяться не будет. Используемый ниже термин "модуль" может означать программное обеспечение, аппаратные средства или их комбинацию, способную реализовывать заданные функции. Устройство в варианте осуществления, описанном ниже, предпочтительно реализуется с помощью программного обеспечения, но также возможна и предполагается реализация с помощью аппаратных средств или с помощью комбинации программного обеспечения и аппаратных средств.

Следует отметить, что различные модули, включенные в устройство, могут быть реализованы процессором в устройстве сетевой стороны; или, разумеется, могут быть реализованы конкретной логической схемой. В процессе реализации процессор может быть центральным процессором (CPU), микропроцессором (MPU), процессором цифровых сигналов (DSP), программируемой пользователем вентильной матрицей (FPGA) и т.п.

На фиг.5 показана структурная блок-схема устройства для отправки данных согласно варианту осуществления настоящего изобретения. Как показано на фиг.5, устройство включает в себя первый модуль 52 обработки, модуль 54 объединения, второй модуль 56 обработки и модуль 58 передачи (или передатчик).

Первый модуль 52 обработки выполнен с возможностью выполнения первой заданной обработки над данными, подлежащими передаче, для получения первого результата обработки.

Модуль 54 объединения подключен к первому модулю 52 обработки и выполнен с возможностью объединения первого результата обработки с данными, подлежащими передаче, для получения сцепленных данных.

Второй модуль 56 обработки подключен к модулю 54 объединения и выполнен с возможностью выполнения второй заданной обработки над сцепленными данными для получения обработанных данных. Обработанные данные включают в себя множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных. В некоторых вариантах осуществления первый модуль 52 обработки, модуль 54 объединения, второй модуль 56 обработки могут совместно упоминаться как процессор.

Модуль 58 передачи подключен ко второму модулю 56 обработки и выполнен с возможностью передачи сегмента данных в обработанных данных, соответствующего текущей передаче данных устройства сетевой стороны.

Посредством вышеупомянутого устройства выполняется первая заданная обработка над данными, подлежащими передаче, для получения первого результата обработки, и первый результат обработки объединяется с данными, подлежащими передаче. Вторая заданная обработка выполняется над сцепленными данными. Обработанные данные включают в себя множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных. Передается сегмент данных, соответствующих текущей передаче данных устройства сетевой стороны. То есть каждый сегмент данных соответствует передаче данных, так что терминал может определить количество передач, соответствующих данным после того, как терминал примет данные, отправленные устройством сетевой стороны, и дополнительно определить количество передач данных, переданных устройством сетевой стороны. Таким образом, может быть решена проблема, заключающаяся в том, что терминал не может определить, в какой передаче принятые данные передаются сетевой стороной.

В других вариантах осуществления второй модуль 56 обработки может быть дополнительно выполнен с возможностью выполнения канального кодирования сцепленных данных для получения кодированных данных; повторения кодированных данных N раз для получения повторных данных; и скремблирования повторных данных с использованием указанного идентификатора для получения скремблированных данных. N является положительным целым числом.

Следует отметить, что указанный выше идентификатор может включать в себя, но не ограничиваться этим, по меньшей мере одно из: идентификатора луча, идентификатора соты или набора идентификаторов терминала.

Следует отметить, что второй модуль 56 обработки может быть дополнительно выполнен с возможностью выполнения канального кодирования сцепленных данных по меньшей мере одним из следующих способов кодирования: полярный код, код с низкой плотностью проверок на четность и сверточный код с задаваемой концевой комбинацией битов.

Следует отметить, что второй модуль 56 обработки может быть дополнительно выполнен с возможностью выполнения операции XOR над скремблированной последовательностью, выработанной с использованием указанного идентификатора и повторных данных, для получения скремблированных данных.

Следует отметить, что скремблированная последовательность включает в себя по меньшей мере одно из: кода Голда, M-последовательности или ZC-последовательности.

Следует отметить, что код Голда является псевдослучайным кодом, полученным из M-последовательности, и образуется путем сложения по модулю 2 для перестановки пары M-последовательности. Термин "М-последовательность" является сокращенным наименованием линейной последовательности сдвигового регистра максимальной длины и представляет собой псевдослучайную последовательность, псевдошумовой код или псевдослучайный код. ZC-последовательность представляет собой последовательность Задова-Чу.

В других вариантах осуществления первый модуль 52 обработки может быть дополнительно выполнен с возможностью выполнения циклического контроля избыточности над данными, подлежащими передаче, для получения первого результата проверки; и выполнения по меньшей мере одной из следующих операций над первым результатом проверки для получения первого результата обработки: выполнение заданной операции над первым результатом проверки с использованием маски для представления числа антенных портов; и выполнение операции XOR над временным идентификатором соты радиосети и первым результатом проверки.

Следует отметить, что в случае 8 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X8 +X7 +X4 +X3 +X +1, g = X8 +X2 +X +1, g = X8 +X4 +X3 +X +1 или g = X8 +X4 +X3 +X2 +1; в случае 16 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X16 + X12 + X5 + 1, g = X16 + X2 + X + 1 или g = X16 + X14 + X + 1; в случае 17 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X17 + X3 + 1, g = X17 + X12 + X11 + X6 + X4 + X + 1 или g = X17 + X13 + X11 + X10 + X7 + X5 + X4 + X3+ X + 1; в случае 18 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X18 + X5 + X2 + X + 1, g = X18 + X16 + X15 + X13 + X8 + X5 + X4 + X3 + X2 + X + 1 или g = X18 + X16 + X11 + X10 + X9 + X8 + X6 + X5 + X4 + X + 1; в случае 19 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X19 + X5 + X2 + X + 1, g = X19 + X16 + X8 + X5 + X4 + X3 + X2 + X + 1 или g = X19 + X12 + X9 + X8 + X6 + X5 + X4 + X2 + 1; в случае 20 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X20 + X3 +1, g = X20 + X16 + X9 + X4 + X3 + X2 +1 или g = X20 + X19 + X18 + X14 + X6 + X2 +X +1; в случае 21 контрольного бита, используемого для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X21 + X2 +1, g = X21 +X20 +X13 +X11 +X7 +X4 +X3 +1 или g = X21 +X20 +X18 +X16 +X14 +X13 +X10 +X9 +X7 +X3 +1; в случае 22 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X22 + X +1; в случае 23 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X23 + X5 +1; в случае 24 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X24 + X4 + X3 + X +1, g = X24 + X23 + X6 + X5 + X + 1 или g = X24 + X23 + X18 + X17 + X14 + X11 + X10 + X7 + X6 + X5 + X4 + X3 +X+1; и в случае 32 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X32 +X7 +X5 +X3 +X2 +X +1, g = X32 +X29 +X18 +X14 +X3 +1 или g = X32 +X14 +X12 +X10 +X9 +X8 +X4 +X3 +X +1. Показатель степени X используется для указания контрольного бита, используемого при выполнении циклического контроля избыточности.

Следует отметить, что в случае, когда антенный порт является портом с одной антенной, маска включает в себя число L_CRC двоичных битов "0". В случае, когда антенный порт является портом с 2-мя антеннами, маска включает в себя число L_CRC двоичных битов "1". В случае, когда антенный порт является портом с 4-мя антеннами, маска включает в себя: число mod(L_CRC/2) двоичных цепочек "01" и число mod(L_CRC, 2) двоичных битов "0". В случае, когда антенный порт является портом с 8-ю антеннами, маска включает в себя: число mod(L_CRC/2) двоичных цепочек "10" и число mod(L_CRC, 2) двоичных битов "1". В случае, когда антенный порт является портом с 16-ю антеннами, маска включает в себя одно из: числа mod(L_CRC/4) двоичных цепочек "0110" и числа mod(L_CRC, 4) двоичных битов "1"; двоичных цепочек floor(L_CRC/4) "0110" и множества битов от первого бита до mod(L_CRC, 4)-го бита двоичных цепочек floor(L_CRC/4) "0110"; или двоичных цепочек floor(L_CRC/4) "0110" и множества битов от последнего бита до mod(L_CRC, 4)-го бита из последнего бита двоичных цепочек floor(L_CRC/4) "0110". В случае, когда антенный порт является портом с 32-мя антеннами, маска включает в себя одно из: числа двоичных цепочек mod(L_CRC/4) "1001" и числа mod(L_CRC, 4) двоичных битов "0"; floor(L_CRC/4) двоичных цепочек "1001" и множества битов от первого бита до mod(L_CRC, 4)-го бита двоичных цепочек floor(L_CRC/4) "1001"; или двоичных цепочек floor(L_CRC/4) "1001" и множества битов от последнего бита до mod(L_CRC, 4)-го бита из последнего бита двоичных цепочек floor(L_CRC/4) "1001". L_CRC включает в себя по меньшей мере одно из: количества битов циклического контроля избыточности, количества битов идентификатора соты, количества битов идентификатора луча, количества битов временного идентификатора соты радиосети или количества битов циклического контроля избыточности минус количество резервных битов. Количество резервных битов является любым целым числом от 0 до 16, floor() представляет собой операцию округления в сторону уменьшения, mod(L_CRC, 2) представляет собой операцию по модулю 2 над L_CRC, и mod(L_CRC, 4) представляет собой операцию по модулю 4 над L_CRC.

Следует отметить, что первый модуль 52 обработки может быть дополнительно выполнен с возможностью выполнения по меньшей мере одной из следующих операций: выполнение операции XOR над маской и первым результатом проверки; и выполнение операции сложения по модулю 2 над маской и первым результатом проверки.

Следует отметить, что первый модуль 52 обработки может быть дополнительно выполнен с возможностью выполнения по меньшей мере одной из следующих операций: в случае, когда количество битов временного идентификатора соты радиосети меньше количества битов первого результата проверки, добавление заданного количества двоичных битов "0" к начальной или конечной части временного идентификатора соты радиосети для получения первого временного идентификатора соты радиосети, и выполнение операции XOR над первым временным идентификатором соты радиосети и первым результатом проверки; или в случае, когда количество битов временного идентификатора соты радиосети больше, чем количество битов первого результата проверки, добавление заданного количества двоичных битов "0" к начальной или конечной части первого результата проверки для получения второго результата проверки, и выполнение операции XOR над временным идентификатором соты радиосети и вторым результатом проверки. Заданное количество имеет абсолютное значение разности между количеством битов идентификатора соты радиосети и количеством битов первого результата проверки.

В других вариантах осуществления модуль 54 объединения может быть дополнительно выполнен с возможностью выполнения по меньшей мере одной из следующих операций: размещение первого результата обработки перед данными, подлежащими передаче, для получения сцепленных данных; размещение первого результата обработки среди данных, подлежащих передаче, для получения сцепленных данных; и размещение первого результата обработки после данных, подлежащих передаче, для получения сцепленных данных. Каждые М битов данных, которые должны передаваться в данных, подлежащих передаче, вставляются с битом данных первого результата обработки, и все биты первого результата обработки вставляются в данные, подлежащие передаче, для получения сцепленных данных. M является натуральным числом.

Следует отметить, что по меньшей мере два сегмента данных в множестве сегментов данных имеют перекрывающиеся данные, или перекрывающиеся данные не существуют в множестве сегментов данных, и настоящее изобретение не ограничивается этим.

Следует отметить, что вышеупомянутое устройство может, но необязательно, располагаться в устройстве сетевой стороны, таком как базовая станция.

Следует отметить, что различные модули, описанные выше, могут быть реализованы с помощью программного обеспечения или аппаратных средств. Реализация с помощью аппаратных средств может, но не обязательно, выполняться следующими способами: различные модули, описанные выше, расположены в одном и том же процессоре, или различные модули, описанные выше, расположены в их соответствующих процессорах в любой комбинации.

Вариант 4 осуществления

Вариант осуществления настоящего изобретения дополнительно предусматривает устройство обработки данных. Различные модули, включенные в устройство, могут быть реализованы процессором в терминале; или, разумеется, могут быть реализованы конкретной логической схемой. В процессе реализации процессор может быть центральным процессором (CPU), микропроцессором (MPU), процессором цифровых сигналов (DSP), программируемой пользователем вентильной матрицей (FPGA) и т.п.

На фиг.6 показана структурная блок-схема устройства обработки данных согласно варианту осуществления настоящего изобретения. Как показано на фиг.6, устройство включает в себя модуль 62 приема и модуль 64 определения.

Модуль 62 приема выполнен с возможностью приема данных, отправленных устройством сетевой стороны. Данные представляют собой сегмент данных среди данных, полученных из предварительно обработанных данных, которые должны быть переданы устройством сетевой стороны.

Модуль 64 определения подключен к модулю 62 приема и выполнен с возможностью определения, согласно заданному соответствию между сегментами данных и количеством передач данных и принятых данных, количества передач данных, соответствующих принятым данным.

Посредством вышеупомянутого устройства количество передач данных, соответствующих принятым данным, определяется в соответствии с предварительно установленным соответствием между сегментами данных и количеством передач данных, так что терминал знает количество передач принятых данных, переданных сетевой стороной, тем самым решая проблему, заключающуюся в том, что терминал не может определить, в какой передаче принятые данные передаются сетевой стороной.

Следует отметить, что соответствие может быть предварительно определено между устройством сетевой стороны и терминалом и может быть также предварительно сконфигурировано устройством сетевой стороны для терминала, но это не является ограничением.

Следует отметить, что соответствие может включать в себя: соответствие между начальными точками сегментов данных в предварительно обработанных данных и номерами передач данных.

В других вариантах осуществления модуль 54 определения может быть дополнительно выполнен с возможностью получения начальной позиции принятых данных в предварительно обработанных данных; и поиска, согласно начальной позиции, соответствия для количества передач данных, соответствующих начальной позиции.

Следует отметить, что вышеупомянутое устройство может, но необязательно, располагаться в терминале.

Следует отметить, что различные модули, описанные выше, могут быть реализованы с помощью программного обеспечения или аппаратных средств. Реализация с помощью аппаратных средств может, но не обязательно, выполняться следующими способами: различные модули, описанные выше, расположены в одном и том же процессоре, или различные модули, описанные выше, расположены в их соответствующих процессорах в любой комбинации.

Вариант 5 осуществления

Вариант осуществления настоящего изобретения дополнительно предусматривает устройство сетевой стороны. На фиг.7 показана структурная блок-схема устройства сетевой стороны согласно варианту осуществления настоящего изобретения. Как показано на фиг.7, устройство сетевой стороны включает в себя процессор 72 и память 74.

Процессор 72 выполнен с возможностью: выполнения первой предварительно определенной обработки над данными, подлежащими передаче, для получения первого результата обработки; объединения первого результата обработки с данными, подлежащими передаче, для получения сцепленных данных; выполнения второй заданной обработки над сцепленными данными для получения обработанных данных; и передачи сегмента данных в обработанных данных, соответствующего текущей передаче данных устройства сетевой стороны. Обработанные данные содержат множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных.

Память 74 подключена к процессору 72.

Посредством вышеупомянутого устройства сетевой стороны выполняется первая заданная обработка над данными, подлежащими передаче, для получения первого результата обработки, и первый результат обработки объединяется с данными, подлежащими передаче. Вторая заданная обработка выполняется над сцепленными данными. Обработанные данные включают в себя множество сегментов данных, и каждый сегмент из множества сегментов данных соответствует передаче данных. Передается сегмент данных, соответствующих текущей передаче данных устройства сетевой стороны. То есть каждый сегмент данных соответствует передаче данных, так что терминал может определить количество передач, соответствующих данным после того, как терминал примет данные, отправленные устройством сетевой стороны, и дополнительно определить количество передач данных, переданных устройством сетевой стороны. Таким образом, может быть решена проблема, заключающаяся в том, что терминал не может определить, в какой передаче принятые данные передаются сетевой стороной.

В других вариантах осуществления процессор 72 может быть дополнительно выполнен с возможностью выполнения канального кодирования сцепленных данных для получения кодированных данных; повторения кодированных данных N раз для получения повторных данных; и скремблирования повторных данных с использованием указанного идентификатора для получения скремблированных данных. N является положительным целым числом.

Следует отметить, что указанный выше идентификатор может, но необязательно, включать в себя по меньшей мере одно из: идентификатора луча, идентификатора соты или набора идентификаторов терминала.

Следует отметить, что процессор 72 может быть дополнительно выполнен с возможностью выполнения канального кодирования сцепленных данных по меньшей мере одним из следующих способов кодирования: полярный код, код с низкой плотностью проверок на четность и сверточный код с задаваемой концевой комбинацией битов.

Следует отметить, что процессор 72 может быть дополнительно выполнен с возможностью выполнения операции XOR над скремблированной последовательностью, выработанной с использованием указанного идентификатора и повторных данных, для получения скремблированных данных.

Следует отметить, что скремблированная последовательность включает в себя по меньшей мере одно из: кода Голда, M-последовательности или ZC-последовательности.

Следует отметить, что код Голда является псевдослучайным кодом, полученным из M-последовательности, и образуется путем сложения по модулю 2 для перестановки пары M-последовательности. Термин "М-последовательность" является сокращенным наименованием линейной последовательности сдвигового регистра максимальной длины и представляет собой псевдослучайную последовательность, псевдошумовой код или псевдослучайный код. ZC-последовательность представляет собой последовательность Задова-Чу.

В других вариантах осуществления процессор 72 может быть дополнительно выполнен с возможностью выполнения циклического контроля избыточности над данными, подлежащими передаче, для получения первого результата проверки; и выполнения по меньшей мере одной из следующих операций над первым результатом проверки для получения первого результата обработки: выполнение заданной операции над первым результатом проверки с использованием маски для представления числа антенных портов; и выполнение операции XOR над временным идентификатором соты радиосети и первым результатом проверки.

Следует отметить, что в случае 8 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X8 +X7 +X4 +X3 +X +1, g = X8 +X2 +X +1, g = X8 +X4 +X3 +X +1 или g = X8 +X4 +X3 +X2 +1; в случае 16 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X16 + X12 + X5 + 1, g = X16 + X2 + X + 1 или g = X16 + X14 + X + 1; в случае 17 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X17 + X3 + 1, g = X17 + X12 + X11 + X6 + X4 + X + 1 или g = X17 + X13 + X11 + X10 + X7 + X5 + X4 + X3+ X + 1; в случае 18 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X18 + X5 + X2 + X + 1, g = X18 + X16 + X15 + X13 + X8 + X5 + X4 + X3 + X2 + X + 1 или g = X18 + X16 + X11 + X10 + X9 + X8 + X6 + X5 + X4 + X + 1; в случае 19 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X19 + X5 + X2 + X + 1, g = X19 + X16 + X8 + X5 + X4 + X3 + X2 + X + 1 или g = X19 + X12 + X9 + X8 + X6 + X5 + X4 + X2 + 1; в случае 20 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X20 + X3 +1, g = X20 + X16 + X9 + X4 + X3 + X2 +1 или g = X20 + X19 + X18 + X14 + X6 + X2 +X +1; в случае 21 контрольного бита, используемого для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X21 + X2 +1, g = X21 +X20 +X13 +X11 +X7 +X4 +X3 +1 или g = X21 +X20 +X18 +X16 +X14 +X13 +X10 +X9 +X7 +X3 +1; в случае 22 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X22 + X +1; в случае 23 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X23 + X5 +1; в случае 24 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X24 + X4 + X3 + X +1, g = X24 + X23 + X6 + X5 + X + 1 или g = X24 + X23 + X18 + X17 + X14 + X11 + X10 + X7 + X6 + X5 + X4 + X3 +X+1; и в случае 32 контрольных битов, используемых для циклического контроля избыточности, образующий полином g, используемый при выполнении циклического контроля избыточности, включает в себя по меньшей мере одно из: g = X32 +X7 +X5 +X3 +X2 +X +1, g = X32 +X29 +X18 +X14 +X3 +1 или g = X32 +X14 +X12 +X10 +X9 +X8 +X4 +X3 +X +1. Показатель степени X используется для указания контрольного бита, используемого при выполнении циклического контроля избыточности.

Следует отметить, что в случае, когда антенный порт является портом с одной антенной, маска включает в себя число L_CRC двоичных битов "0". В случае, когда антенный порт является портом с 2-мя антеннами, маска включает в себя число L_CRC двоичных битов "1". В случае, когда антенный порт является портом с 4-мя антеннами, маска включает в себя: число mod(L_CRC/2) двоичных цепочек "01" и число mod(L_CRC, 2) двоичных битов "0". В случае, когда антенный порт является портом с 8-ю антеннами, маска включает в себя: число mod(L_CRC/2) двоичных цепочек "10" и число mod(L_CRC, 2) двоичных битов "1". В случае, когда антенный порт является портом с 16-ю антеннами, маска включает в себя одно из: числа mod(L_CRC/4) двоичных цепочек "0110" и числа mod(L_CRC, 4) двоичных битов "1"; двоичных цепочек floor(L_CRC/4) "0110" и множества битов от первого бита до mod(L_CRC, 4)-го бита двоичных цепочек floor(L_CRC/4) "0110"; или двоичных цепочек floor(L_CRC/4) "0110" и множества битов от последнего бита до mod(L_CRC, 4)-го бита из последнего бита двоичных цепочек floor(L_CRC/4) "0110". В случае, когда антенный порт является портом с 32-мя антеннами, маска включает в себя одно из: числа mod(L_CRC/4) двоичных цепочек "1001" и числа mod(L_CRC, 4) биты "0"; floor(L_CRC/4) двоичных цепочек "1001" и множество битов от первого бита до mod(L_CRC, 4)-го бита двоичных цепочек floor(L_CRC/4) "1001"; или двоичных цепочек floor(L_CRC/4) "1001" и множества битов от последнего бита до mod(L_CRC, 4)-го бита из последнего бита двоичных цепочек floor(L_CRC/4) "1001". L_CRC включает в себя по меньшей мере одно из: количества битов циклического контроля избыточности, количества битов идентификатора соты, количества битов идентификатора луча, количества битов временного идентификатора соты радиосети или количества битов циклического контроля избыточности минус количество резервных битов. Количество резервных битов является любым целым числом от 0 до 16, floor() представляет собой операцию округления в сторону уменьшения, mod(L_CRC, 2) представляет собой операцию по модулю 2 над L_CRC, и mod(L_CRC, 4) представляет собой операцию по модулю 4 над L_CRC.

Следует отметить, что процессор 72 может быть дополнительно выполнен с возможностью выполнения по меньшей мере одной из следующих операций: выполнение операции XOR над маской и первым результатом проверки; и выполнение операции сложения по модулю 2 над маской и первым результатом проверки.

Следует отметить, что процессор 72 может быть дополнительно выполнен с возможностью выполнения по меньшей мере одной из следующих операций: в случае, когда количество битов временного идентификатора соты радиосети меньше количества битов первого результата проверки, добавление заданного количества двоичных битов "0" к начальной или конечной части временного идентификатора соты радиосети для получения первого временного идентификатора соты радиосети, и выполнение операции XOR над первым временным идентификатором соты радиосети и первым результатом проверки; или в случае, когда количество битов временного идентификатора соты радиосети больше, чем количество битов первого результата проверки, добавление заданного количества двоичных битов "0" к начальной или конечной части первого результата проверки для получения второго результата проверки, и выполнение операции XOR над временным идентификатором соты радиосети и вторым результатом проверки. Заданное количество имеет абсолютное значение разности между количеством битов идентификатора соты радиосети и количеством битов первого результата проверки.

В других вариантах осуществления процессор 72 может быть дополнительно выполнен с возможностью выполнения по меньшей мере одной из следующих операций: размещение первого результата обработки перед данными, подлежащими передаче, для получения сцепленных данных; размещение первого результата обработки среди данных, подлежащих передаче, для получения сцепленных данных; и размещение первого результата обработки после данных, подлежащих передаче, для получения сцепленных данных. Каждые М битов данных, которые должны передаваться в данных, подлежащих передаче, вставляются с битом данных первого результата обработки, и все биты первого результата обработки вставляются в данные, подлежащие передаче, для получения сцепленных данных. M является натуральным числом.

Следует отметить, что по меньшей мере два сегмента данных в множестве сегментов данных имеют перекрывающиеся данные, или перекрывающиеся данные не существуют в множестве сегментов данных, и настоящее изобретение не ограничивается этим.

Вариант 6 осуществления

Вариант осуществления настоящего изобретения дополнительно предусматривает терминал. На фиг.8 показана структурная блок-схема терминала согласно варианту осуществления настоящего изобретения. Как показано на фиг.8, терминал включает в себя: процессор 82 и память 84.

Процессор 82 выполнен с возможностью приема данных, отправленных устройством сетевой стороны, и определения, согласно заданному соответствию между сегментами данных и количеством передач данных и принятых данных, количества передач данных, соответствующих принятым данным. Данные представляют собой сегмент данных среди данных, полученных из предварительно обработанных данных, которые должны быть переданы устройством сетевой стороны.

Память 84 подключена к процессору 82.

Посредством вышеупомянутого терминала, количество передач данных, соответствующих принятым данным, определяется в соответствии с предварительно установленным соответствием между сегментами данных и количеством передач данных, так что терминал знает количество передач принятых данных, переданных сетевой стороной, тем самым решая проблему, заключающуюся в том, что терминал не может определить, в какой передаче принятые данные передаются сетевой стороной.

Следует отметить, что соответствие может быть предварительно согласовано между устройством сетевой стороны и терминалом и может быть также предварительно сконфигурировано устройством сетевой стороны для терминала, но это не является ограничением.

Следует отметить, что соответствие может включать в себя: соответствие между начальными точками сегментов данных в предварительно обработанных данных и номерами передач данных.

В других вариантах осуществления процессор 82 может быть дополнительно выполнен с возможностью получения начальной позиции принятых данных в предварительно обработанных данных; и поиска, согласно начальной позиции, соответствия для количества передач данных, соответствующих начальной позиции.

Вариант осуществления настоящего изобретения дополнительно предусматривает систему. Система включает в себя устройство сетевой стороны, описанное в варианте 5 осуществления, и терминал, описанный в варианте 6осуществления.

Вариант 7 осуществления

Следует отметить, что в варианте осуществления настоящего изобретения способ отправки данных или способ обработки данных, если они реализованы в форме программных функциональных модулей и продаются или используются в качестве независимых продуктов, могут также храниться на машиночитаемом носителе информации. Исходя из этого понимания, технические решения, предусмотренные вариантами осуществления настоящего изобретения, вносящего в значительной степени или частично вклад в предшествующий уровень техники, могут быть воплощены в виде программного продукта. Компьютерный программный продукт хранится на носителе информации и включает в себя несколько инструкций для обеспечения возможности компьютерному устройству (которым может быть персональный компьютер, сервер или сетевое устройство и т.д.) выполнять весь или часть способа, предусмотренного в каждом варианте осуществления настоящего изобретения. Вышеуказанный носитель информации включает в себя: флэш-диск USB, переносной жесткий диск, постоянное запоминающее устройство (ПЗУ), магнитный диск, оптический диск или другой носитель, способный хранить программные коды. Таким образом, вариант осуществления настоящего изобретения не ограничивается какой-либо конкретной комбинацией аппаратных средств и программного обеспечения.

Соответственно, вариант осуществления настоящего изобретения дополнительно предусматривает носитель информации. Носитель информации включает в себя хранящиеся на нем программы, которые при их исполнении выполняют способ, описанный в любом из приведенных выше вариантов осуществления.

В других вариантах осуществления носитель информации может, но не обязательно, включать в себя флэш-диск USB, постоянное запоминающее устройство (ПЗУ), оперативное запоминающее устройство (ОЗУ), переносной жесткий диск, магнитный диск, оптический диск или другой носитель, способный хранить программные коды.

Вариант осуществления настоящего изобретения дополнительно предусматривает процессор. Процессор выполнен с возможностью исполнения программ, которые при их исполнении выполняют этапы способа согласно любому из приведенных выше вариантов осуществления.

В других вариантах осуществления для конкретных примеров в варианте осуществления может быть сделана ссылка на примеры, описанные в вышеупомянутых вариантах осуществления и режимах реализации, и в варианте осуществления не будет присутствовать повторение.

Следует понимать, что "один вариант осуществления" или "вариант осуществления", упомянутый в описании, означает, что конкретный признак, структура или характеристика, относящиеся к вариантам осуществления, включены, по меньшей мере, в один вариант осуществления настоящего изобретения. Следовательно, появление фразы "в одном варианте осуществления" или "в варианте осуществления" в различных местах по всему описанию не обязательно относится к одному и тому же варианту осуществления. Кроме того, эти конкретные признаки, структуры или характеристики могут быть объединены в одном или нескольких вариантах осуществления любым подходящим способом. Следует понимать, что в различных вариантах осуществления настоящего изобретения порядковые номера вышеупомянутых процессов не означают порядок выполнения, и порядок выполнения вышеупомянутых процессов должен определяться в соответствии с их функциями и внутренней логикой, которая не должна ограничивать процессы реализации настоящего изобретения любым ненадлежащим образом. Порядковые номера описанных выше вариантов осуществления настоящего изобретения приведены всего лишь для упрощения описания и не указывают на превосходство и неполноценность вариантов осуществления.

Следует отметить, что используемый здесь термин "содержащий", "включающий в себя" или любой другой его вариант предназначен для охвата неисключительного включения, так что процесс, способ, изделие или устройство, которое включает в себя ряд элементов, не включает в себя только явно перечисленные элементы, но также включает в себя другие элементы, которые явно не перечислены или присущи такому процессу, способу, изделию или устройству. При отсутствии дополнительных ограничений элементы, определяемые выражением "включающий в себя …", не исключают наличия дополнительных идентичных элементов в процессе, способе, изделии или устройстве, которое включает в себя эти элементы.

Следует понимать, что устройства и способы, раскрытые в вариантах осуществления настоящего изобретения, могут быть реализованы другими способами. Варианты осуществления устройства, описанные выше, являются просто иллюстративными. Например, разделение на блоки является просто логическим разделением функций, и на практике разделение на блоки может быть реализовано другими способами. Например, несколько блоков или компонентов могут быть объединены или могут быть интегрированы в другую систему, или некоторые функции могут быть опущены или не выполнены. Кроме того, подключение, прямое подключение или коммуникационные соединения между представленными или описанными компонентами могут представлять собой опосредованное подключение или коммуникационные соединения через интерфейсы между устройствами или блоками и могут быть электрическими, механическими или иметь другие формы.

Блоки, описанные выше как отдельные компоненты, могут или не могут быть физически разделены. Компоненты, представленные как блоки, могут или не могут быть физическими блоками, то есть могут быть расположены в одном месте или могут быть распределены по нескольким сетевым блокам. Часть или все эти блоки могут быть выбраны в соответствии с практическими требованиями для достижения целей решений в вариантах осуществления настоящего изобретения.

Более того, различные функциональные блоки в вариантах осуществления настоящего изобретения могут быть интегрированы в один блок обработки, или каждый блок может использоваться как отдельный блок, или два или более блоков могут быть интегрированы в один блок. Интегрированный функциональный блок может быть реализован аппаратными средствами или может быть реализован аппаратными средствами совместно с программным функциональным блоком.

Специалистам в данной области техники может быть понятно, что все или часть этапов в вариантах осуществления способа, описанных выше, могут быть реализованы аппаратными средствами, связанными с программными инструкциями, эти программы могут храниться на машиночитаемом носителе информации, и при их исполнении эти программы выполняют этапы, включающие в себя описанные выше варианты осуществления способа; и вышеупомянутый носитель информации включает в себя различные носители, способные хранить программные коды, такие как съемное запоминающее устройство, постоянное запоминающее устройство (ПЗУ), магнитный диск или оптический диск.

В качестве альтернативы, вышеупомянутый интегрированный блок согласно настоящему изобретению может также храниться на машиночитаемом носителе данных, если он реализован в форме программного функционального модуля, и продается или используется в качестве независимого продукта. Исходя из этого понимания, технические решения, предусмотренные вариантами осуществления настоящего изобретения, вносящего в значительной степени или частично вклад в предшествующий уровень техники, могут быть воплощены в виде программного продукта. Компьютерный программный продукт хранится на носителе информации и включает в себя несколько инструкций для обеспечения возможности компьютерному устройству (которым может быть персональный компьютер, сервер или сетевое устройство и т.д.) выполнять весь или часть способа, предусмотренного в каждом варианте осуществления настоящего изобретения. Вышеупомянутый носитель информации включает в себя различные носители, способные хранить программные коды, такие как съемное запоминающее устройство, ПЗУ, магнитный диск или оптический диск.

Выше приведены только варианты осуществления настоящего изобретения, и они не предназначены для ограничения настоящего изобретения. Специалистам в данной области техники легко представить модификации или замены в рамках технического объема настоящего изобретения. Эти модификации или замены находятся в пределах объема настоящего изобретения. Таким образом, объем защиты настоящего изобретения подпадает под объем прилагаемой формулы изобретения.

Промышленная применимость

В вариантах осуществления настоящего изобретения первая заданная обработка выполняется над данными, подлежащими передаче, для получения первого результата обработки; первый результат обработки объединяется с данными, подлежащими передаче, для получения сцепленных данных; вторая заданная обработка выполняется над сцепленными данными для получения обработанных данных; и передается сегмент данных в обработанных данных, который соответствует текущей передаче данных устройства сетевой стороны. Таким образом, решена проблема уровня техники, заключающаяся в том, что терминал не может определить, в какой передаче принятые данные передаются сетевой стороной.

| название | год | авторы | номер документа |

|---|---|---|---|

| CRC-БИТЫ ДЛЯ ОБЪЕДИНЕННОГО ДЕКОДИРОВАНИЯ И ВЕРИФИКАЦИИ УПРАВЛЯЮЩЕЙ ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ ПОЛЯРНЫХ КОДОВ | 2017 |

|

RU2733282C1 |

| СПОСОБ ПЕРЕДАЧИ СИГНАЛА СИНХРОНИЗАЦИИ В СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ И УСТРОЙСТВО ДЛЯ ЭТОГО | 2018 |

|

RU2719354C1 |

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ | 2018 |

|

RU2728527C1 |

| КОНФИГУРАЦИЯ ДЛЯ ОПОРНОЙ СИГНАЛИЗАЦИИ В СИСТЕМАХ БЕСПРОВОДНОЙ СВЯЗИ | 2020 |

|

RU2805982C1 |

| КОДИРОВАНИЕ ПОДТВЕРЖДЕНИЙ ПРИЕМА ГИБРИДНОГО АВТОМАТИЧЕСКОГО ЗАПРОСА НА ПОВТОРЕНИЕ В СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ С НЕСКОЛЬКИМИ АНТЕННАМИ | 2013 |

|

RU2621002C2 |

| СПОСОБ ОБРАБОТКИ СОБЫТИЙ И УСТРОЙСТВО | 2019 |

|

RU2805168C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРСИИ ИЗБЫТОЧНОСТИ СИСТЕМНОЙ ИНФОРМАЦИИ | 2019 |

|

RU2777447C2 |

| УСТРОЙСТВО СВЯЗИ И СПОСОБ СВЯЗИ | 2017 |

|

RU2771448C2 |

| СПОСОБ И УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ И МАШИНОЧИТАЕМЫЙ НОСИТЕЛЬ ХРАНЕНИЯ ДАННЫХ | 2020 |

|

RU2812018C2 |

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 2007 |

|

RU2408979C2 |

Группа изобретений относится к средствам для отправки данных. Технический результат – улучшение качества канала передачи. Для этого предложен способ отправки данных, который включает в себя этапы, на которых: выполняют первую заданную обработку над данными, подлежащими передаче, для получения первого результата обработки; объединяют первый результат обработки с данными, подлежащими передаче, для получения сцепленных данных; выполняют вторую заданную обработку над сцепленными данными для получения обработанных данных и передают сегмент данных в обработанных данных, который соответствует текущей передаче данных устройства сетевой стороны. 8 н. и 4 з.п. ф-лы, 8 ил.

1. Способ сетевой связи, содержащий этапы, на которых: