Изобретение относится к технологии эксплуатации мемристора с диэлектрической структурой, расположенной между его двумя электродами, обладающей резистивной памятью и обеспечивающей филаментарный механизм переключения мемристора, и может быть использовано для стабильного переключения такого мемристора за счет автоматической подстройки формы и длительности импульсов напряжения, переключающих мемристор в высокоомное или низкоомное состояние.

Особенностью работы мемристоров в качестве элементов памяти, является резистивная стохастичность мемристора в высокоомном и низкоомном состояниях при переключении мемристора в данные состояния.

Так традиционное переключение мемристоров, например, на основе смешанного оксида металлов, осуществляется с помощью стандартной управляющей программы измерения вольтамперных характеристик мемристора и его переключения (см. патенты РФ №2472254, H01L 45/00, В82В 1/00, 2013 на изобретение «Мемристор на основе смешанного оксида металлов» и №2524415, H01L 45/00, В82В 1/00, 2014 на изобретение «Мемристор на основе смешанного оксида металлов»), сопровождаемого разбросом величин сопротивления мемристора в высокоомном и низкоомных состояниях, оцениваемым в информационных источниках на уровне ~20-50% (см. например, статью на англ. яз. автора Daniele lelmini «Resistive switching memories based on metal oxides: mechanisms, reliability and scaling» - Semicond. Sci. Technol. 2016, v. 31, №063002, p. 12, fig. 16).

Приведенный пример переключения мемристора в описаниях изобретений к двум указанным российским патентам свидетельствует о значительном резерве повышения его эффективности в связи с низкой технологичностью настройки переключения мемристора на основе предварительного усреднения сопротивлений мемристора в высокоомном и низкоомном состояниях и сохранением проблемы снижения резистивной стохастичности мемристора, проявляемой при его переключениях.

Известно устройство для регулирования импульсов переключения мемристора, выполняющее функцию переключения последнего и содержащее источник напряжения для подачи на мемристор, детектор напряжения для обнаружения напряжения мемристора, в котором напряжение мемристора основано на начальном сопротивлении мемристора и напряжении, подаваемом источником напряжения, компаратор для сравнения напряжения мемристора с контрольной величиной напряжения мемристора, причем последняя используется для регулирования импульса переключения мемристора, контур обратной связи для указания управляющему переключателю, когда напряжение мемристора по меньшей мере равно контрольной величине напряжения, и управляющий переключатель для автоматического отключения и отсоединения мемристора от источника напряжения, когда напряжение мемристора, по меньшей мере, равно контрольной величине напряжения (см. п. 1 формулы изобретения по патенту US 9837147, G11C 13/00, 2017 на изобретение "Regulating memristor switching puls").

В указанном аналоге осуществлено регулирование импульсов переключения мемристора, основанное на изменении заряда последовательно включенного с мемристором конденсатора (при подаче на мемристор постоянного напряжения), используемого в качестве детектора напряжения мемристора и одновременном сравнении снимаемого с помощью этого детектора изменяющегося по величине напряжения мемристора с контрольной величиной напряжения мемристора, которая должна соответствовать одному из переключаемых состояний мемристора, и ухудшающее управление стабильной работой мемристора в связи с низкой технологичностью определения нестабильной контрольной величины указанного напряжения мемристора на основе текущей статистики замеров напряжений мемристора из-за резистивной стохастичности последнего и зависимостью сопротивления мемристора в высокоомном и низкоомном состояниях от стабильности источника напряжения и времени переключения мемристора от быстродействия управляющего переключателя.

Изложенная специфика осуществления указанного аналога в связи с иным физическим механизмом детектирования текущего состояния мемристора (см. в конце настоящего описания группы изобретений обоснование разницы в физическом механизме переключения мемристора в заявляемом устройстве и устройстве по патенту US 9837147), основанным на текущем обнаружении изменяющегося напряжения мемристора, а так же из-за различий в системе управления процессом переключения мемристора из одного состояния в другое явилась причиной отказа от его использования в настоящем описании в качестве прототипа заявляемого устройства для переключения мемристора, поэтому выбрана форма раскрытия сущности предлагаемой группы изобретений - без прототипа.

Технический результат предлагаемой группы изобретений - разработка оптимального устройства для автоматического переключения мемристора, характеризующегося стабильным его переводом (независящем от напряжения питания и предыстории работы мемристора) в высокоомное или низкоомное состояние при сочетании повышенного по технологичности обеспечения измерения текущей величины сопротивления мемристора (в режиме отслеживания сопротивления сопротивления мемристора) и сравнения ее с задаваемыми аналоговыми величинами сопротивления мемристора в высокоомном или низкоомном состоянии, одновременной подачи импульса напряжения с изменяемой формой для переключения мемристора без зависимости от стабильности источника постоянного напряжения, от предыстории работы мемристора и от быстродействия системы обратной связи, состоящей из дифференциальных усилителей и реостатов, и упрощением схемотехнической реализации устройства для осуществления предлагаемого способа на основе снижения резистивной стохастичности мемристора при его переключениях.

Кроме того, предлагаемое изобретение расширяет актуальный арсенал эффективных контрольно-измерительных исполнительных средств, обеспечивающих стабильное переключение мемристоров.

Для достижения указанного технического результата предлагается устройство для переключения мемристора, содержащее два источника постоянного напряжения, с противоположной друг к другу полярностью, два реостата, два резистивных делителя и два дифференциальных усилителя напряжения, образующие по одному две группы элементов для переключения мемристора в высокоомное или низкоомное состояние.

Причем в каждой указанной группе реостат соединен своим входом с источником постоянного напряжения, своим выходом с первым электродом мемристора и управляющим входом с выходом дифференциального усилителя напряжения, а резистивный делитель соединен своими первым входом с источником постоянного напряжения и вторым входом с землей и своим выходом с инвертирующим входом дифференциального усилителя.

При этом ко второму электроду мемристора подсоединен резистор, образующий с мемристором, выполняющим функцию второго резистивного плеча, дополнительный резистивный делитель, выход которого подключен к неинвертирующим входам обоих дифференциальных усилителей в указанных группах, входящие в состав обоих резистивных делителей в указанных группах резисторы с их подключением к соответствующим источникам постоянного напряжения имеют сопротивления, равные сопротивлениям мемристора в высокоомном или низкоомном состоянии, а оба реостата имеют настройку своих граничных величин сопротивления больше величины сопротивления мемристора в высокоомном состоянии и меньше величины сопротивления мемристора в низкоомном состоянии.

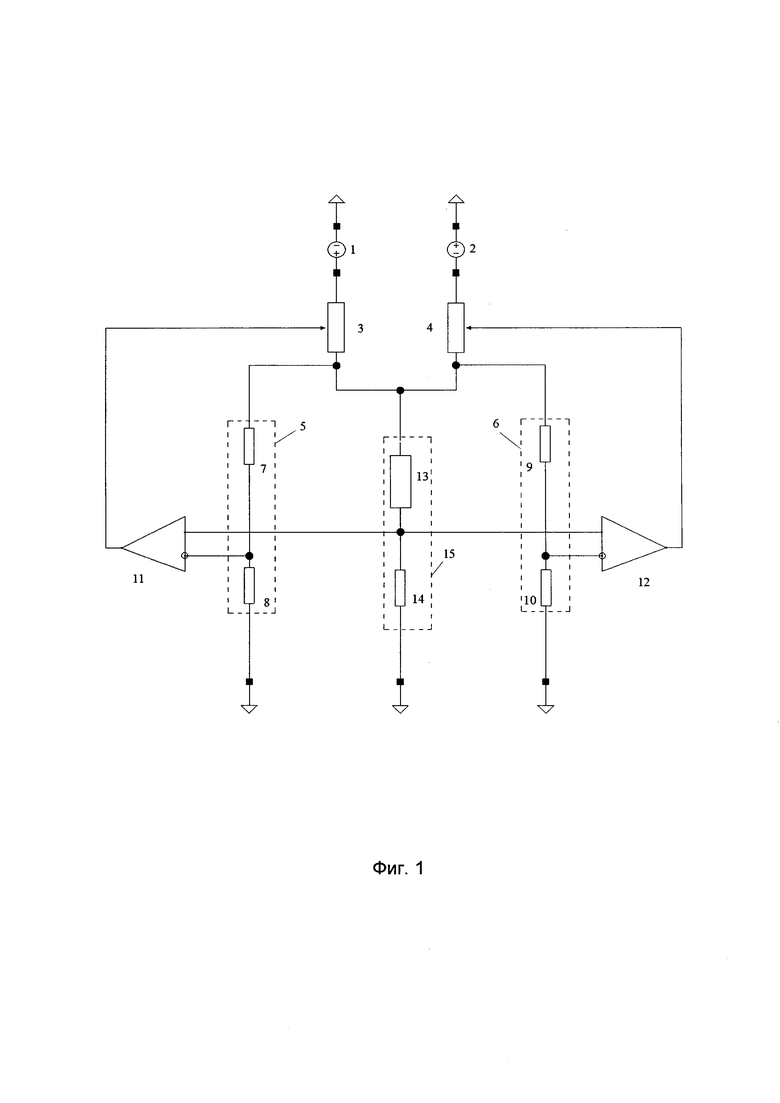

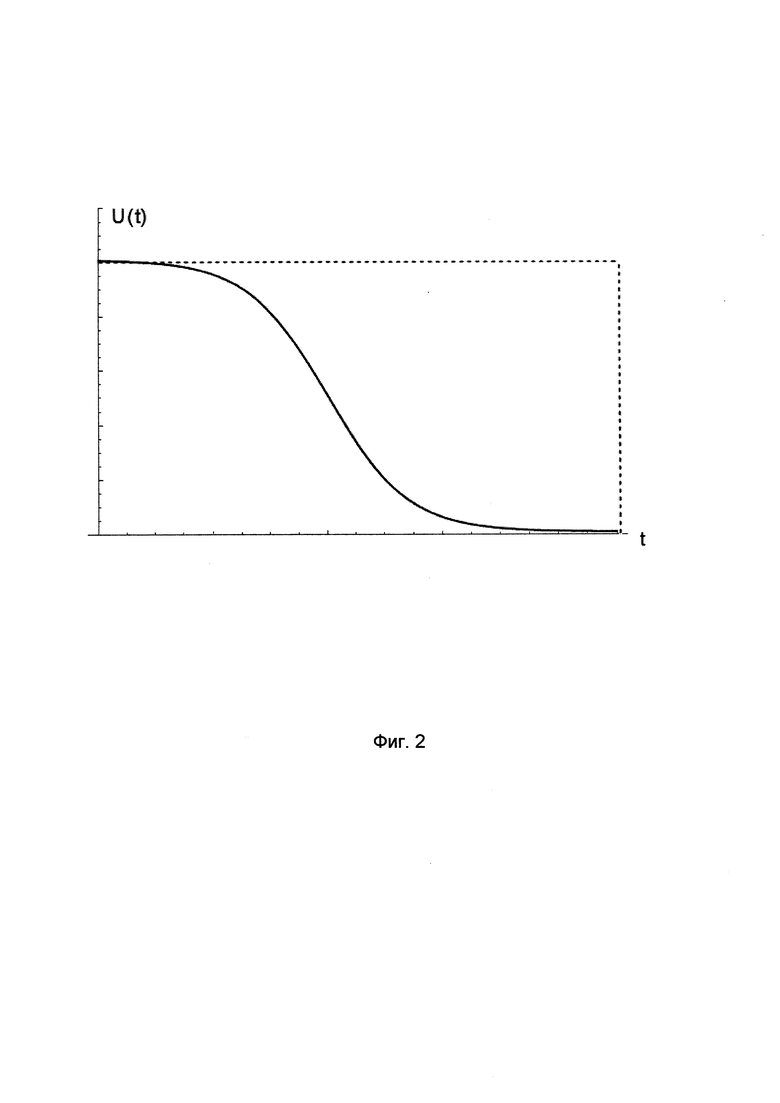

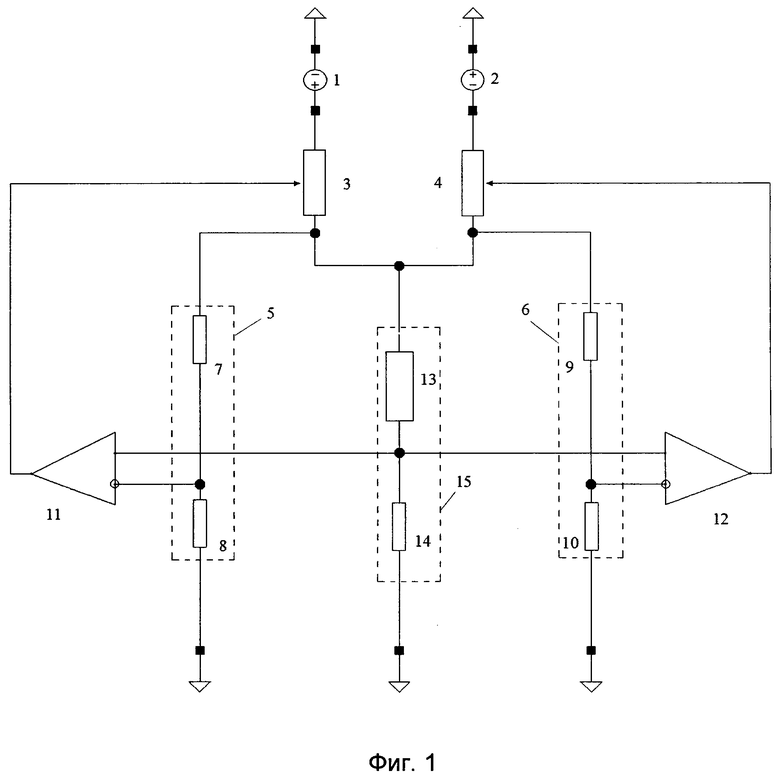

На фиг. 1 показана блок-схема предлагаемого устройства для переключения мемристора; на фиг. 2 - преобразование формы переключающего импульса в процессе работы устройства на фиг. 1.

Устройство для переключения мемристора (см. фиг. 1) содержит два источника постоянного напряжения 1 и 2, с противоположной друг к другу полярностью, два реостата 3 и 4, два резистивных делителя 5 и 6, состоящих из резисторов 7, 8 и 9, 10 соответственно, и два дифференциальных усилителя 11 и 12, образующие по одному две группы элементов для переключения соответственно в низкоомное и высокоомное состояние мемристора 13, подключенного к резистору 14.

Причем в каждой указанной группе реостат 3 или 4 соединен своим входом с источником постоянного напряжения 1 или 2, своим выходом с первым электродом мемристора 13 и управляющим входом с выходом дифференциального усилителя напряжения 11 или 12, а резистивный делитель 5 или 6 соединен своими первым входом с источником постоянного напряжения 1 или 2 и вторым входом с землей и своим выходом с инвертирующим входом дифференциального усилителя 11 или 12.

При этом ко второму электроду мемристора 13 подсоединен резистор 14, образующий с мемристором 13, выполняющим функцию второго резистивного плеча, дополнительный резистивный делитель 15, выход которого подключен к неинвертирующим входам обоих дифференциальных усилителей 11 и 12 в указанных группах, входящие в состав резистивных делителей 5 и 6 в указанных группах резисторы 7 и 9 имеют сопротивления, равные сопротивлениям мемристора в низкоомном или высокоомном состоянии, а реостаты 3 и 4 имеют настройку своих граничных величин сопротивления больше величины сопротивления мемристора 13 в высокоомном состоянии и меньше величины сопротивления мемристора 13 в низкоомном состоянии.

Предлагаемое устройство для переключения мемристора работает следующим образом.

Пусть мемристор 13 находится в высокоомном состоянии и требуется перевести его в низкоомное состояние. Для этого включается источник 1 (источник 2 отключен), создающий прямоугольный импульс напряжения положительной полярности.

Сопротивления резисторов 8, 10 и 14 должны быть равны между собой, точное же значение их сопротивления не принципиально для работы схемы и может быть выбрано, как среднее арифметическое значение сопротивления резисторов 7 и 9. Поскольку изначально мемристор находится в высокоомном состоянии, его сопротивление выше сопротивления резистора 7, который задает сопротивление мемристора в низкоомном состоянии, следовательно, в начальный момент времени напряжение на выходе делителя напряжения 15 будет ниже, чем напряжение на выходе делителя напряжения 5. Таким образом, на вход дифференциального усилителя 11 будет подаваться отрицательная разность потенциалов. Будучи усиленным усилителем 11 отрицательный сигнал придет на управляющий вход реостата 3, сделав его электрическое сопротивление низким. В результате все напряжение, вырабатываемое источником 1, будет падать на делителе 15 и, в частности, на мемристоре 13, вызывая максимально быстрое (при заданном напряжении источника 1) уменьшение его сопротивления. По мере уменьшения сопротивления мемристора 13 напряжение на выходе делителя 15 будет расти, а разность потенциалов на входе дифференциального усилителя 11 будет уменьшаться по модулю, приводя к тому, что сопротивление реостата начнет увеличиваться. Поскольку с увеличением сопротивления реостата 3 все большая часть напряжения, вырабатываемого источником 1, будет падать на реостате 3, форма импульса напряжения, поступающего на вход делителя 15 (в состав которого входит мемристор 13) начнет все больше отличаться от прямоугольной (см. фиг 2, где пунктиром изображен прямоугольный импульс напряжения, вырабатываемый источником 1, а сплошной линией -преобразованный импульс напряжения, поступающий на вход делителя 15). Вслед за уменьшением напряжения на входе делителя 15 начнет уменьшаться и скорость изменения сопротивления мемристора, пропорциональная приложенному к мемристору напряжению. Это обстоятельство обеспечит более точную настройку сопротивления мемристора 13 в низкоомном состоянии, по сравнению с методом, описанном в патенте US 9837147, поскольку при быстрых, лавинообразных изменениях сопротивления мемристора возникают сложности с точным определением того момента, когда сопротивление мемристора достигает заданного значения, вызванные задержками, неизбежно возникающими в процессе переключения любого реального компаратора и размыкания любого реального ключа, использованных в группе изобретений по патенту US 9837147. Замедление же процесса изменения сопротивления мемристора 13 в предлагаемой схеме позволит снизить влияние быстродействия используемых элементов схемы (а так же задержек в них) на точность установки сопротивления мемристора 13 в требуемом состоянии. В тот момент времени, когда сопротивление мемристора 13 достигнет значения сопротивления 7, напряжения на выходах делителей 5 и 15 сравняются. Напряжение на выходе усилителя 11 в этот момент станет равным нулю, переведя сопротивление реостата в максимально возможное значение, много большее, чем сопротивление мемристора в высокоомном состоянии. При этом практически все напряжение, вырабатываемое источником 1, будет падать на реостате, закончив тем самым процесс изменения сопротивления мемристора 13, который будет переведен в низкоомное состояние со значением сопротивления, равным сопротивлению резистора 7.

Аналогичным образом происходит переключение мемристора 13 из низкоомного состояния в высокоомное, для чего на него подается отрицательное напряжение с помощью источника 2 (источник 1 при этом отключен). Поскольку теперь в начальный момент работы схемы мемристор 13 находится в низкоомном состоянии, напряжение на выходе делителя 15 будет ниже (с учетом знака), чем напряжение на выходе делителя 6. Таким образом, в начальный момент работы схемы на вход дифференциального усилителя 12 так же будет подаваться отрицательная разность потенциалов. Будучи усиленным усилителем 12 отрицательный сигнал придет на управляющий вход реостата 4, сделав его электрическое сопротивление низким. В результате все напряжение, вырабатываемое источником 2, будет падать на делителе 15 и, в частности, на мемристоре 13, вызывая максимально быстрое (при заданном напряжении источника 2) увеличение его сопротивления. По мере увеличения сопротивления мемристора 13 напряжение на выходе делителя 15 будет расти (уменьшаясь по модулю), а разность потенциалов на входе дифференциального усилителя 12 будет уменьшаться по модулю, приводя к тому, что сопротивление реостата начнет увеличиваться. При этом коэффициент усиления усилителя 12 должен быть выбран таким образом, чтобы скорость роста сопротивления реостата 4 была выше скорости роста сопротивления мемристора 13. Поскольку с увеличением сопротивления реостата 4 все большая часть напряжения, вырабатываемого источником 2, будет падать на реостате 4 (а не на мемристоре 13), скорость изменения сопротивления мемристора, пропорциональная приложенному к мемристору напряжению, начнет уменьшаться. В тот момент времени, когда сопротивление мемристора 13 достигнет значения сопротивления 9, напряжения на выходах делителей 6 и 15 сравняются. Напряжение на выходе усилителя 12 в этот момент станет равным нулю, переведя сопротивление реостата в максимально возможное значение, много большее, чем сопротивление мемристора в высокоомном состоянии. При этом практически все напряжение, вырабатываемое источником 2, будет падать на реостате, закончив тем самым процесс изменения сопротивления мемристора 13, который будет переведен в высокоомное состояние со значением сопротивления, равным сопротивлению резистора 9.

При этом стабильное переключение мемристора 13 с установкой повышенной по технологичности обеспечения заданной величины сопротивления мемристора 13 в высокоомном или низкоомном состоянии в сравнении с обеспечением контрольной величины напряжения мемристора в описании группы изобретений по патенту US 9837147 достигается в результате выбора в качестве контролируемой величины непосредственно сопротивления мемристора 13 (а не протекшего через мемристор по указанному американскому патенту заряда), а в качестве контрольных величин - сопротивлений резисторов 7 и 9. Такой выбор позволяет устранить зависимость сопротивления мемристора 13 в высокоомном и низкоомном состояниях от стабильности источника напряжения (вследствие независимости величин сопротивления резисторов 7 и 9 от поданного на них напряжения), а так же от предыстории работы мемристора 13 без необходимости проведения предварительных измерений зависимости сопротивления мемристора 13 от протекшего через него заряда (что исключает из состава устройства дополнительные блоки, требуемые для проведения таких измерений, повышая таким образом его технологичность), а так же без необходимости проведения подстройки контрольного напряжения при изменении напряжения импульсов, подаваемых для переключения мемристора 13 (что так же повышает технологичность устройства за счет исключения из него блоков подстройки контрольного напряжения).

А исключение необходимости использования измерительных приборов для получения информации о зависимости сопротивления мемристора от прошедшего через него заряда в описании группы изобретений по патенту US 9837147 упрощает схемотехническую реализацию устройства для осуществления предлагаемого способа.

Кроме того, использование дифференциальных усилителей, способных формировать на своем выходе аналоговое напряжение из некоторого диапазона, вместо компараторов, выдающих лишь одно из двух логических состояний, а так же использование реостатов с плавно изменяющимся сопротивлением вместо ключей, способных быть лишь в одном из двух возможных (замкнутое и разомкнутое) состояний, позволяет аналоговым образом контролировать форму напряжения, подающегося на мемристор, с целью изменения скорости его переключения.

В примере выполнения предлагаемого устройства для переключения мемристора 13, имеющего структуру Au/Ta (8 нм) / ZrO2 (12 мол. % Y2O3, 10 нм) / ТаОх (10 HM)/TiN/Ti, при х, имеющем величину от 2.0 до 2.5, проводилось математическое моделирование с использованием САПР Cadence измерение текущей величины мемристора 13 сопротивления, усиление сигнала, пропорционального разности текущего сопротивления мемристора и заданного сопротивления мемристора в высокоомном (100 КОм) или низкоомном (1 КОм) состоянии с помощью дифференциального усилителя 11 или 12 и одновременная подача от источников 1 или 2 прямоугольного импульса с амплитудой не менее 3 В, преобразуемого затем с помощью с помощью реостатов 3 или 4, управляемых дифференциальными усилителями 11 или 12 соответственно в импульс формой (см. фиг. 2), отличной от прямоугольной, и с полярностью, соответственно положительной или отрицательной и длительностью в пределах интервала величин от 10 не до 10 мс в зависимости от наступления момента, по меньшей мере, равенства измеряемого текущего сопротивления мемристора 13 с указанными величинами сопротивления мемристора 13 в высокоомном или низкоомном состоянии.

Сопротивление резисторов 8, 10 и 14 составляло в данном примере 50 КОм, а мемристор 13 переводился в состояние с низким сопротивлением, равным 1 КОм, и в состояние с высоким сопротивлением, равным 100 КОм, с ошибкой, не превосходящей 1%.

Сопротивления реостатов 1 и 2 в замкнутом состоянии составляло 100 Ом, в разомкнутом - 1 ГОм.

Обоснование разницы в физическом механизме переключения мемристора в заявляемой группе изобретений и группе изобретений по патенту US 9837147.

Впервые понятие мемристора ввел Леон Чуа в 1971 году в работе (L.O. Chua, Memristor-the missing circuit element. IEEE Trans. Circuit Theory. 18, 507-519 (1971)). В соответствии с данным им определением электрическое сопротивление мемристора определяется зарядом q, прошедшим через мемристор. Если известно, какой ток I(t) (где t - это текущее время) протекал через мемристор в течение некоторого времени, то заряд, прошедший через мемристор к моменту времени Т, можно, по определению, записать как интеграл:

Таким образом, зная этот интеграл, можно определить величину электрического сопротивления мемристора. Но все это верно лишь для идеального мемристора, введенного Чуа. Реальные современные электронные компоненты, называемые мемристорами, в действительности являются так называемыми мемристивными системами, которым присущи некоторые (но не все) из свойств идеального мемристора (см., например, обзор на английском языке автора Daniele lelmini «Resistive switching memories based on metal oxides: mechanisms, reliability and scaling» - Semicond. Sci. Technol. 2016, v. 31, №063002). Для реальных электронных компонентов точный вид зависимости электрического сопротивления от прошедшего через них заряда неизвестен. Более того, электрическое сопротивление таких мемристивных систем зависит не только от заряда, но и от других факторов, и сам вид зависимости может меняться со временем.

В описании группы изобретений по патенту US 9837147 нет информации о том, как следует получать напряжение мемристора («memristor voltage»), это понятие введено без точного определения. Однако описан детектор - устройство для получения этого напряжения. Устройство представляет собой конденсатор, включенный последовательно с мемристором. Ток, протекающий через мемристор, заряжает конденсатор, напряжение на котором пропорционально заряду, накопленному на обкладках конденсатора. Этот заряд определяется по формуле (1). Таким образом, измеряя напряжение на конденсаторе, можно получить информацию о заряде, который накопился на его обкладках, пройдя сквозь мемристор. А зная заряд, прошедший через мемристор, можно узнать и сопротивление мемристора. Такова логика устройства, предложенного в патенте US 9837147. Использовать такое устройство на практике можно лишь при условии того, что известна точная зависимость сопротивления мемристора от прошедшего через него заряда. Однако, как уже было сказано выше, в общем случае такая зависимость неизвестна, более того, даже если ее предварительно измерить, это не решит проблему, поскольку зависимость эта меняется со временем. Поэтому в заявляемом изобретении отсутствует измерение заряда, прошедшего через мемристор 13, и вычисление сопротивления мемристора 13 по измеренной величине заряда, а происходит измерение сопротивления мемристора 13 напрямую. Измерение сопротивления основывается на определении сопротивления как величины, равной отношению падения напряжения на мемристоре 13 к току, протекающему через этот мемристор. При использовании в резистивных делителях 5, 6 и 15 одинаковых резисторов 8, 10 и 14, автоматически обеспечивается равенство токов, протекающих через делители 5 и 15 (или через делители 6 и 15 - в зависимости от того, происходит переключение мемристора 13 в низкоомное или в высокоомное состояние соответственно) в тот момент, когда сравниваются напряжения, подаваемые на вход дифференциального усилителя 11 (или 12 - для переключения в высокоомное состояние). Таким образом, в тот момент, когда напряжения, подаваемые на дифференциальный усилитель 11 (или 12), сравняются, будет известно, что электрическое сопротивление мемристора 13 стало равным электрическому сопротивлению резистора 7 (или резистора 9). Поскольку величина сопротивления резисторов 7 или 9 не зависит от напряжений, создаваемых источниками 1 или 2, не будет от этого напряжения зависеть и сопротивление мемристора 13, переведенного в высокоомное или низкоомное состояние.

Причем в основе патента US 9837147 лежит идея сравнения некого «напряжения мемристора» (memristor voltage), получаемого неуказанным в патенте способом, с целевым напряжением, метод определения которого в патенте так же не указан, и использование результата сравнения этих напряжений для отключения источника питания от мемристора. При использовании метода регулировки импульсов напряжения, подаваемых для переключения мемристора из одного состояния в другое, описанного в патенте US 9837147 необходимо:

1. разработать способ получения «напряжения мемристора», о котором известно лишь, что оно зависит от напряжения питания и начального состояния мемристора;

2. разработать способ задания целевого напряжения;

3. иметь информацию о конкретной зависимости состояния данного конкретного мемристора от напряжения, использующегося для сравнения с целевым напряжением, которое в общем случае зависит от заряда, прошедшего через мемристор.

Кроме того, переключение мемристора, предложенное в патенте US 2017/0062048 А1 предполагает регулировку длительности импульс напряжения прямоугольной формы, подаваемых на мемристор с целью его переключения. Одной из основных проблем, возникающих при использовании такого метода, является сильная зависимость скорости переключения мемристора от величины напряжения, подаваемого на него с целью переключения (см., например, статью авторов Gilberto Medeiros-Ribeiro, Frederick Perner, Richard Carter, Hisham Abdalla, Matthew D Pickett, R Stanley Williams на англ. языке Lognormal switching times for titanium dioxide bipolar memristors: origin and resolution, Nanotechnology, 2011, v. 22, №095702). Поскольку время срабатывания любого компаратора напряжения конечно, задержка, возникающая при его переключении, будет приводить к ошибке установки сопротивления мемристора из-за того, что момент времени размыкания ключа будет отличаться от момента времени, когда «напряжение мемристора» сравняется с целевым значением. А поскольку в реальном приборе напряжение, подаваемое на мемристор для его переключения, будет флуктуировать со временем, вместе с ним будет изменяться и скорость переключения мемристора, а следовательно, ошибка установки сопротивления мемристора также будет меняться от одного акта переключения к другому. С целью преодоления указанной проблемы в предлагаемом нами методе вместо компаратора, имеющего только два возможных значения выходного сигнала, используется дифференциальный усилитель напряжения (11 или 12), на выходе которого может быть любое значение напряжения из рабочего диапазона выходных напряжений, определяемое коэффициентом усиления усилителя и разницей напряжения на его входах. На входы указанного усилителя подаются два напряжения: первое из них пропорционально текущему сопротивлению мемристора 13, второе - заданному значения сопротивления мемристора 13 в высокоомном или низкоомном состоянии. Чем больше разница этих напряжений, тем больше напряжение на выходе усилителя. Напряжение с выхода усилителя 11 или 12 подается на управляющий вход реостата 3 или 4, который используется в предлагаемом устройстве вместо ключа, который может быть либо замкнут, либо разомкнут.Низкое напряжение на управляющем входе реостата 3 или 4 соответствует низкому сопротивлению этого реостата, высокое напряжение на управляющем входе реостата 3 или 4 соответствует его высокому сопротивлению. Реостат 3 или 4 следует выбрать так, чтобы его низкое сопротивление было много меньше сопротивления мемристора 13 в низкоомном состоянии, а его высокое сопротивление было много больше сопротивления мемристора 13 в высокоомном состоянии. В качестве такого реостата может использоваться р-канальный полевой транзистор при подаче на мемристор 13 напряжения положительной полярности и n-канальный полевой транзистор при подаче на мемристор 13 напряжения отрицательной полярности.

Таким образом, в отличие от предложенного в патенте US 2017/0062048 А1 метода, в предлагаемом устройстве происходит детектирование электрического сопротивления мемристора 13. В случае если это сопротивление отличается от заданного значения сопротивления мемристора 13 в высоокоомном (или в низкоомном - в зависимости от того, в какое состояние мемристор 13 требуется переключить) состоянии, на управляющий вход реостата 3 или 4 подается низкое напряжение, что приводит к тому, что большая часть падения напряжения происходит на мемристоре 13. Это, в свою очередь, приводит к быстрому изменению значения сопротивления мемристора 13. Однако по мере того, как сопротивление мемристора 13 будет приближаться к заданном значению сопротивления мемристора 13 в высокоомном (или в низкоомном) состоянии, напряжение на выходе усилителя 11 или 12 будет увеличиваться. Вследствие этого будет возрастать сопротивление реостата 3 или 4, а падение напряжения на мемристоре 13 будет убывать, уменьшая таким образом скорость переключения мемристора 13. При уменьшении скорости переключения мемристора 13 возможные ошибки, связанные с конечной скоростью работы усилителя 11 или 12 будут оказывать меньшее влияние. Таким образом, результатом использования предлагаемого устройства является адаптивное изменение величины падения напряжения на мемристоре 13, увеличивающее скорость его переключения в начале процесса переключения и замедляющее скорость его переключения в конце процесса перелючения, когда высокое значение скорости переключения мемристора 13 приводит к повышению ошибки установки его сопротивления.

Кроме того, в отличие от метода регулирования в патенте US 9837147 метода, работа предлагаемого устройства не требует предварительного вычисления и задания целевого напряжения, а следовательно, не требует и информации о конкретном виде зависимости состояния мемристора 13 от прошедшего через него заряда. При использовании предлагаемого устройства задаются лишь значения сопротивления мемристора 13 в высокоомном и низкоомном состоянии.

Таким образом, в предлагаемом устройстве контролируется длительность и форма импульса напряжения с преобразуемой формой, подаваемого на мемристор 13, для перевода его в одно из двух логических состояний - с низким и с высоким сопротивлением. Такой контроль обеспечивает снижение разброса значений сопротивления мемристора 13 (по сравнению со случаем, когда для переключения мемристора 13 используется подача импульсов напряжения фиксированной длительности) за счет использования системы контроля текущего сопротивления мемристора 13, а также независимость получаемых значений сопротивления мемристора 13 в высокоомном и низкоомном состояниях от амплитуд подаваемых на него импульсов и от предыстории работы мемристора 13.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ управления работой мемристора и устройство для его осуществления | 2019 |

|

RU2737794C1 |

| Устройство программирования резистивных состояний мемристорных элементов | 2022 |

|

RU2795273C1 |

| Способ генерации случайных чисел с помощью мемристорного источника стохастических сигналов и устройство для его осуществления | 2021 |

|

RU2787560C1 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| Способ формирования мемристивных структур на основе композитных оксидов с агломератами наночастиц | 2021 |

|

RU2767721C1 |

| ОДНОЭЛЕКТРОННЫЙ МЕМРИСТОР (НАНОЯЧЕЙКА) И СПОСОБ ПРИМЕНЕНИЯ | 2023 |

|

RU2823967C1 |

| Способ формирования полимерного мемристора на основе двухслойной структуры полупроводниковый полимер-сегнетоэлектрический полимер | 2022 |

|

RU2786791C1 |

| МЕМРИСТОР НА ОСНОВЕ СМЕШАННОГО ОКСИДА МЕТАЛЛОВ | 2011 |

|

RU2472254C9 |

| МЕМРИСТОР НА ОСНОВЕ СМЕШАННОГО ОКСИДА МЕТАЛЛОВ | 2013 |

|

RU2524415C1 |

| Способ получения активного слоя для бесформовочного элемента энергонезависимой резистивной памяти | 2021 |

|

RU2779436C1 |

Изобретение относится к технологии эксплуатации мемристора с диэлектрической структурой, расположенной между его двумя электродами, обладающей резистивной памятью и обеспечивающей филаментарный механизм переключения мемристора, и может быть использовано для стабильного переключения такого мемристора за счет автоматической подстройки формы и длительности импульсов напряжения, переключающих мемристор в высокоомное или низкоомное состояние. Предлагается устройство для переключения мемристора, содержащее два источника постоянного напряжения, с противоположной друг к другу полярностью, два реостата, два резистивных делителя и два дифференциальных усилителя напряжения, образующие по одному две группы элементов для переключения мемристора в высокоомное или низкоомное состояние. Причем в каждой указанной группе реостат соединен своим входом с источником постоянного напряжения, своим выходом с первым электродом мемристора и управляющим входом с выходом дифференциального усилителя напряжения, а резистивный делитель соединен своими первым входом с источником постоянного напряжения и вторым входом с землей и своим выходом с инвертирующим входом дифференциального усилителя. При этом ко второму электроду мемристора подсоединен резистор, образующий с мемристором, выполняющим функцию второго резистивного плеча, дополнительный резистивный делитель, выход которого подключен к неинвертирующим входам обоих дифференциальных усилителей в указанных группах, входящие в состав обоих резистивных делителей в указанных группах резисторы с их подключением к соответствующим источникам постоянного напряжения имеют сопротивления, равные сопротивлениям мемристора в высокоомном или низкоомном состоянии, а оба реостата имеют настройку своих граничных величин сопротивления больше величины сопротивления мемристора в высокоомном состоянии и меньше величины сопротивления мемристора в низкоомном состоянии. Изобретение обеспечивает формирование устройства для автоматического переключения мемристора, характеризующееся стабильным его переводом (независящим от напряжения питания и предыстории работы мемристора) в высокоомное или низкоомное состояние. 2 ил.

Устройство для переключения мемристора, содержащее два источника постоянного напряжения, с противоположной друг к другу полярностью, два реостата, два резистивных делителя и два дифференциальных усилителя напряжения, образующие по одному две группы элементов для переключения мемристора в высокоомное или низкоомное состояние, причем в каждой указанной группе реостат соединен своим входом с источником постоянного напряжения, своим выходом с первым электродом мемристора и управляющим входом с выходом дифференциального усилителя напряжения, а резистивный делитель соединен своими первым входом с источником постоянного напряжения и вторым входом с землей и своим выходом с инвертирующим входом дифференциального усилителя, при этом ко второму электроду мемристора подсоединен резистор, образующий с мемристором, выполняющим функцию второго резистивного плеча, дополнительный резистивный делитель, выход которого подключен к неинвертирующим входам обоих дифференциальных усилителей в указанных группах, входящие в состав обоих резистивных делителей в указанных группах резисторы с их подключением к соответствующим источникам постоянного напряжения имеют сопротивления, равные сопротивлениям мемристора в высокоомном или низкоомном состоянии, а оба реостата имеют настройку своих граничных величин сопротивления больше величины сопротивления мемристора в высокоомном состоянии и меньше величины сопротивления мемристора в низкоомном состоянии.

| US 9837147 B2, 05.12.2017 | |||

| US 9847128 B2, 19.12.2017 | |||

| US 9343145 B2, 17.05.16 | |||

| МАГНИТОЭЛЕКТРИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2573207C2 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

Авторы

Даты

2021-03-04—Публикация

2019-12-10—Подача