Изобретение относится к области электротехники и микроэлектроники, касается устройства программирования резистивных состояний мемристорных элементов, которое может быть использовано в составе микросхем различного функционального назначения.

Известно устройство для регулирования импульсов переключения мемристора, содержащее источник напряжения, детектор напряжения для обнаружения напряжения мемристора. В детекторе напряжение мемристора основано на начальном сопротивлении мемристора и напряжении, подаваемом источником напряжения. Компаратор в данном устройстве служит для сравнения напряжения мемристора с контрольной величиной напряжения мемристора, причем последняя используется для регулирования импульса переключения мемристора. Контур обратной связи служит для передачи значения напряжения на управляющий переключатель. Управляющий переключатель используется для автоматического отключения и отсоединения мемристора от источника напряжения, когда напряжение на мемристоре, по меньшей мере, равно контрольной величине напряжения (US 9837147 В2, кл. G11C13/00, G11C27/02, опубл. 05.12.2017 г.). Данное изобретение представляет собой схему для генерирования импульса напряжения, настраиваемого в зависимости от ряда характеристик мемристора, таких как начальное значение сопротивления тестируемого мемристорного устройства. Это устройство может использоваться для регулирования импульсов переключения мемристоров в схемах тестирования или как часть схемы записи.

Недостатком схемы является необходимость в вычислении сопротивления мемристора в процессе программирования.

Известно устройство для переключения мемристора (RU 2744246 С1, кл. H01L45/00, G11C11/02, опубл. 04.03.2021 г.), содержащее два источника постоянного напряжения, с противоположной друг к другу полярностью, два реостата, два резистивных делителя и два дифференциальных усилителя напряжения, образующие по одному две группы элементов для переключения мемристора в высокоомное или низкоомное состояние. Устройство может быть применимо для автоматического переключения и стабильного перевода мемристора (не зависящего от напряжения питания и предыстории работы мемристора) в высокоомное или низкоомное состояние.

Наиболее близким по технической сущности к предлагаемому устройству программирования резистивных состояний мемристорных элементов является устройство для управления работой мемристора, защищенное патентом RU 2737794 C1, кл. H01L45/00, G11C11/02, опубл. 03.12.2020 г., принятое за ближайший аналог (прототип).

Устройство по прототипу содержит два источника постоянного напряжения с противоположной друг к другу полярностью, два ключа, два резистивных делителя и два компаратора, образующие по одному две группы элементов для переключения мемристора в высокоомное или низкоомное состояние.

Недостатком приведенных выше устройств является необходимость использования нескольких коммутаторов и использование в качестве выходной величины падения напряжения на мемристоре, которое в свою очередь, зависит от значения входного напряжения программирования и сопротивления мемристора. В процессе программирования требуется управление двумя источниками напряжения и вычисление сопротивления мемристора.

В задачу изобретения положено разработка устройства программирования резистивных состояний мемристорных элементов, не требующего вычисления сопротивления мемристора в процессе программирования.

Техническим результатом от использования предлагаемого изобретения является повышение универсальности схемы устройства, упрощение его схемотехнической реализации.

Технический результат изобретения достигается тем, что в устройство программирования резистивных состояний мемристорных элементов, содержащее блок управления напряжением, биполярный источник напряжения, операционный усилитель с программируемым мемристором в цепи обратной связи и компаратор на выходе схемы, добавляется идентичный первому канал операционного усилителя с эталонным переменным резистором в цепи обратной связи.

Это достигается тем, что устройство программирования резистивных состояний мемристорных элементов содержит блок управления напряжением, биполярный источник напряжения, два резистора, два операционных усилителя, программируемый мемристор, эталонный переменный резистор, компаратор, в котором первый резистор выполнен на входе канала первого операционного усилителя, второй резистор выполнен на входе канала второго операционного усилителя, в цепи обратной связи первого операционного усилителя выполнен программируемый мемристор, в цепи обратной связи второго операционного усилителя выполнен эталонный переменный резистор, при этом блок управления напряжением соединен с биполярным источником напряжения, биполярный источник напряжения соединен с первым резистором на входе канала первого операционного усилителя и со вторым резистором на входе канала второго операционного усилителя, на выходе каналов операционных усилителей установлен компаратор.

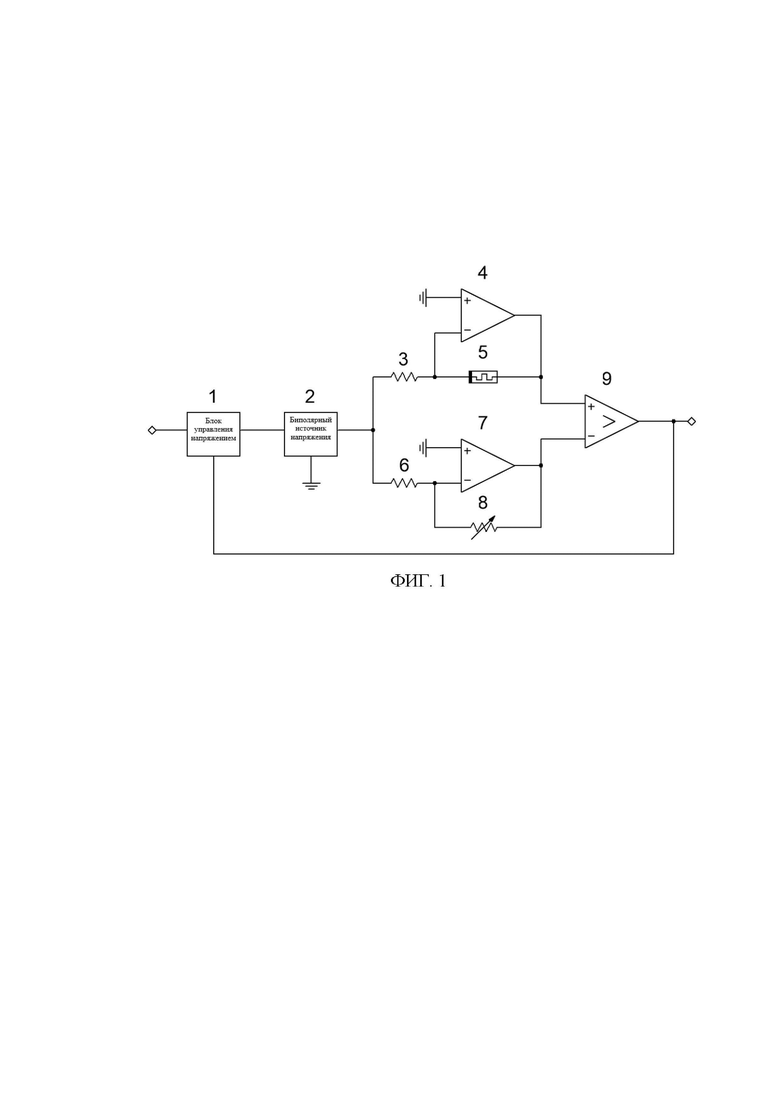

На фиг. 1 представлена схема устройства программирования резистивных состояний мемристорных элементов.

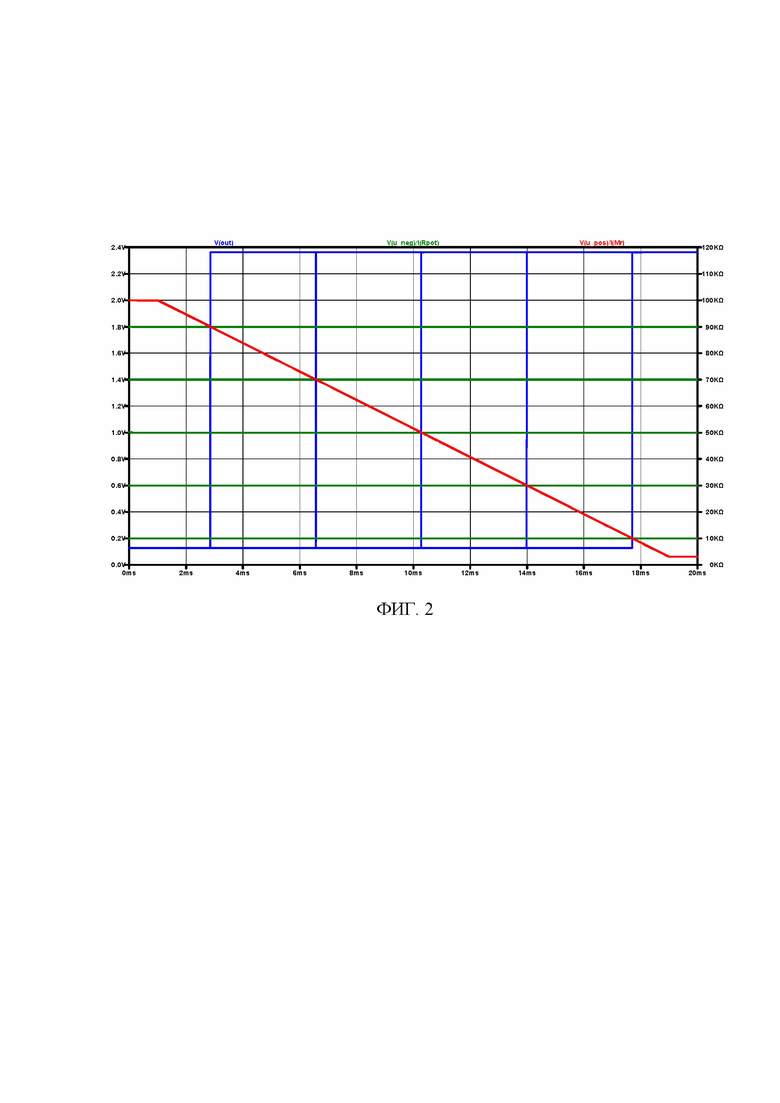

На фиг. 2 показано семейство графиков, демонстрирующих работу устройства программирования в соответствии с примером 1.

Конструктивно устройство программирования резистивных состояний мемристорных элементов на фиг. 1 содержит:

1 - блок управления напряжением;

2 - биполярный источник напряжения;

3, 6 - резисторы;

4, 7 - операционные усилители;

5 - программируемый мемристор;

8 - эталонный переменный резистор;

9 - компаратор.

Блок управления напряжением 1 соединен с биполярным источником напряжения 2.

Биполярный источник напряжения 2 соединен с первым резистором 3 на входе канала первого операционного усилителя 4 и со вторым резистором 6 на входе канала второго операционного усилителя 7.

Первый резистор 3 выполнен на входе канала первого операционного усилителя 4.

Второй резистор 6 выполнен на входе канала второго операционного усилителя 7.

В цепи обратной связи первого операционного усилителя 4 выполнен программируемый мемристор 5.

В цепи обратной связи второго операционного усилителя 7 выполнен эталонный переменный резистор 8.

На выходе каналов операционных усилителей 4 и 7 установлен компаратор 9.

Предлагаемое устройство программирования резистивных состояний мемристорных элементов работает следующим образом.

Процесс программирования начинается со сброса программируемого мемристора 5 в высокоомное состояние. После чего осуществляется настройка на нужное сопротивление переменного резистора 8. Это сопротивление будет иметь программируемый мемристор 5 по окончании процесса программирования. Блок управления 1 контролирует и перестраивает напряжение биполярного источника напряжения 2 в зависимости от выходного напряжения компаратора 9. Затем на выходе биполярного источника напряжения 2 формируется последовательность импульсов или линейно нарастающее напряжение. При этом, в цепи первого операционного усилителя 4 через программируемый мемристор 5 будет протекать постепенно нарастающий ток, а проводимость мемристора будет увеличиваться. В момент, когда внутреннее сопротивление программируемого мемристора 5 окажется равным сопротивлению эталонного переменного резистора 8, напряжение на выходе первого канала операционного усилителя 4 превысит напряжение на выходе второго канала операционного усилителя 7. Тогда компаратор 9 переключится, а его выходное напряжение сменит полярность. Это будет являться критерием завершения процесса программирования.

Применение в данной схеме двухполярного источника напряжения и операционного усилителя позволяет осуществить программирование мемристора любого типа, как понижающего сопротивление (переход SET), так и повышающего сопротивление (переход RESET), а также перевод мемристора в любое состояние без его перекоммутации или сброса в начальное состояние.

Предложенное схемотехническое решение позволяет уменьшить число электронных компонентов по сравнению с устройствами в изобретениях по патентам РФ № 2744246 и № 2737794. В предлагаемой схеме нет необходимости применения резистивных делителей, ключей или реостатов, а также нескольких компараторов. Все это упрощает схемотехническую реализацию и повышает универсальность устройства.

В разработанном устройстве нет необходимости использования измерительного оборудования для получения информации о предыстории работы мемристора и зависимости сопротивления мемристора от протекшего через него заряда, что повышает технологичность устройства по сравнению с изобретением по патенту US 9837147.

Ниже представлен пример конкретного осуществления предлагаемого изобретения.

Пример 1.

При реализации устройства программирования использовали ЦАП повышенной разрядности, с возможностью формирования двухполярного напряжения на выходе LTC2641AIDD-14#PBF. Этот ЦАП требует внешнего источника опорного напряжения (ИОН) напряжением 2,048 В, который объединен с ИОН приемного канала. Для компактной реализации устройства использовали мультиплексор, а не набор SPST-ключей. Выбор именно мультиплексора позволил сэкономить на количестве управляющих сигналов, т.к. в составе мультиплексоров присутствует дешифратор. В результате был выбран мультиплексор ADG1606. Этот вариант удобнее тем, что предназначен для двухполярного питания и не требует дополнительного преобразователя уровня управляющих сигналов. Выходные сигналы четырех мультиплексоров объединяются с помощью ADG1612. В качестве потенциометра выбрали микросхему AD5271BRMZ-100, представляющую собой цифровой потенциометр с максимальным сопротивлением 100 кОм и управлением посредством последовательного интерфейса. Микросхема специфицирована для напряжения питания ±2,5 В. Ее и использовали в конструкции.

На фиг. 2 показано семейство графиков, демонстрирующих работу устройства программирования при вариации сопротивления аттенюатора в диапазоне от 10 до 90 кОм с шагом 20 кОм. Выходной сигнал компаратора - «Vout», показан синим. В начальном состоянии оно равно логическому нулю. По мере уменьшения сопротивления мемристора, в момент равенства его сопротивления сопротивлению аттенюатора, компаратор меняет логическое состояние, сигнализируя о завершении процедуры и необходимости снятия тока программирования. Моменты срабатывания компаратора оказываются точно в момент равенства сопротивлений мемристора и аттенюатора во всем диапазоне вариабельных значений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ генерации случайных чисел с помощью мемристорного источника стохастических сигналов и устройство для его осуществления | 2021 |

|

RU2787560C1 |

| 3D запоминающая матрица на основе комплементарной мемристорно-диодной ячейки | 2017 |

|

RU2697623C2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ОДНОЭЛЕКТРОННЫЙ МЕМРИСТОР (НАНОЯЧЕЙКА) И СПОСОБ ПРИМЕНЕНИЯ | 2023 |

|

RU2823967C1 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ДАТЧИКОВ | 2022 |

|

RU2795214C1 |

| Способ управления работой мемристора и устройство для его осуществления | 2019 |

|

RU2737794C1 |

| Устройство для переключения мемристора | 2019 |

|

RU2744246C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2005 |

|

RU2292051C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2010 |

|

RU2499237C2 |

Изобретение относится к области электротехники и микроэлектроники. Техническим результатом является повышение универсальности схемы устройства, упрощение его схемотехнической реализации. Для этого устройство содержит блок управления напряжением, биполярный источник напряжения, два резистора, два операционных усилителя, программируемый мемристор, эталонный переменный резистор, компаратор. Первый резистор выполнен на входе канала первого операционного усилителя. Второй резистор выполнен на входе канала второго операционного усилителя. В цепи обратной связи первого операционного усилителя выполнен программируемый мемристор. В цепи обратной связи второго операционного усилителя выполнен эталонный переменный резистор. При этом блок управления напряжением соединен с биполярным источником напряжения. Биполярный источник напряжения соединен с первым резистором на входе канала первого операционного усилителя и со вторым резистором на входе канала второго операционного усилителя. На выходе каналов операционных усилителей установлен компаратор. 2 ил., 1 пр.

Устройство программирования резистивных состояний мемристорных элементов содержит блок управления напряжением, биполярный источник напряжения, два резистора, два операционных усилителя, программируемый мемристор, эталонный переменный резистор, компаратор, в котором первый резистор выполнен на входе канала первого операционного усилителя, второй резистор выполнен на входе канала второго операционного усилителя, в цепи обратной связи первого операционного усилителя выполнен программируемый мемристор, в цепи обратной связи второго операционного усилителя выполнен эталонный переменный резистор, при этом блок управления напряжением соединен с биполярным источником напряжения, биполярный источник напряжения соединен с первым резистором на входе канала первого операционного усилителя и со вторым резистором на входе канала второго операционного усилителя, на выходе каналов операционных усилителей установлен компаратор.

| Способ управления работой мемристора и устройство для его осуществления | 2019 |

|

RU2737794C1 |

| US 9837147 B2, 05.12.2017 | |||

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| Устройство для переключения мемристора | 2019 |

|

RU2744246C1 |

Авторы

Даты

2023-05-02—Публикация

2022-12-21—Подача