Группа изобретений относится к мемристорной технологии генерации случайных чисел и может быть использована в широком спектре приложений для обеспечения безопасности современного цифрового оборудования в связи с полезными свойствами мемристоров, включающими их низкое энергопотребление, большую скорость переключения и высокую масштабируемость.

Работа генераторов случайных чисел на мемристорах со структурой «металл-оксид-металл», представляющих собой новую разновидность аналоговых генераторов случайных чисел, основана на использовании мемристорных источников стохастических сигналов, возникающих в связи с естественным случайным характером переключения мемристоров в проводящее состояние (при подаче на них импульсов напряжения их переключения из высокоомного в низкоомное состояние) в результате формирования проводящих каналов (филаментов) в расположенной между мемристорными электродами наноразмерной активной среде, и последующей обработке указанных стохастических сигналов в соответствии с алгоритмом формирования из них последовательности случайных чисел.

Актуальность разработки таких генераторов случайных чисел подтверждается всплеском интереса к созданию аппаратных систем информационных баз на основе мемристоров со стороны ведущих мировых научных групп (см. статьи на англ. яз. авторов Y. Pang and other «Memristors for Hardware Security Applications». Adv. Electron. Mater, 2019, p.1800872 и авторов R. Carboni, D. Ielmini «Stochastic Memory Devices for Security and Computing». Adv. Electron. Mater, 2019, p.1900198).

Уровень техники в области мемристорной технологии генерации случайных чисел характеризуется генераторами случайных чисел на мемристорах, характеризующихся особенностями подготовки (съема и преобразования) самих стохастических сигналов из мемристорных источников.

Так, известен генератор случайных чисел с мемристорным источником стохастических сигналов (см. заявку на изобретение «True random number generator (TRNG) circuit using a diffusive memristor» US201903031041, G06F7/58, G06F7/58, H01L45/00, H03K3/84, 2019) выполненный в виде энергозависимого мемристора, выдающего снимаемый с него стохастически переключаемый выходной сигнал в связи со случайным временем задержки порогового переключения этого мемристора с последующими преобразованием компаратором этого сигнала в сигнал со случайной шириной импульса и синхронной логической обработкой последнего перед входом в схему счетчика, генерирующего выходной сигнал случайной последовательности битов, которая выдержала все 15-ть статистических тестов NIST (National Institute of Standards and Technology, США) для проверки случайности генерируемых величин.

Основным недостатком этого аналога является усложнение подготовки самого стохастического сигнала, вырабатываемого мемристорным источником, состоящим из одного энергозависимого мемристора, из-за выбора в качестве указанного стохастического сигнала непосредственно времени задержки переключения мемристора и необходимости его преобразования в сигнал со случайной шириной импульса.

Еще более усложнена мемристорная технология генерации случайных чисел в статьях на англ. яз. авторов Balatti S. and other «Physical unbiased generation of random numbers with coupled resistive switching devices». Electron Devices, 2016, v. 63, p. 2029 и авторов Teng Zhang and other «High-speed true random number generation based on paired memristors for security». Electronics Nanotechnology, 2017, v. 2, p. 455202, в которых предлагается подготовка стохастических сигналов мемристорных источников на основе съема разницы стохастики, соответственно, по очереди и вариативно-усложненно переключаемых двух независимых мемристоров (при вариации параметров резистивного переключения, например, таких как напряжение переключения между резистивными состояниями при вариации от цикла к циклу переключения, а также от мемристора к мемристору, а также сопротивление в различных резистивных состояниях).

Вариативность параметров переключения мемристоров и возможность многоуровневого изменения резистивного состояния были использованы при реализации базового элемента аппаратной защиты с использованием двухслойного массива 10×10 металл-оксидных мемристоров в топологии «кросс-бар» (см. статью на англ. яз. авторов H. Nili and other «Hardware-intrinsic security primitives enabled by analogue state and nonlinear conductance variations in integrated memristors». Nature Electronics, 2018, v. 1, p. 197-202). Реализация основных криптографических функций таких массивов мемристоров выглядит следующим образом. На несколько строк матрицы мемристоров подается напряжение, а затем производится сравнение токов, текущих в одной половине столбцов, с токами, текущими в другой половине столбцов. Если ток, например, левой группы столбцов выше, чем ток правой, то на однобитовом выходе фиксируется значение «1», если ниже, то «0». В дальнейшем эти величины преобразуются в последовательности сигналов, которые могут служить в качестве ключа шифрования.

Известен другой подход, который состоит в использовании шумов и флуктуаций тока в каком-либо резистивном состоянии, в основном - в высокопроводящем состоянии (см. инф. материал на англ. яз. авторов Nikolaos Vasileiadis and other «Random Number Generator Based on Multi-State Silicon Nitride Memristor Entropy Sources Combination». Proc. IEEE International Conference on Electronics, Information, and Communication (ICEIC), 2021).

К общим недостаткам рассмотренных аналогов реализации генераторов случайных чисел на мемристорах относятся сложность обслуживающих схем, включающих счетчики, компараторы, ключи и специальные логические схемы (см. инф. материал на англ. яз. авторов Nikolaos Vasileiadis and other «Random Number Generator Based on Multi-State Silicon Nitride Memristor Entropy Sources Combination». Proc. IEEE International Conference on Electronics, Information, and Communication (ICEIC), 2021) или необходимость организации программирования и считывания состояний в больших массивах мемристоров (см. статью на англ. яз. авторов H. Nili and other «Hardware-intrinsic security primitives enabled by analogue state and nonlinear conductance variations in integrated memristors». Nature Electronics, 2018, v. 1, p. 197-202).

При этом, когда для генерации случайных чисел используется сравнение параметра переключения со средним значением, требуется тонкий подбор порога срабатывания компаратора для обеспечения равных вероятностей генерации значений «1» и «0» (см. инф. материал на англ. яз. авторов Nikolaos Vasileiadis and other «Random Number Generator Based on Multi-State Silicon Nitride Memristor Entropy Sources Combination». Proc. IEEE International Conference on Electronics, Information, and Communication (ICEIC), 2021).

Недостатком упомянутых схем на основе спаренных мемристоров (см. статьи на англ. яз. авторов Balatti S. and other «Physical unbiased generation of random numbers with coupled resistive switching devices». Electron Devices, 2016, v. 63, p. 2029 и авторов Teng Zhang and other «High-speed true random number generation based on paired memristors for security». Electronics Nanotechnology, 2017, v. 2, p. 455202) является также то, что для генерации случайных чисел используется пара мемристоров с подачей электрических импульсов на каждый из них независимо, после чего проводится сравнение полученных значений сопротивления с заданной величиной, что также может приводить к отклонениям от равновероятного распределения сгенерированных случайных чисел и требует их дополнительной корректировки с использованием специальных схем.

В связи с отсутствием источников информации, содержащих близкую по механизму подготовку стохастических сигналов, которая в предлагаемых способе и устройстве для его осуществления предусматривает совместное одновременное участие двух или более запаралеленных мемристоров в расширении стохастических возможностей на основе качественно новой простой и эффективной конкуренции автономных стохастик этих мемристоров (когда филаментарный механизм автономного переключения каждого мемристора обеспечивает случайное равновероятное переключение в проводящее состояние одного из двух или более мемристоров при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения) заявителем выбрана форма раскрытия сущности заявляемых способа и устройства для его осуществления без прототипа.

Технический результат от использования предлагаемых способа генерации случайных чисел с помощью мемристорного источника стохастических сигналов и устройства для его осуществления - упрощение подготовки стохастических сигналов и повышение эффективности и технологичности формирования последовательности случайных чисел за счет возможности формирования разрядов битов на основе изменения количества мемристоров.

Для достижения указанного технического результата предлагаются

способ генерации случайных чисел, включающий использование мемристорного источника стохастических сигналов и обработку последних в соответствии с алгоритмом формирования из них последовательности случайных чисел, характеризующийся тем, что в качестве мемристорного источника стохастических сигналов используют параллельно соединенные мемристоры, максимально приближенные друг к другу по рабочим характеристикам их переключения из высокоомного в низкоомное состояние, в количестве, как минимум двух, и обеспечивающие возможность съема указанных стохастических сигналов в виде значений тока, протекающего через один мемристор, после случайного равновероятного переключения в проводящее состояние одного из указанных мемристоров при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения,

и устройство для изложенной генерации случайных чисел, содержащее мемристорный источник стохастических сигналов и подключенный к нему модуль обработки указанных стохастических сигналов в соответствии с алгоритмом формирования из них последовательности случайных чисел, характеризующийся тем, что мемристорный источник стохастических сигналов выполнен в виде параллельно соединенных мемристоров, максимально приближенных друг к другу по рабочим характеристикам их переключения из высокоомного в низкоомное состояние, в количестве, как минимум двух, и оснащен блоком одновременной подачи на указанные мемристоры серии импульсов напряжения их переключения, а модуль обработки указанных стохастических сигналов снабжен блоком считывания сигналов указанного переключения, снимаемых на выходе случайно включаемого одного из них при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения.

В частном случае выполнения мемристорного источника стохастических сигналов в виде трех параллельно соединенных мемристоров, имеющих структуру Au/Zr/ZrO2(Y)/TiN/Ti, максимально приближенных друг к другу по рабочим вольт-амперным характеристикам их переключения из высокоомного в низкоомное состояние, блок одновременной подачи на указанные мемристоры серии импульсов напряжения их переключения выполнен трехканальным, в каждом канале которого смонтированы последовательно соединенные масштабирующий усилитель и ограничитель обратного тока мемристора, соединенные на канальном входе с цифро-аналоговым преобразователем (ЦАП) и подключенные на канальном выходе с многоканальным входом мультиплексора настройки топологии цепи одновременной подачи на входы указанных мемристоров серии импульсов напряжения их переключения, а модуль обработки указанных стохастических сигналов в соответствии с алгоритмом формирования из них последовательности случайных чисел, снабженный блоком считывания сигналов указанного переключения, снимаемых на выходе случайно включаемого первого из них при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения, выполнен в виде одноканальной измерительной цепи, в которой смонтированы последовательно соединенные инвертирующий и масштабирующий усилители, соединенные на входе этой цепи с выходами мемристоров в составе мемристорного источника стохастических сигналов, подключенными на выходе этой цепи к аналого-цифровому преобразователю (АЦП) в составе контроллера, включенного в интерфейс «компьютер-контроллер» и подключенного с помощью цепи управления к входу указанного мультиплексора.

При этом для предэксплуатационной настройки мемристоров в составе мемристорного источника стохастических сигналов в связи возможными технологическими расхождениями в напряжениях переключения указанные мемристоры могут быть снабжены последовательными подстроечными резисторами.

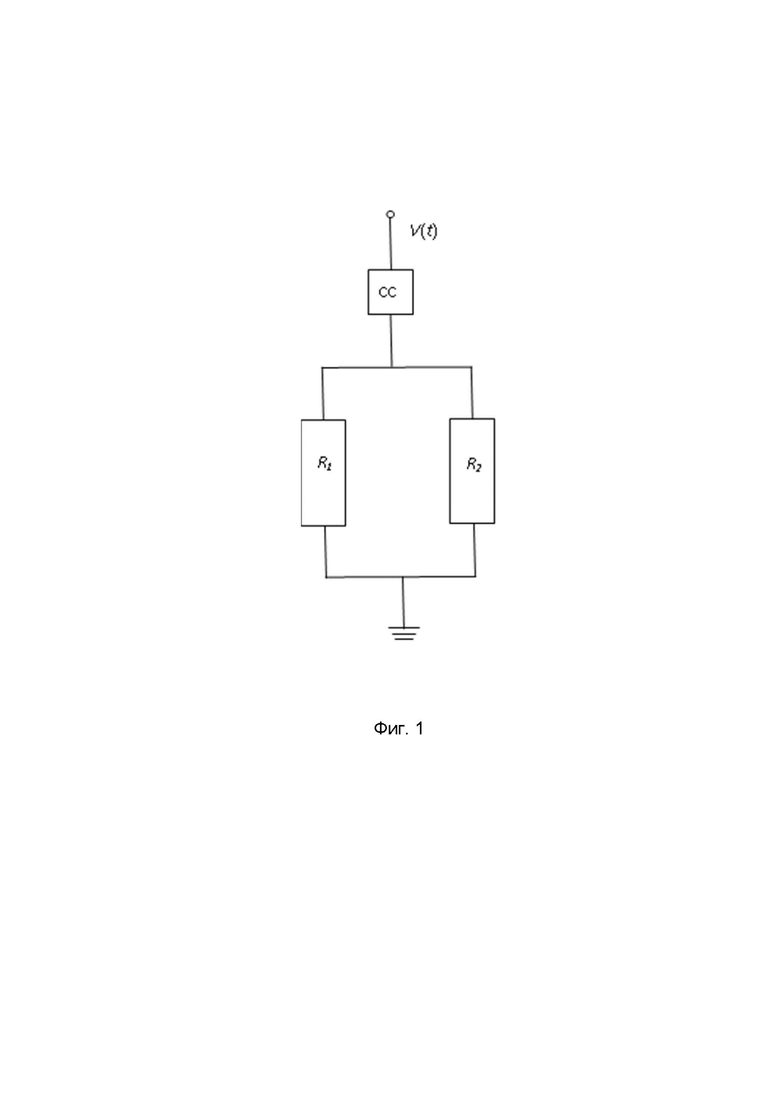

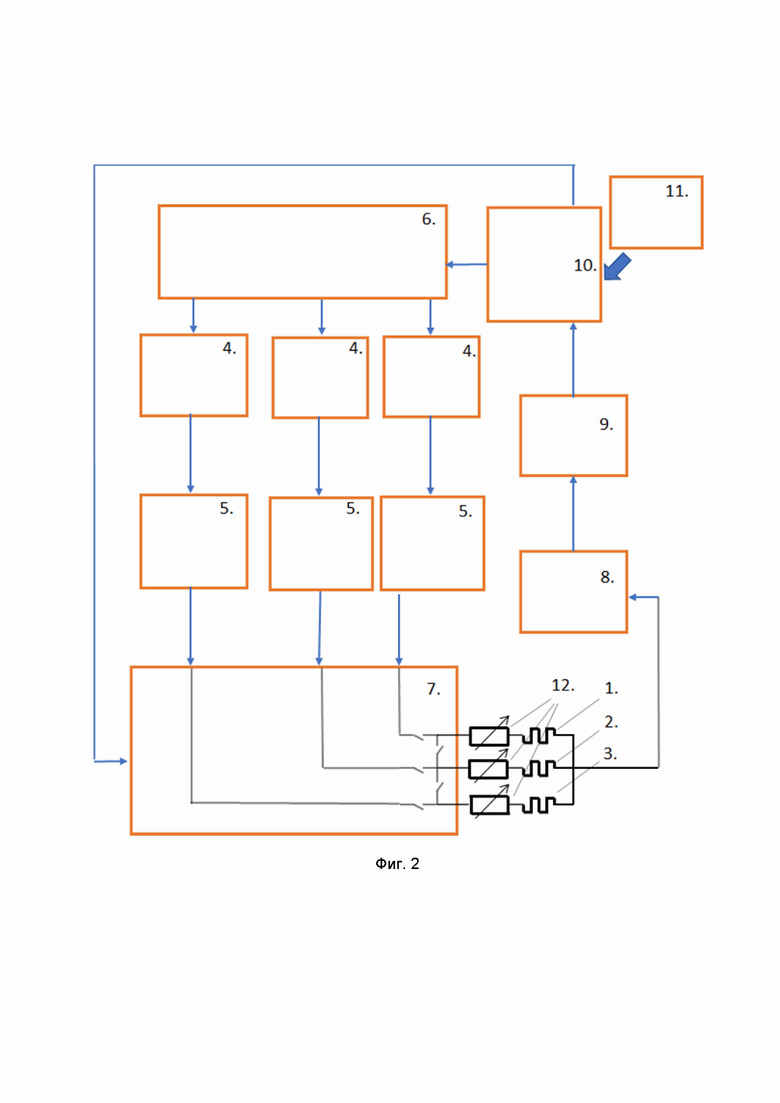

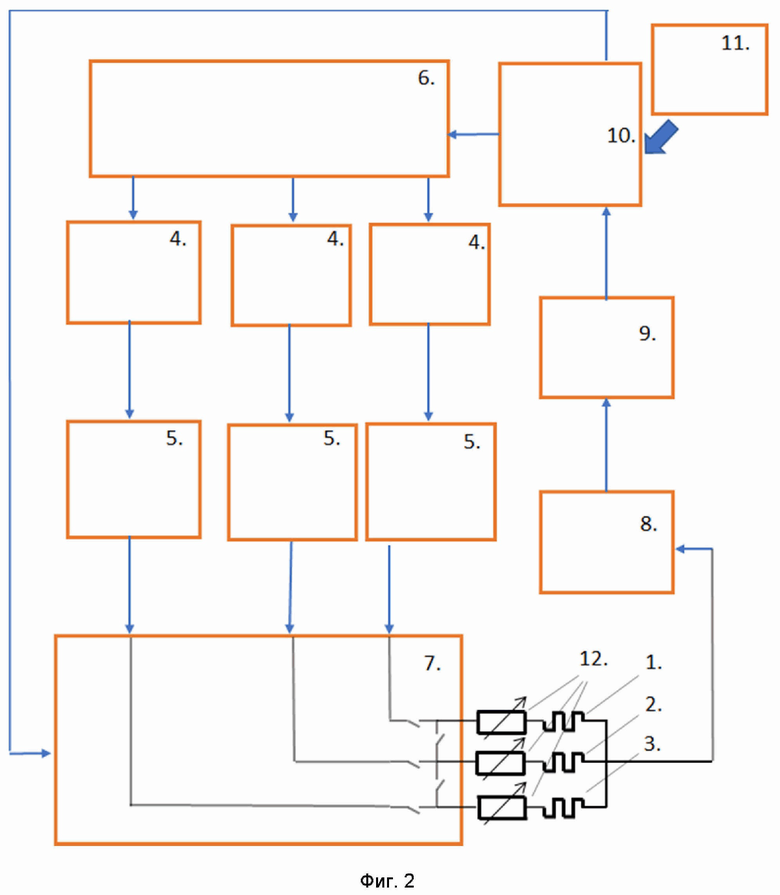

На фиг.1 показана принципиальная схема мемристорного источника стохастических сигналов, поясняющая на примере исполнения указанного источника на 2-х мемристорах механизм работы устройства для осуществления предлагаемого способа генерации случайных чисел; на фиг.2 - блок-схема устройства для осуществления предлагаемого способа генерации случайных чисел с мемристорным источником стохастических сигналов, выполненным на 3-х мемристорах.

*Предлагаемый способ генерации случайных чисел включает использование мемристорного источника стохастических сигналов, выполненного в виде параллельно соединенных мемристоров, максимально приближенных друг к другу по рабочим характеристикам их переключения из высокоомного в низкоомное состояние, в количестве, как минимум двух (в примере выполнения в количестве трех мемристоров), и обеспечивающих возможность съема указанных стохастических сигналов в виде сигналов указанного переключения одного мемристора на выходе случайно включаемого первого из них при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения, и последующую обработку адресно снимаемых стохастических сигналов с мемристоров в соответствии с алгоритмом формирования из указанных сигналов последовательности случайных чисел, причем количество упомянутых мемристоров может быть два, три, четыре, восемь, шестнадцать и иное количество в зависимости от алгоритма указанного формирования.

При этом принцип осуществления предлагаемого способа можно рассмотреть на примере использования мемристорного источника стохастических сигналов на двух параллельных мемристорах с текущими значениями сопротивлений и R2 (см. фиг. 1), подключенных к источнику внешнего напряжения через ограничитель тока «СС» (фиг. 1).

Напряжение, падающее на мемристорах, описывается следующим выражением

где V - напряжение на мемристорах, R1 и R2 - сопротивления мемристоров 1 и 2, а I=Vin (R1+R2)/(R1R2) - ток в цепи, Iсс - ток ограничения.

Сопротивление мемристора может изменяться под действием внешнего напряжения в том случае, если оно превышает значение напряжения переключения SET (порога) Vth. Так как в мемристорах процессы переключения имеют случайный характер, то даже при одновременном воздействии на оба мемристора напряжения V ≥ Vth, один из мемристоров может переключиться раньше другого.

Приведем пример работы данного устройства при правильном выборе параметров схемы. Допустим, что на систему подается внешнее напряжение Vin в виде прямоугольных импульсов, а мемристоры в начальный момент находятся в состоянии с одинаковым сопротивлением R1 = R2 = R, таким, что ток, протекающий через ограничитель тока СС, не превышает Icc. Тогда, согласно (1), напряжение на мемристорах равно внешнему напряжению V = Vin. Пусть при достижении порога Vin = Vth мемристор 1 переключается и уменьшает свое сопротивление так, что ток в цепи I = Vin⋅(R1 + R2)/(R1R2) достигает величины тока ограничения. В таком случае напряжение V на мемристорах падает ниже порогового значения Vth при любом значении Vin, и мемристор 2 уже не может переключиться. Далее с помощью импульса инициализации (RESET) система возвращается в исходное состояние, и процесс повторяется. При этом вследствие случайности процесса переключения первым может переключиться уже мемристор 2. Таким образом реализуется генерация случайных чисел на схеме с двумя мемристорами по принципу «победитель забирает все».

В случае выполнения мемристорного источника стохастических сигналов (см. фиг. 2) в виде трех параллельно соединенных мемристоров 1-3, имеющих структуру Au/Zr/ZrO2(Y)/TiN/Ti, максимально приближенных друг к другу по рабочим вольт-амперным характеристикам их переключения из высокоомного в низкоомное состояние,

блок одновременной подачи на указанные мемристоры серии импульсов напряжения их переключения выполнен трехканальным, в каждом канале которого смонтированы последовательно соединенные масштабирующий усилитель 4 и ограничитель обратного тока мемристора 5, соединенные на канальном входе с ЦАП 6 и подключенные на канальном выходе с многоканальным входом мультиплексора 7 для настройки топологии цепи одновременной подачи на входы указанных мемристоров серии импульсов напряжения их переключения, а модуль обработки указанных стохастических сигналов в соответствии с алгоритмом формирования из них последовательности случайных чисел, снабженный блоком считывания сигналов указанного переключения, снимаемых на выходе случайно включаемого первого из них при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения, выполнен в виде одноканальной измерительной цепи, в которой смонтированы последовательно соединенные инвертирующий и масштабирующий усилители 8 и 9, соединенные на входе этой цепи с выходами мемристоров 1-3 в составе мемристорного источника стохастических сигналов подключенными на выходе этой цепи через инвертирующий и масштабирующий усилители к АЦП контроллера 10 (с функцией считывания сигналов переключения, снимаемых на выходе случайно включаемого одного из мемристоров 1-3 при одновременной подаче на них серии импульсов напряжения их переключения), включенного в интерфейс «компьютер-контроллер» 11 и подключенного с помощью цепи управления к входу мультиплексора 7.

При этом для предэксплуатационной настройки мемристоров 1-3 в составе мемристорного источника стохастических сигналов указанные мемристоры снабжены подстроечными резисторами 12

последовательно подключенными к ним с возможностью предэксплуатационной компенсации технологических расхождений в напряжениях переключения этих мемристоров.

Входящие в состав изложенного устройства составляющие имеют особенности выполнения.

Интерфейс 11, реализован при помощи адаптера USB-UART (CP2102). Обеспечивает возможность управления устройством через специальную desktop-программу (разработана в среде Qt Creator).

8-ми битный контроллер 10 фирмы Atmel Atmega328p со встроенным 10-ти битным АЦП. Используется для управления периферийными узлами устройства.

Восьмиканальный 12-ти битовый ЦАП 6 фирмы Analog Devices AD5308.

Масштабирующий усилитель напряжения 4 на основе мощностного операционного усилителя TCA0372. Используется для преобразования исходного униполярного маломощного сигнала отдельного канала ЦАП 6 в достаточно мощный (номинальный максимальный выходной ток ОУ - 1 А) биполярный сигнал, способный производить настройку состояния мемристоров 1-3 в широких пределах.

Ограничитель обратного тока мемристора 5 (ограничение до 250 мкА). Используется для безопасного управления мемристорами 1-3. Состоит из диода Шоттки (1PS76SB10, 115) и p-канального jFET (MMBFJ177);

Мультиплексор 7 на основе аналоговых 4-х канальных ключей DG445DY. Позволяет менять топологию цепи, переходя от цепи обычного конфигуратора к цепи мемристорного источника стохастических сигналов.

Подстроечные резисторы 12, элементы для предэскплуатационной настройки мемристоров 1-3, имеющих технологические отклонения от номинала вольтамперной характеристики (последовательные сопротивления).

Инвертирующий усилитель 8 на основе ОУ TCA0372. Обеспечивает суммирование токов всех используемых каналов одновременной подачи на мемристоры 1-3 серии импульсов напряжения их переключения.

Масштабирующий усилитель напряжения 9 на основе прецизионного усилителя фирмы National Instruments, используемый для перевода измеряемого биполярного сигнала в маломощный униполярный с диапазоном напряжений, приемлемым для встроенного в контроллер 10 АЦП.

Управление устройством для осуществления предлагаемого способа в примере выполнения производится с компьютера через специальную desktop-программу, разработанную в среде Qt Creator. Программа позволяет переключаться между режимами управления мемристорами 1-3 (режим измерения вольт-амперной характеристики мемристоров 1-3, режим задания целевого сопротивления и режим генерации случайных значений). Режим измерения вольт-амперной характеристики указанной программой производится путем подачи пилообразного напряжения на вход отдельных мемристоров 1-3.

Причем, значения максимума и минимума входного напряжения могут быть изменены непосредственно во время измерения вольт-амперной характеристики мемристоров 1-3. Такой подход измерения оказывает воздействие на состояния проводимости мемристора, что позволяет, в конечном счете, получить ярко выраженную гистерезисную картину, а также повлиять на состояния ветвей гистерезиса. Режим указанной программы для задания целевого сопротивления основывается на следующей идее: достаточно большим отрицательным импульсом напряжения (3-8 В) устанавливается открытое состояние мемристора (ON), далее подается последовательная серия возрастающих положительных импульсов, каждый из которых уменьшает текущее значение проводимости мемристоров 1-3, приближая его к целевому, что контролируется путем повторяющихся измерений проводимости. Наконец, режим генерации случайных значений проводимости выполняется путем чередования 2-х коммутационных режимов при помощи мультиплексора 7. Режим мультиплексации обеспечивает общее соединение между входами мемристоров 1-3, а также последовательное соединение этих мемристоров, каждого со своим резистором 12. На выведенные в закрытое состояние (OFF) мемристоры 1-3 приходит общий отрицательный импульс, переводя один из трех мемристоров в открытое состояние так, что с учетом ограничения тока на ограничителе тока 5 остальные мемристоры шунтируются открывшимся и, таким образом, остаются закрытыми. Номер случайно открытого мемристора в таком случае и есть случайное число, сгенерированное устройством.

Реализация интерфейса «компьютер-контроллер» 11 выполнена за счет адаптера USB-UART (CP2102). Команды, отправляемые описываемому устройству, поступают на контроллер 10 Atmel Atmega328p при помощи встроенного в контроллер 10 uart-модуля (BAUDRATE = 115200). Таким образом в устройстве осуществляется переключение между режимами указанной ранее программы и отсылка измеренных величин тока этой программе. Измерение величины тока производится при помощи встроенного в контроллер 10 АЦП (10 бит). Подача импульсов напряжений на мемристоры 1-3 производится с помощью восьмиканального 12-ти битового ЦАП 6 фирмы Analog Devices AD5308, соединенного с контроллером 10 через SPI-интерфейс. ЦАП 6 представляет собой основное звено канала подачи на мемристоры 1-3 серии импульсов напряжения их переключения. Следующий элемент указанного канала - масштабирующий усилитель 4, выполненный на основе мощностного операционного усилителя TCA0372. Используется для преобразования исходного униполярного маломощного сигнала отдельного канала ЦАП 6 в достаточно мощный (номинальный максимальный выходной ток ОУ - 1 А) биполярный сигнал, способный производить настройку состояния мемристоров 1-3 в широких пределах. Полученный таким образом биполярный сигнал подается на ограничитель обратного тока мемристора 6 (ограничение до 250 мкА). Ограничитель 6 используется для безопасного управления мемристорами 1-3 и состоит из диода Шоттки (1PS76SB10, 115) и p-канального jFET (MMBFJ177). Каналы блока одновременной подачи на мемристоры 1-3 серии импульсов напряжения их переключения соединяются со входами мемристоров 1-3, мультиплексируясь с ними должным образом согласно режимам указанной выше программы. Токи всех этих каналов суммируются при помощи инвертирующего усилителя 8, реализованного за счет микросхемы TCA0372. Суммарный ток подлежит измерению при помощи АЦП, о чем упоминалось выше. Для измерения тока его значение масштабируется до приемлемого АЦП значения (используется прецизионный усилитель 9 фирмы National Instruments для перевода измеряемого биполярного сигнала в маломощный униполярный.

Изложенное позволяет сделать вывод в отношении предлагаемых способа и устройства для его осуществления о повышении эффективности генерации случайных чисел с помощью мемристоров в результате упрощения подготовки стохастических сигналов и повышения технологичности формирования последовательности случайных чисел за счет возможности формирования разрядов битов в связи с возможностью изменения количества мемристоров (наиболее оптимальным для современной микроэлектроники является количество мемристоров - 16).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство программирования резистивных состояний мемристорных элементов | 2022 |

|

RU2795273C1 |

| Способ переключения мемристора | 2022 |

|

RU2814564C1 |

| Устройство для переключения мемристора | 2019 |

|

RU2744246C1 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| МЕМРИСТОР НА ОСНОВЕ СМЕШАННОГО ОКСИДА МЕТАЛЛОВ | 2011 |

|

RU2472254C9 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| Способ получения активного слоя элемента энергонезависимой резистивной памяти | 2023 |

|

RU2812881C1 |

| Способ управления работой мемристора и устройство для его осуществления | 2019 |

|

RU2737794C1 |

| 3D запоминающая матрица на основе комплементарной мемристорно-диодной ячейки | 2017 |

|

RU2697623C2 |

| Способ формирования мемристивных структур на основе композитных оксидов с агломератами наночастиц | 2021 |

|

RU2767721C1 |

Изобретение относится к мемристорной технологии генерации случайных чисел. Технический результат - упрощение подготовки стохастических сигналов и повышение эффективности и технологичности формирования последовательности случайных чисел. Для достижения указанного технического результата предлагается использовать в качестве мемристорного источника стохастических сигналов параллельно соединённые мемристоры, имеющих структуру Au/Zr/ZrO2(Y)/TiN/Ti и максимально приближенные друг к другу по рабочим характеристикам их переключения из высокоомного в низкоомное состояние, в количестве, трех; трехканального блока одновременной подачи на указанные мемристоры серии импульсов напряжения, в каждом канале которого смонтированы последовательно соединённые масштабирующий усилитель и ограничитель обратного тока мемристора, соединённые на канальном входе с цифро-аналоговым преобразователем и подключённые на канальном выходе с многоканальным входом мультиплексора; модуля обработки указанных стохастических сигналов, снабжённого одноканальной измерительной цепью, в которой смонтированы последовательно соединённые инвертирующий и масштабирующий усилители. 2 н. и 1 з.п. ф-лы, 2 ил.

1. Способ генерации случайных чисел, включающий использование мемристорного источника стохастических сигналов и обработку последних в соответствии с алгоритмом формирования из них последовательности случайных чисел, характеризующийся тем, что в качестве мемристорного источника стохастических сигналов используют параллельно соединённые мемристоры, максимально приближенные друг к другу по рабочим характеристикам их переключения из высокоомного в низкоомное состояние, и с помощью которых осуществляют съём указанных стохастических сигналов в виде сигналов указанного переключения одного мемристора на выходе случайно включаемого первого из них при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения, отличающийся тем, что мемристорный источник стохатических сигналов выполнен в виде трёх параллельно соединённых мемристоров, имеющих структуру Au/Zr/ZrO2(Y)/TiN/Ti, максимально приближенных друг к другу по рабочим вольт-амперным характеристикам их переключения из высокоомного в низкоомное состояние, блок одновременной подачи на указанные мемристоры серии импульсов напряжения их переключения выполнен трёхканальным, в каждом канале которого смонтированы последовательно соединённые масштабирующий усилитель и ограничитель обратного тока мемристора, соединённые на канальном входе с цифро-аналоговым преобразователем и подключённые на канальном выходе с многоканальным входом мультиплексора настройки топологии цепи одновременной подачи на входы указанных мемристоров серии импульсов напряжения их переключения, а модуль обработки указанных стохастических сигналов в соответствии с алгоритмом формирования из них последовательности случайных чисел, снабжённый блоком считывания сигналов указанного переключения, снимаемых на выходе случайно включаемого первого из них при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения, выполнен в виде одноканальной измерительной цепи, в которой смонтированы последовательно соединённые инвертирующий и масштабирующий усилители, соединённые на входе этой цепи с выходами мемристоров в составе мемристорного источника стохатических сигналов и подключённые на выходе этой цепи к аналого-цифровому преобразователю в составе контроллера, включённого в интерфейс «компьютер-контроллер» и подключённого с помощью цепи управления к входу указанного мультиплексора.

2. Устройство для генерации случайных чисел по п. 1, содержащее мемристорный источник стохастических сигналов и подключённый к нему модуль обработки указанных стохастических сигналов в соответствии с алгоритмом формирования из них последовательности случайных чисел, характеризующийся тем, что мемристорный источник стохастических сигналов выполнен в виде параллельно соединённых мемристоров, максимально приближенных друг к другу по рабочим характеристикам их переключения из высокоомного в низкоомное состояние, и оснащён блоком одновременной подачи на указанные мемристоры серии импульсов напряжения их переключения, а модуль обработки указанных стохастических сигналов снабжён блоком считывания сигналов указанного переключения снимаемых на выходе случайно включаемого первого из них при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения, отличающееся тем, что мемристорный источник стохатических сигналов выполнен в виде трёх параллельно соединённых мемристоров, имеющих структуру Au/Zr/ZrO2(Y)/TiN/Ti, максимально приближенных друг к другу по рабочим вольт-амперным характеристикам их переключения из высокоомного в низкоомное состояние, блок одновременной подачи на указанные мемристоры серии импульсов напряжения их переключения выполнен трёхканальным, в каждом канале которого смонтированы последовательно соединённые масштабирующий усилитель и ограничитель обратного тока мемристора, соединённые на канальном входе с цифро-аналоговым преобразователем и подключённые на канальном выходе с многоканальным входом мультиплексора настройки топологии цепи одновременной подачи на входы указанных мемристоров серии импульсов напряжения их переключения, а модуль обработки указанных стохастических сигналов в соответствии с алгоритмом формирования из них последовательности случайных чисел, снабжённый блоком считывания сигналов указанного переключения, снимаемых на выходе случайно включаемого первого из них при одновременной подаче на эти мемристоры серии импульсов напряжения их переключения, выполнен в виде одноканальной измерительной цепи, в которой смонтированы последовательно соединённые инвертирующий и масштабирующий усилители, соединённые на входе этой цепи с выходами мемристоров в составе мемристорного источника стохатических сигналов и подключённые на выходе этой цепи к аналого-цифровому преобразователю в составе контроллера, включённого в интерфейс «компьютер-контроллер» и подключённого с помощью цепи управления к входу указанного мультиплексора.

3. Устройство по п. 2, отличающееся тем, что мемристоры в составе мемристорного источника стохастических сигналов снабжены подстроечными резисторами.

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

| Станок для придания концам круглых радиаторных трубок шестигранного сечения | 1924 |

|

SU2019A1 |

| US 8680906 B1, 25.03.2014 | |||

| Запоминающее устройство на основе комплементарной мемристорно-диодной ячейки | 2017 |

|

RU2649657C1 |

Авторы

Даты

2023-01-10—Публикация

2021-10-28—Подача