Область техники, к которой относится изобретение

Изобретение относится к области цифровой вычислительной техники и электроники, а именно к выбору способов построения цифровых микросхем, отказоустойчивых к облучению, и более точно относится к способам косвенного измерения отказоустойчивости испытательных резервированных цифровых микросхем при их облучении с целью получения экспериментальных оценок отказоустойчивости, которую могут обеспечить различные способы постоянного резервирования цифровых микросхем. Предлагаемый способ косвенного измерения должен позволить получить экспериментальные оценки отказоустойчивости, которые могут обеспечить способы мажоритарного резервирования микросхем при их облучении, сравнить эти экспериментальные оценки с теоретическими оценками, чтобы выбрать подходящий способ постоянного резервирования цифровых микросхем. Изобретение может найти применение для выбора подходящего способа постоянного резервирования микросхем при создании цифровых микросхем, отказоустойчивых к облучению.

Уровень техники

Под отказоустойчивостью микросхемы понимается ее способность выполнять заданные функции и выдавать верные результаты при отказах - постоянных и временных (т.е. при сбоях). Понятие отказоустойчивости нередко путают с надежностью и радиационной стойкостью. В книге Александрова П.А., Жука В.И. и Литвинова В.Л. «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением» (М.: Издательский дом «ПоРог», 2019) дан терминологический обзор понятия «отказоустойчивость» и отмечается, что для оценки отказоустойчивости микросхемы в отечественной литературе и за рубежом используют вероятность отказа микросхемы.

Отказоустойчивость микросхемы тем выше, чем ниже вероятность ее отказа. Отказоустойчивостью микросхемы можно считать вероятность ее безотказной работы:

где Рот - вероятность отказа микросхемы.

В работах Александрова П.А., Жука В.И., Литвинова В.Л. и др., обзор которых дан в указанной выше книге этих авторов, предложены и теоретически исследованы различные способы постоянного поэлементного резервирования микросхем (структурное дублирование, квадрирование, девятикратное резервирование одиночных транзисторов) и постоянного мажоритарного резервирования цифровых микросхем.

В этих работах приведены математические формулы отказоустойчивости облучаемых микросхем, являющиеся теоретическими оценками вероятности отказа микросхемы при ее резервировании указанными способами и без ее резервирования. Эти теоретические оценки отказоустойчивости позволяют предварительно выбрать подходящий способ резервирования без разработки и создания конкретных сложных микросхем.

Однако, учитывая большую стоимость разработки и изготовления сложных цифровых микросхем, для большей обоснованности выбора способа резервирования для построения цифровых микросхем, отказоустойчивых к облучению, необходимо получить экспериментальные оценки отказоустойчивости, которые могут обеспечить различные способы постоянного резервирования цифровых микросхем.

Для получения этих экспериментальных оценок необходимо провести испытания различных способов постоянного резервирования облучаемых цифровых микросхем, а не испытания конкретных микросхем, созданных для разных применений и имеющих структуру, не позволяющую обнаруживать подавляющее число отказов. Например, если конкретная цифровая микросхема представляет собой арифметическое устройство, то о его отказе можно будет судить по неверному результату на его выходе, но при этом нельзя обнаружить отказы в его элементах и измерить время до первого ее отказа, который может произойти задолго до получения результата арифметической операции. А без этого невозможно будет вычислить отказоустойчивость цифровой микросхемы.

Предлагаемое изобретение посвящено проблеме создания технических средств для проведения испытаний мажоритарного способа резервирования микросхем. Эти средства представляют собой способ косвенного измерения отказоустойчивости испытательных цифровых микросхем, построенных способом постоянного мажоритарного резервирования, и функциональную структуру испытательной микросхемы, которая может быть реализована мажоритарным способом постоянного резервирования. Здесь под испытательной микросхемой понимается микросхема, единственной функцией которой является обеспечение испытания способа косвенного измерения отказоустойчивости микросхем при способе их постоянного резервирования. Для обеспечения указанного испытания функциональная структура испытательной микросхемы должна позволять обнаруживать все отказы в ней в процессе ее работы.

Известен способ постоянного мажоритарного резервирования цифровых микросхем, отказоустойчивых к облучению и ориентированных на построение логических устройств, а не устройств памяти (см., книгу Александрова П.А., Жука В.И. и Литвинова В.Л. «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением», М.: Издательский Дом «ПоРог», 2019, Раздел 7, С. 54-70) и статью этих авторов в соавторстве с Бударагиным В.В. и Стельмак С.Е. «Сравнительные оценки отказоустойчивости мажоритарно резервированных и покомпонентно дублированных микросхем при облучении» // Нано- и микросистемная техника, 2016, №3, С. 176-185.

Однако способ косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных способом постоянного мажоритарного резервирования и функциональная структура испытательной цифровой микросхемы, предназначенной для реализации этого способа, не известен.

Прототипом предлагаемого способа является способ косвенного измерения отказоустойчивости облучаемых цифровых испытательных микросхем, построенных способом постоянного резервирования (см. патент РФ № RU 2724804 от 27.11.2019, МПК G06F 11/07, Александров П.А., Жук В.И., «Способ косвенных измерений отказоустойчивости облучаемых испытательных цифровых микросхем, построенных различными способами поэлементного резервирования, и функциональная структура испытательной микросхемы, предназначенной для реализации этого способа»).

Однако способ-прототип предназначен для косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных способами постоянного поэлементного резервирования, и не может быть использован для косвенного измерения отказоустойчивости облучаемых испытательных микросхем, построенных способом мажоритарного резервирования.

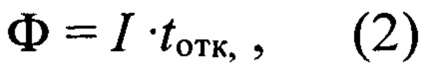

Способ-прототип состоит в том, что во время облучения микросхемы измеряют начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы, затем вычисляют флюенс, при котором произошел отказ микросхемы, по формуле:

где Ф - флюенс, или иначе говоря, число частиц, попавших в 1 см2 микросхемы за время облучения до ее отказа,

I - интенсивность облучения,

tотк - начальный отрезок времени облучения микросхемы до ее отказа,

позволяющий оценить вероятность отказа микросхемы, а затем по вычисленному флюенсу, площади микросхемы, числу логических элементов в микросхеме и заданной вероятности повреждения единицы площади микросхемы при попадании в нее частицы, вычисляют отказоустойчивость микросхемы по соответствующей способу ее построения на основе постоянного поэлементного резервирования формуле вероятности отказа микросхемы:

где j - идентификатор способа построения микросхемы,

Рот, .j - вероятность отказа микросхемы, характеризующая ее отказоустойчивость,

ƒj, Фj и Sj - формула, флюенс и площадь микросхемы, соответствующие j-му способу построения микросхемы,

N - число условных одинаковых компонентов, в частности, логических элементов, в микросхеме,

W - вероятность повреждения единицы площади микросхемы при попадании в нее частицы.

В способе-прототипе в качестве соответствующей способу построения цифровой микросхемы формуле (3) могут быть использованы конкретные известные или пока неизвестные математические формулы вероятности отказа микросхем, построенных способами постоянного поэлементного резервирования, а именно структурно дублированной, квадрированной и 9-кратно резервированной микросхемы, а также для нерезервированной микросхемы.

Недостаток способа-прототипа состоит в том, что он не позволяет провести косвенное измерение отказоустойчивости испытательных цифровых микросхем, построенных способом постоянного мажоритарного резервирования. Это обусловлено тем, что в способе-прототипе не используют испытательные цифровые микросхемы, построенные способом постоянного мажоритарного резервирования и не используют формулу вероятности отказа цифровой микросхемы, построенной способом постоянного мажоритарного резервирования.

Прототипом предлагаемой функциональной структуры испытательной цифровой микросхемы для косвенного измерения ее отказоустойчивости при облучении является функциональная структура, построенная способом постоянного поэлементного резервирования (см. указанный выше патент РФ № RU 2724804 от 27.11.2019).

Функциональная структура-прототип содержит входной и выходной n-разрядные двоичные регистры, узел управления приемом контрольных эталонов во входной регистр от необлучаемой вычислительной системы управления измерением и узел управления приемом кода результата в выходной регистр по сигналу указанной вычислительной системы управления измерением, а также n-разрядную двоичную комбинационную логическую схему, представляющую набор последовательных цепочек одинаковых одновходовых логических элементов, причем каждая из этих цепочек установлена между одноименными i-ми (i=1, 2, …, n) двоичными разрядами входного и выходного регистра. Функциональная структура-прототип реализуется различными способами постоянного поэлементного резервирования или без ее резервирования.

Недостаток функциональной структуры-прототипа состоит в том, что она не реализована мажоритарным способом резервирования с использованием мажоритарных клапанов и поэтому не может быть использована для косвенного измерения отказоустойчивости облучаемых испытательных микросхем, построенных способом мажоритарного резервирования.

Раскрытие сущности изобретения

Проблемой, решаемой предлагаемым изобретением, является разработка способа косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных способом постоянного мажоритарного резервирования, и функциональной структуры испытательной микросхемы, построенной способом постоянного мажоритарного резервирования и позволяющей обнаруживать в ней отказы и предназначенной для реализации предлагаемого способа косвенного измерения.

Предлагаемые способ и функциональная структура направлены на достижение технического результата, состоящего в создании средств проведения испытаний способа построения цифровых микросхем на основе постоянного мажоритарного резервирования с целью получения экспериментальных оценок их отказоустойчивости к облучению.

Достижение этого технического результата оказалось возможным благодаря тому, что оценки отказоустойчивости облучаемых микросхем «по площадям», использованные в прототипе, основаны на том факте, что облучение действует на «площадь» микросхемы независимо от ее функционального содержания. Это позволило создать для испытаний способа постоянного мажоритарного резервирования микросхем простую функциональную структуру испытательной микросхемы, специально предназначенную и приспособленную для измерения ее отказоустойчивости в процессе ее облучения и позволяющую просто обнаруживать отказы испытательной микросхемы в процессе ее облучения.

Для достижения этого технического результата предложен способ косвенного измерения отказоустойчивости облучаемых цифровых микросхем, построенных способом постоянного резервирования, заключающийся в том, что это косвенное измерение отказоустойчивости проводят на испытательной микросхеме во время ее облучения и при этом измеряют начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы, затем вычисляют флюенс, при котором произошел отказ микросхемы, по формуле:

где Ф - флюенс,

I - интенсивность облучения,

tотк - начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы,

а затем по вычисленному флюенсу, площади микросхемы, числу логических элементов в микросхеме и заданной вероятности повреждения единицы площади микросхемы при попадании в нее частицы, вычисляют отказоустойчивость микросхемы по соответствующей способу ее построения формуле вероятности отказа микросхемы,

измерение начального отрезка времени облучения микросхемы до ее отказа производят на облучаемой испытательной микросхеме, соединенной с необлучаемой вычислительной системой управления измерением, с помощью которой производят измерение времени облучения, вычисления флюенса и отказоустойчивости микросхемы, проверку результатов работы микросхемы и фиксацию отказов микросхемы,

время облучения микросхемы измеряют числом циклов ее работы, в каждом из которых на информационном входе микросхемы устанавливают контрольный эталон, а на выходе микросхемы получают код результата, эти циклы задают управляющими сигналами необлучаемой вычислительной системы управления измерением, в которой ведут счет циклов и из которой передают в микросхему контрольные эталоны, а также в которую передают коды результатов в каждом цикле и в которой в каждом цикле фиксируют отказ микросхемы при несовпадением ее кода результата с входным эталоном,

в качестве указанного начального отрезка времени работы микросхемы до ее отказа измеряют средний отрезок времени облучения микросхемы от момента облучения, принятого за начальный, до момента фиксации числа последовательных отказов облучаемой микросхемы в заданном числе соседних циклов ее работы,

при этом в качестве испытательной микросхемы используют микросхему, построенную способом мажоритарного резервирования логических блоков с формированием результатов с помощью мажоритарных клапанов, а отказоустойчивость микросхемы вычисляют по формуле, соответствующей мажоритарному способу ее построения и кратности резервирования.

Это позволяет решить проблему создания способа косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных способом постоянного мажоритарного резервирования и при этом обеспечить простые способы измерения отрезков времени облучения испытательной микросхемы и способ обнаружения ее отказов.

Достижению этого технического результата способствует то, что измеряют отрезок времени облучения микросхемы от момента начала измерения времени облучения микросхемы по сигналу устройства управления затвором облучения, подаваемого в необлучаемую вычислительную систему управления измерением, до цикла работы микросхемы, в котором будет обнаружен первый отказ микросхемы, характеризуемый фактом ошибки в коде, являющемся результатом работы микросхемы, при сравнении этого кода с эталоном, соответствующим моменту начала измерения времени облучения.

Это позволяет обнаружить первый отказ в микросхеме при ее облучении и в дальнейшем использовать момент этого первого отказа при измерении среднего отрезка времени облучения микросхемы до ее отказа.

Достижению указанного технического результата способствует также то, что за момент облучения, принятый за начальный момент измерения среднего отрезка времени облучения микросхемы, принимают начальный момент начала измерения времени облучения по сигналу устройства управления затвором облучения, подаваемому в необлучаемую вычислительную систему управления измерением.

Это позволяет по желанию испытателя использовать отрезок времени до первого отказа микросхемы при измерении среднего отрезка времени облучения микросхемы до ее отказа.

Достижению технического результата способствует и то, что за момент облучения, принятый за начальный момент измерения среднего отрезка времени облучения микросхемы, принимают момент первого отказа микросхемы после начала измерения в необлучаемой вычислительной системе управления измерением.

Это позволяет по желанию испытателя в дальнейшем использовать момент этого первого отказа при измерении среднего отрезка времени облучения микросхемы до ее отказа.

Технический результат достигается также благодаря тому, что измеряют отрезок времени облучения микросхемы от момента предыдущего ее отказа до момента следующего ее отказа по числу циклов работы микросхемы, прошедших от момента предыдущего отказа до цикла ее работы, в котором будет обнаружена ошибка в коде, являющемся результатом работы микросхемы, при сравнении этого кода с эталоном, соответствующим коду результата при предыдущем отказе микросхемы.

Это позволяет решить задачу измерения длительности среднего отрезка облучения микросхемы до ее отказа.

Для достижения технического результата предложена функциональная структура испытательной микросхемы, содержащая входной и выходной n-разрядные двоичные регистры, узел управления приемом контрольных эталонов во входной регистр от необлучаемой вычислительной системы управления измерением и узел управления приемом кода результата в выходной регистр по сигналу указанной вычислительной системы управления измерением, причем на входе каждого разряда выходного регистра установлен один k-кратно резервированный логический узел, содержащий мажоритарный клапан, выход которого соединен со входом того разряда выходного регистра, который соответствует этому логическому узлу, и установленные на входах мажоритарного клапана k одинаковых резервируемых блоков, каждый из которых содержит последовательную цепочку одновходовых комбинационных логических элементов, а вход каждой из этих цепочек соединен с выходом одного из разрядов входного регистра.

Это позволяет создать простую функциональную структуру испытательной микросхемы, служащую для реализации предлагаемого способа косвенного измерения отказоустойчивости облучаемых испытательных микросхем, построенных способом постоянного мажоритарного резервирования и обеспечивающих обнаружение в них отказов.

Краткое описание чертежей

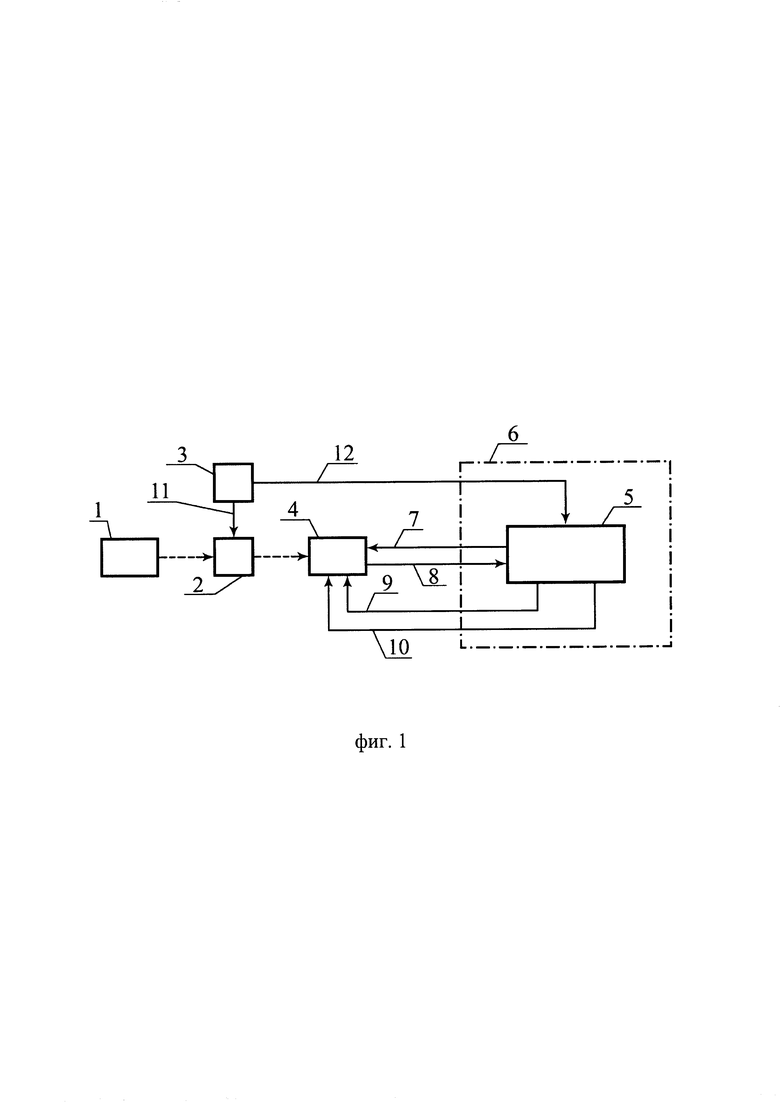

На фиг. 1 показана схема испытательной системы для косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных с использованием способа постоянного мажоритарного резервирования.

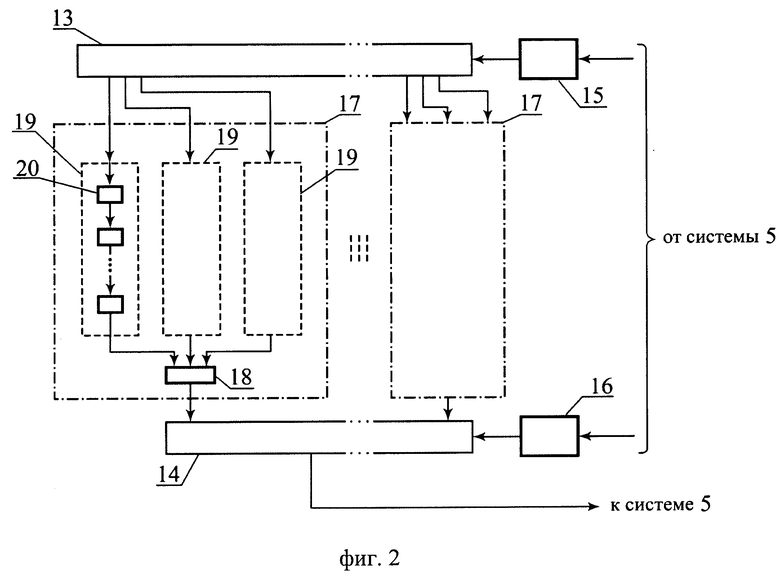

На фиг. 2 показана функциональная структура испытательной цифровой микросхемы для косвенного измерения ее отказоустойчивости при облучении, реализуемая с использование способа ее постоянного мажоритарного резервирования.

Осуществление изобретения

1. Состав испытательной системы

Испытательная система (фиг. 1) для косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных способом постоянного мажоритарного резервирования, содержит источник 1 радиационного излучения, построенный, например, на основе атомного реактора, затвор 2 облучения, устройство 3 управления затвором 2 облучения, испытательная цифровая микросхема 4, установленная в качестве облучаемого образца, и удаленная необлучаемая вычислительная система 5 управления измерением, установленная в необлучаемом помещении 6. Соединение 7 служит для передачи n-разрядного двоичного кода контрольного эталона из вычислительной системы 5 в микросхему 4. Соединение 8 служит для передачи n-разрядного двоичного кода результата работы микросхемы 4 в вычислительную систему 5. Соединение 9 служит для подачи управляющего сигнала приема контрольных эталонов в микросхему 4, а соединение 10 служит для подачи управляющего сигнала приема кода результата работы микросхемы 4 в ее выходной регистр (на фиг. 1 не показан). Соединение 11 служит для подачи устройством 3 сигналов управления («открыть», «закрыть») затвором 2 облучения, а соединение 12 служит для подачи управляющего сигнала начала измерений в вычислительную систему 5.

2. Функциональная структура испытательной цифровой микросхемы

Функциональная структура испытательной цифровой микросхемы 4, реализуемая с использованием способа ее постоянного мажоритарного резервирования (фиг. 2) содержит входной n-разрядный двоичный регистр 13, выходной n-разрядный двоичный регистр 14, узел 15 управления приемом n-разрядного двоичного кода контрольного эталона во входной регистр 13, узел 16 управления приемом кода результата работы микросхемы 4 в выходной регистр 14. Для реализации мажоритарного резервирования в микросхеме 4 установлены k-кратно (k=3, 5 или 7) резервированные узлы 17. Для примера на фиг. 2 используется k=3, т.е. троирование. На выходе каждого узла 17 установлен мажоритарный клапан 18, выход которого соединен со входом соответствующего этому узлу 17 разряду выходного регистра 14.

Мажоритарный клапан 18 формирует выходной логический сигнал, равный значению логического сигнала на большинстве его входов (см., например, книгу см., книгу Александрова П.А., Жука В.И. и Литвинова В.Л. «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением», М.: Издательский Дом «ПоРог», 2019, подраздел 7.2.2, С. 57). В литературе мажоритарный клапан называют также мажоритарным элементом (см. книгу Угрюмова Е.П. «Цифровая схемотехника», 3-е издание, СПб «БХВ-Петербург», 2010, С. 106). Однако сложные мажоритарные элементы состоят из большого числа логических элементов, особенно при большой кратности резервирования (при k=5 и 7). Поэтому представляется, что общем случае правильнее вместо термина «мажоритарный элемент» пользоваться термином «мажоритарный клапан» (см. Википедию).

Мажоритарные клапаны 18 могут быть нерезервированными или резервированными, т.е., например, дублированными, либо квадрированными, т.е., построенными на квадрированных транзисторах (см., например, указанную выше книгу Александрова П.А., Жука В.И. и Литвинова В.Л. «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением», М.: Издательский дом «ПоРог», С. 58, 64-66, 71-73).

Разряду входного регистра 13 соответствует только один разряд выходного регистра 14. На k входах мажоритарного клапана 18 установлены соответственно k одинаковых резервируемых блоков 19. Каждый из блоков 19 содержит цепочку одновходовых комбинационных логических элементов 20, а вход каждой из этих цепочек соединен с выходом одного из разрядов входного регистра 12.

Работа испытательной системы (фиг. 1) для косвенного измерения отказоустойчивости облучаемых испытательных микросхем рассматривается ниже в три этапа: сначала рассматривается совместная работа вычислительной системы 5 и микросхемы 4 (фиг. 2), затем рассматривается измерение отрезков времени и после этого рассматривается вычисление отказоустойчивости микросхемы 4.

3. Совместная работа вычислительной системы 5 и микросхемы 4

Начиная с момента своего включения вычислительная система 5 с постоянной частотой синхронно формирует пары управляющих сигналов начала и конца циклов работы микросхемы 4. Период этой частоты является длительностью Tц цикла работы вычислительной системы 5:

где Т1 - длительность времени между сигналами начала и конца цикла работы микросхемы 4,

Т2 - длительность обработки кода результата работы микросхемы 4, полученного в одном цикле ее работы.

Эта обработка кода результата работы микросхемы 4, полученного в одном цикле ее работы, осуществляется вычислительной системой 5, которая измеряет время работы микросхемы 4 по числу указанных циклов работы вычислительной системы 5, равному числу циклов работы микросхемы 4. Из формулы (4) видно, что цикл работы микросхемы 4 является частью цикла работы вычислительной системы 5.

Время облучения микросхемы 4 вычисляют умножением измеренного числа циклов работы вычислительной системы 5 на длительность Tц этого цикла.

Вычислительная система 5 передает в микросхему 4 управляющие сигналы начала цикла по соединению 9, и управляющие сигналы конца цикла работы микросхемы 4 передает по соединению 10. Каждый цикл работы микросхемы 4 определен парой сигналов начала и конца цикла ее работы.

Сигналы начала цикла поступают в узел 15 управления приемом контрольных эталонов во входной регистр 13 микросхемы 4, а сигналы конца цикла работы микросхемы 4 поступают в узел 16 управления приемом кода результата работы микросхемы 4 в выходной регистр 14. В узлах 15 и 16 формируются управляющие сигналы приема кодов во входной регистр 13 и в выходной регистр 14 соответственно.

Проверка отказа микросхемы 4

В начале каждого цикла по сигналу начала цикла, подаваемому в узел 15 из вычислительной системы 5, происходит прием контрольного эталона во входной регистр 13. Затем в результате переходного процесса в последовательных цепочках одинаковых комбинационных логических элементов 20 на входах мажоритарных клапанов 18 формируются выходные коды резервируемых блоков 19, а на выходах мажоритарных клапанов 18 формируются коды результата работы микросхемы 4 в течение одного цикла. И в конце цикла работы микросхемы 4 эти коды с выходов мажоритарных клапанов 18 принимаются в выходной регистр 14.

Потенциальные выходные сигналы регистра 14 передают в вычислительную систему 5 по соединению 8. Длительность цикла работы микросхемы 4 в основном определяется длительностью переходного процесса в последовательных цепочках одинаковых логических элементов 20, число которых в цепочке может быть очень большим, и в мажоритарных клапанах 18.

Отказ микросхемы 4 фиксируется по несоответствию кода во входном регистре 13 коду в выходном регистре 14. Это несоответствие проверяется в вычислительной системе 5 и состоит в том, что код в разряде выходного регистра 14, соединенном с выходом любого мажоритарного клапана 18, должен содержать код, совпадающий с большинством кодов в разрядах входного регистра 12, соединенных со входами резервируемых блоков 19, выходы которых соединены со входами этого мажоритарного клапана 18. Например, пусть при троировании коды в трех разрядах входного регистра 12, выходы которых соединены с тремя входами резервируемых блоков 19, входящих в один резервированный узел 17, будут 101. Тогда при отсутствии ошибки этому коду должен соответствовать код «1» на выходе мажоритарного клапана 18 и в соединенном с ним разряде выходного регистра 14.

Если в каком-либо цикле указанные проверяемые коды соответствуют друг другу, то в этом цикле отказа микросхемы не произошло. В следующем цикле можно сохранить прежний эталон во входном регистре 13, например, не подавая сигнал начала цикла в узел 15, и проверить на соответствие указанные проверяемые коды в микросхемы 4 с помощью вычислительной системы 5. Если же в каком-либо цикле вычислительная система 5 обнаружит взаимное несоответствие проверяемых кодов, то произошел отказ микросхемы 4.

Если в некотором цикле вычислительная система 5 обнаруживает отказ микросхемы 4, то в следующем цикле она в качестве эталона передает во входной регистр 14 ошибочный выходной код, полученный в предыдущем цикле. Если в этом следующем цикле выходной код микросхемы 4 совпадет с ошибочным входным кодом, то это означает, что в этом следующем цикле не было отказа. Если же в этом следующем цикле ошибочный входной код не совпадет с выходным кодом микросхемы 4, то это означает, что в этом следующем цикле произошел отказ, что будет зафиксировано вычислительной системой 5.

4. Измерение времени облучения

Перед началом работы устанавливают нужный режим источника 1 радиационного излучения с заданной постоянной интенсивностью I. Затем открывают затвор 2 по сигналу устройства 3 управления затвором 2, передаваемому по соединению 11. Затем в момент времени, регулируемый испытателем, по сигналу устройства 3, который подается по соединению 12, включают начало измерения в вычислительной системе 5 управления измерением. Момент начала измерения обозначим t0.

Поскольку время открытия механического затвора 2 достаточно большое (порядка нескольких секунд) и неопределенное, то момент начала облучения может не совпадать с моментом начала измерения в вычислительной системе 5. В связи с этим испытателю предоставлена возможность вести одновременно два вида измерения времени работы микросхемы 4.

В первом виде измерения за момент облучения, принятый за начальный, принимают момент начала измерения t0=0. Во втором виде измерения за момент облучения, принятый за начальный, принимают момент фиксации первого отказа микросхемы после момента начала измерений t0.

Как говорилось выше, время облучения микросхемы 4 измеряют числом циклов, умноженным на длительность цикла работы вычислительной системы 5 управления изменением.

Время облучения до момента первого отказа микросхемы измеряют от момента начала измерений t0=0 до цикла работы микросхемы 4, в котором будет обнаружен первый отказ микросхемы 4, характеризуемый фактом ошибки в ее выходном коде при сравнении его с входным контрольным эталоном (во входном регистре 13) микросхемы 4, соответствующим моменту начала измерения t0=0.

По окончании заданного числа циклов в вычислительной системе 5 вычисляют условный начальный отрезок времени tотк облучения микросхемы 4 до ее отказа, позволяющий оценить вероятность отказа микросхемы 4. В качестве этого указанного начального отрезка времени работы микросхемы 4 до ее отказа вычисляют средний начальный отрезок времени облучения микросхемы от момента облучения, принятого за начальный, до ее последнего отказа в заданном числе соседних циклов ее работы.

Пусть, например, после момента tн облучения, принятого за начальный, в заданном числе циклов, произойдут отказы микросхемы 4 в моменты t1, t2, t3, то средний начальный отрезок времени облучения микросхемы 4 будет

tотк=(t1+t2+t3)/3.

Для вычисления, например, времени t3 сначала измеряют отрезок времени

от момента t2 предыдущего отказа микросхемы 4 до момента t3 следующего ее отказа, после чего вычисляют момент t3 следующего ее отказа:

от момента t2 предыдущего отказа микросхемы 4 до момента t3 следующего ее отказа, после чего вычисляют момент t3 следующего ее отказа:

Для получения величин, аналогичных величине  измеряют отрезок времени облучения микросхемы 4 от момента предыдущего ее отказа до момента следующего ее отказа по числу циклов работы микросхемы 4, прошедших от момента предыдущего отказа до цикла ее работы, в котором будет обнаружена ошибка в выходном коде микросхемы 4 при сравнении этого кода с эталоном, соответствующим выходному коду результата при предыдущем отказе микросхемы 4.

измеряют отрезок времени облучения микросхемы 4 от момента предыдущего ее отказа до момента следующего ее отказа по числу циклов работы микросхемы 4, прошедших от момента предыдущего отказа до цикла ее работы, в котором будет обнаружена ошибка в выходном коде микросхемы 4 при сравнении этого кода с эталоном, соответствующим выходному коду результата при предыдущем отказе микросхемы 4.

Оценим приблизительно длительность цикла Тц по формуле (4). Длительность Т1 времени между сигналами начала и конца цикла микросхемы 4 оценим приблизительно по времени переходного процесса в цепочках комбинационных узлах 17, пренебрегая временем приема кодов во входной регистр 13 и в выходной регистр 14 микросхемы 4. Примем, что число двоичных разрядов в каждом из этих регистров будет n=50. Тогда, если суммарное число логических элементов во всех резервируемых блоках 19 примерно равно 100000, то длина цепочки логических элементов 20 в одном резервируемом блоке 19 будет равно 2000. При задержке на логический элемент (вентиль) 1 нсек, длительность Т1 переходного процесса в блоках 19 будет 2000 нсек, т.е. 2 мксек. Примем, например, что длительность обработки кода результата работы микросхемы 4 в одном цикле Т2=1 мксек, что вполне реально при тактовой частоте 50 мгц вычислительной системы 5. В этом случае длительность цикла составит 3 мксек, а частота циклов составит 0.33 мгц.

5. Вычисление экспериментальной оценки отказоустойчивости

По окончании измерения среднего отрезка времени tотк облучения микросхемы 4 до ее отказа в вычислительной системе 5 вычисляют флюенс, при котором произошел отказ микросхемы, по формуле:

где Ф - флюенс, I - постоянная интенсивность облучения, ⋅tотк - начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы,

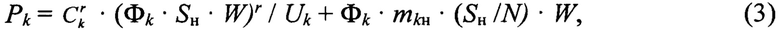

а затем по вычисленному флюенсу, площади микросхемы, числу логических элементов в микросхеме, заданной вероятности повреждения единицы площади микросхемы при попадании в нее частицы и другим параметрам, в вычислительной системе 5 вычисляют отказоустойчивость микросхемы по соответствующей мажоритарному способу ее построения формуле вероятности отказа микросхемы. Например, в качестве такой формулы могут быть использованы формула вероятности отказа облучаемой микросхемы, построенной способом постоянного мажоритарного резервирования с нерезервированными компараторами:

и формула вероятности отказа облучаемой микросхемы, построенной способом постоянного мажоритарного резервирования с дублированными компараторами:

где k - кратность резервирования, нечетная, k=3, 5, 7;

r=(k+1)/2,

- число сочетаний из k по r,

- число сочетаний из k по r,

Pk - вероятность отказа микросхемы, характеризующая ее отказоустойчивость,

Фk - флюенс.

Uk - число резервированных узлов микросхемы с кратностью k резервирования,

W - вероятность повреждения единицы площади микросхемы при попадании в нее частицы,

mkн - число транзисторов в мажоритарном клапане при кратности резервирования k,

- число компонентов (например, транзисторов) в одном резервируемом блоке при кратности резервирования k,

- число компонентов (например, транзисторов) в одном резервируемом блоке при кратности резервирования k,

N - число компонентов в нерезервированной микросхеме,

Sн - площадь нерезервированной микросхемы.

Формула (3) выводится из формул (7.3-16), (7.3-8) и (7.3-12), приведенных в книге П.А. Александрова, В.И. Жука и В.Л. Литвинова «Способы построения отказоустойчивых цифровых микросхем и оценки вероятностей их отказа, вызванного облучением». - М.: Издательский Дом «ПоРог», 2019, С. 66, 64, 65. А указанная выше формула (4) приведена под номером (7.3-19) в той же книге (С. 67).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных различными способами постоянного поэлементного резервирования, и функциональная структура испытательной микросхемы, предназначенной для реализации этого способа | 2019 |

|

RU2724804C1 |

| СПОСОБ ПОСТОЯННОГО ПОЭЛЕМЕНТНОГО ДУБЛИРОВАНИЯ В ЦИФРОВЫХ ТРАНЗИСТОРНЫХ МИКРОСХЕМАХ | 2017 |

|

RU2677359C1 |

| СПОСОБ ПОСТОЯННОГО ПОЭЛЕМЕНТНОГО ДУБЛИРОВАНИЯ В ДИСКРЕТНЫХ ЭЛЕКТРОННЫХ СИСТЕМАХ (ВАРИАНТЫ) | 2011 |

|

RU2475820C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| СПОСОБ И ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ОТКАЗОУСТОЙЧИВОЙ ОБРАБОТКИ ИНФОРМАЦИИ КРИТИЧЕСКИХ ФУНКЦИЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ | 2008 |

|

RU2413975C2 |

| Способ отказоустойчивого функционирования вычислительных комплексов для систем обработки информации военного назначения и устройство его реализующее | 2022 |

|

RU2775259C1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| СПОСОБ ФОРМИРОВАНИЯ 4-КАНАЛЬНОЙ ОТКАЗОУСТОЙЧИВОЙ СИСТЕМЫ БОРТОВОГО КОМПЛЕКСА УПРАВЛЕНИЯ ПОВЫШЕННОЙ ЖИВУЧЕСТИ И ЭФФЕКТИВНОГО ЭНЕРГОПОТРЕБЛЕНИЯ И ЕГО РЕАЛИЗАЦИЯ ДЛЯ КОСМИЧЕСКИХ ПРИМЕНЕНИЙ | 2011 |

|

RU2449352C1 |

| ОТКАЗОУСТОЙЧИВАЯ СИСТЕМА УПРАВЛЕНИЯ | 2021 |

|

RU2763092C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

Группа изобретений относится к области вычислительной техники и электроники и может быть использована для построения цифровых микросхем, отказоустойчивых к облучению. Техническим результатом является обеспечение косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных способом постоянного мажоритарного резервирования. Функциональная структура испытательной цифровой микросхемы содержит входной n-разрядный двоичный регистр, выходной n-разрядный двоичный регистр, узел управления приемом n-разрядного двоичного кода контрольного эталона во входной регистр, узел управления приемом кода результата работы микросхемы в выходной регистр. Для реализации мажоритарного резервирования в микросхеме установлены k-кратно резервированные узлы. На выходе каждого узла установлен мажоритарный клапан. На k входах мажоритарного клапана установлены соответственно k одинаковых резервируемых блоков. Каждый из блоков содержит цепочку одновходовых комбинационных логических элементов. 2 н. и 5 з.п. ф-лы, 2 ил.

1. Способ косвенного измерения отказоустойчивости облучаемых цифровых микросхем, построенных способом постоянного резервирования, состоящий в том, что это косвенное измерение отказоустойчивости проводят на испытательной микросхеме во время ее облучения и при этом измеряют начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы, затем вычисляют флюенс, при котором произошел отказ микросхемы, по формуле:

Ф=I⋅tотк,,

где Ф - флюенс, I - интенсивность облучения, tотк - начальный отрезок времени облучения микросхемы до ее отказа, позволяющий оценить вероятность отказа микросхемы, а затем по вычисленному флюенсу, площади микросхемы, числу логических элементов в микросхеме и заданной вероятности повреждения единицы площади микросхемы при попадании в нее частицы, вычисляют отказоустойчивость микросхемы по соответствующей способу ее построения формуле вероятности отказа микросхемы,

измерение начального отрезка времени облучения микросхемы до ее отказа производят на облучаемой испытательной микросхеме, соединенной с необлучаемой вычислительной системой управления измерением, с помощью которой производят измерение времени облучения, вычисления флюенса и отказоустойчивости микросхемы, проверку результатов работы микросхемы, фиксацию ее отказов и формируют управляющие сигналы циклов ее работы и работы микросхемы,

время облучения микросхемы измеряют по числу циклов ее работы, умноженному на длительность цикла работы указанной вычислительной системы, в каждом цикле из указанной вычислительной системы передают на вход микросхемы контрольные эталоны, в эту вычислительную систему передают коды результатов работы микросхемы, а в качестве указанного начального отрезка времени работы микросхемы до ее отказа измеряют средний отрезок времени облучения микросхемы от момента облучения, принятого за начальный, до последнего отказа в заданном числе соседних циклов ее работы, отличающийся тем, что в качестве испытательной микросхемы используют микросхему, построенную способом мажоритарного резервирования логических блоков с формированием результатов с помощью мажоритарных клапанов, расположенных на выходах этих логических блоков, в вычислительной системе в каждом цикле фиксируют отказ микросхемы при несоответствии кода ее результата входному эталону, а отказоустойчивость микросхемы вычисляют по формуле, соответствующей мажоритарному способу ее построения и кратности резервирования.

2. Способ по п. 1, отличающийся тем, что несоответствие кода результата работы испытательной микросхемы входному эталону состоит в том, что код разряда этого результата, сформированный хотя бы одним мажоритарным клапаном, не равен большинству кодов в разрядах входного эталона, подаваемых на входы резервируемых логических блоков, на выходе которых установлен этот мажоритарный клапан.

3. Способ по п. 1, отличающийся тем, что измеряют отрезок времени облучения микросхемы от момента начала измерения времени облучения микросхемы по сигналу устройства управления затвором облучения, подаваемого в необлучаемую вычислительную систему управления измерением, до цикла работы микросхемы, в котором будет обнаружен первый отказ микросхемы, характеризуемый фактом ошибки в коде результата работы микросхемы, при сравнении этого кода с эталоном, соответствующим моменту начала измерения времени облучения.

4. Способ по п. 1, отличающийся тем, что за момент облучения, принятый за начальный момент измерения среднего отрезка времени облучения микросхемы до момента фиксации заданного числа последовательных отказов облучаемой микросхемы, принимают начальный момент начала измерения времени облучения по сигналу устройства управления затвором облучения, подаваемому в необлучаемую вычислительную систему управления измерением.

5. Способ по п. 1, отличающийся тем, что за момент облучения, принятый за начальный момент измерения среднего отрезка времени облучения микросхемы до момента фиксации заданного числа последовательных отказов облучаемой микросхемы, принимают момент первого отказа микросхемы после начала измерения в необлучаемой вычислительной системе управления измерением.

6. Способ по п. 1, отличающийся тем, что измеряют отрезок времени облучения микросхемы от момента предыдущего ее отказа до момента следующего ее отказа по числу циклов работы микросхемы, прошедших от момента предыдущего отказа до цикла ее работы, в котором будет обнаружена ошибка в коде, являющемся результатом работы микросхемы, при сравнении этого кода с эталоном, соответствующим коду результата при предыдущем отказе микросхемы.

7. Функциональная структура испытательной цифровой микросхемы для косвенного измерения ее отказоустойчивости при облучении, реализуемая способом постоянного резервирования, содержащая входной и выходной n-разрядные двоичные регистры, узел управления приемом контрольных эталонов во входной регистр от необлучаемой вычислительной системы управления измерением и узел управления приемом кода результата в выходной регистр по сигналу указанной вычислительной системы управления измерением, отличающаяся тем, что на входе каждого разряда выходного регистра установлен один k-кратно резервированный логический узел, содержащий мажоритарный клапан, выход которого соединен со входом того разряда выходного регистра, который соответствует этому логическому узлу, и установленные на входах мажоритарного клапана k одинаковых резервируемых блоков, каждый из которых содержит последовательную цепочку одновходовых комбинационных логических элементов, а вход каждой из этих цепочек соединен с выходом одного из разрядов входного регистра.

| Способ косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных различными способами постоянного поэлементного резервирования, и функциональная структура испытательной микросхемы, предназначенной для реализации этого способа | 2019 |

|

RU2724804C1 |

| СПОСОБ ПОСТОЯННОГО ПОЭЛЕМЕНТНОГО ДУБЛИРОВАНИЯ В ЦИФРОВЫХ ТРАНЗИСТОРНЫХ МИКРОСХЕМАХ | 2017 |

|

RU2677359C1 |

| СПОСОБ ПОСТОЯННОГО ПОЭЛЕМЕНТНОГО ДУБЛИРОВАНИЯ В ДИСКРЕТНЫХ ЭЛЕКТРОННЫХ СИСТЕМАХ (ВАРИАНТЫ) | 2011 |

|

RU2475820C1 |

| CN 106301352 A, 04.01.2017 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

Авторы

Даты

2021-10-01—Публикация

2020-12-18—Подача