Изобретение относится к области вычислительной техники, а именно к способам построения высоконадежных вычислительных управляющих систем путем дублирования информации, и устройств, предназначенных для приема и обработки информации и выдачи результирующих сигналов объекту управления [G06F11/16].

Из уровня техники известна ОТКАЗОУСТОЙЧИВАЯ КОМПЛЕКСНАЯ СИСТЕМА УПРАВЛЕНИЯ [RU 2629454 C2, опубл.: 29.08.2017], содержащая на каждом посту управления летчика ручку управления с четырехкратно резервированными датчиками положения ручки (ДПР) по количеству каналов управления (крен, тангаж, рыскание), пульт управления, резервированные вычислители (ВУ) системы автоматического управления, четырехкратно резервированные ВУ системы дистанционного управления, четырехкратно резервированный интегральный блок датчиков, четырехкратно резервированный блок резервной навигации, три четырехкратно резервированных блока управления приводами, приводы, число которых определяется числом рулевых поверхностей ЛА и потребной степенью резервирования.

Недостатком аналога является высокая материалоемкость и трудозатраты производства системы, обусловленная тем, что отказоустойчивость упомянутой системы обуславливается путем резервирования ее элементов, выполненных как минимум в трехкратном исполнении.

Также известно УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК В ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ [RU 2524854 С1, опубл.: 10.08.2014], содержащее первый, второй и третий n-разрядные параллельные регистры с входом «запись», группу элементов «НЕ» (n-элементов «НЕ»), блок мажоритарной логики, информационные входы регистров поразрядно объединены и являются информационным входом устройства, выходы второго регистра соединены с входами группы элементов «НЕ», отличающееся тем, что в него введены n-элементов «исключающее ИЛИ», первая и вторая группа элементов «И», элемент задержки; блок мажоритарной логики выполнен на n-мажоритарных элементах, первые входы которых объединены со вторыми входами элементов «исключающее ИЛИ» и соединены с соответствующими информационными выходами первого регистра, вторые входы соединены с соответствующими выходами элементов «НЕ», а третьи входы соединены с соответствующими информационными выходами третьего регистра со смещением на n/2 разряд относительно первого регистра; первые входы элементов «исключающее ИЛИ» объединены с первыми входами соответствующих элементов «И» второй группы элементов «И» и подключены к выходам соответствующих мажоритарных элементов, а выходы соединены с первыми входами соответствующих элементов «И» первой группы элементов «И», вторые входы которых объединены и являются входом разрешения выдачи информации о неисправности устройства («ошибка»); выходы элементов «И» первой группы элементов «И» являются выходами «ошибка» устройства; выходы элементов И второй группы элементов «И» являются информационными выходами устройства, вторые входы которых объединены и подключены к выходу элемента задержки, вход которого объединен с входом «запись» третьего регистра.

Недостатком аналога является низкая надежность устройства, обусловленная двойным преобразованием входного цифрового сигнала в регистрах и обратным преобразованием выходного цифрового сигнала в мажоритарных элементах, что дополнительно усложняет устройство.

Наиболее близкой по технической сущности является ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ УПРАВЛЯЮЩАЯ СИСТЕМА С-01 [RU 2618365 C2, опубл.: 03.05.2017], что в трехканальную резервированную управляющую систему в каждый модуль А, В, С дополнительно введены узел интерфейса шины Q-bus, узел таймеров синхронизации, узел приема и обработки импульсных сигналов, узел приема и обработки потенциальных сигналов, узел регистров с соответствующими связями.

Основной технической проблемой прототипа является сложность диагностирования неисправности и/или отказа в работе какого-либо из каналов, связанные с появлением одиночных аппаратных или программных ошибок, обусловленная отсутствием в системе элементов контроля и визуализации ее работы.

Задачей изобретения является устранение недостатков прототипа.

Технический результат изобретения заключается в повышении надежности и эффективности системы управления.

Указанный технический результат достигается за счет того, что отказоустойчивая система управления, содержащая основной и резервные модули управления на базе процессоров, мажоритарные элементы, модули вывода сигналов и блок синхронизации, отличающаяся тем, что основной и резервные модули управления объединены общими входной и выходной шинами данных, при этом выходная шина данных выполнена с возможностью передачи сигналов от каждого из модулей управления на все мажоритарные элементы одновременно, к выходам мажоритарных элементов подключены блоки контроля ошибок для каждого из модулей управления и модули вывода сигналов, к выходам блоков контроля ошибок подключены блоки индикации ошибок для вывода информации об отказавшем канале управления.

В частности, мажоритарных элементов выполнено по количеству модулей управления.

В частности, блок синхронизации подключен к входам/выходам процессоров.

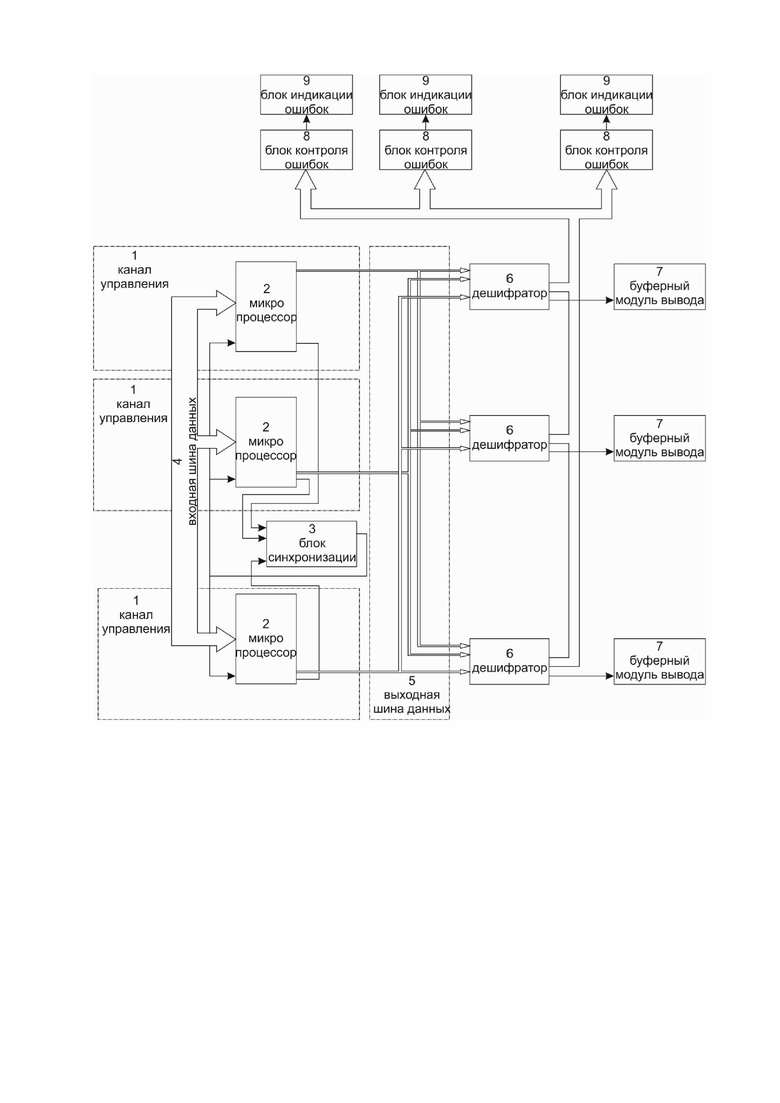

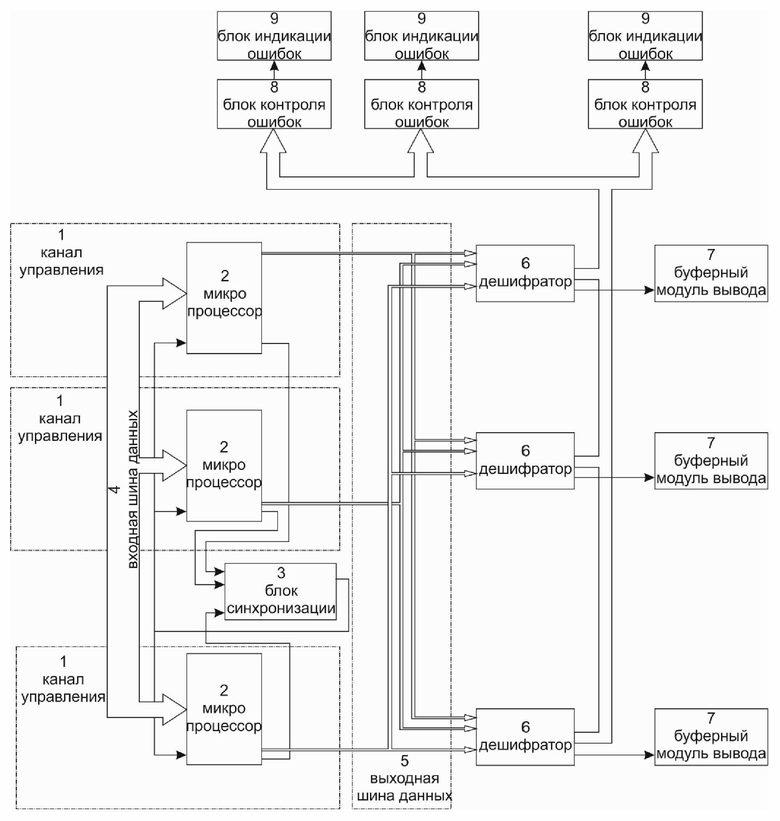

На фигуре показана схема отказоустойчивой системы управления, на которой обозначено: 1 – модули управления, 2 – процессоры, 3 – блок синхронизации, 4 – входная шина данных, 5 – выходная шина данных, 6 – мажоритарные элементы, 7 – буферные модули вывода, 8 – блоки контроля ошибок, 9 – блоки индикации ошибок.

Осуществление изобретения.

Отказоустойчивая система управления содержит N-модулей управления 1, включающие в себя по одному процессору 2 на каждый из каналов управления 1 и блок синхронизации программ 3. Процессоры 2 объединены общей входной шиной данных 4. Выходы процессоров 2 объединены в общую выходную шину данных 5 подключенную к каждому из N-мажоритарных элементов 6. Выход каждого из мажоритарных элементов 6 соединен с отдельным буферным модулем вывода 7. Новым является то, что выходы мажоритарных элементов 6 общей шиной соединены с блоками контроля ошибок 8, выполненных по числу модулей управления 1. К выходу каждого из блоков контроля ошибок 8 подключен отдельный блок индикации ошибок 9.

Отказоустойчивая система управления работает следующим образом.

При включении системы на вход процессоров 2 модулей управления 1 одновременно по общей шине входных сигналов 4 подают поток входных сигналов от субъекта управления (на фигурах не показан). В блоке синхронизации программ 3 вырабатывают разрешающий сигнал для работы процессоров 2 и подают его на вход процессоров 2 каждого из N-модулей управления 1. Упомянутые процессоры 2 после получения разрешающего сигнала от блока синхронизации программ 3 осуществляют одновременную обработку по заранее записанному в них алгоритму потока входящих по входной шине данных 4 сигналов. По окончании обработки обработанные сигналы с процессоров 2 по общей выходной шине 5 подают одновременно на входы всех мажоритарных элементов 6.

При совпадении сигналы с каждого из мажоритарных элементов 6 подают на отдельные буферные модули вывода 7. При несовпадении какого либо из сигналов на выходе процессоров 2 модулей управления 1 возникающем в результате аппаратной или программной ошибки, на упомянутый буферный модуль вывода 7 сигналы подают по мажоритарному принципу, то есть по принципу большинства, при котором значение выходного сигнала с мажоритарных элементов 6 совпадает со значением большинства сигналов, поступающих на мажоритарные элементы 6 с процессоров 2 модулей управления 1, при этом в блоках контроля ошибок 8 определяют модуль управления 1 с которого поступил ошибочный сигнал, отмечают его как отказавший и выводят информацию об ошибке на блок индикации ошибок 9 в режиме реального времени, что позволяет своевременно выявить отказавший модуль управления 1 и отремонтировать или заменить его и повысить надежность системы в целом, уменьшить вероятность ее отказа и за счет этого повысить эффективность системы управления, чем обеспечивают достижение технического результата. С буферных модулей вывода 7 сигналы передают на объект управления.

После прохождения цикла обработки сигналов на всех процессорах 2 следующий цикл обработки начинается только после выработки разрешающего сигнала с блока синхронизации программ 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ формирования отказоустойчивой комплексной системы управления (КСУ) и отказоустойчивая КСУ | 2016 |

|

RU2629454C2 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| РЕЗЕРВИРОВАННАЯ ЧЕТЫРЁХКАНАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2017 |

|

RU2665252C1 |

| СИСТЕМА ВИБРАЦИОННОГО КОНТРОЛЯ | 2008 |

|

RU2371695C1 |

| СПОСОБ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ИЗБЫТОЧНОСТЬЮ НЕОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2015 |

|

RU2612569C2 |

| Резервированная система | 1982 |

|

SU1084802A1 |

| Способ функционирования комплексов средств автоматизации систем обработки информации и управления и устройство, его реализующее | 2020 |

|

RU2767018C2 |

| УСТРОЙСТВО МАЖОРИТАРНОГО РЕЗЕРВИРОВАНИЯ (ВАРИАНТЫ) | 2005 |

|

RU2298823C2 |

| Резервированное устройство для управления электропневмоклапанами | 1989 |

|

SU1647512A1 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

Изобретение относится к области вычислительной техники, а именно к способам построения высоконадежных вычислительных управляющих систем путем дублирования информации, и устройств, предназначенных для приема и обработки информации и выдачи результирующих сигналов объекту управления. Отказоустойчивая система управления содержит основной и резервные модули управления на базе процессоров, мажоритарные элементы, модули вывода сигналов и блок синхронизации. Основной и резервные модули управления объединены общими входной и выходной шинами данных. Выходная шина данных выполнена с возможностью передачи сигналов от каждого из модулей управления на все мажоритарные элементы одновременно. К выходам мажоритарных элементов подключены блоки контроля ошибок для каждого из модулей управления и модули вывода сигналов, к выходам блоков контроля ошибок подключены блоки индикации ошибок для вывода информации об отказавшем канале управления. Повышается надежность и эффективность системы управления. 2 з.п. ф-лы, 1 ил.

1. Отказоустойчивая система управления, содержащая основной и резервные модули управления на базе процессоров, мажоритарные элементы, модули вывода сигналов и блок синхронизации, отличающаяся тем, что основной и резервные модули управления объединены общими входной и выходной шинами данных, при этом выходная шина данных выполнена с возможностью передачи сигналов от каждого из модулей управления на все мажоритарные элементы одновременно, к выходам мажоритарных элементов подключены блоки контроля ошибок для каждого из модулей управления и модули вывода сигналов, к выходам блоков контроля ошибок подключены блоки индикации ошибок для вывода информации об отказавшем канале управления.

2. Система по п.1, отличающаяся тем, что мажоритарных элементов выполнено по количеству модулей управления.

3. Система по п.1, отличающаяся тем, что блок синхронизации подключен к входам/выходам процессоров.

| Трехканальная резервированная управляющая система С-01 | 2015 |

|

RU2618365C2 |

| Способ формирования отказоустойчивой комплексной системы управления (КСУ) и отказоустойчивая КСУ | 2016 |

|

RU2629454C2 |

| US 6732300 B1, 04.05.2004 | |||

| CN 108228391 A, 29.06.2018 | |||

| US 20160048434 A1, 18.02.2016. | |||

Авторы

Даты

2021-12-27—Публикация

2021-06-15—Подача