Изобретение относится к вычислительной технике и предназначено для построения резервированных систем высокой надежности.

Известно трехканальное резервированное устройство с перестраиваемой структурой (см. авт. св. СССР 1037260, G 06 F 11/18), содержащее резервный блок, элементы И-НЕ, мажоритарный блок, состоящий из первого, второго, третьего и четвертого элементов И и элемента ИЛИ-НЕ, блок коммутации питания.

Известно устройство управления резервированием (см. авт. св. СССР 1474652, G 06 F 11/20), содержащее регистр команд, первый элемент И, элемент И с инверсным входом, коммутатор кода признака, коммутатор кода операции, блок выбора операционных блоков, операционные блоки, шифратор начального адреса, счетчик адреса, блок памяти, второй элемент И.

Недостатками данных устройств является отсутствие защиты от отказов типа "сбой". "Сбой" - событие, заключающееся в однократном искажении перерабатываемого в радиоэлектронном устройстве сигнала, возникающее под воздействием внутренних или внешних дестабилизирующих факторов (помех) (А.Я. Резиновский. Испытания на надежность радиоэлектронных комплексов. - М.: Радио и связь. 1985 г., стр. 9).

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство с гибридным резервированием (см. Методы анализа и синтеза структур управляющих систем / Б. Г. Волик, Б. Б. Буянов, Н. В. Лубков и др. ; Под ред. Б.Г. Волика. - М.: Энергоатомиздат, 1988, стр. 242-244). Известное устройство состоит из n рабочих каналов, мажоритарного элемента, пороговых элементов, элемента ИЛИ, кольцевого регистра, регистров памяти.

Выход каждого из n каналов подключен к коммутирующим входам трех исполнительных ключей одноименных разрядов регистров памяти. Выходы исполнительных ключей объединены по регистрам памяти и соединены с одноименными входами мажоритарного элемента и пороговых элементов. Выход мажоритарного элемента подключен ко входам пороговых элементов и одновременно является информационным выходом устройства. Выходы пороговых устройств подключены ко входам исполнительных ключей одноименных разрядов регистров памяти, а также подключены к одноименным входам элемента ИЛИ. Выход элемента ИЛИ подключен ко входам кольцевого регистра. Соответствующие выходы кольцевого регистра подключены к соответствующим входам исполнительных ключей регистров памяти. Устройство с гибридным резервированием реализует принцип гибридного резервирования с мажоритарным выбором выходного сигнала, автоматического отключения отказавших каналов и замещением их резервными.

Недостатками прототипа являются относительно невысокая надежность. Надежность - свойство объекта сохранять во времени в установленных пределах значения всех параметров, характеризующих способность выполнять требуемые функции в заданных режимах и условиях применения, технического обслуживания, ремонтов, хранения и транспортирования (B.C. Авдуевский, И.В. Апполонов, Е. Ю. Барзилович и др. Надежность и эффективность в технике: Справочник: В 10 т. / Ред. совет: B.C. Авдуевский (пред.) и др. -М.: Машиностроение, 1986, т. 1: Методология. Организация. Терминология/Под ред. А.И. Рембезы, стр. 185). ), связанная с включением схемы управления при отказах типа "сбой", а также с жестко централизованным управлением каналами коммутации.

Целью изобретения является разработка устройства резервирования, обеспечивающего более высокую надежность устройства.

Поставленная цель достигается тем, что в известном устройстве резервирования, содержащем К блоков каналов коммутации, где К=(2n+1), n=1, 2, 3,..., N информационных блоков, где N≥K+1, мажоритарный элемент, блок анализа, выход i-го информационного блока, где i=1, 2,...,N, подключен к i-му информационному входу каждого из К блоков каналов коммутации, информационный выход j-ro, где j=1, 2,...,K, блока каналов коммутации подключен к j-ым информационным входам мажоритарного элемента и блока анализа, информационный выход мажоритарного элемента подключен к общему информационному входу блока анализа и является информационным выходом устройства, дополнительно введены К блоков управления коммутаторами, управляющий блок, генератор тактовых импульсов, блок установки начального состояния. Первый и второй установочные выходы блока установки начального состояния подключены соответственно к первым и вторым установочным входам каждого из К блоков управления коммутаторами. I-ый определяющий выход j-го блока управления коммутатором подключен соответственно к i-му определяющему входу j-го блока каналов коммутации. I-ый отключающий выход j-го блока управления коммутатора подключен к i-ым запрещающим входам остальных блоков управления коммутаторами. J-ый результирующий выход блока анализа подключен соответственно к j-му результирующему входу управляющего блока, синхронизирующий вход которого подключен к выходу генератора тактовых импульсов. J-ая пара дуплексных выходов управляющего блока подключена к соответствующей паре управляющих входов j-го блока управления коммутатором.

Благодаря новой совокупности существенных признаков за счет введения К блоков управления коммутаторами, управляющего блока, генератора тактовых импульсов, блока установки начального состояния достигается возможность исключения реакции схемы управления при отказах типа "сбой" и отключения соответствующих блоков каналов коммутации из-за отказа соответствующего регистра кольцевого регистра сдвига блока управления коммутатором, чем и обеспечивается более высокая надежность заявляемого устройства.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

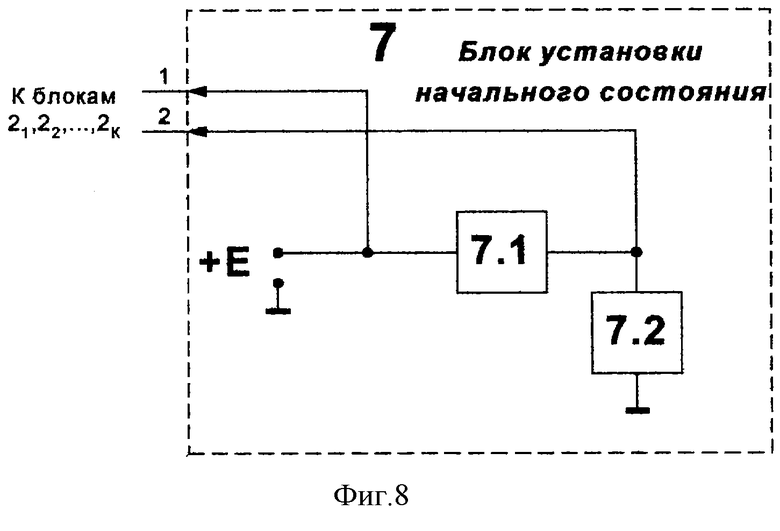

Заявленное устройство поясняется схемами:

фиг.1 - схема устройства резервирования;

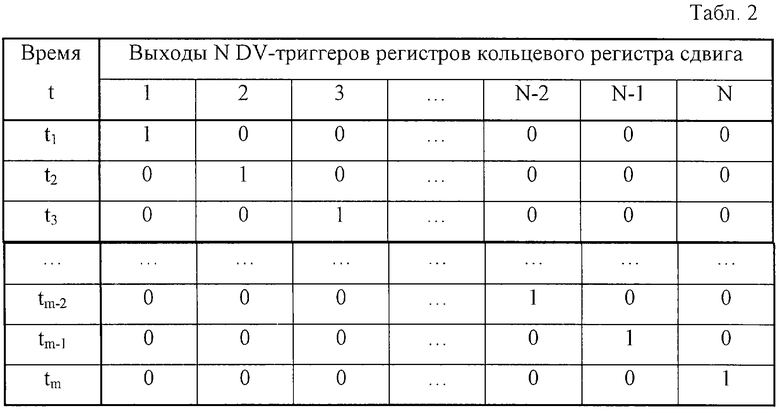

фиг.2 - схема блока каналов коммутации;

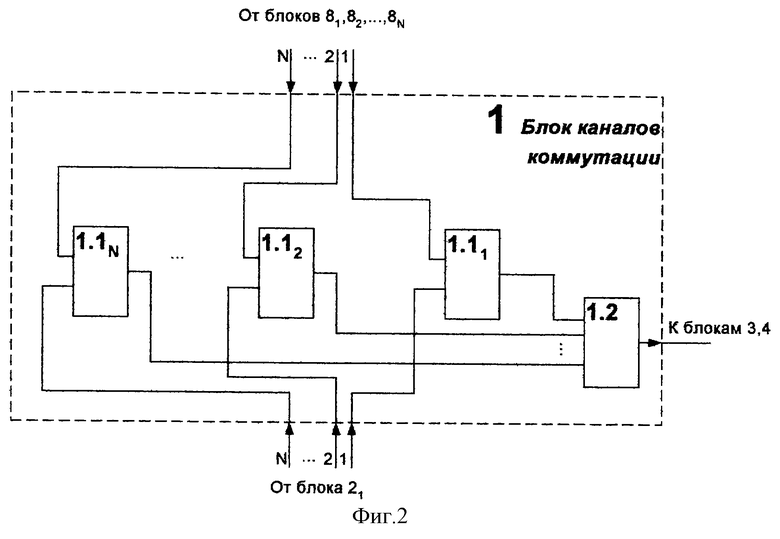

фиг.3 - схема блока управления коммутатором;

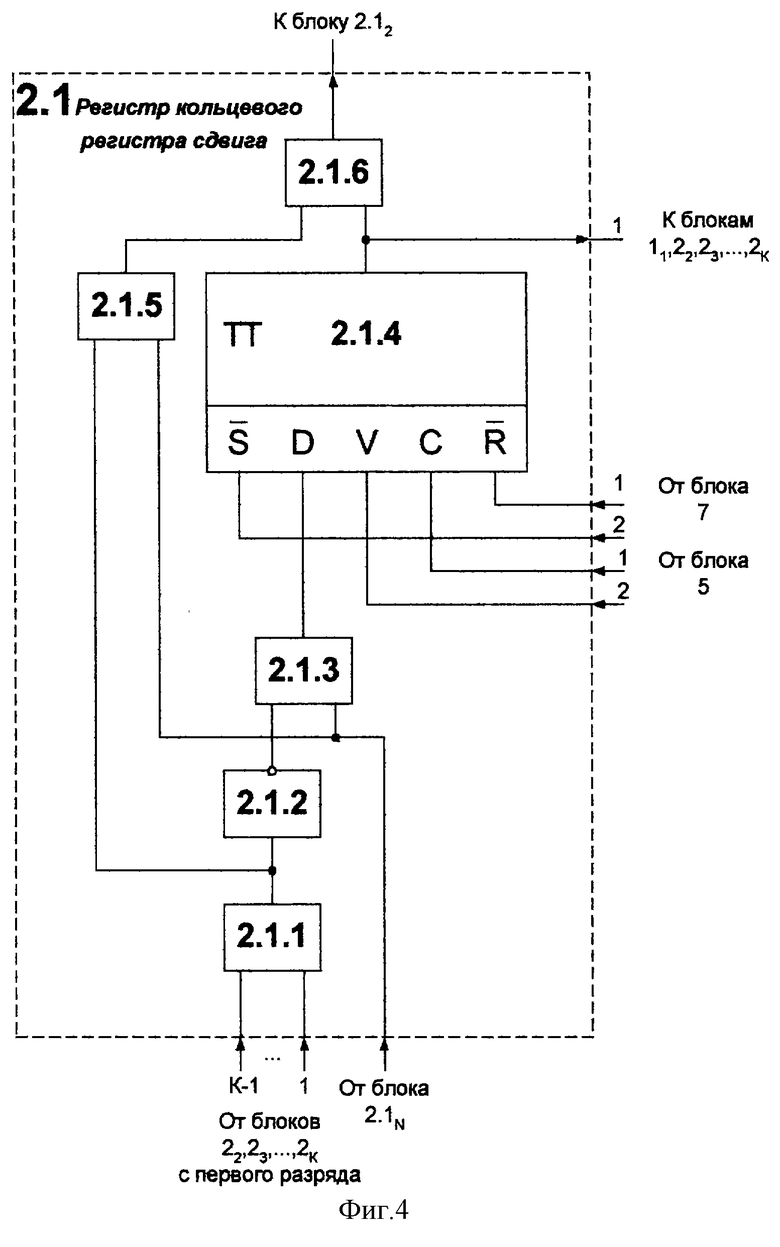

фиг.4 - схема регистра кольцевого регистра сдвига;

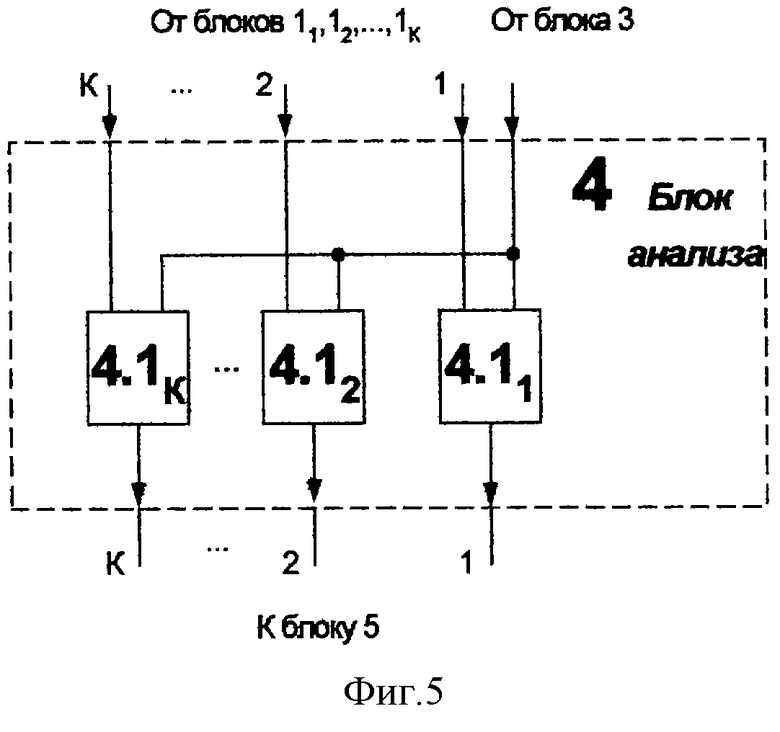

фиг.5 - схема блока анализа;

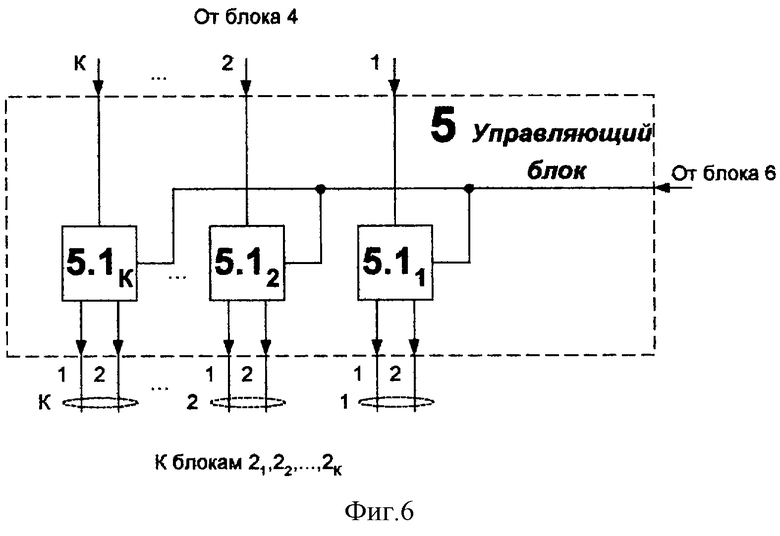

фиг.6 - схема управляющего блока;

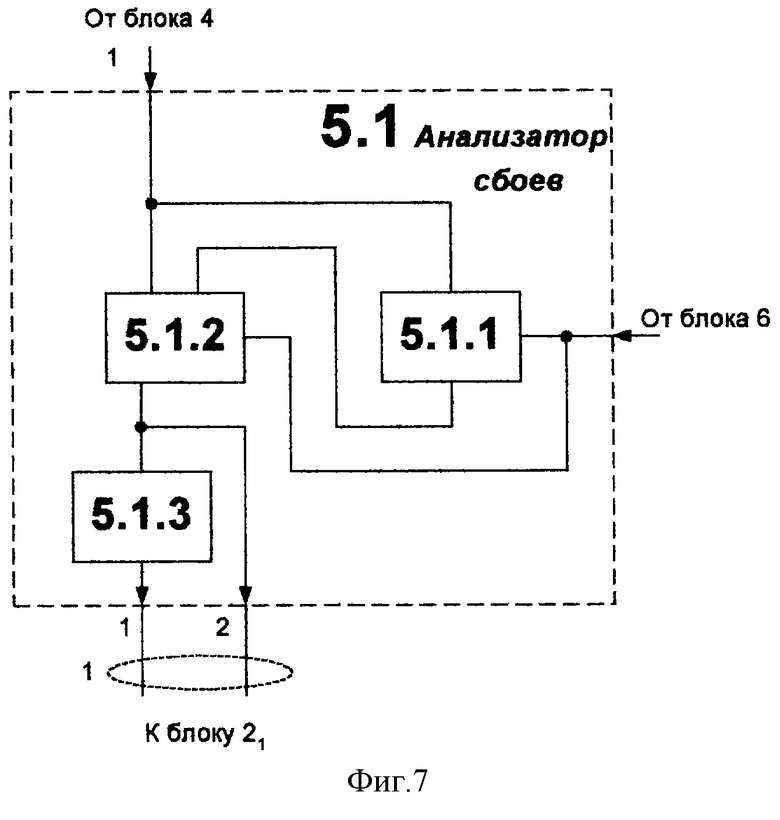

фиг.7 - схема анализатора сбоев;

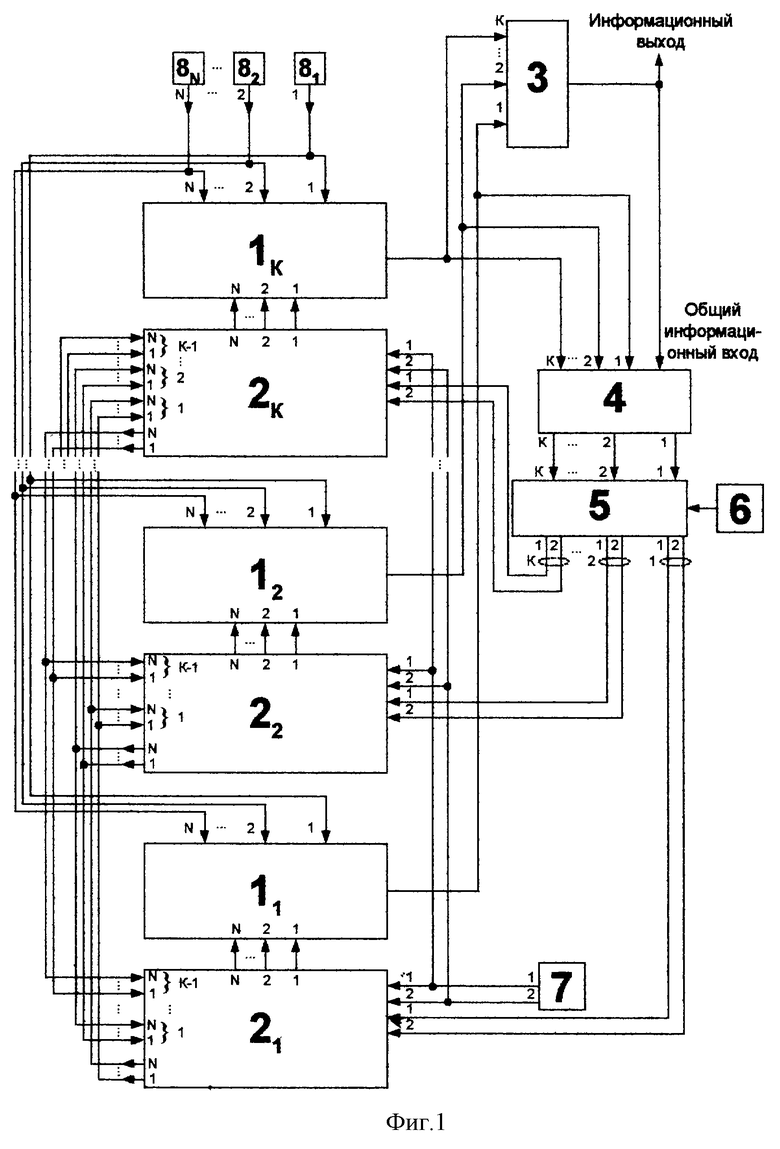

фиг.8 - схема блока установки начального состояния.

Устройство резервирования (фиг.1) состоит из К блоков каналов коммутации 11, 12, . . .,1K. К блоков управления коммутаторами 21, 22,..., 2K, мажоритарного элемента 3, блока анализа 4, управляющего блока 5, генератора тактовых импульсов 6, блока установки начального состояния 7, N информационных блоков 81, 82,...,8N.

Информационные выходы N информационных блоков 81, 82,...,8N подключены к соответствующим N информационным входам каждого из К блоков каналов коммутации 11, 12, ...,1K. К информационных выходов блоков каналов коммутации 11, 12,...,1K подключены к соответствующим К информационным входам мажоритарного элемента 3 и блока анализа 4. Информационный выход мажоритарного элемента 3 подключен к общему информационному входу блока анализа 4 и является информационным выходом устройства. Первый и второй установочные выходы блока установки начального состояния 7 подключены соответственно к первым и вторым установочным входам каждого из К блоков управления коммутаторами 21,22,..., 2K. N определяющих выходов j-го блока управления коммутатором 2 подключены к соответствующим N определяющим входам j-го блока каналов коммутации 1. N отключающих выходов j-го блока управления коммутатором 2 подключены к соответствующим N запрещающим входам остальных, кроме j-го, блоков управления коммутаторами 2. К результирующих выходов блока анализа 4 подключены соответственно к К результирующим входам управляющего блока 5, синхронизирующий вход которого подключен к выходу генератора тактовых импульсов 6. К пар управляющих дуплексных выходов управляющего блока 5 подключены к соответствующим парам управляющих входов К блоков управления коммутаторами 21, 22,...,2K.

Блок каналов коммутации 1 (фиг.2) предназначен для подключения работоспособных и отключения неработоспособных информационных блоков 81,82...., 8n.

Блоки каналов коммутации 11, 12,...,1K идентичны. Блок каналов коммутации 1 состоит из N элементов И 1.11,1.12,...1.1N многовходового элемента ИЛИ 1.2. N информационных и N определяющих входов подключены соответственно к первым и вторым входам соответствующих элементов И 1.11,1. 12,..., 1.1N. Выходы этих элементов подключены ко входам многовходового элемента ИЛИ 1.2. Выход многовходового элемента ИЛИ 1.2 является информационным выходом блока каналов коммутации 1.

Блок управления коммутатором 2 (фиг.3) предназначен для формирования сигнала на первоначальное подключение информационного выхода соответствующего информационного блока 81 (82,...,8N) на информационный выход соответствующего блока каналов коммутации 11 (12,...,1K) в соответствии с алгоритмом установки начального состояния устройства, а также для отключения в случае отказа информационного выхода неработоспособных информационных блоков 81, 82,...,8N от информационного выхода блока каналов коммутации l1 (12,..., 1K).

Блоки управления коммутаторами 21,22,...,2K идентичны. Блок управления коммутатором 2 состоит из идентичных регистров кольцевого регистра сдвига 2.11, 2.12, ...,2.1N. Первый и второй установочные входы подключены к соответствующим установочным входам регистров кольцевого регистра сдвига 2.11, 2.12,...,2.1N. Причем первый и второй установочный вход j-го, где j=l,2,..., K, регистра кольцевого регистра сдвига 2.1 j-го блока управления коммутатором 2 является инверсным относительно установочных входов остальных К-1 регистров кольцевого регистра сдвига 2.1 j-го блока управления коммутатором 2. Первый и второй управляющие входы подключены соответственно к синхронизирующему и управляющему входам регистров кольцевого регистра сдвига 2.11, 2.12, . ..,2.1N. N К-1-х запрещающих входов подключены к соответствующим К-1 запрещающим входам регистров кольцевого регистра сдвига 2.11, 2.12,..., 2.1N. N первых выходов регистров кольцевого регистра сдвига 2.11, 2.12,..., 2.1N являются одновременно отключающими и определяющими выходами блока управления коммутатором 2. Вторые выходы регистров кольцевого регистра сдвига 2.11, 2.12, . ..,2.1N подключены ко входам последующих регистров кольцевого регистра сдвига 2.11,2.12,...,2.1N.

Регистр кольцевого регистра сдвига 2.1 (фиг.4) предназначен для формирования сигнала на первоначальное подключение информационного выхода информационного блока 81 (82,...,8N) на информационный выход блока каналов коммутации 1 в соответствии с алгоритмом установки начального состояния устройства, а также для отключения в случае отказа информационного выхода неработоспособного информационного блока 81 (82,...,8N) от информационного выхода блока каналов коммутации 1.

Регистры кольцевого регистра сдвига 2.11, 2.12,...,2.1N идентичны. Регистр кольцевого регистра сдвига 2.1 состоит из многовходового элемента ИЛИ 2.1.1, элемента И-НЕ 2.1.2, первого элемента И 2.1.3, DV-триггера 2.1.4, второго элемента И 2.1.5, элемента ИЛИ 2.1.6. Первый и второй установочные входы первого регистра кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 подключены к установочным  входам DV-триггера 2.1.4. Остальные N-1 регистров кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 подключены соответственно к установочным

входам DV-триггера 2.1.4. Остальные N-1 регистров кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 подключены соответственно к установочным  входам DV-триггеров. Первый и второй управляющие входы подключены соответственно к синхронизирующему С и управляющему V входам DV-триггера 2.1.4. К-1 запрещающих входов подключены ко входу многовходового элемента ИЛИ 2.1.1. Второй вход первого и второго элементов И 2.1.3 и 2.1.5 подключен к выходу предыдущего регистра кольцевого регистра сдвига. Выход DV-триггера 2.1.4 подключен ко второму входу элемента ИЛИ 2.1.6, а также является одновременно отключающим и определяющим выходом регистра кольцевого регистра сдвига 2.1. Выход элемента ИЛИ 2.1.6 подключен ко входу последующего регистра кольцевого регистра сдвига. Выход многовходового элемента ИЛИ 2.1.1 одновременно подключен ко входу элемента И-НЕ 2.1.2 и к первому входу второго элемента И 2.1.5. Выход элемента И-НЕ 2.1.2 подключен к первому входу первого элемента И 2.1.3. Выход первого элемента И 2.1.3 подключен к информационному D входу DV-триггера 2.1.4. Выход второго элемента И 2.1.5 подключен к первому входу элемента ИЛИ 2.1.6.

входам DV-триггеров. Первый и второй управляющие входы подключены соответственно к синхронизирующему С и управляющему V входам DV-триггера 2.1.4. К-1 запрещающих входов подключены ко входу многовходового элемента ИЛИ 2.1.1. Второй вход первого и второго элементов И 2.1.3 и 2.1.5 подключен к выходу предыдущего регистра кольцевого регистра сдвига. Выход DV-триггера 2.1.4 подключен ко второму входу элемента ИЛИ 2.1.6, а также является одновременно отключающим и определяющим выходом регистра кольцевого регистра сдвига 2.1. Выход элемента ИЛИ 2.1.6 подключен ко входу последующего регистра кольцевого регистра сдвига. Выход многовходового элемента ИЛИ 2.1.1 одновременно подключен ко входу элемента И-НЕ 2.1.2 и к первому входу второго элемента И 2.1.5. Выход элемента И-НЕ 2.1.2 подключен к первому входу первого элемента И 2.1.3. Выход первого элемента И 2.1.3 подключен к информационному D входу DV-триггера 2.1.4. Выход второго элемента И 2.1.5 подключен к первому входу элемента ИЛИ 2.1.6.

Мажоритарный элемент 3 предназначен для подключения К информационных входов от блоков каналов коммутации 11, 12,...,1K на общий информационный вход блока анализа 4 и информационный выход по их большинству.

Блок анализа 4 (фиг.5) предназначен для сравнения информационной последовательности сигналов, поданных от мажоритарного элемента 3 и блоков каналов коммутации 11, 12, ...,1K и формирования результирующего сигнала управляющему блоку 5.

Блок анализа 4 состоит из идентичных сумматоров по модулю два 4.11, 4.12, . . .,4.1K. К информационных входов подключены ко вторым входам сумматоров по модулю два 4.11, 4.12,...,4.1K. На первые входы сумматоров по модулю два 4.11, 4.12,...,4.1K подключен общий информационный вход. К выходов сумматоров по модулю два 4.11, 4.12,...,4.1K являются результирующими выходами блока анализа.

Управляющий блок 5 (фиг.6) предназначен для формирования управляющих сигналов блокам управления коммутаторами 21, 22,...,2K.

Управляющий блок 5 состоит из идентичных анализаторов сбоев 5.11, 5.12,. . . , 5.1K. К результирующих входов подключены ко вторым входам анализаторов сбоев 5.11, 5.12,...,5.1K. К первым входам анализаторов сбоев 5.11, 5.12,... ,5.1K подключен синхронизирующий вход. К дуплексных пар, являющихся выходами анализаторов сбоев 5.11, 5.12, ..., 5.1K, являются управляющими выходами управляющего блока.

Анализатор сбоев 5.1 (фиг.6) предназначен для формирования управляющих сигналов блоку управления коммутатором 21 (22,...,2K).

Анализатор сбоев 5.1 состоит из таймера 5.1.1, счетчика импульсов 5.1.2 и одновибратора 5.1.3. Первый результирующий вход одновременно подключен к первому входу таймера 5.1.1 и счетчика импульсов 5.1.2. Синхронизирующий вход подключен ко второму входу таймера 5.1.1 и счетчика импульсов 5.1.2. Выход таймера 5.1.1 подключен к третьему входу счетчика импульсов 5.1.2. Выход счетчика импульсов 5.1.2 подключен ко входу одновибратора 5.1.3 и одновременно является вторым управляющим выходом анализатора сбоев 5.1. Выход одновибратора 5.1.3 является первым управляющим выходом анализатора сбоев 5.1.

Генератор тактовых импульсов 6 предназначен для генерации тактовой последовательности импульсов.

Выход генератора тактовых импульсов 6 является синхронизирующим выходом. В качестве генератора тактовых импульсов может быть использован генератор тактовых импульсов, описанный в книге Справочник по интегральным микросхемам. /Под общ. ред. Б.В. Тарабрина. М.: Энергия, 1977, стр. 521).

Блок установки начального состояния 7 (фиг.7) предназначен для формирования установочных сигналов блокам управления коммутаторами 21, 22,...,2K.

Блок установки начального состояния 7 состоит из резистора 7.1 и конденсатора 7.2. Первый и второй выходы блока установки начального состояния 7 являются установочными выходами.

Информационные блоки 81, 82,...,8N предназначены для подачи информационной последовательности сигналов на информационные входы блоков каналов коммутации 11, 12,...,1K.

Входящие в рассмотренные блоки элементы И, ИЛИ, И-НЕ, многовходовые элементы ИЛИ известны и описаны, например, в книге Цифровые интегральные микросхемы: Справочник /П. П. Мальцев, Н.С. Долидзе, М.И. Критенко и др. - М.: Радио и связь, 1994, стр.234-237, счетчики импульсов - на стр. 68. Таймеры известны и описаны, например, в книге Справочник по цифровой вычислительной технике: процессоры и память. / Б.Н. Малиновский, Е.И. Брюхович, Е.Л. Денисенко и др.; Под ред. Б.Н. Малиновского. - Киев: Техника, 1979, стр. 27-35, стр. 176-180. Сумматоры по модулю два известны и описаны, например, в книге Микросхемы и их применение: Справ. Пособие /В.А. Батушев, В.Н. Вениаминов, В.Г. Ковалев и др. - М.: Энергия, 1978, стр. 178-180. DV-триггеры известны и описаны, например, в книге Микросхемы и их применение: Справ. Пособие /В.А. Батушев, В. Н. Вениаминов, В. Г. Ковалев и др. - М.: Энергия, 1978, стр. 164-168 или в книге Справочник по цифровой вычислительной технике: процессоры и память. / Б.Н. Малиновский, Е.И. Брюхович, Е.Л. Денисенко и др.; Под ред. Б. Н. Малиновского. - Киев: Техника, 1979, стр. 148-152. Одновибраторы известны и описаны, например, в книге Микросхемы и их применение: Справ. Пособие /В. А. Батушев, В.Н. Вениаминов, В.Г. Ковалев и др. - М.: Энергия, 1978, стр. 193 или в книге Линейные интегральные схемы: Справочник /В.П. Шило. - М.: Советское радио, 1979, стр. 210-214. Мажоритарный элемент известен и описан, например, в книге Построение надежных вычислительных машин /У. Пирс. - М.: Мир, 1968, стр. 17.

Заявленное устройство работает следующим образом. Информационные выходы N рабочих и резервных информационных блоков 81, 82,...,8N подключены к N информационным входам К блоков каналов коммутации 1. В К блоках каналов коммутации 1 в соответствии с установленным алгоритмом работы устройства резервирования происходит проключение данных N информационных блоков 81, 82, ...,8N на информационные выходы К блоков каналов коммутации 1.

Подключение N информационных блоков 81, 82,...,8N на информационные выходы К блоков каналов коммутации 1 определяется рядом правил:

- в любой момент времени к информационному выходу одного блока каналов коммутации 1 может быть подключен только один из N информационных блоков 81, 82,...,8N;

- одновременно к информационным выходам К блоков каналов коммутации 1 должны быть подключены информационные входы от разных информационных блоков 81, 82,...,8N;

- подключение одного из N информационного блока 81, 82,...,8N на информационный выход одного из К блока каналов коммутации 1 допустимо в случае отказа одного из К находящихся в активном состоянии информационных блоков 81, 82,...,8N, при этом производится его замена любым информационным блоком 81, 82,...,8N из резервных (работоспособных, но не активных в данный момент времени);

- отказавшие (неработоспособные) информационные блоки 81, 82,...,8N от информационных выходов К блоков каналов коммутации 1 должны быть отключены до момента их восстановления (приведения в работоспособное состояние);

- замена К активных информационных блоков 81, 82,...,8N на резервные должна происходить только при устойчивых отказах, при отказах типа "сбой" смена К активных информационных блоков 81, 82,...,8N на резервные не происходит.

Приведенные выше правила определяют следующую последовательность работы устройства резервирования.

Информационная последовательность сигналов с информационного выхода мажоритарного элемента 3 поступает на общий информационный вход блока анализа 4. Одновременно информационные последовательности сигналов с информационных выходов К блоков каналов коммутации 1 поступают на соответствующие К информационные входы блока анализа 4. В результате этого в блоке анализа 4 формируется К результирующих сигналов. Эти результирующие сигналы подаются на К результирующих входов управляющего блока 5.

Блок анализа 4 (фиг. 5) представляет собой К идентичных сумматоров по модулю два 4.1. На первые входы сумматоров по модулю два 4.1 подается информационная последовательность сигналов с информационного выхода мажоритарного элемента 3, а на вторые входы - информационная последовательность сигналов с информационных выходов соответствующих К блоков каналов коммутации 1. При совпадении информационных последовательностей сигналов с информационного выхода мажоритарного элемента 3 и с информационных выходов К блоков каналов коммутации 1 на результирующих выходах К сумматоров по модулю два 4.1 будет сигнал логического "0", а при несовпадении - сигнал логической "1". Сигнал логической "1" указывает на то, что с информационного выхода соответствующего блока каналов коммутации 1 поступает искаженная информационная последовательность сигналов по причине отказа или сбоя одного из N информационных блоков 81, 82,...,8N. В результате этого необходимо принять решение на замену соответствующего отказавшего информационного блока 81, 82,...,8N на резервный (при его отказе или сбое) или на сохранение пути прохождения информационной последовательности сигналов без проведения реконфигурации устройства в целом.

Сигналы с К результирующих выходов блока анализа 4 (выходы К сумматоров по модулю два 4.1) поступают на К соответствующих результирующих входов управляющего блока 5.

Одним из основных назначений управляющего блока 5 является формирование управляющих сигналов для К блоков управления коммутаторами 2. При этом управляющие сигналы должны быть сформированы только в том случае, когда любой из К активных информационных блоков 81, 82,...,8N находится в состоянии устойчивого отказа и требует замены на резервный. Таким образом, управляющий блок 5 исключает реакцию устройства на отказы типа "сбой".

Принцип работы управляющего блока 5 (фиг.6) можно рассмотреть на примере работы анализатора сбоев 5.1. Анализатор сбоев 5.1 (фиг.7) управляющего блока 5 функционирует следующим образом. При появлении на результирующем выходе сумматора по модулю два 4.1 блока анализа 4 сигнала логической "1" сигнал одновременно поступает на первые входы таймера

5.1.1 и счетчика импульсов 5.1.2. На вторые входы таймера 5.1.1 и счетчика импульсов 5.1.2 подается синхронизирующий сигнал с выхода генератора тактовых импульсов 6. Счетчик импульсов 5.1.2 с частотой тактовой синхронизации подсчитывает количество импульсов сигнала логической "1" за установленное время, которое определяется временем работы таймера 5.1.1. Если количество импульсов сигнала логической "1" не превышает установленную норму, то по окончании работы таймера 5.1.1 счетчик импульсов 5.1.2 обнуляется. Это указывает на то, что отказ одного из информационных блоков 81, 82, . . ., 8N имел сбойный характер и его переключение на резервный не требуется. В противном случае, когда по окончании отведенного (установленного) интервала времени счетчик импульсов 5.1.2 полностью заполнится, на его выходе появится сигнал логической "1". Данный сигнал является управляющим для работы одного из К блоков управления коммутатором 2. Одновременно запускается одновибратор 5.1.3. Его время работы соответствует времени, необходимому для реализации переходных процессов в блоке управления коммутатором 2 при его реконфигурации, вызванной управляющим сигналом от счетчика импульсов 5.1.2. Сигнал с выхода одновибратора 5.1.3 является синхронизирующим сигналом блока управления коммутатором 2.

Сигналы с К дуплексных пар управляющих выходов управляющего блока 5 поступают на соответствующие управляющие входы К блоков управления коммутаторами 2.

Порядок функционирования блока управления коммутатором 2 можно рассмотреть на примере функционирования первого блока управления коммутатором 2 (фиг. 3), т. к. работа остальных К-1 блоков управления коммутаторами 2 аналогична.

Основу первого блока управления коммутатором 2 составляет кольцевой регистр сдвига, разрядами которого являются N регистров кольцевого регистра сдвига 2.1. Порядок функционирования регистра кольцевого регистра сдвига 2.1 (фиг. 4) можно рассмотреть на примере функционирования первого регистра кольцевого регистра сдвига 2.1, т.к. работа остальных N-1 регистров кольцевого регистра сдвига 2.1 аналогична.

Первый регистр кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 формирует сигнал первому блоку каналов коммутации 1 на подключение (отключение) первого информационного блока 81 к информационному выходу данного блока каналов коммутации 1. При этом разрешающим сигналом на подключение первого информационного блока 81 на информационный выход первого блока каналов коммутации 1 является сигнал логической "1", а запрещающим - сигнал логического "0".

Подготовка к работе первого регистра кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 производится следующим образом. Установочный вход 1 подключен к установочному входу  DV-триггера 2.1.4, на который подается сигнал логической "1". Установочный вход 2 подключен к установочному входу

DV-триггера 2.1.4, на который подается сигнал логической "1". Установочный вход 2 подключен к установочному входу  DV-триггера 2.1.4, на который подается кратковременный (определяемый временем протекания переходных процессов DV-триггера) сигнал логического "0". В результате этого на выходе DV-триггера 2.1.4, а следовательно, и на выходе первого регистра кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2, устанавливается сигнал логической "1".

DV-триггера 2.1.4, на который подается кратковременный (определяемый временем протекания переходных процессов DV-триггера) сигнал логического "0". В результате этого на выходе DV-триггера 2.1.4, а следовательно, и на выходе первого регистра кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2, устанавливается сигнал логической "1".

На выходах остальных N-1 регистров кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 устанавливается сигнал логического "0". Это обеспечивается подключением установочного входа 1 к установочному входу  N-1 DV-триггеров регистров кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2, а установочного входа 2 - к установочному входу

N-1 DV-триггеров регистров кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2, а установочного входа 2 - к установочному входу

Таким образом, на определяющих и отключающих выходах первого блока управления коммутатором 2 образуется кодовая комбинация, состоящая из сигнала логической "1" на выходе первого регистра кольцевого регистра сдвига 2.1 и сигналов логического "0" на выходах остальных N-1 регистров кольцевого регистра сдвига 2.1.

Сигналы с определяющих выходов первого блока управления коммутатором 2 позволяют однозначно подключить информационный выход первого информационного блока 81 на информационный выход первого блока каналов коммутации 1.

Затем на установочный вход 2 N DV-триггеров регистров кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 подается сигнал логической "1", в результате чего N DV-триггеров регистров кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 переходят в режим работы по информационному D, управляющему V и синхронизирующему С входам.

Таким образом, подготовка к работе первого блока управления коммутатором 2 завершена.

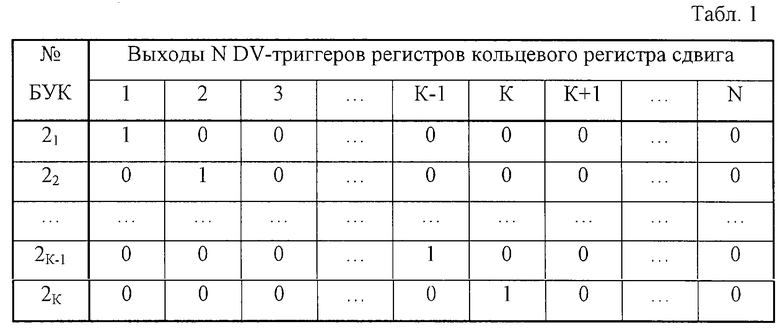

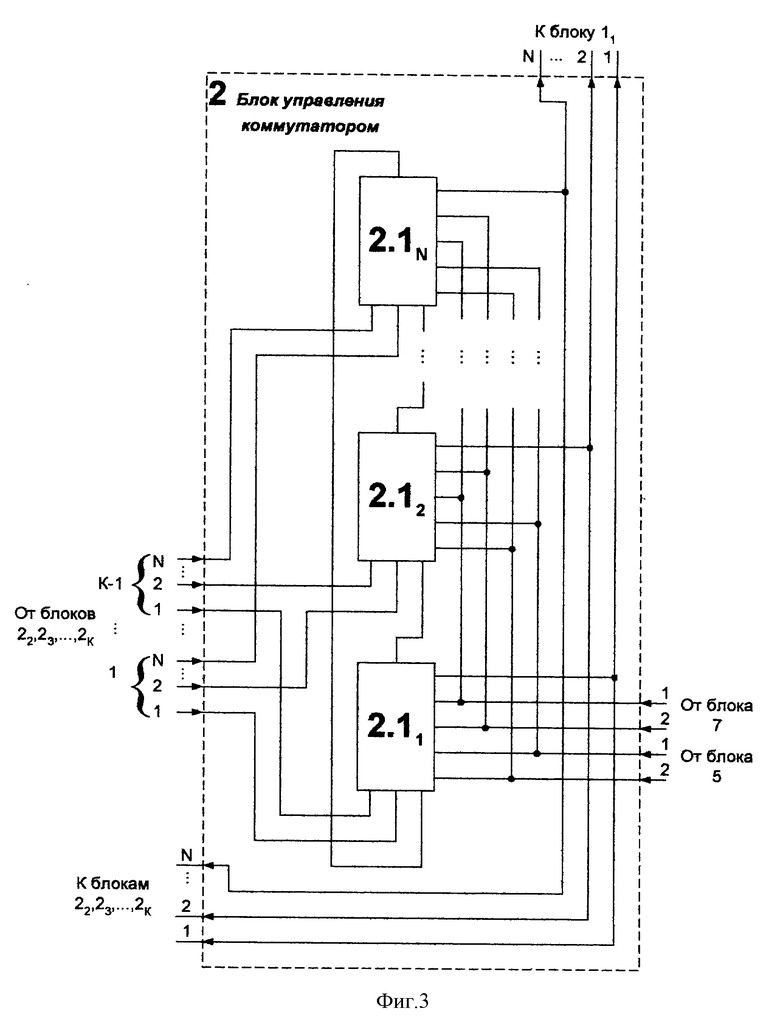

Кодовые комбинации на выходах блоков управления коммутаторами 2 после установки начального состояния представлены в табл. 1.

Сигналы с отключающих выходов первого блока управления коммутатором 2 поступают на запрещающие входы остальных К-1 блоков управления коммутаторами 2. Эти сигналы являются запрещающими для N DV-триггеров регистров кольцевого регистра сдвига данных К-1 блоков управления коммутаторами 2 на формирование определяющих сигналов соответствующим К-1 блокам каналов коммутации 1 на подключение первого информационного устройства 81 на информационный выход данных К-1 блоков каналов коммутации 1.

Аналогично сигналы с отключающих выходов остальных К-1 блоков управления коммутаторами 2 поступают на запрещающие входы первого блока управления коммутатором 2. Они также являются запрещающими для N DV-триггеров регистров кольцевого регистра сдвига первого блока управления коммутатором 2 на формирование определяющего сигнала первому блоку каналов коммутации 1 на подключение остальных информационных блоков 82, 83,...,8N на информационный выход данного блока каналов коммутации 1.

В процессе работы устройства резервирования данный алгоритм работы распространяется и на остальные К-1 блоки управления коммутаторами 2. В общем случае разрешенные кодовые комбинации на выходах N DV-триггеров регистров кольцевого регистра сдвига блоков управления коммутаторами 2 приведены в табл. 2.

Предположим, что рассматривается режим работы блоков управления коммутаторами 2 на момент времени после установки начального состояния и необходимо заменить неработоспособное первое информационное устройство 81 на работоспособное резервное.

В этом случае к управляющим входам 1 и 2 блоков управления коммутаторами 2 придет сигнал логической "1". Управляющие входы 1 и 2 проключены на синхронизирующий С и управляющий V входы N DV-триггеров. В результате чего N DV-триггеров готовы к приему сигнала по информационному входу D в течение периода времени, равному длительности сигнала логической "1" по управляющему входу 1 (синхронизирующему входу С). При этом, если на D входе DV-триггера был сигнал логической "1", то на его выходе также появится сигнал логической "1", и наоборот.

На выходе DV-триггера 2.1.4 первого регистра кольцевого регистра сдвига 2.1 блока управления коммутатором 2 присутствует сигнал логической "1". Этот сигнал логической "1" подается на второй вход элемента ИЛИ 2.1.6 и независимо от сигналов на его первом входе на его выходе также появляется сигнал логической "1". Затем сигнал логической "1" подается на второй регистр кольцевого регистра сдвига 2.1. Но по запрещающему входу от второго блока управления коммутатором 2 подается кодовая комбинация, содержащая сигнал логической "1" во втором разряде. Этот сигнал логической "1" запрещает одновременное подключение второго информационного блока 82 на выход первого блока канала коммутации 1. В результате этого сигнал логической "1" через цепь обхода DV-триггера появится на выходе второго регистра кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2. Достигнув К+1-го регистра кольцевого регистра сдвига 2.1 первого блока управления коммутатором 2 сигнал логической " 1" переведет DV-триггер в противоположное состояние. На выходе DV-триггера появится сигнал логической "1". Этот сигнал логической "1" подключит К+1-й информационный блок 8K+1 на выход первого блока каналов коммутации 1 при условии, что этот К+1-й информационный блок 8K+1 окажется не подключенным к выходу одного из остальных К-1 блоков каналов коммутации 1 и не окажется неработоспособным.

Таким образом формируется кодовая комбинация на подключение одного из резервных информационных блоков 81, 82,...,8N на информационный выход блока каналов коммутации 1.

Введение распределенной системы блоков управления коммутаторами повышает надежность данного устройства вследствие исключения возможности отключения соответствующего блока каналов коммутации из-за отказа соответствующего регистра кольцевого регистра сдвига блока управления коммутатором.

Сигналы с определяющих выходов К блоков управления коммутаторами 2 и информационных выходов N информационных блоков 81, 82,...,8N поступают соответственно на определяющие и информационные входы соответствующих К блоков каналов коммутации 1.

Рассмотрим порядок функционирования первого блока каналов коммутации 1 после установки начального состояния, так как остальные К-1 блоков каналов коммутации 1 работают аналогично.

Информационная последовательность сигналов поступает от N информационных блоков 81, 82,...,8N на информационные входы первого блока каналов коммутации 1. Информационные входы первого блока каналов коммутации 1 подключены на соответствующие первые входы N элементов И 1.1. Кодовая комбинация с определяющих выходов первого блока управления коммутатором 2 подается на определяющие входы первого блока каналов коммутации 1. При этом сигнал логической "1" подается на второй вход первого элемента И 1.1, а сигнал логического "0" - на вторые входы N-1 элементов И 1.1. На выходе первого элемента И 1.1 будет информационная последовательность сигналов, которая поступает на первый вход многовходового элемента ИЛИ 1.2. На выходах N-1 элементов И 1.1 будет сигнал логического "0", который подается на N-1 входы многовходового элемента ИЛИ 1.2. В результате этого на выходе многовходового элемента ИЛИ 1.2 будет информационная последовательность сигналов с выхода первого информационного блока 81. При подаче на определяющие входы другой кодовой комбинации на информационный выход будет подключен соответствующий информационный блок 82, 83,...,8N.

Информационная последовательность сигналов от информационных выходов К блоков каналов коммутации 1 поступает на К информационных входов блока анализа 4 и мажоритарного элемента 3, а выход мажоритарного элемента 3 является информационным выходом устройства.

Таким образом, анализ принципа работы заявляемого устройства резервирования показывает очевидность того факта, что наряду с сохраненными возможностями по реализации принципа гибридного резервирования с мажоритарным выбором выходного сигнала, автоматического отключения отказавшего рабочего канала и замещением его резервным повышена надежность устройства, связанная с включением схемы управления при отказах типа "сбой", а также с введением распределенной системы блоков управления коммутаторами. Данное устройство позволяет повысить надежность прохождения информации, что существенно расширяет область применения устройства, расширяет функциональные возможности аппаратуры, где заявленное устройство резервирования будет использовано.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР СЛУЧАЙНЫХ ЧИСЕЛ | 2001 |

|

RU2211481C2 |

| РЕГИСТР СДВИГА | 2002 |

|

RU2219597C1 |

| РЕГИСТР СДВИГА | 2003 |

|

RU2247433C2 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2001 |

|

RU2211540C2 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ РАДИОПЕРЕДАТЧИКА С ДИНАМИЧЕСКОЙ ЗАДЕРЖКОЙ | 2002 |

|

RU2221332C1 |

| РЕЗЕРВИРОВАННЫЙ УСИЛИТЕЛЬ | 2001 |

|

RU2199843C1 |

| СПОСОБ И УСТРОЙСТВО СЖАТИЯ КОДИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИЗ СИМВОЛОВ УПОРЯДОЧЕННОГО m-ИЧНОГО АЛФАВИТА В КОДИРОВАННУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ ДВОИЧНЫХ СИМВОЛОВ | 2000 |

|

RU2168857C1 |

| СПОСОБ И УСТРОЙСТВО СЖАТИЯ КОДИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИЗ СИМВОЛОВ БЕСКОНЕЧНОГО АЛФАВИТА В КОДИРОВАННУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ ДВОИЧНЫХ СИМВОЛОВ | 2000 |

|

RU2176129C1 |

| СПОСОБ РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНЫХ СТАНЦИЙ СЕТИ СПУТНИКОВОЙ СВЯЗИ, УСТРОЙСТВО РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНОЙ СТАНЦИИ И ФОРМИРОВАТЕЛЬ УПРАВЛЯЮЩЕГО СИГНАЛА | 2001 |

|

RU2214682C2 |

Изобретение относится к вычислительной технике и предназначено для построения резервированных систем высокой надежности. Техническим результатом является разработка устройства резервирования, обеспечивающего более высокую надежность устройства. Технический результат достигается за счет того, что устройство резервирования состоит из К блоков каналов коммутации, К блоков управления коммутаторами, мажоритарного элемента, блока анализа, управляющего блока, генератора тактовых импульсов, блока установки начального состояния, информационных блоков. 8 ил., 2 табл.

Устройство резервирования, содержащее К блоков каналов коммутации, где K= (2n+l), n=1, 2, 3, ..., N информационных блоков, где N≥K+1, мажоритарный элемент, блок анализа, выход i-го информационного блока, где i=1, 2,...,N, подключен к i-му информационному входу каждого из К блоков каналов коммутации, информационный выход j-гo, где j=1, 2,...,K, блока каналов коммутации подключен к j-м информационным входам мажоритарного элемента и блока анализа, информационный выход мажоритарного элемента подключен к общему информационному входу блока анализа и является информационным выходом устройства, отличающееся тем, что дополнительно введены К блоков управления коммутаторами, генератор тактовых импульсов, блок установки начального состояния и управляющий блок, предназначенный для формирования управляющих сигналов для блоков управления коммутаторами при нахождении любого из активных информационных блоков в состоянии устойчивого отказа, требующего замены на резервный, первый и второй установочные выходы блока установки начального состояния подключены соответственно к первым и вторым установочным входам каждого из К блоков управления коммутаторами, i-й определяющий выход j-гo блока управления коммутатором подключен соответственно к i-му определяющему входу j-гo блока каналов коммутации, i-й отключающий выход j-гo блока управления коммутатором подключен к i-м запрещающим входам остальных блоков управления коммутаторами, j-й результирующий выход блока анализа подключен соответственно к j-му результирующему входу управляющего блока, синхронизирующий вход которого подключен к выходу генератора тактовых импульсов, j-я пара дуплексных выходов управляющего блока подключена к соответствующей паре управляющих входов j-гo блока управления коммутатором.

| SU 1188922 A1, 30.10.1985 | |||

| Резервированное устройство | 1989 |

|

SU1605236A1 |

| Устройство для управления переключением резерва | 1974 |

|

SU546889A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕЗЕРВИРОВАНИЯ РАДИОСТАНЦИЙ | 1990 |

|

RU2018939C1 |

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| US 4562575 A, 31.12.1985 | |||

| US 4797884 A, 10.01.1989. | |||

Авторы

Даты

2003-06-27—Публикация

2001-06-15—Подача