Изобретение относится к области тестирования интегральных микросхем энергонезависимой памяти с последовательным интерфейсом и может применяться для тестирования микросхем памяти на соответствие статических параметров техническим условиям и на корректность работы при операциях чтения, записи и стирания данных.

Тестирование микросхем памяти является важным этапом процесса их производства. Рост сложности структуры микросхем памяти приводит к повышению процента брака выпуска микросхем. По оценкам экспертов, в скором будущем 90% всей площади кремниевой пластины будет занимать память разных видов [International Technology Roadmap for Semiconductors, 2007 Edition. URL: https://www.semiconductors.org/wp-content/uploads/2018/08/2007Design.pdf Дата обращения: 27.05.2023]. По этой причине наблюдается увеличение требований на качественное тестирование микросхем памяти. К тому же развитие технологий программирования памяти приводит к появлению неизвестных дефектов.

Энергонезависимые запоминающие устройства имеют широкое распространение в разных областях применения. Главной особенностью этого вида памяти является возможность долговременного хранения данных без питания микросхемы. Сложная структура (металлизированные слои) и высокая плотность размещения данных предоставляет возможность использовать энергонезависимую память в схемах с низким энергопотреблением и невысоким напряжением, что подчеркивает значимость данного вида запоминающих устройств.

Энергонезависимые микросхемы памяти с последовательным интерфейсом имеют небольшое количество выводов, благодаря чему они занимают мало места на печатной плате, при этом упрощаются проектирование связей и разводка микросхемы на плате, возрастают показатели надежности и уменьшаются уровни шумов.

В связи с тем, что неисправности оперативных запоминающих устройств не в полной мере описывают существующие дефекты постоянных запоминающих устройств, существует необходимость определять особенности появления неисправностей в энергонезависимой памяти.

Вопрос эффективности средств тестирования и диагностирования неисправностей в энергонезависимой памяти остается актуальным. Эффективность решений складывается из двух параметров: количество обнаруженных дефектов и длительность диагностики.

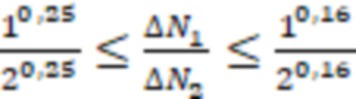

Известен способ тестирования статических оперативных запоминающих устройств с целью выявления контрафактных микросхем, бывших в употреблении, на основе свойств деградации статических оперативных запоминающих устройств (RU 2757977, МПК G01R 31/30, 25.10.2021), сущность которого заключается в следующем: производят подсчет нестабильных бит путем записи при номинальном напряжении питания (Vп=Vном) во все биты статического оперативного запоминающего устройства значение 1 или 0. Затем напряжение питания уменьшают до значения, выбранного из диапазона 0≤Vп≤2/3Vп, которое гарантированно ниже критического уровня удержания микросхемой информации. После чего все биты статического оперативного запоминающего устройства последовательно вдоль линии слов переводят в режим чтения на период, достаточный для разрядки RC константы электрической схемы. Далее содержимое статического оперативного запоминающего устройства считывают и подсчитывают количество бит, изменивших свое значение (N). Микросхему статического оперативного запоминающего устройства с записанным во все ячейки значением 1 или 0 подвергают стрессовому воздействию путем воздействия повышенной температурой и напряжением (Vстресс) в течение периода времени Δt. Способ реализуют посредством комбинации подсчета нестабильных бит и по крайней мере двух итераций стрессового воздействия и подсчета нестабильных бит, при этом после первого подсчета нестабильных бит инициализируют начальное количество нестабильных бит N0=N, после второго подсчета нестабильных бит считают приращенное количество нестабильных бит относительно первого подсчета первой итерации стресса ΔN1=N-N0, после третьего подсчета нестабильных бит считают общее приращенное количество нестабильных бит относительно второго подсчета ΔN2=N-N0, затем вычисляют истинность выражения  , истинность которого говорит о том, что микросхема статического оперативного запоминающего устройства «новая», а ложное значение - «использованная». Технический результат: выявление микросхем статического оперативного запоминающего устройства, бывших в употреблении, простым цифровым оборудованием без применения точных аналоговых измерительных приборов, посредством штатного интерфейса микросхемы, без специальных требований к ее электрической и топологической схеме, без априорной первичной информации о свойствах ее физически неклонируемых функциях.

, истинность которого говорит о том, что микросхема статического оперативного запоминающего устройства «новая», а ложное значение - «использованная». Технический результат: выявление микросхем статического оперативного запоминающего устройства, бывших в употреблении, простым цифровым оборудованием без применения точных аналоговых измерительных приборов, посредством штатного интерфейса микросхемы, без специальных требований к ее электрической и топологической схеме, без априорной первичной информации о свойствах ее физически неклонируемых функциях.

К недостаткам известного способа относятся невозможность качественного и точного определения неисправности на конкретном бите. Данный способ применим к тестированию оперативных запоминающих устройств для определение общего состоянии памяти на основе приращения значений нестабильных бит, то есть производится вероятностное определение пригодности памяти. К тому же данный способ неприменим для постоянных запоминающих устройств, так как не учитываются операции стирания. Способ не позволяет оценить соответствие статических параметров микросхемы памяти норме.

Известно энергонезависимое запоминающее устройство и способ его самотестирования (US 2007/0165454, МПК G11C I6/04, 19.07.2007), согласно которому тестовый интерфейс получает тестовую команду, обозначающую выполнение теста для ячейки памяти. Схема хранения тестов хранит тестовую информацию, необходимую для выполнения теста. Цепь тестовой памяти включает в себя стираемый программируемый блок памяти. Декодер декодирует тестовую команду, введенную в тестовый интерфейс, и выбирает тестовую информацию, хранящуюся в тестовой запоминающей схеме. Усилитель считывания считывает из тестовой схемы хранения тестовую информацию, выбранную декодером. Цепь хранения содержит тестовую информацию, считываемую усилителем считывания. Схема управления управляет тестовой операцией проверки того, нормально ли работает ячейка памяти, на основе тестовой информации, хранящейся в схеме хранения. Схема хранения дефектов формируется для ячейки памяти и сохраняет информацию об отказе, указывающую, что ячейка памяти неисправна, если ячейка памяти не работает нормально в тестовом режиме. Технический результат – сокращение времени тестирования энергонезависимого запоминающего устройства.

К недостаткам известного способа относятся невозможность определения, какую неисправность содержит конкретная ячейка памяти. Производится запись тестовой информации в конкретную ячейку памяти и сравнивается с шаблоном (ожидаемым значением), однако не проводится проверка влияние операции записи на значение в ячейках памяти на одной битовой строке. Схема хранения не производит анализ влияния операции стирания на состояние ячейки. Данный способ также не позволяет оценить соответствие статических параметров микросхемы памяти норме.

Известно устройство и способ тестирования памяти, предназначенные для восстановления ячейки памяти в системе тестирования памяти (US 9831003B2, МПК GIIC 29/44, GIIC 29/56, 28.11.2017), в котором тестовое устройство обнаруживает адрес сбоя, проверяя запоминающее устройство в соответствии с тестовой командой, и временно сохраняет адрес сбоя в памяти адреса сбоя (fail address memory, FAM). Адрес сбоя передается в запоминающее устройство в соответствии с режимом передачи адреса сбоя, временно сохраняется в памяти временного адреса сбоя запоминающего устройства, а затем сохраняется в массиве защиты от предохранителей, который является энергонезависимым запоминающим устройством. Для обеспечения надежности данных сохраненные данные могут быть считаны для проверки данных, а результат проверки может быть последовательно или параллельно передан на тестовое устройство. Технический результат – повышение эксплуатационной надежности запоминающего устройства.

К недостаткам известного способа относятся вероятность ошибки передачи адреса сбоя из тестируемого устройства по алгоритму передачи адреса сбоя. Схема хранения не производит анализ влияния операции стирания на состояние ячейки. Известный способ дорогостоящий и также не позволяет оценить соответствие статических параметров микросхемы памяти норме.

Известен способ обеспечения программируемых тестовых условий для встроенной схемы самотестирования устройства флэш-памяти (WO 2006081168, МПК G11C29/12, 03.08.2006). Способ включает предоставление интерфейса (built-in self-test, BIST), адаптированного для настройки условий тестирования, используемого в схеме BIST, предоставление ячеек памяти устройства флэш-памяти, и обеспечение схемы BIST, адаптированной для проверки флэш-памяти. Способ дополнительно содержит передачу с интерфейсом BIST одной или нескольких глобальных переменных, связанных с условием проверки, настройку условия проверки, используемого схемой BIST, на основе значений, представленных глобальными переменными, выполнение одной или нескольких тестовых операций во флэш-памяти в соответствии с настроенным тестовым условием, и сообщают о результатах операций тестирования памяти. Способ может дополнительно включать в себя среду последовательной связи и использование протокола последовательного тестирования для передачи глобальных переменных в интерфейс BIST и результатов тестирования из интерфейса. Глобальные переменные также могут быть предоставлены пользователем запоминающего устройства. Технический результат – своевременное тестирование памяти с достаточно высокой степенью охвата неисправностей без необходимости постоянного интерактивного (последовательного) контроля с помощью внешнего тестового оборудования.

К недостаткам известного способа относятся увеличение служебной площади самой микросхемы с возможным негативным влиянием на функциональность памяти. Известный способ в основном используется для производственного тестирования по принципу «годен/не годен» без определения конкретной неисправности и адреса обнаружения неисправности, необходимых для мониторинга процесса и ремонта устройства.

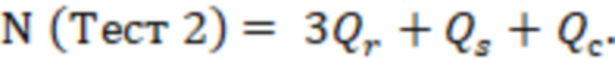

Необходимо отметить, что при создании универсального и надежного способа тестирования микросхем энергонезависимой памяти необходимо ограничить число моделей неисправностей, обнаруживаемых при тестировании, так как, во-первых, имеет смысл рассматривать неисправности, которые являются базовыми для возникновения других видов дефектов (Hamdioui S. et al. Memory fault modeling trends: A case study //Journal of Electronic Testing. – 2004. – Т. 20. – С. 245-255.). Так как обнаружить базовые дефекты проще, чем более сложные модели неисправностей, можно однозначно определить неисправность микросхемы памяти, затратив при этом меньше ресурсов. Во-вторых, число наиболее вероятных дефектов ограничено. В работе (Kang D. et al. Probability level dependence of failure mechanisms in sub-20 nm NAND flash memory //IEEE Electron Device Letters. – 2014. – Т. 35. – №. 3. – С. 348-350.) показано, что модели неисправности SAF, TF, WED, WPD, BED и BPD имеют большую вероятность появления в памяти по сравнению с другими дефектами. Описание всех моделей представлено на Фиг 1.

Первый блок дефектов относятся ко всем видам памяти:

SAF – константные неисправности ячеек памяти. Дефект характеризуется тем, что ячейка принимает одно и то же значение логического 0 или 1 и не может поменять свое состояние при выполнении любых действия с этой ячейкой.

TF – дефект переключения ячеек памяти. Дефект характеризуется тем, что при записи значения, в ячейке памяти не происходит изменений и логический 0 не может перейти в логическую 1 и наоборот (Kang D. et al. Probability level dependence of failure mechanisms in sub-20 nm NAND flash memory //IEEE Electron Device Letters. – 2014. – Т. 35. – №. 3. – С. 348-350.).

Следующий блок моделей неисправностей характерен для энергонезависимой памяти.

Модель неисправности WED (word-line erase disturbance). Нарушение возникает, когда программирование ячейки вызывает стирание значения логического 0 в соседней ячейке в той же строке слова.

Модель неисправности WPD (word-line program disturbance). Дефект возникает, когда программирование ячейки вызывает программирование на логической 0 соседней ячейки в той же строке слова.

Модель неисправности BED (line erase disturbance). Нарушения BED аналогично нарушению WED, за исключением расположения дефектных ячеек. Для помех этого типа затронутые ячейки находятся на той же битовой линии, что и выбранная ячейка.

Модель неисправности BPD (bit-line program disturbance). Нарушения BPD аналогично нарушению WPD, но дефектные ячейки находятся на той же битовой линии, что и программируемая ячейка.

Модель неисправности RD (read disturbance). Суть неисправности RD заключается в том, что после прочтения значения ячейки памяти значение изменяется на противоположное.

Модель неисправности OED (over-erase disturbance). OED характеризуется тем, что пороговое напряжение выбранной ячейки низкое и невозможно ее запрограммировать (в любом случае ячейка в состоянии «стерта»).

Существует множество способов тестирования памяти: маршевые тесты, шахматный код, галопирующий тест и многие другие. Способы отличаются временем тестирования и количеством обнаруженных дефектов.

Ниже рассмотрены наиболее часто применяемые способы тестирования памяти.

Галопирующий тест. Пример использования представлен в разработке системы тестирования памяти для измерения скачков напряжения на линиях электропередачи (Mohammad M. G. Fault model and test procedure for phase change memory //IET computers & digital techniques. – 2011. – Т. 5. – №. 4. – С. 263-270.). Суть этого способа заключается в постоянной записи байта в ячейку памяти и сравнение записанного значения с эталонным. Вначале в ячейку памяти записывается байт 0000 0000, далее производится запись 0000 0001 и осуществляется проверка на изменение первых 7 бит (сравнение с эталоном 0000 0001). После этого в эту же ячейку записывается следующий байт 0000 0010 и также проходит сравнение с шаблоном. Процесс продолжается до записи в эту ячейку значения 1000 0000. Далее запускается цикл на проверку логического 0 и записывается в эту же ячейку памяти число 1111 1111. Изменение значение числа происходит с нулевого бита с последующей проверкой оставшихся битов с эталонным значением. Таким образом, галопирующий тест позволяет провести два цикла теста на проверку логической 1 и 0. Описанный тест работает медленно и может потребовать сотни часов на объемах памяти в сотни Мбайт, соответственно такой способ тестирования памяти целесообразно использовать на небольших объемах памяти, не превышающих 6-8 Кбайт. Этот способ позволяет обнаружить SAF и TF дефекты.

«Шахматный код». Суть алгоритма заключается в следующем: логическая 1 и 0 записываются в ячейки памяти массива ячеек в шахматном порядке. Алгоритм делит ячейки на две чередующиеся группы, так что каждая соседняя ячейка находится в другой группе. Шаблон шахматной доски в основном используется для обнаружения SAF дефекта и отказов, возникающих в результате утечек, коротких замыканий между ячейками. Шаги алгоритма включают запись «шахматного» кода с порядком адресации вверх; чтение «шахматного» кода с порядком адресации вверх; запись обратного «шахматного» кода с порядком адресации вверх; чтение обратного «шахматного» кода с порядком адресации вверх.

Маршевый тест. В этих тестах применяются шаблоны, которые «маршируют» вверх и вниз по адресу памяти при записи значений и чтении значений из известных ячеек памяти. Количество маршевых элементов конечно, при этом каждый марш определяется адресной последовательностью и порядком операций записи и чтения. Последовательность определяется по инкременту, декременту или одновременному возрастанию и убыванию номера ячейки памяти. Последовательность определяется из простейших операций: запись значения логического 0 в ячейку памяти; чтение значения ячейки памяти с ожиданием логического 0; запись значения логической 1 в ячейку памяти; чтение значения ячейки памяти с ожиданием логической 1. Маршевые тесты проще в реализации и быстрее в исполнении, что отвечает требованиям бизнеса тестирования микросхем памяти. По этой причине дипломантами выбран именно этот вид тестирования для реализации программно-аппаратного комплекса по тестированию микросхем энергонезависимой памяти (Li Y. et al. Design of Memory Test System for Measuring Transmission Lines Galloping //Journal of Physics: Conference Series. – IOP Publishing, 2019. – Т. 1187. – №. 2. – С. 022027.; Ярмолик С. В. Анализ методов тестирования флэш-памяти //Доклады Белорусского государственного университета информатики и радиоэлектроники. – 2010. – №. 4 (50). – С. 62-68.).

Для энергонезависимой памяти обычных алгоритмов тестирования недостаточно. Операции и требования к испытаниям для энергонезависимой памяти отличаются от энергозависимой (Ярмолик В. Н., Леванцевич В. А., Деменковец Д. В. Анализ и синтез маршевых тестов запоминающих устройств //Цифровая трансформация. – 2021. – №. 2. – С. 45-55.; Mohammad M.Gh., Saluja K.K., Yap A. Testing flash memories // VLSI Design 2000. Wireless and Digital Imaging in the Millennium. Proceedings of 13th International Conference on VLSI Design. IEEE Comput. Soc. – P. 406–411.; Yeh J. C. et al. Flash memory testing and built-in self-diagnosis with march-like test algorithms //IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. – 2007. – Т. 26. – №. 6. – С. 1101-1113.). Оперативная память, кроме того, что она является энергозависимой, отличается от постоянной памяти отсутствием операции стирания. Таким образом необходимо изучить методы тестирования с учётом внесения в них операции стирания (Mohammad M. G., Saluja K. K. Flash memory disturbances: Modeling and test //Proceedings 19th IEEE VLSI Test Symposium. VTS 2001. – IEEE, 2001. – С. 218-224.; Van der Velde D. P., vd Goor A. J. Designing a memory module tester //Records of the 1999 IEEE International Workshop on Memory Technology, Design and Testing. – IEEE, 1999. – С. 91-98.; Kinoshita, Saluja. Built-in testing of memory using an on-chip compact testing scheme //IEEE Transactions on Computers. – 1986. – Т. 100. – №. 10. – С. 862-870.; Карташёв С. С., Лосев В. В., Крупкина Т. Ю. Исследование и разработка схемы последовательного доступа к flash-памяти //Известия высших учебных заведений. Электроника. – 2016. – Т. 21. – №. 5. – С. 478-481.).

Для тестирования энергонезависимой памяти используются расширенные алгоритмы маршевого тестирования – Flash-March и March-FT.

Flash-March – один из первых маршевых тестов, предназначенных для энергонезависимой памяти (Yeh J. C. et al. Flash memory testing and built-in self-diagnosis with march-like test algorithms //IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. – 2007. – Т. 26. – №. 6. – С. 1101-1113.).

Его последовательность выглядит следующим образом (формула (1)):

C;↑(R1,S);↕(R0);C;↓(R1,S);↕(R0) (1)

где:

Операция C – Clear означает стирание памяти, она устанавливает значения всех ячеек в 1, стрелки указывают направление операций, с начала в конец или из конца в начало.

Операция R1 – Read 1 чтение с ожиданием 1 в ячейках.

Операция R0 – Read 0, соответственно, операция чтения с ожиданием 0 в прочитанных ячейках.

S – Set установка в 0.

Операции, указанные в скобках, выполняются одна за другой к одной ячейке и только после выполнения идёт переход к следующей (по направлению стрелки) ячейке, пока итерация не достигнет конца или начала памяти.

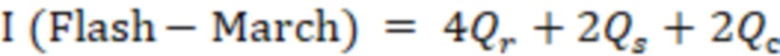

Сложность этого теста рассчитывается по общему количеству циклов чтения R (Qr), операциям установки S (Qs), стирания C (Qc) и основным аргументов является емкость памяти Q. Соответственно сложность Flash-March I рассчитывается по формуле (2):

(2)

(2)

March-FT – следующий представитель поколения маршевых тестов для энергонезависимой памяти (Yeh J. C. et al. Flash memory testing and built-in self-diagnosis with march-like test algorithms //IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. – 2007. – Т. 26. – №. 6. – С. 1101-1113.).

March-FT представляет собой следующую последовательность (3):

C;↑(R1,S,R0);↕(R0);C;↓(R1,S,R0);↕(R0) (3)

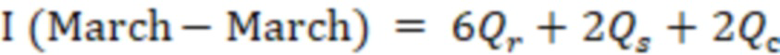

В отличие от Flash-March в этом тесте производится двойное чтение установки логического нуля. Сложность N рассчитывается по формуле (4):

(4)

(4)

Основным недостатком рассмотренных маршевых тестов является их сложность и длительность выполнения диагностики.

Предлагаются способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления.

Способ тестирования микросхем энергонезависимой памяти отличается тем, что Тест 1, Тест 2, Тест 3, предназначенные для тестирования микросхем энергонезависимой памяти, проводятся выборочно либо последовательно друг за другом, по завершению каждого из тестов, причем команды внутри каждого теста выполняются в строгой последовательности: Тест 1 производится со следующей последовательностью: C;↑(R1, S);↓(R0): операция стирания значений во всех ячейках памяти, затем следует операция чтения ячеек памяти в прямой последовательности по инкременту, и если значение ячейки равно логической 1, то происходит установка в эту ячейку логического 0, далее идёт операция считывания в обратной последовательности по декременту с ожиданием значения логического 0; Тест 2 производится со следующей последовательностью: C;↑(R1,S,R0);↓(R0): начинается с операции стирания и установки логической 1, далее следует операция чтения ячеек памяти с начала в конец по инкременту с ожиданием логической 1, после этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается, затем считываются все ячейки в обратном порядке; Тест 3 производится со следующей последовательностью: C;↑(R1,S);C;↓(R1,S,R0);↑(R0), который начинается с операции стирания, после этого из начала в конец идут операции чтения и установки в 0, далее следует операция чтения ячеек памяти с конца по инкременту с ожиданием логической 1, после этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается, затем считываются все ячейки в прямом порядке.

Устройство для осуществления способа тестирования микросхем энергонезависимой памяти содержит центральное вычислительное устройство для подачи управляющих сигналов на источник питания, мультиметр и микроконтроллер, источник питания, необходимый для подачи входного напряжения на микросхему энергонезависимой памяти и схемы реле, мультиметр для измерения статических параметров микросхемы энергонезависимой памяти, микроконтроллерную плату оснастки, причем микроконтроллерная плата оснастки состоит из микроконтроллера, предназначенного для отправки команд, соответствующих последовательностям выполнения команд Теста 1, Теста 2, Теста 3, в микросхему энергонезависимой памяти и получения от нее проверяемых значений, схем реле, предназначенных для переключения режима работы при измерении статических параметров микросхемы энергонезависимой памяти, и матрицы транзисторов, обеспечивающей управление реле от микроконтроллера. Центральное вычислительное устройство соединяется с источником питания и мультиметром через интерфейс USB и с микроконтроллером платы оснастки через интерфейс USB-UART. Микросхема энергонезависимой памяти с последовательным доступом подключается к микроконтроллеру через интерфейс I2C.

Техническая задача, на решение которой направлено заявляемое изобретение, заключается в проведении качественного функционального тестирования микросхем энергонезависимой памяти.

Техническим результатом заявленного изобретения является расширение диапазона определения дефектов энергонезависимой памяти: выявление SAF, TF, WED, WPD, BED, BPD, RD и OED в микросхемах энергонезависимой памяти, сокращение сложности и длительности выполнения тестирования.

Для решения поставленной технической задачи предлагаются способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления.

Способ тестирования микросхем энергонезависимой памяти отличается тем, что Тест 1, Тест 2, Тест 3, предназначенные для тестирования микросхем энергонезависимой памяти, проводятся выборочно либо последовательно друг за другом, по завершению каждого из тестов, причем команды внутри каждого теста выполняются в строгой последовательности: Тест 1 производится со следующей последовательностью: C;↑(R1, S);↓(R0): операция стирания значений во всех ячейках памяти, затем следует операция чтения ячеек памяти в прямой последовательности по инкременту, и если значение ячейки равно логической 1, то происходит установка в эту ячейку логического 0, далее идёт операция считывания в обратной последовательности по декременту с ожиданием значения логического 0; Тест 2 производится со следующей последовательностью: C;↑(R1,S,R0);↓(R0): начинается с операции стирания и установки логической 1, далее следует операция чтения ячеек памяти с начала в конец по инкременту с ожиданием логической 1, после этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается, затем считываются все ячейки в обратном порядке; Тест 3 производится со следующей последовательностью: C;↑(R1,S);C;↓(R1,S,R0);↑(R0), который начинается с операции стирания, после этого из начала в конец идут операции чтения и установки в 0, далее следует операция чтения ячеек памяти с конца по инкременту с ожиданием логической 1, после этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается, затем считываются все ячейки в прямом порядке.

Устройство для осуществления способа тестирования микросхем энергонезависимой памяти содержит центральное вычислительное устройство для подачи управляющих сигналов на источник питания, мультиметр и микроконтроллер, источник питания, необходимый для подачи входного напряжения на микросхему энергонезависимой памяти и схемы реле, мультиметр для измерения статических параметров микросхемы энергонезависимой памяти, микроконтроллерную плату оснастки, причем микроконтроллерная плата оснастки состоит из микроконтроллера, предназначенного для отправки команд, соответствующих последовательностям выполнения команд Теста 1, Теста 2, Теста 3, в микросхему энергонезависимой памяти и получения от нее проверяемых значений, схем реле, предназначенных для переключения режима работы при измерении статических параметров микросхемы энергонезависимой памяти, и матрицы транзисторов, обеспечивающей управление реле от микроконтроллера. Центральное вычислительное устройство соединяется с источником питания и мультиметром через интерфейс USB и с микроконтроллером платы оснастки через интерфейс USB-UART. Микросхема энергонезависимой памяти с последовательным доступом подключается к микроконтроллеру через интерфейс I2C.

Осуществление описанного способа тестирования микросхем энергонезависимой памяти и устройства для его осуществления позволяет достигнуть заявленного технического результата – расширения диапазона определения дефектов энергонезависимой памяти: выявления SAF, TF, WED, WPD, BED, BPD, RD и OED в микросхемах энергонезависимой памяти, сокращения сложности и длительности выполнения тестирования.

Таким образом техническая задача, заключающаяся в проведении качественного функционального тестирования микросхем энергонезависимой памяти, решается за счет масштабирования покрытия неисправностей. Модели неисправностей возможно обнаружить на этапе чтения значений в памяти. Для того, чтобы определить какие неисправности может обнаружить алгоритм необходимо последовательно проанализировать команды теста.

Тест 1 представляет алгоритм со следующей последовательностью: C;↑(R1, S);↓(R0): сначала производится операция стирания значений во всех ячейках памяти. После этого следует операция чтения ячеек памяти в прямой последовательности по инкременту, и если значение ячейки равно логической 1, то происходит установка в эту ячейку логического 0. Далее идёт операция считывания в обратной последовательности по декременту с ожиданием значения логического 0.

Тест 1 позволяет обнаружить SAF и OED дефекты. Обнаружить SAF неисправность можно по первой паре команд C стирания и R1 чтения с ожиданием логической 1. Во время выполнения команды стирания происходит побайтовая запись логической 1 во все ячейки памяти, затем срабатывает команда чтения значений в этих ячейках с прямой адресацией с ожиданием логической 1 и если обнаружен логический 0, то эта ячейка идентифицируется, как «зараженная» константой неисправностью SAF. OED возможно обнаружить последующей парой команд S установкой 0 и R0 чтением с ожиданием 0. Соответственно если после установки 0 обнаружена логическая 1, чтением с обратной адресацией, то фиксируется неисправность стирания в этой ячейки памяти.

Тест 1 позволяет сократить время тестирования в 2 раза.

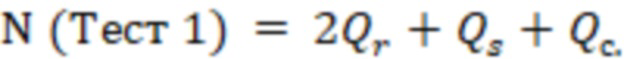

Сложность данного теста минимальна и рассчитывается по формуле (5):

(5)

(5)

Тест 2 определяется как последовательность: C;↑(R1,S,R0);↓(R0: начинается с операции стирания и установки логической 1. Далее следует операция чтения ячеек памяти с начала в конец по инкременту с ожиданием логической 1. После этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается. Далее считать все ячейки в обратном порядке.

Тест 2 помимо ранее описанных дефектов позволяет обнаружить неисправность чтения RD. Данную ошибку можно обнаружить на этапе последнего чтения. После первого чтения с ожиданием 0, производится повторное чтение с ожиданием 0, и если считанные значения байтов отличается от первого чтения, то это характеризуется наличием дефекта RD.

Тест 2 позволяет сократить время тестирования в 2 раза по сравнению с более сложными тестами Flash-March и March-FT.

Сложность этого теста можно определить по следующей формуле (6):

(6)

(6)

Тест 3 имеет следующую последовательность: C;↑(R1,S);C;↓(R1,S,R0);↑(R0).

Как и предыдущие тесты, алгоритм начинается с операции стирания. После этого из начала в конец идут операции чтения и установки в 0. Далее следует повторение операций из Тест 2, но «марш» совершается в противоположном направлении. Тест 3 значительно сложнее первого и второго теста и соответственно предполагается, что этот тест позволяет обнаружить большее количество дефектов. SAF дефект возможно обнаружить на первом чтении. Далее производятся команды установки 0 прямой адресацией с последующей операцией стиранием. После этой пары операций, считыванием с обратной адресацией и ожиданием 1, будет возможно обнаружить дефект переключения TF. Последующая операция чтения R0 позволяет обнаружить неисправность стирания OED по принципу, как в тесте 1 и 2. Последняя команда чтения позволяет обнаружить ошибку чтения RD.

Сложность теста определяется по формуле (7):

. (7)

. (7)

Устройство для осуществления заявленного способа содержит центральное вычислительное устройство, источник питания 5,0 В с разрешением 1 мВ, мультиметр, измеряющий постоянный ток в диапазоне 200.000 мкА с разрешением 1 нА, микроконтроллер на 400 кГц, матрицу транзисторов (набор ключей) 50,0 В 0,35 A, электромагнитное реле 10 А, подключенные к выходам 1C-7C матриц транзисторов, входы которых подключены ко входам RD0-11 микроконтроллера, операционный усилитель 160 МГц, USB коннектор, конденсаторы 33 пкФ – 100 нФ, резисторы 27 – 15к Ом, диоды 10 В, 500 мВт. В качестве переключателей использованы электромагнитные реле, которые подсоединены к управляющему модулю через матрицы транзисторов. Использование реле вместо микроамперметра позволяет сократить материальные затраты. Также необходимо обеспечить переключение между контактами для установки нужного режима измерения. Ручное переключение затратно по времени, а реле позволят обеспечить простое решение для автоматического переключения. Вместо реле можно использовать простое соединение и, меняя его, измерять в различных режимах, однако с помощью реле под управлением модулем возможно измерение всех токов утечки без каких-либо дополнительных действий со схемой измерений. К тому же использование активных элементов вместо реле привело бы к тому, что нужно проводить метрологические операции.

К контактам микроконтроллера SCL и SDA подключены контакты памяти SCK, SDA, вход WP заземлён. Данный интерфейс имеет всего две линии связи – SCL и SDA, по которым необходимо проводить параметрический контроль. В отличие от I2C интерфейс SPI имеет 4 линии связи, что приводит к усложнению процесса измерения статических параметров в 2 раза.

Для связи между микроконтроллером и центральным вычислительным устройством используется интерфейс USB/UART, так как он подходит для подключения одного устройства и позволяет быстро обмениваться данными. UART универсальный приемник-передатчик, который позволяет настроить соединение между компьютером и микроконтроллером. Для приема и передачи используется аппаратный модуль UART микроконтроллера. При передаче данных по интерфейсу USB/UART используется скорость обмена 19200 бит, 1 стоп бит.

Для связи между центральным вычислительным устройством и оснасткой используется интерфейс USB/USB, так как он позволяет подключить одновременно много устройств оснастки, в частности источник питания и мультиметр.

Устройство тестирования микросхем энергонезависимой памяти работает следующим образом. С персонального компьютера поступают сигналы по интерфейсу USB, содержащие информацию обо всех параметрах тестируемой микросхемы ПЗУ, а также обо всех условиях проводимого тестирования и выбранном алгоритме. Через преобразователь интерфейса USB в UART данная информация по интерфейсу UART попадает в микроконтроллер, который обрабатывает ее и подает управляющие сигналы на блок выбора источника питания, на основании которых происходит подключение требуемого источника к испытуемой микросхеме памяти.

Реле подключены к выходам 1C-7C матриц транзисторов ULN2003A, входы которых подключены ко входам RD0-11 микроконтроллера. Использование ULN2003A в режиме ключа обусловлено тем, что ток реле достаточно высок и подключать реле напрямую к выходам микроконтроллера невозможно. Схема с реле RL1-9 позволяет измерять токи утечек в разных режимах, переключение RL10 позволяет измерить ток потребления, а переключение RL11 выходное напряжение. Управляя реле с помощью микроконтроллера, можно задавать различные режимы измерения. Например, по умолчанию контакты памяти SCK, SDA подключены к контактам микроконтроллера SCL и SDA, соответственно, вход WP заземлён. При подаче питания на вход RD4 микроконтроллером реле RL4 и RL5 переключаются в другое положение, таким образом, подключая SCK и SDA к земле. Данное переключение реле позволяет закончить функциональный контроль и начать проведение параметрического, то есть начать измерять ток утечки микросхемы в различных режимах работы. Топология печатной платы устройства изображена на Фиг. 2. Ток утечки измеряется на трех данных входах-выходах (SDA, SCL и WP) при различных режимах работы микросхемы. Режимы работы задаются путём подачи питания либо заземления каждого из контактов микросхемы памяти. Всего возможно реализовать 6 режимов работы микросхемы. 4 режима для измерения токов утечек: SCL- SDA+ WP-, SCL+ SDA+ WP-, SCL+ SDA- WP+, SCL+ SDA+ WP+. Один режим для измерения тока потребления SCL+ SDA+ WP- и один режим для измерения выходного напряжения низкого уровня SCL+ SDA+ WP+. Полное описание состояние сигналов SCL, SDA и WP представлено в таблице 1.

Таблица 1 – Режимы работы микросхемы

В память микроконтроллера (МК) загружена программа, содержащая готовые алгоритмы испытания микросхем энергонезависимой памяти, а также всевозможные интерфейсы и ключевые флаги, необходимые для работы с периферийными устройствами.

После подачи напряжения питания на тестер супервизором формируется сигнал сброса и происходит запуск программы из памяти микроконтроллера. Согласно программе, выполняется инициализация портов и интерфейсов микроконтроллера. Для организации узла необходимо его проинициализировать. Для этого необходимо направление порта Tx сделать выходом, а Rx входом. Tx это шестой бит регистра TRISC, Rx седьмой. Далее необходимо определить значение генератора скорости передачи SPBRG. Значение можно определить по формуле (8):

SPBRG = (F_CPU /(ω*φ))-1 (8)

где F_CPU – частота процессора, определяем, как отношение частоты микроконтроллера к тактовой частоте (#define F_CPU 10000000/64);

ω – тактовая частота процессора;

φ – скорость передачи данных (φ=19200).

После этого необходимо провести инициализацию регистра статуса и контроля и передачи данных TXSTA и регистр состояния и контроля приемки RCSTA. Далее необходимо провести настройку работы последовательного порта по прерыванию. Для этого необходимо 4 (TXIE) и 5 (RCIE) бит регистра разрешения прерывания PIE1 перевести в режим «разрешить», присвоив битам значение логической 1. Бит TXIE позволяет разрешить прерывание передачи сообщения по UART, а RCIE разрешит прерывание приема. На этом инициализация UART выполнена.

Далее по последовательному порту необходимо передать сообщение непосредственно на компьютер, согласно структурной схеме комплекса и временной диаграмме. Для этого сначала ожидаем получение флага прерывания и после этого необходимо запустить проверку заполнения регистра состояния и контроля приемника RCSTA, за это отвечает первый бит переполнения. Если он принимает значение логического 0, то ошибки приемки нет, иначе ошибка есть. Если ошибки приемки не нет, необходимо отключить приемку путем установки бита CREN в 0. По истечению времени задержки приемки, необходимо включить приемку следующим образом: RCSTA.CREN=1.

Для написания работы алгоритма I2C необходимо описать инициализацию регистров, функции отправки стартового, повторного стартового, стопового импульсов, импульсов подтверждения и отклонения, а также функций записи и чтения. Функции записи и чтения написаны в нескольких вариациях, для возможности отправки одного байта или массива байт. Регистры SSPSTAT, SSPCON1 и SSPCON2 необходимы для включения MSSP модуля, который позволяет подавать тактовые сигналы по модулю SCL. Данные регистры настраиваются по-разному в зависимости от того, какой интерфейс используется SPI или I2C.

Регистр TRISC устанавливает биты PORTC, как входы или выходы. Например, для того чтобы установить B6, как выход, необходимо B6 установить в 0. Соответственно для настройки регистра, как входя, необходимо значение бита установить в логическую 1. SSPADD регистр устанавливает частоту обмена данными по I2C протоколу, поэтому там используются переменные, для вычисления необходимой частоты.

После этого возможно реализовать передачу и прием слова по интерфейсу I2C. Для этого необходимо открыть коммуникацию ведущего и ведомого устройства, запустить цикл while, посылая адрес памяти с командой записи. Ожидая пока ведомое устройство свободно, запустить restart интерфейса по передачи сообщения и циклом for производить запись каждого байта.

Алгоритм чтение сообщения, поступившего в ведомое устройство, аналогичен записи, однако со своим набором команд. Здесь важно правильно настроить регистр NACK, иначе чтение будет нарушено. На протяжении всей длительности цикла активного программирования микросхема не воспринимает внешнее обращение по I2C-шине. Время цикла стирания/записи измеряется (контролируется) установлением времени обращения к микросхеме. Если микросхема выдает подтверждение при последующем обращении, то цикл программирования уже закончился. Если не выдает, то цикл программирования еще продолжается.

После подтверждения исправности тестера в программном обеспечении (ПО) требуется задать все основные параметры испытуемой микросхемы памяти:

рабочее напряжение шины I2C тестируемой микросхемы;

напряжение питания;

COM-порт, к которому подключен тестер;

разрядность шины адреса;

значение тока утечки на выводах в зависимости от режима испытания;

допустимое значение отклонения тока утечки, согласно ТУ.

Все указанные выше данные, необходимые для корректной работы тестера с данной микросхемой памяти, записываются в регистры микроконтроллера и автоматически извлекаются им в ходе выполнения программы. Сразу подключается необходимый источник питания, настройки драйверов, компараторов и нагрузки активируют соответствующие режимы измерения статических параметров, контролирующих выводы шины данных.

Для контроля приборов используется спецификация IEEE-488, которая описывает интерфейс подключения к цифровым приборам. В данной спецификации описаны стандартные команды для программируемых цифровых приборов. Одной из таких команд является команда «*IDN?» которая запрашивает ID прибора. С использованием данной команды в программно-аппаратном комплексе происходит инициализация мультиметра и источника питания по их ID. После инициализации приборов используются специальные команды из системы команд RIGOL. Данная система различна для приборов и описана в документации на них. Для установки напряжения используется команда ":APPLy CH1,5,0", которая устанавливает напряжение канала 1 в источнике питания равное пяти вольтам. После этого используется команда ":OUTPut CH1,ON", которая открывает/включает этот канал. Для измерения тока и отправки результатов измерения мультиметру подаётся команда ":MEASure:CURRent:DC?".

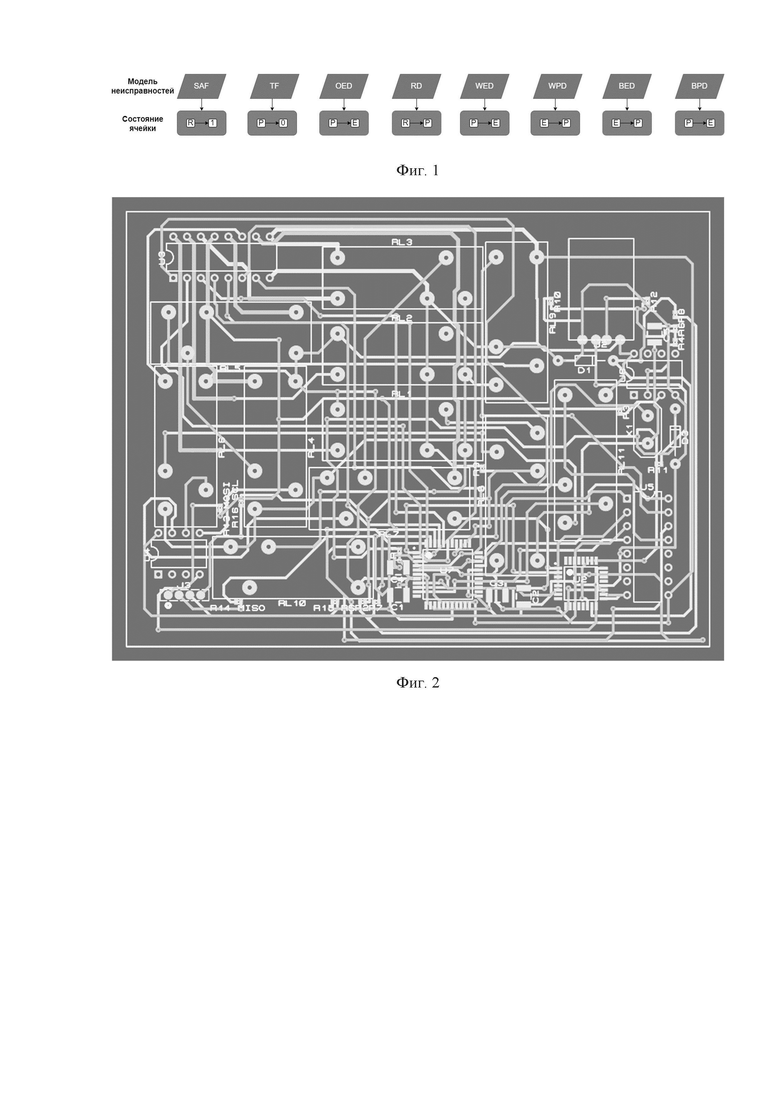

После успешного подключения оснастки и установки связи управляющего устройства с микроконтроллером предоставляется выбор вида тестирования интегральной микросхемы памяти. Для проведения функционального контроля (обнаружение неисправностей) необходимо выбрать один из тестов в левой части экрана, в зависимости от того какие неисправности нужно исследовать. По результатам тестирования будет сформирован файл в формате xml с подробным описанием оценки проведенного контроля, согласно Фиг. 3.

Такой формат выбран благодаря его независимости от платформы, он отвечает международному стандарту и имеет строгий синтаксис, что позволяет документу быть простым и непротиворечивым.

По результатам тестирования будет предоставлена оценка исправности интегральной микросхемы. В случае обнаружения неисправности будет предоставлена информация о количестве неисправных байт.

В дополнении будет высчитан общий процент неисправных байт. Более подробный отчет по тестированию будет сохранен в файл протокола.

Формат протокола следующий:

<Memory_name> объявляется имя объекта контроля. Данные берутся из подготовленного файла пользователем </Memory_name>

<Functional_testing> описание функционального контроля: name - название метода тестирования, time - время тестирования и memory_size - емкость объекта контроля.

объявляется список неисправностей и номер бита, где дефект обнаружен.

<Functional_outcome> объявляется количество неисправных байт </Functional_outcome>

<Functional_result> объявляется результат функционального контроля – Годен/Не годен </Functional_result>. Функциональный тест закончен </Functional_testing>.

<Param_testing> старт описания результатов параметрического контроля.

<param> описание режима измерения токов утечки согласно таблице 1.

<Standart> описание значения нормы: единица измерения значения нормы тока утечки, допустимая погрешность при измерении в % и значение нормы согласно ТУ </Standart>

<acceptance> объявляется результат параметрического контроля для заданного режима – Норма/Не норма <acceptance>

<Param_result> объявляется результат параметрического контроля для микросхемы. Параметрическое тестирование закончено </Param_testing>.

<Result> объявляется результат функционального и параметрического контроля – Годен/Не годен </Result>

В случае, если обнаружена неисправность в ходе функционального тестирования, микросхема считается негодной.

При параметрическом контроле в случае отклонения параметра от нормы микросхема считается негодной.

В результате предлагаемое изобретение позволяет проводить в полном объеме функциональный и параметрический контроль микросхем энергонезависимой памяти.

Заявляемое изобретение иллюстрируется чертежами, где:

на Фиг. 1 представлено описание всех моделей неисправностей, обнаруживаемых при тестировании;

на Фиг. 2 представлена топология печатной платы устройства;

на Фиг. 3 представлен файл в формате xml с подробным описанием оценки проведенного контроля;

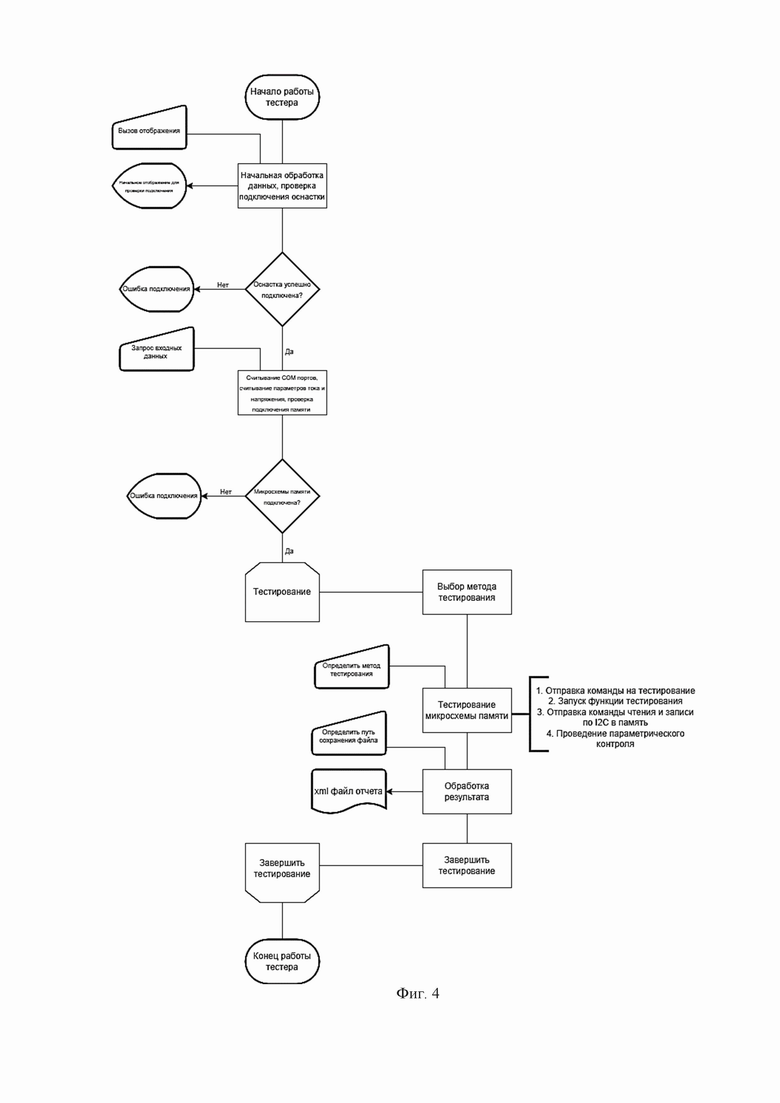

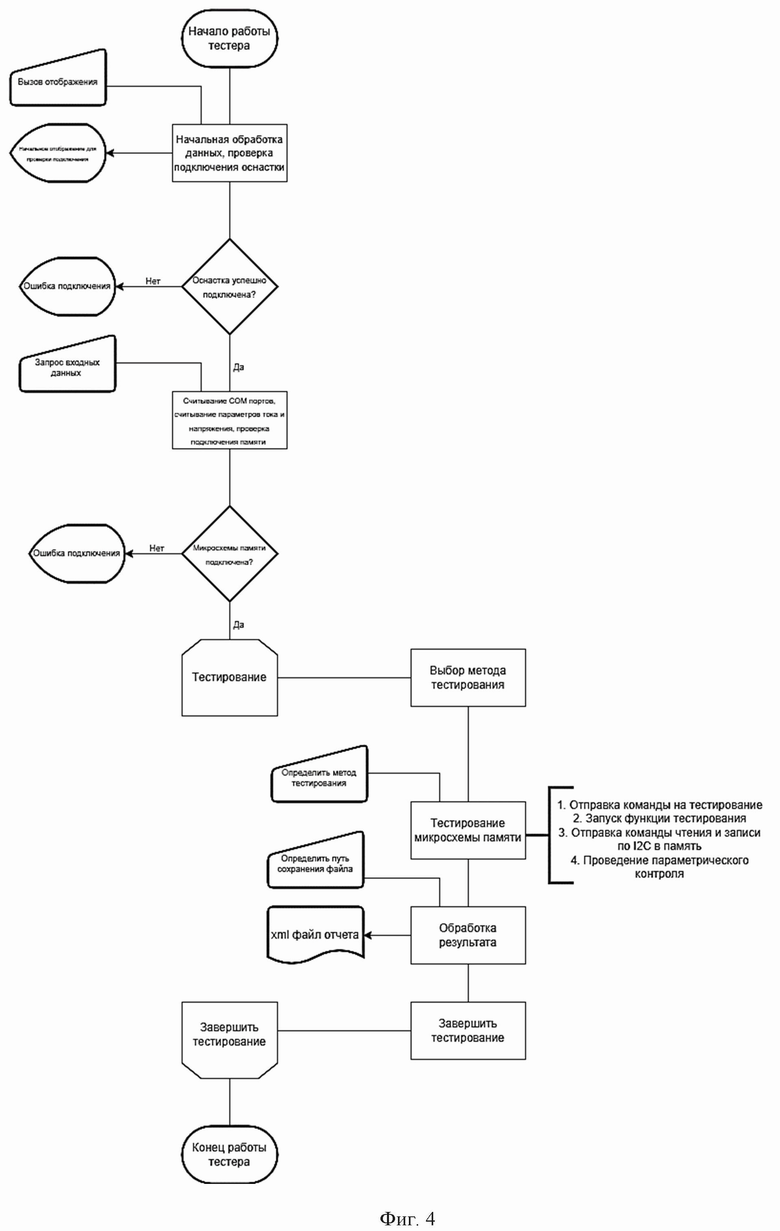

на Фиг. 4 показан полный алгоритм работы устройства.

Ниже изобретение иллюстрируется следующими примерами.

Пример 1. В таблице 2 показаны результаты моделирования энергонезависимой памяти 256 байт (256x8), буфер записи страницы до 8 байт.

Таблица 2 – Результаты тестирования микросхемы памяти IN24LC02BN

Таблица 3– Среднее время тестирования микросхемы памяти IN24LC02BN

При использовании заявленного способа время обнаружения неисправности сокращается с O( ) до O(

) до O( ).

).

Пример 2. Работу комплекса осуществляли по следующим шагам:

Проверка подключаемых устройств – источники питания и измерительные приборы.

Считывание значений напряжения и тока, определение COM порта для определения платы оснастки. Проверка подключения интегральной микросхемы и микроконтроллера.

Проведение функционального и параметрического контроля микросхемы памяти.

Обработка и вывод результатов тестирования пользователю.

Полный алгоритм работы устройства показан на Фиг. 4.

Методы испытаний описаны в таблице 4.

Таблица 4 – Методы испытаний

Подключить мультиметр RIGOL DM3068 к микроконтроллерной оснастке согласно принципиальной схеме комплекса.

В приложении нажать на кнопку «Подключить источник питания и амперметр»

Кнопка «Перейти к подключению микросхемы памяти» доступна.

Задать напряжение питания тестируемой микросхемы согласно ТУ – 5 Вольт.

Выбрать COM порт подключения комплекса. В случае необходимости обновить список доступных портов.

Выбрать путь к файлу, в котором согласно образцу* заполнены параметры микросхемы. Файл формата txt.

Нажать на кнопку «Проверить подключение микросхемы памяти и микроконтроллера»

Приложении выдаст сообщение об успешном подключении микроконтроллера и микросхемы памяти.

Кнопка «Перейти к подключению микросхемы памяти» доступна.

Выбрать путь сохранения файла с результатом тестирования или оставить по умолчанию.

Нажать на кнопку «Начать тестирование»

Нажать на кнопку «В меню»

Общий процент неисправных байт.

Заполненный протокол испытаний.

Зафиксировать время исполнения теста.

Выбрать путь сохранения файла с результатом тестирования или оставить по умолчанию.

Нажать на кнопку «Начать тестирование»

Нажать на кнопку «В меню»

Общий процент неисправных байт.

Заполненный протокол испытаний.

Зафиксировать время исполнения теста.

Выбрать путь сохранения файла с результатом тестирования или оставить по умолчанию.

Нажать на кнопку «Начать тестирование»

Нажать на кнопку «В меню»

Общий процент неисправных байт.

Заполненный протокол испытаний.

Зафиксировать время исполнения теста.

Выбрать путь сохранения файла с результатом тестирования или оставить по умолчанию.

Нажать на кнопку «Начать тестирование»

Нажать на кнопку «В меню»

Общий процент неисправных байт.

Заполненный протокол испытаний.

Зафиксировать время исполнения теста.

Выбрать путь сохранения файла с результатом тестирования или оставить по умолчанию.

Нажать на кнопку «Начать тестирование»

Нажать на кнопку «В меню»

Общий процент неисправных байт.

Заполненный протокол испытаний.

Зафиксировать время исполнения теста.

Выбрать путь сохранения файла с результатом тестирования или оставить по умолчанию.

Нажать на кнопку «Начать тестирование»

Нажать на кнопку «Закрыть программу»

Таким образом, вышеизложенное описание свидетельствует о выполнении при использовании заявленного изобретения следующей совокупности условий:

средство, воплощающее заявленное изобретение, при его осуществлении, предназначено для тестирования микросхем памяти на соответствие статических параметров техническим условиям и на корректность работы при операциях чтения, записи и стирания данных;

для заявленного способа, в том виде как оно охарактеризовано в изложенной формуле изобретения, подтверждена возможность его осуществления с помощью описанных в заявке средств и методов;

средство, воплощающее заявленное изобретение при осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата – расширения диапазона определения дефектов энергонезависимой памяти: выявления SAF, TF, WED, WPD, BED, BPD, RD и OED в микросхемах энергонезависимой памяти, сокращения сложности и длительности выполнения тестирования.

Изобретение относится к способу и устройству тестирования микросхем энергонезависимой памяти. Технический результат заключается в расширении диапазона определения дефектов энергонезависимой памяти. В способе Тест 1, Тест 2, Тест 3, предназначенные для тестирования микросхем энергонезависимой памяти, проводятся выборочно либо последовательно друг за другом, по завершении каждого из тестов, причем команды внутри каждого теста выполняются в строгой последовательности: Тест 1 производится со следующей последовательностью: C;↑(R1, S);↓(R0): операция стирания значений во всех ячейках памяти, затем следует операция чтения ячеек памяти в прямой последовательности по инкременту, и если значение ячейки равно логической 1, то происходит установка в эту ячейку логического 0, далее идёт операция считывания в обратной последовательности по декременту с ожиданием значения логического 0; Тест 2 производится со следующей последовательностью: C;↑(R1,S,R0);↓(R0): начинается с операции стирания и установки логической 1, далее следует операция чтения ячеек памяти с начала в конец по инкременту с ожиданием логической 1, после этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается, затем считываются все ячейки в обратном порядке; Тест 3 производится со следующей последовательностью: C;↑(R1,S);C;↓(R1,S,R0);↑(R0), который начинается с операции стирания, после этого из начала в конец идут операции чтения и установки в 0, далее следует операция чтения ячеек памяти с конца по инкременту с ожиданием логической 1, после этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается, затем считываются все ячейки в прямом порядке. 2 н. и 2 з.п. ф-лы, 4 ил., 4 табл.

1. Способ тестирования микросхем энергонезависимой памяти, характеризующийся тем, что Тест 1, Тест 2, Тест 3, предназначенные для тестирования микросхем энергонезависимой памяти, проводятся выборочно либо последовательно друг за другом, по завершении каждого из тестов, причем команды внутри каждого теста выполняются в строгой последовательности: Тест 1 производится со следующей последовательностью: C;↑(R1, S);↓(R0): операция стирания значений во всех ячейках памяти, затем следует операция чтения ячеек памяти в прямой последовательности по инкременту, и если значение ячейки равно логической 1, то происходит установка в эту ячейку логического 0, далее идёт операция считывания в обратной последовательности по декременту с ожиданием значения логического 0; Тест 2 производится со следующей последовательностью: C;↑(R1,S,R0);↓(R0): начинается с операции стирания и установки логической 1, далее следует операция чтения ячеек памяти с начала в конец по инкременту с ожиданием логической 1, после этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается, затем считываются все ячейки в обратном порядке; Тест 3 производится со следующей последовательностью: C;↑(R1,S);C;↓(R1,S,R0);↑(R0), который начинается с операции стирания, после этого из начала в конец идут операции чтения и установки в 0, далее следует операция чтения ячеек памяти с конца по инкременту с ожиданием логической 1, после этого каждая ячейка с первой по последнюю считывается, на случай если какие-либо из ячеек изменили свои значения, устанавливается в логический 0 и сразу считывается, затем считываются все ячейки в прямом порядке.

2. Устройство для осуществления способа по п. 1, которое содержит центральное вычислительное устройство для подачи управляющих сигналов на источник питания, мультиметр и микроконтроллер, источник питания, необходимый для подачи входного напряжения на микросхему энергонезависимой памяти и схемы реле, мультиметр для измерения статических параметров микросхемы энергонезависимой памяти, микроконтроллерную плату оснастки, причем микроконтроллерная плата оснастки состоит из микроконтроллера, предназначенного для отправки команд, соответствующих последовательностям выполнения команд Теста 1, Теста 2, Теста 3, в микросхему энергонезависимой памяти и получения от нее проверяемых значений, схем реле, предназначенных для переключения режима работы при измерении статических параметров микросхемы энергонезависимой памяти, и матрицы транзисторов, обеспечивающей управление реле от микроконтроллера.

3. Устройство по п. 2, в котором центральное вычислительное устройство соединяется с источником питания и мультиметром через интерфейс USB и с микроконтроллером платы оснастки через интерфейс USB-UART.

4. Устройство по п. 3, в котором микросхема энергонезависимой памяти с последовательным доступом подключается к микроконтроллеру через интерфейс I2C.

| ПРИСПОСОБЛЕНИЕ ДЛЯ ИЗМЕРЕНИЯ ПЕРЕДНЕГО УГЛАПЛАШЕК | 0 |

|

SU199432A1 |

| ПЕЧЬ ДЛЯ ВЕДЕНИЯ МЕТАЛЛУРГИЧЕСКИХ, ХИМИЧЕСКИХ И ТЕПЛОВЫХ ПРОЦЕССОВ | 0 |

|

SU199833A1 |

| СПОСОБ ЭЛЕКТРОКОНТАКТНОЙ ОБРАБОТКИ | 0 |

|

SU194203A1 |

| US 9032264 B2, 12.05.2015 | |||

| WO 1987005432 A1, 11.09.1987 | |||

| US 20040153924 A1, 05.08.2004 | |||

| US 6055200 A1, 25.04.2000 | |||

| US 20150279485 A1, 01.10.2015 | |||

| US 20030074611 A1, 17.04.2003 | |||

| US 9831003 B2, 28.11.2017 | |||

| WO 2006081168 A1, 03.08.2006. | |||

Авторы

Даты

2024-06-21—Публикация

2023-09-28—Подача