Изобретения относятся к технике связи и вычислительной технике и могут использоваться в системах передачи информации. Изобретения могут быть использованы при любых видах дельта-модуляции [ДМ].

Известным является вид дельта-модуляции, включающий в себя:

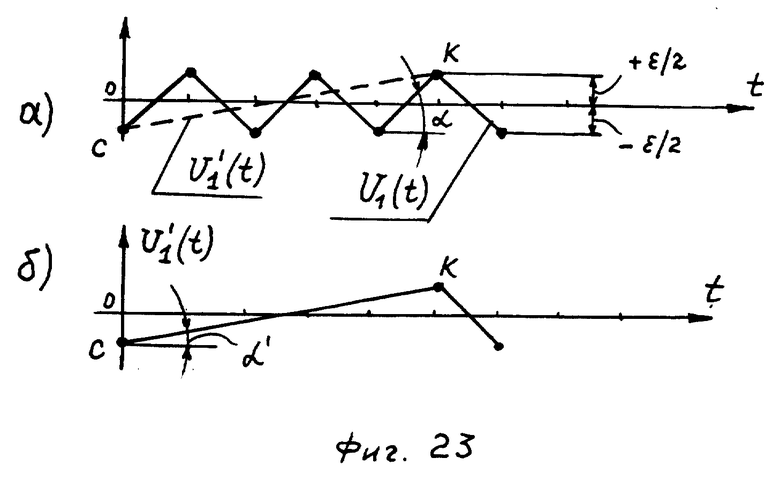

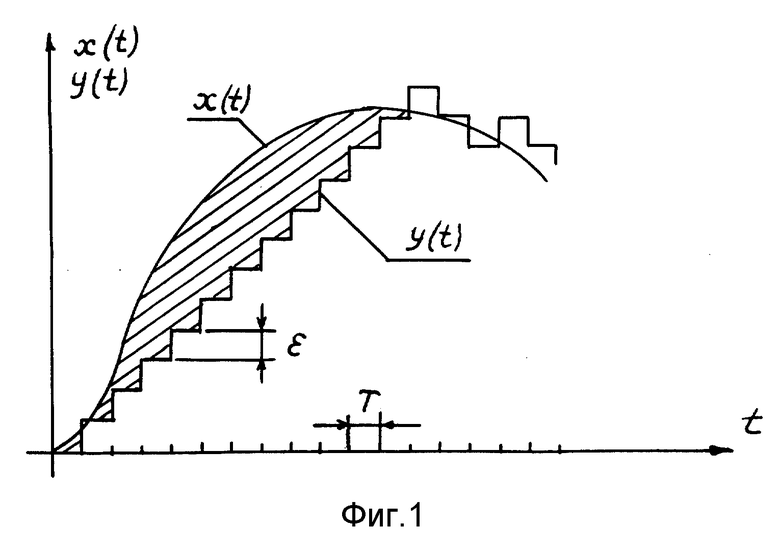

1. На передающей стороне [т.е. в модуляторе] известный способ формирования ступенчатого аппроксимирующего напряжения y(t) в процессе слежения за аналоговым сигналом x(t), при котором в зависимости от знака разности между x(t) и y(t), определяемым в каждом тактовом интервале T, на выходе модулятора получают импульсную последовательность L(t), состоящую из импульсов положительной и отрицательной полярности [фиг. 1].

2. На приемной стороне [т.е. в демодуляторе] известный способ восстановления исходного сигнала из принятой импульсной последовательности L(t) путем формирования из L(t) аппроксимирующего ступенчатого напряжения аналогично тому, которое имеет место в модуляторе с последующей его фильтрацией.

Данный вид дельта-модуляции описан в пат. N 932140 Франция, авт. св. N 106036 "Способ передачи электрических сигналов", Коробков Л.Л., а также в кн. Р. Стил "Принципы дельта-модуляции". Перев. с англ. под ред. В.В. Маркова, - М.: Связь, 1979, с. 17.

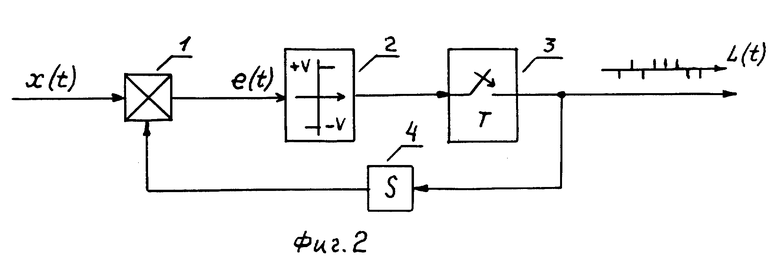

Структурная схема дельта-модулятора, отвечающая данному виду ДМ, приведена на фиг. 2 и содержит последовательно соединенные схему разности 1, компаратор 2, дискретизатор 3, выход которого через интегратор 4 соединен с одним из входов схемы разности 1, второй вход которой является входом дельта-модулятора.

Модулятор [фиг. 2] является известным и не может поэтому являться предметом изобретения. Модулятор работает следующим образом. Входной аналоговый сигнал x(t) поступает на один из входов схемы разности 1, на другой вход которой подается сигнал с выхода модулятора через цепь обратной связи, содержащую интегратор 4, преобразующий выходные импульсы модулятора снова в аналоговый ступенчатый сигнал y1(t). В схеме разности 1 сигнал y1(t) вычитается из сигнала x(t), в результате чего образуется сигнал ошибки e(t). Последний передается одним из двух возможных уровней квантования в зависимости от его полярности с помощью компаратора 2, являющегося квантователем. Выход компаратора 2 опрашивается с периодом T секунд дискретизатором 3, в результате формируется последовательность импульсов L(t), содержащая импульсы либо положительной, либо отрицательной полярности в зависимости от знака сигнала ошибки e(t).

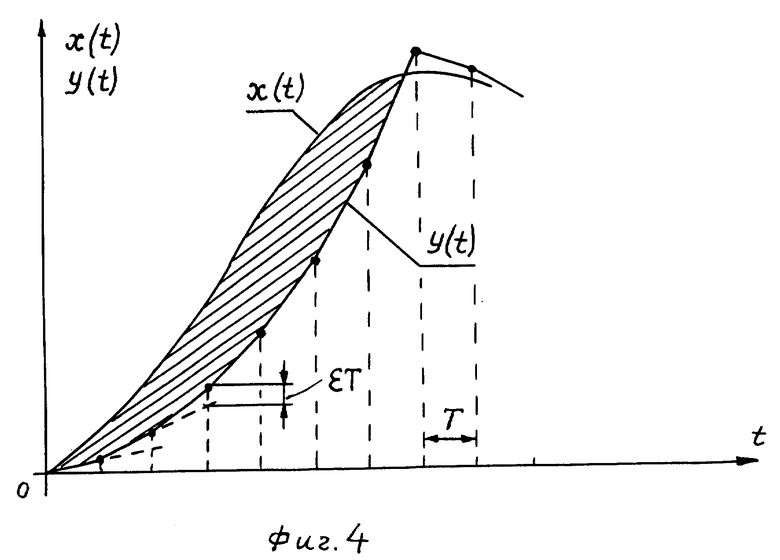

На фиг. 1 через ε обозначено значение одной ступеньки аппроксимирующего напряжения.

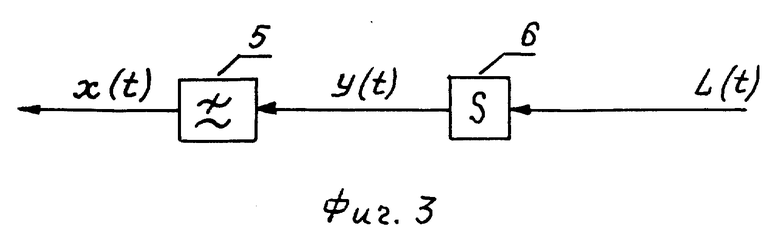

Демодулятор, расположенный на приемной стороне, содержит последовательно соединенные интегратор 6 и фильтр нижних частот 5 [фиг. 3]. В процессе демодуляции восстанавливают исходный сигнал x(t), пропуская приходящие импульсы последовательно через интегратор 6 и сглаживающий фильтр ФНЧ 5.

Известен, например, вид ДМ с двойным интегрированием, сокращенно ДМДИ. Форма аппроксимирующего напряжения y(t), характерная для данного вида ДМ, совместно с кривой исходного сигнала x(t) показана на фиг. 4, где T - период дискретизации, т. е. тактовый интервал [см. упомянутую выше кн. Р. Стил "Принципы дельта-модуляции", стр. 44 - 51].

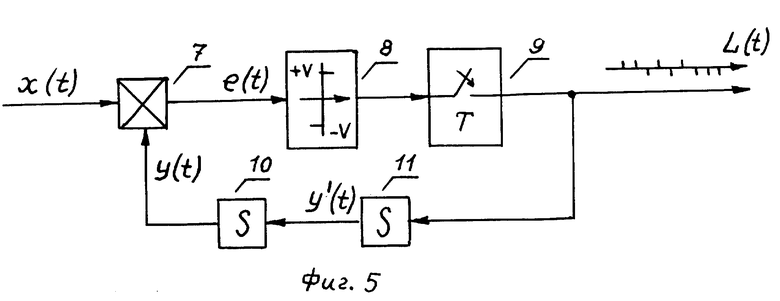

Структурная схема модулятора, отвечающая этому виду ДМ, показана на фиг. 5 и содержит схему разности 7, компаратор 8, дискретизатор 9, два интегратора 10 и 11.

Работа этого дельта-модулятора аналогична работе модулятора системы линейной ДМ, рассмотренной выше [фиг. 2]. Отличие заключается лишь в том, что здесь в цепи обратной связи расположен не один, а два интегратора.

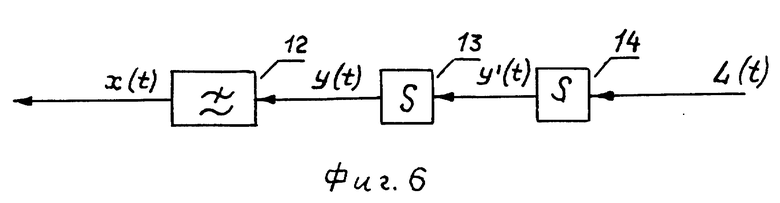

При этом на выходе первого интегратора цепи обратной связи [интегратор 11] образуется аппроксимирующее напряжение ступенчатой формы y'(t), т.е. изменяющееся в каждом тактовом интервале на ±ε. После второго интегратора 10 получают окончательное аппроксимирующее напряжение y(t) уже с переменной крутизной линейных участков, которая изменяется за тактовый интервал на значение, равное εT. Известный способ восстановления исходного сигнала при этом виде ДМ в целом аналогичен рассмотренному ранее виду ДМ и осуществляется с помощью демодулятора, структурная схема которого приведена на фиг. 6. При этом в отличие от схемы [фиг. 3] данный демодулятор содержит также не один, а два интегратора 13 и 14 и ФНЧ 12.

Всем известным способам восстановления исходного сигнала при различных видах ДМ, формирующим только одно аппроксимирующее напряжение, свойственны следующие недостатки:

1. Значительное отклонение формы исходного сигнала при его восстановлении на приемной стороне от первоначального вида в случае больших изменений крутизны исходного сигнала, т.е. появление существенных искажений "перегрузки по крутизне", которые можно оценить по величине площади между кривыми исходного сигнала x(t) и аппроксимирующего напряжения y(t) [заштрихованные области на фиг. 1 и 4].

2. Невозможность одновременного уменьшения как шума квантования, так и искажений "перегрузки по крутизне" при неизменной тактовой частоте.

Указанные недостатки известных способов восстановления исходного сигнала, использующих лишь одно аппроксимирующее напряжение, отрицательно сказываются на качестве работы устройств с применением дельта-модуляции [ДМ].

Известен также способ восстановления исходного сигнала при ДМ, использующий двойную аппроксимацию [прототип], сокращенно ДМДА, описанный в пат. РФ N 1571766 "Способ восстановления исходного сигнала при дельта-модуляции и устройство для дельта-демодуляции", авторы: Андреев В.А., Луценко А.П., Блинов Р. А., зарегистрированном в IP изобретений 11.08.93, преобразованном из авт. свидетельства, опубл. в БИ N 22, 15.06.90.

Способ восстановления исходного сигнала ДМДА взят за прототип как имеющий наибольшее число сходных признаков с заявляемым способом и заключается в следующем.

Способ восстановления исходного сигнала при дельта-модуляции, включающий в себя обнаружение пачки однополярных импульсов в импульсной последовательности входного дельта-модулированного сигнала с одновременной задержкой этой импульсной последовательности, формирование из нее первого аналогового сигнала, возрастание или убывание которого на время T действия каждого импульса входного дельта-модулированного сигнала соответствует заранее заданной полярности этого импульса, формирование выходного сигнала путем фильтрации аналогового сигнала, отличающийся тем, что, с целью повышения точности восстановления исходного сигнала, импульсную последовательность задерживают на время T•N [N - максимально возможное число импульсов в пачке], одновременно с первым формируют второй аналоговый сигнал, направление изменения которого аналогично направлению изменения первого аналогового сигнала, после обнаружения пачки однополярных импульсов увеличивают крутизну первого аналогового сигнала с каждым следующим импульсом этой пачки, начиная с минимальной крутизны в момент появления каждой пачки однополярных импульсов, и уменьшают крутизну второго аналогового сигнала с каждым следующим импульсом той же пачки в порядке, обратном порядку увеличения крутизны первого аналогового сигнала, до минимальной крутизны в момент окончания пачки импульсов, суммируют сформированные таким образом первый и второй аналоговые сигналы, после чего фильтруют суммарный аналоговый сигнал.

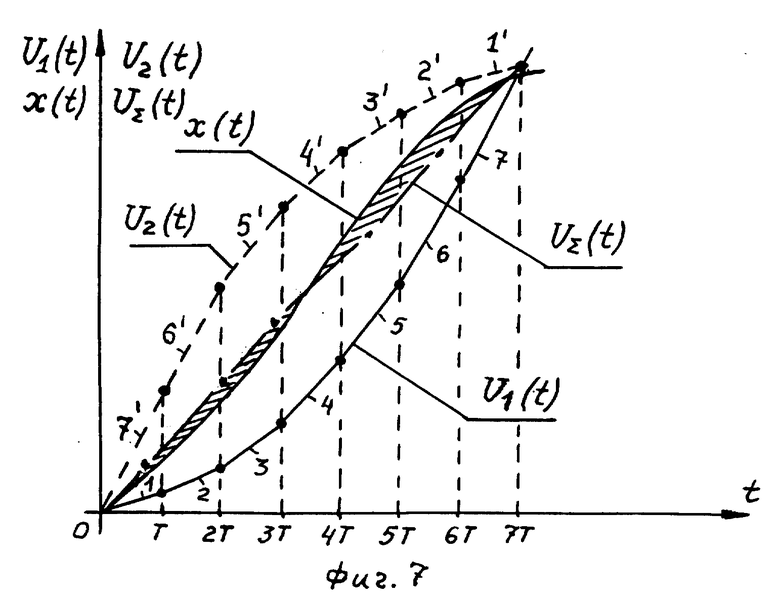

Сущность способа ДМДА на примере сравнения его с ДМ с двойным интегрированием [ДМДИ] показана на фиг. 7.

При этом для удобства сравнения способов ДМДИ и ДМДА кривые исходного сигнала x(t) и I-го аппроксимирующего напряжения U1(t) взяты аналогичными кривым x(t) и y(t), приведенных на фиг. 4. Участки кривой напряжения U1(t) на фиг. 7 для определенности пронумерованы согласно тактовым интервалам [предполагается, что пересечение кривых x(t) и U1(t) произошло, например, на 7-ом тактовом интервале].

Предположим теперь, что удалось сформировать еще одно [второе] аппроксимирующее напряжение [кривая U2(t) на фиг. 7], которое является обратно отображенным первому. Термин "обратно отображенное" напряжение понимается в том смысле, что у второго аппроксимирующего напряжения U2(t) наклон участков аппроксимации идет в противоположной последовательности по сравнению с наклоном участков кривой I-го напряжения U1(t), т.е. сначала для U2(t) формируется первый участок 7' с наклоном, соответствующим последнему участку I-го напряжения U1(t) [участок 7] , затем формируется второй участок 6', соответствующий предпоследнему участку [участок 6] I-го напряжения U1(t) и т.д.

Если теперь произвести сложение обоих напряжений U1(t) и U2(t) и взять полусумму от получаемого результата, то суммарное напряжение UΣ(t) [с коэффициентом суммирования 0,5] после фильтрации и будет представлять собой восстановленный исходный сигнал x(t), значительно лучше отображающий оригинал, чем только одно аппроксимирующее напряжение U1(t).

Действительно, величина площади между кривыми исходного сигнала x(t) и результирующего напряжения UΣ(t) получается значительно меньше, чем между кривыми x(t) и U1(t) и это проявляется тем сильнее, чем больше крутизна исходного сигнала x(t), что видно из сравнения графиков, представленных на фиг. 4 и фиг. 7.

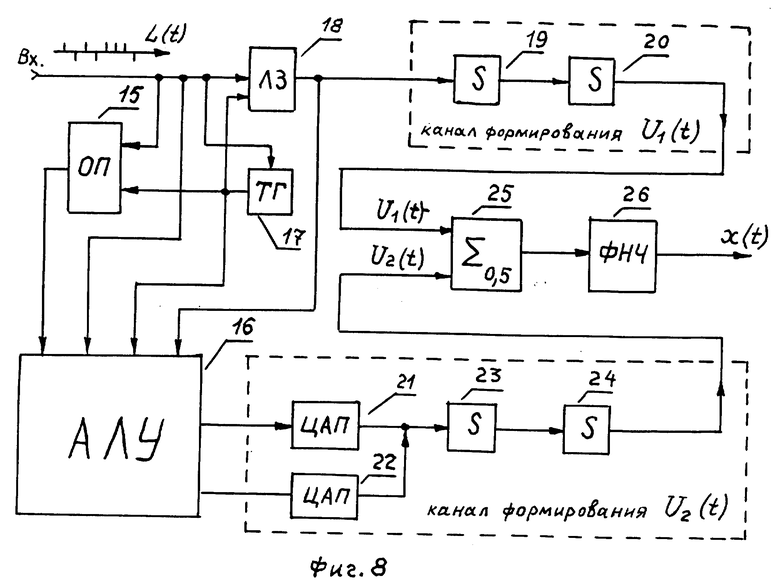

Структурная схема устройства ДМДА приведена на фиг. 8 и содержит определитель полярности ОП 15 [схема совпадения], один из входов которого соединен с входом устройства. Выход тактового генератора ТГ 17 соединен с вторым входом ОП 15. Выход ОП 15 соединен с первым входом арифметико-логического устройства АЛУ 16.

Второй вход АЛУ 16 соединен с входом устройства.

Третий вход АЛУ 16 соединен с выходом ТГ 17 и одним из входов линии задержки ЛЗ 18, другой вход которой подключен к входу устройства.

Четвертый вход АЛУ 16 соединен с выходом ЛЗ 18.

Вход ТГ 17 соединен с входом устройства, что обеспечивает синхронизацию работы тактового генератора ТГ 17 в соответствии с периодом следования приходящих импульсов последовательности L(t).

К выходу ЛЗ 18 подсоединены последовательно включенные интеграторы 19 и 20, образующие канал формирования первого аппроксимирующего напряжения U1(t).

Выходы АЛУ 16 соединены с входами двух цифроаналоговых преобразователей ЦАП 21 и ЦАП 22, которые идентичны и отличаются только знаком опорного напряжения, подаваемого на ЦАП.

Один из ЦАП включается в работу, когда в последовательности L(t) присутствуют импульсы положительной полярности, другой ЦАП включается в работу при наличии отрицательных импульсов в последовательности L(t). Управляет работой обоих ЦАП АЛУ 16.

Выходы ЦАП 21 и ЦАП 22 объединены и к ним подключены последовательно соединенные интеграторы 23 и 24, которые совместно с ЦАП образуют канал формирования 2-го аппроксимирующего напряжения U2(t).

Напряжения U1(t) и U2(t) подаются на первый и второй входы полусумматора 25, выход которого соединен с входом ФНЧ 26.

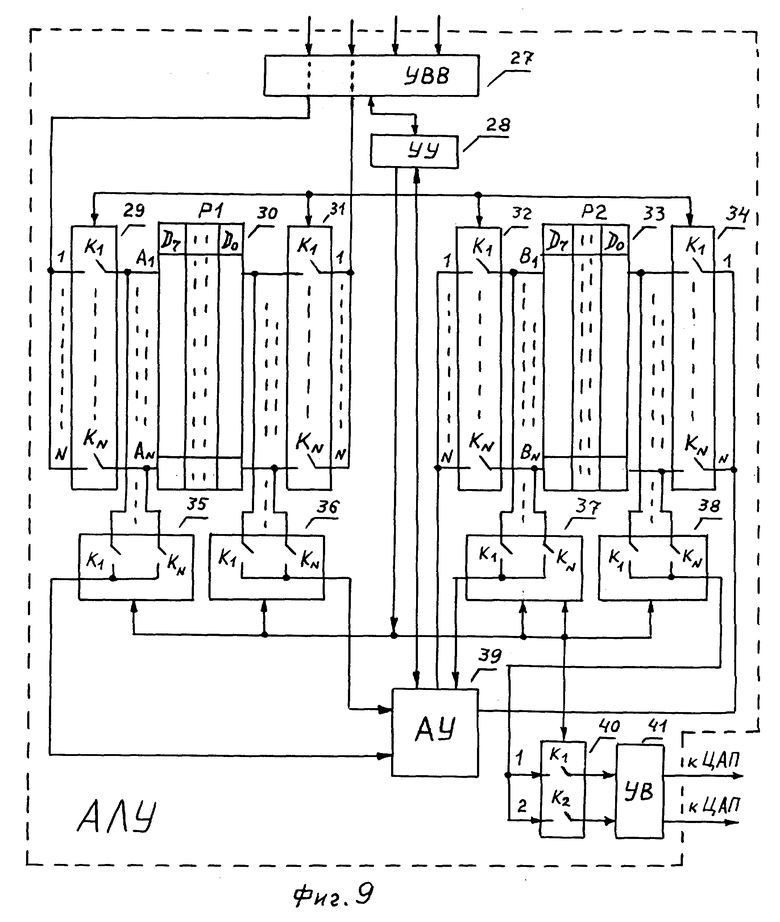

Функциональная схема АЛУ, использованного в устройстве по пат. N 1571766, приведена на фиг. 9 и содержит устройство ввода УВВ 27, предназначенное для установления режима работы, пуска и остановки действия программы, и имеет четыре входа, связанные соответственно с выходом и входом ЛЗ 18, с выходом ОП 15 и выходом ТГ 17.

АЛУ включает в себя устройство управления УУ 28, которое обеспечивает совместную работу блоков АЛУ. Оно управляет также работой всех блоков электронных ключей 3, 5, 6, 8, 9, 10, 11, 12, 14.

УУ 28 позволяет считывать и выполнять все необходимые команды и соединено с УВВ 27 и арифметическим устройством АУ 39.

Устройство вывода УВ 41 предназначено для вывода информации с ячеек памяти регистра сравнения 33 [обозначенного также через P2] на ЦАП 21 или на ЦАП 22 [фиг. 8].

В качестве АЛУ может быть использован готовый микропроцессор, например КР 580ИК80А или любой другой, в том числе выполненный на дискретных логических элементах.

Работа известного устройства [фиг. 8].

Приходящие на демодулятор импульсы последовательности L(t) поступают также и на 1-й вход определителя полярности ОП 15, а на 2-й вход ОП 15 поступают положительные импульсы с выхода тактового генератора ТГ 17.

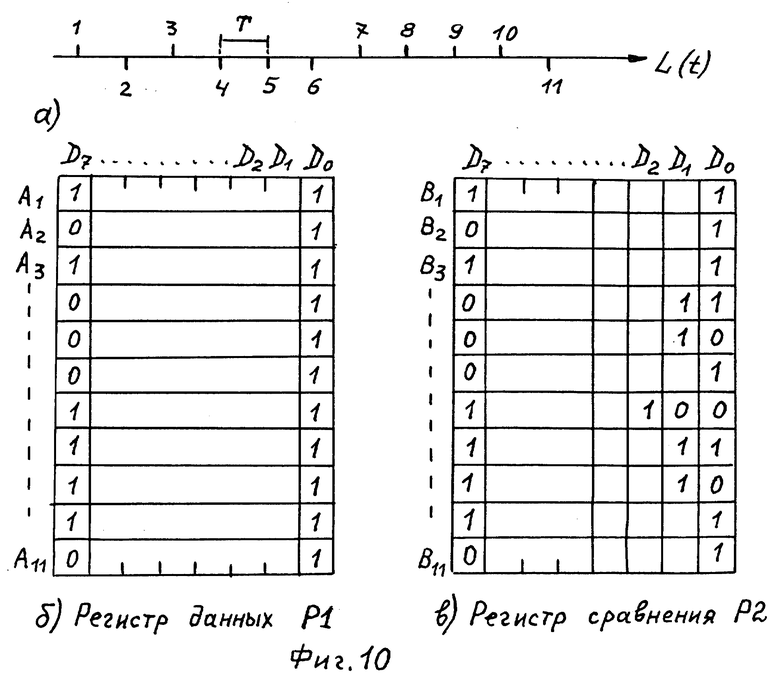

В случае наличия импульса положительной полярности в последовательности L(t) на выходе ОП 15 появляется выходной импульс, а при наличии в L(t) отрицательных импульсов на выходе ОП 15 сигнала не будет. В результате этого на 1-м этапе работы АЛУ в старшем бите D7 ячеек памяти A регистра данных P1 [фиг. 10б] будут записываться логические единицы "1" тогда, когда в L(t) имеются импульсы положительной полярности и останутся "0" в случае прихода отрицательных импульсов [в качестве приема рассматривается последовательность, приведенная на фиг. 10a].

Таким образом бит D7 регистра P1 является знаковым битом.

В младшем бите D0 ячеек памяти регистра P1 с помощью работы блока 31 электронных ключей будут записываться "1" при поступлении очередных импульсов в последовательности L(t) вне зависимости от их полярности, для чего используется 2-й вход АЛУ, следовательно, бит D0 регистра P1 является битом, фиксирующим приход очередного импульса.

Запись информации в регистр данных 30 [обозначенного также через P1] осуществляется с помощью замыкания и размыкания ключей [K1...KN] блоков 29 и 31 электронных ключей [фиг. 9].

С арифметическим устройством АУ 39 регистр P1 связан с помощью блоков 35 и 36 электронных ключей.

Второй этап работы АЛУ.

Он заключается в обработке содержимого, записанного в регистр данных P1, с целью выделения групп однополярных импульсов как положительных, так и отрицательных, что необходимо в последующем для формирования 2-го аппроксимирующего напряжения U2(t), для чего устройство управления УУ 28 [фиг. 9] реализует следующую программу.

Во-первых, сначала в первую ячейку памяти B1 регистра сравнения 33 [обозначенного также через P2] переписывают содержимое 1-й ячейки памяти A1 регистра данных 30.

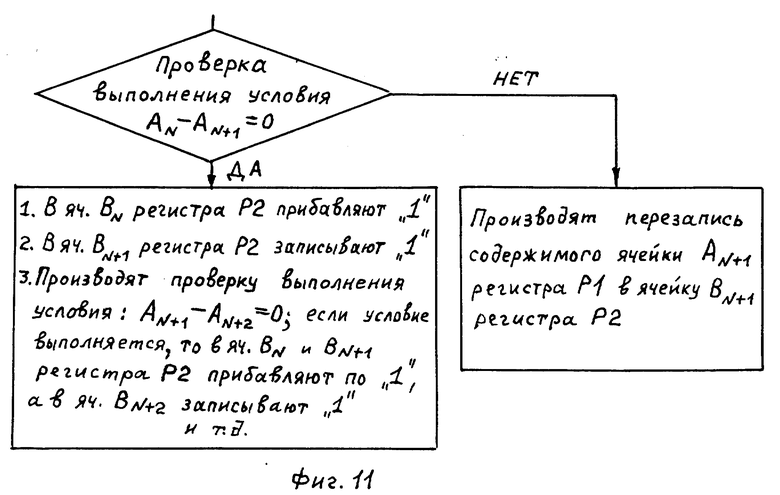

Во-вторых, в арифметическом устройстве АУ 39 осуществляют сравнение содержимого знакового бита D7 Регистра P1 для двух соседних ячеек AN и AN+1 по программе, алгоритм которой приведен на фиг. 11.

Запись информации в регистр сравнения P2 осуществляется с помощью блоков 32 и 34 электронных ключей, а считывание информации с ячеек регистра P2 происходит с помощью блоков 37, 38, 40 электронных ключей.

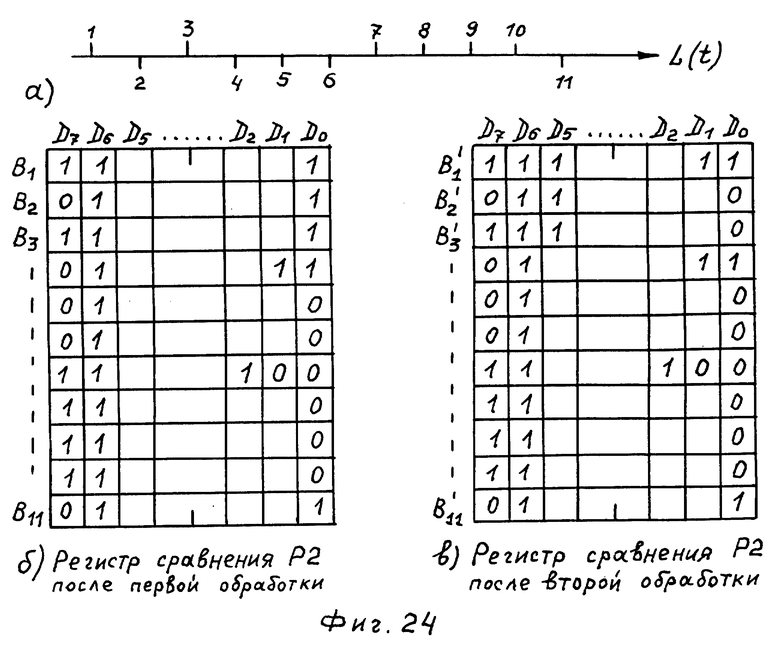

Результаты обработки произвольно взятой в качестве примера импульсной последовательности L(t) [фиг. 10a] по алгоритму [фиг. 11] приведены на фиг. 10b.

При этом содержание знакового бита D7 регистра сравнения P2 [фиг. 10b] соответствует содержимому знакового бита D7 регистра P1.

Опрашивание ячеек памяти регистра сравнения P2 начинается с момента появления 1-го импульса на выходе линии задержки ЛЗ 18. Переход к опрашиванию очередной ячейки определяется периодом следования импульсов тактового генератора ТГ 17, синхронизированных с частотой следования импульсов последовательности L(t). Режим молчания определяется нулевым состоянием ячеек памяти P2.

Несмотря на указанные преимущества способа ДМ с двойной аппроксимацией [ДМДА] перед способами ДМ, реализующими только одно аппроксимирующее напряжение, способ ДМДА также имеет недостатки, основные из которых следующие:

1. При уменьшении искажений "перегрузки по крутизне" уровень шумов квантования не уменьшается.

2. Наличие помимо канала формирования 1-го аппроксимирующего напряжения еще и канала формирования 2-го аппроксимирующего напряжения усложняет аппаратуру демодулятора.

Отмеченные выше недостатки известных способов ДМ, использующих как одно, так и два аппроксимирующих напряжения, отрицательно сказываются на качестве работы устройств с применением ДМ.

Задачей настоящего изобретения является повышение точности восстановления исходного сигнала при формировании только одного аппроксимирующего напряжения для любого вида дельта-модуляции [путем уменьшения как искажений "перегрузки на крутизне", так и шумов квантования].

Решение задачи изобретения достигается за счет того, что в способе восстановления исходного сигнала при дельат-модуляции, включающем в себя запись и запоминание принимаемой импульсной последовательности входного дельта-модулированного сигнала, обнаружение в записанной последовательности пачек однополярных импульсов, формирование из этой импульсной последовательности аналогового сигнала, возрастание или убывание которого на время действия каждого импульса входного дельта-модулированного сигнала в течение тактового интервала Т соответствует заранее заданной полярности этого импульса, формирование выходного сигнала путем фильтрации аналогового сигнала, дополнительно производят обнаружение и обработку пачек разнополярных импульсов, при этом проверяют количество импульсов в отдельно взятой пачке разнополярных импульсов на нечетность [четность], причем в случае нечетного числа N импульсов в пачке осуществляют обработку всего этого числа импульсов, а в случае четного числа N' импульсов в пачке осуществляют обработку лишь N'-1 числа импульсов, в результате которой вырабатывают цифровой сигнал, соответствующий используемому виду дельта-модуляции, после чего преобразуют полученный цифровой сигнал в аналоговый сигнал с неравномерным шагом дискретизации во времени, из которого формируют выходной сигнал.

Решение данной задачи достигается за счет того, что в устройство для дельта-демодуляции, содержащее определитель полярности приходящих импульсов, информационный вход которого является входом устройства, арифметико-логический узел, тактовый генератор, цифроаналоговый преобразователь, интегратор и фильтр нижних частот, выход которого является выходом устройства, введен блок переработки и перекодирования информации [БППИ], вход которого подключен к выходу арифметико-логического узла, а выход БППИ подключен к входу знакопеременного цифроаналогового преобразователя, к выходу которого последовательно подсоединены интегратор и фильтр нижних частот.

Устройство, реализующее предложенный способ восстановления исходного сигнала при ДМ, может быть выполнено в 2-х вариантах построения его схемы.

1. С последовательной связью между арифметико-логическим узлом [АЛУ] и блоком переработки и перекодирования информации [БППИ], выполненном раздельно от АЛУ.

2. С параллельной связью между блоком АЛУ и блоком ПЗУ, т.е. когда АЛУ входит составной частью в блок БППИ, который в этом случае представляет собой, например, микроконтроллер, с взаимным обменом информацией между блоками АЛУ и ПЗУ.

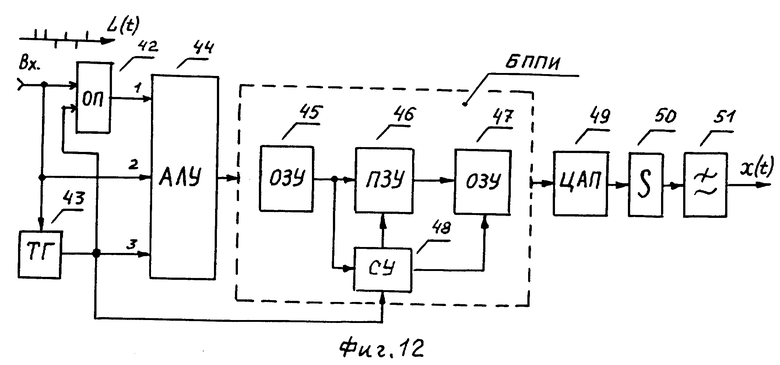

Структурная схема устройства с последовательной связью между арифметико-логическим узлом [АЛУ] и блоком переработки и перекодирования информации [БППИ] приведена на фиг. 12 и содержит определитель полярности ОП 42, первый вход которого соединен с входом устройства, а второй вход ОП 42 соединен с выходом тактового генератора ТГ 43, подключенному к входу устройства.

Выход определителя полярности ОП 42 соединен с 1-м входом арифметико-логического устройства [узла] АЛУ 44, второй вход которого соединен с входом устройства, а третий вход АЛУ соединен с выходом тактового генератора ТГ 43.

Выход АЛУ 44 подключен к входу блока переработки и перекодирования информации БППИ, предназначенном в простейшем случае, когда устройство [т.е. демодулятор] работает с одним каким-либо видом ДМ, для хранения двоичного числа [кода] , переписанного с регистра сравнения АЛУ 44, с последующей передачей этого кода на вход ЦАП 49, а в более сложных случаях, когда демодулятор работает при различных видах тактируемой дельта-модуляции не только для хранения двоичного числа, переписанного с АЛУ 44, но и его перекодирования под тот или иной вид ДМ, для чего используются соответствующие шины данных ПЗУ 46. Входом блока БППИ является вход ОЗУ 45, выход которого подключен к входу постоянного запоминающего устройства ПЗУ 46, а также к одному из входов схемы управления СУ 48, второй вход которой подключен к выходу тактового генератора ТГ 43.

Выход ПЗУ 46 соединен с одним из входов второго ОЗУ 47. Выходы схемы управления СУ 48 подключены к вторым входам ПЗУ 46 и ОЗУ 47. Выход 2-го ОЗУ 47, являющийся выходом блока БППИ, подключен к входу знакопеременного цифроаналогового преобразователя ЦАП 49, с опорным напряжением, получаемым в биполярном коде.

Выход ЦАП 49 соединен с входом интегратора 50, а его выход подсоединен к входу фильтра нижних частот ФНЧ 51, выход которого является выходом устройства.

Вообще говоря, устройство [фиг. 12] могло бы функционировать и без первого ОЗУ 46, используемого в качестве регистра-защелки, а лишь при наличии ПЗУ 46 и ОЗУ 47, однако в этом случае возможны сбои в работе для блока БППИ.

Первое и второе ОЗУ являются статическими, т.е. способными хранить информацию продолжительное время, и могут быть выполнены на триггерах или же с использованием готовых микросхем, например, типа 155ТМ7 или 155ТМ8

В качестве ПЗУ 46 могут быть использованы готовые микросхемы 573-й серии, например, типа 573РФ5, 573РФ6 или же другие микросхемы, аналогичные этим.

Схема управления СУ 48 предназначена для выработки синхроимпульсов, обеспечивающих синхронизацию совместной работы ОЗУ и ПЗУ. Она весьма проста и в качестве ее могут быть использованы готовые микросхемы 155-й или 555-й серий.

В качестве знакопеременного ЦАП 49 может быть использован, например, ЦАП 572ПА1А или ЦАП 1107ПА1А.

Фильтр нижних частот ФНЧ 51 может быть реализован на операционном усилителе ОУ типа, например, К574УД1Б, а интегратор может быть выполнен на ОУ типа К140УДБ или К140УД7.

Как видим, реализация устройства [фиг. 12] не представляет трудностей.

Устройство [фиг. 12] работает следующим образом.

Перед началом работы во всех ячейках памяти регистра данных и регистра сравнения арифметико-логического устройства [узла] АЛУ 44, которое выполнено аналогично известному АЛУ [фиг. 9], устанавливают нули "0", а ключи всех блоков электронных ключей устанавливают в разомкнутое состояние.

1-ый этап работы АЛУ.

Работа АЛУ и всего устройства в целом начинается с приходом первого импульса последовательности L(t) на вход устройства.

Приходящие импульсы поступают на вход тактового генератора ТГ 43, на один из входов АЛУ 44, а также на один из входов определителя полярности ОП 42, на другой вход которого подаются положительные импульсы с выхода тактового генератора ТГ 43, как показано на фиг. 12.

Таким образом выходной импульс у ОП 42 появляется и поступает в АЛУ 44 лишь при наличии в ДМ-сигнале положительных импульсов, а при наличии отрицательных импульсов в ДМ-сигнале на выходе ОП 42 будет "0".

Блоки электронных ключей, входящие в состав АЛУ 44, построены и работают аналогично блокам электронных ключей известного устройства [фиг. 9].

В результате в старшем бите D7 ячеек памяти AN регистра данных Р1, как и в известном устройстве, будут записываться "1" тогда, когда в приходящей последовательности L(t) имеют место положительные импульсы и останутся нули "0" при наличии в последовательности L(t) отрицательных импульсов.

Таким образом бит D7 является знаковым битом, как это показано на фиг. 14б, для случая импульсной последовательности вида [фиг. 14а], взятой в качестве примера.

В младшем бите D0 ячеек памяти регистра данных Р1 [фиг. 14б], как и в случае работы известного устройства [фиг. 9] будут записываться логические единицы "1" при поступлении каждого очередного импульса вне зависимости от его полярности, для чего предусмотрен вход 2 АЛУ 44 [фиг. 12].

При этом для реализации предлагаемого способа восстановления исходного сигнала при ДМ в устройстве [фиг. 12] в отличие от устройства [фиг. 9] в регистре данных к знаковому биту D7 добавлен еще один бит - D6, в котором фиксируются приходящие импульсы вне зависимости от их полярности, т.е. аналогично биту D0.

Необходимость использования для регистрации знака импульса не одного, а двух битов D7 и D6 объясняется тем, что при обработке как пачек однополярных импульсов, так и пачек разнополярных импульсов, при наличии лишь одного знакового бита D7 было бы невозможно по знаковому биту отличить режим свободной ячейки, т. е. отсутствие импульсов в последовательности L(t) от наличия в ней отрицательных импульсов, что будет видно из дальнейшего рассмотрения. Что касается регистра сравнения Р2, то в него на 1-м этапе работы АЛУ записывается точно такая же информация, что и в регистр данных Р1 [фиг. 14б], что упрощает алгоритм последующей обработки.

Таким образом на 1-м этапе работы АЛУ 44 [фиг. 12] в памяти устройства, а именно в регистре данных Р1 и в регистре сравнения Р2, будет зафиксирована полная информация с приходящей на демодулятор последовательности L(t).

Что касается фиг. 14в, то характер заполнения содержимого ячеек памяти регистра сравнения Р2 соответствует времени, относящемуся к 2-му этапу работы АЛУ 44, когда содержимое ячеек памяти регистра Р1 было уже обработано, а результаты этой обработки и зафиксированы на фиг. 14в.

Об алгоритме обработки сказано далее.

Синхронизация работы блоков АЛУ осуществляется с помощью ТГ 43.

2-й этап работы АЛУ.

Этот этап заключается в обработке содержимого регистра данных Р1 [фиг. 14б] с занесением результатов обработки в регистр сравнения Р2, с целью выделения из последовательности L(t) групп [пачек] однополярных импульсов как положительных, так и отрицательных.

Алгоритм этой обработки состоит в следующем.

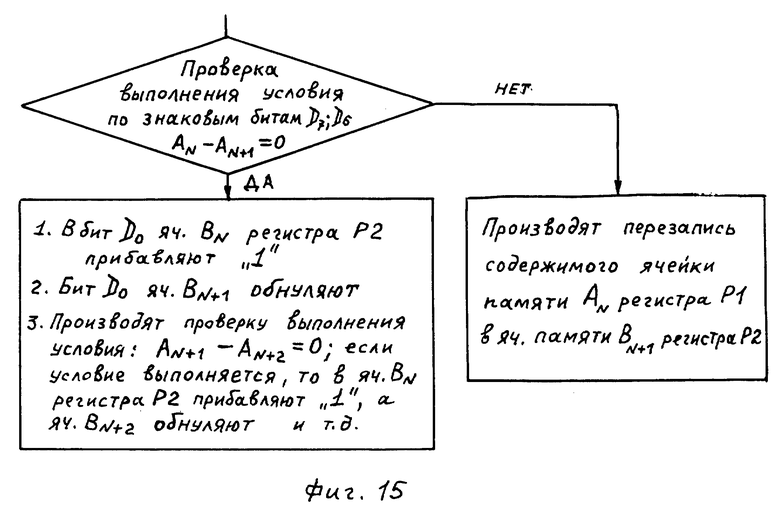

1. Осуществляют сравнение содержимого знаковых битов D7; D6 регистра данных Р1 [фиг. 14б] для двух соседних ячеек AN и AN+1, путем проверки выполнения условия; AN - AN+1 = 0 и далее по программе, алгоритм которой приведен на фиг. 15 и включает в себя следующие операции.

Если условие AN - AN+1 = 0 выполняется, то:

1. В бит D0 яч. BN регистра сравнения Р2 прибавляют "1".

2. Бит D0 яч. BN+1 обнуляют.

3. Производят проверку выполнения условия AN+1 - AN+2 = 0, если условие выполняется, то в яч. BN регистра Р2 прибавляют еще одну лог. "1", а яч. BN+2 обнуляют и т.д.

Таким образом с каждым очередным импульсом в пачке однополярных импульсов содержимое начальной ячейки, соответствующей 1-му импульсу этой пачки, увеличивается на одну лог. "1", а остальные ячейки регистра Р2, соответствующие последующим импульсам в пачке, обнуляются. Полярность импульсов определяют биты D7 и D6.

4. При невыполнении условия AN - AN+1 = 0 [т.е. пачка однополярных импульсов заканчивается] и производят перезапись содержимого яч. AN регистра данных Р1 в яч. BN+1 регистра сравнения Р2.

Результат обработки содержимого регистра данных Р1 [фиг. 14б] для случая рассматриваемой последовательности из 11 импульсов [фиг. 14а] по указанному выше алгоритму приведен на фиг. 14в.

Отличием алгоритма, представленного на фиг. 15, от алгоритма обработки регистра данных Р1, описанного в упомянутом выше пат. РФ N 1571766, является то, что теперь в ячейках регистра сравнения Р2, соответствующих пачкам однополярных импульсов, появляются нули [чего ранее не было] во всех ячейках, относящимся к пачкам однополярных импульсов, кроме тех ячеек, в которых фиксируется [т. е. записывается] общее число однополярных импульсов в данной пачке.

Указанное обстоятельство позволяет в дальнейшем при считывании содержимого ячеек регистра сравнения Р2 реализовать режим переменной дискретизации во времени в процессе формирования аппроксимирующего напряжения [чего ранее в известных способах было невозможно], о чем далее будет сказано подробнее, при рассмотрении алгоритма [фиг. 16].

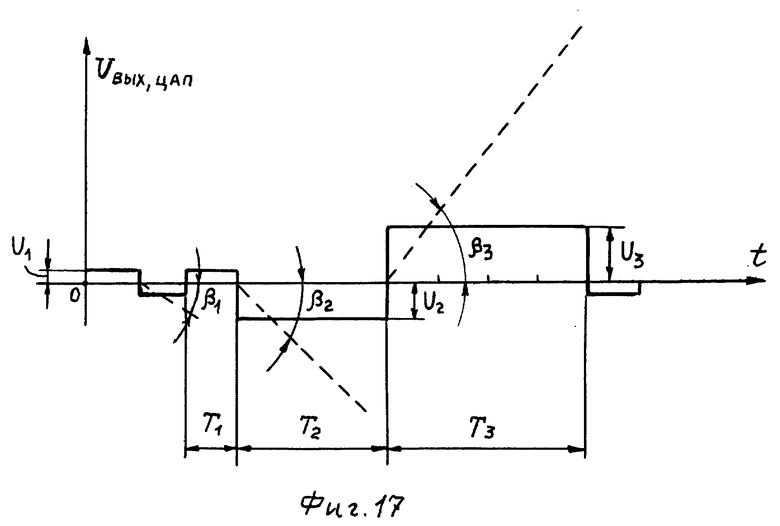

Сейчас же отметим лишь то, что при считывании двоичного кода с ячеек регистра сравнения Р2 [фиг. 14в] для хранения его в блоке БППИ [фиг. 12] и последующей подачей этого кода на вход знакопеременного ЦАП 49, выходное напряжение ЦАП 49 будет иметь вид ступенек с амплитудами U1; U2; U3 и с длительностями соответственно T1, T2, T3, как это показано на фиг. 17.

При этом штриховые линии, идущие под углами β1; β2; β3, характеризуют скорость нарастания выходного напряжения интегратора 50, на вход которого это ступенчатое напряжение [U1; U2; U3] подают.

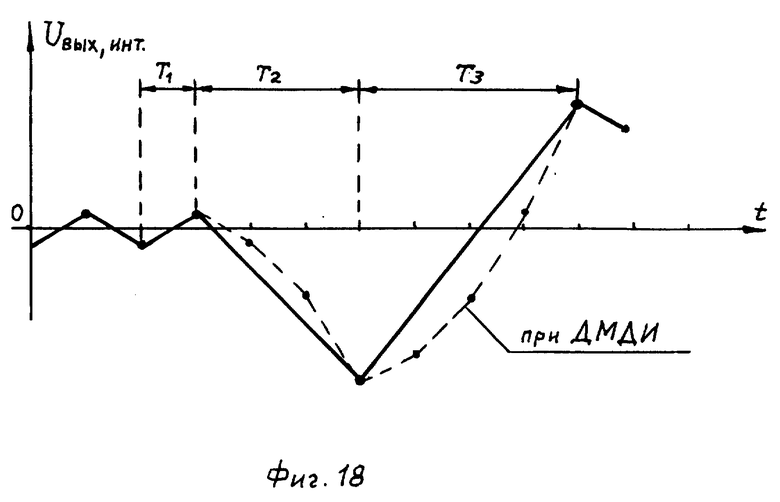

Вид выходного напряжения интегратора 50, соответствующего выходному напряжению ЦАП 49 [фиг. 17], показан на фиг. 18.

Период опрашивания очередной ячейки памяти определяется периодом следования импульсов тактового генератора ТГ 43 [фиг. 12], работа которого синхронизирована в соответствии с частотой следования импульсов входного тактируемого ДМ-сигнала, поступающего на вход устройства.

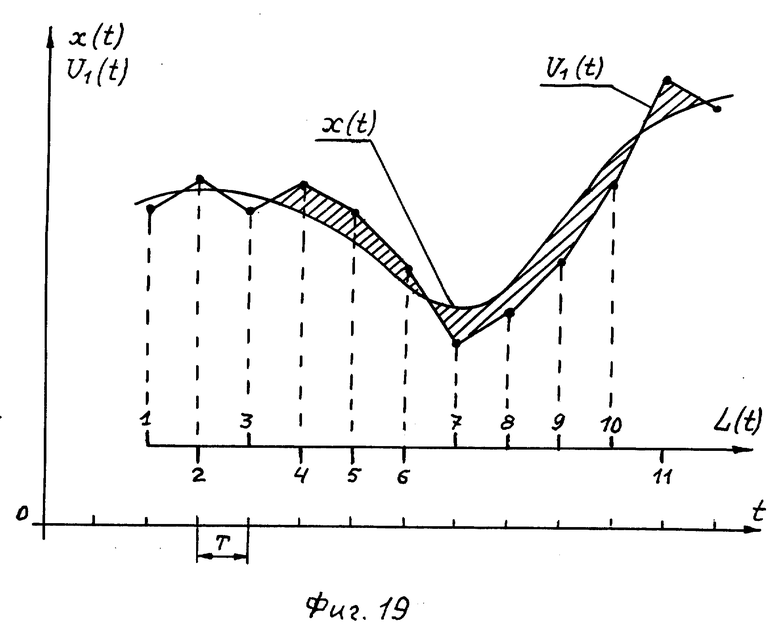

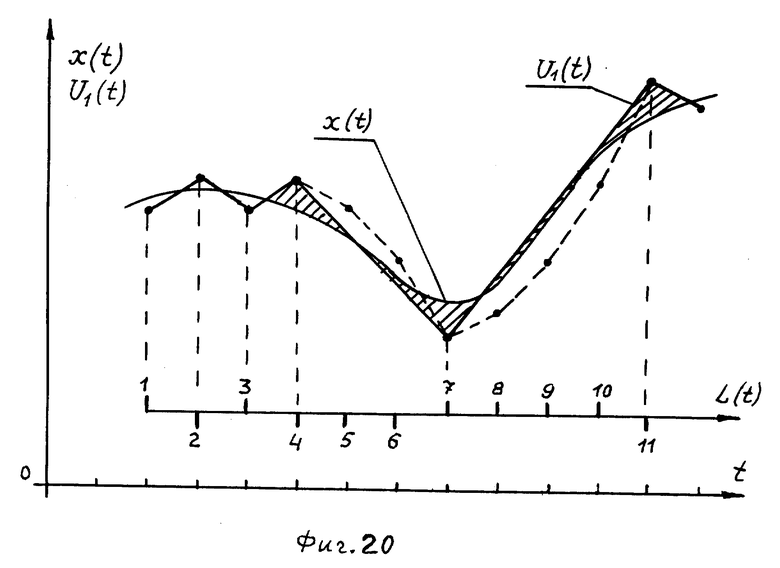

Причем, если бы даже ограничиться лишь использованием только алгоритма обработки последовательности L(t), приведенном на фиг. 15, то и в этом случае уже имелись бы существенные преимущества перед известными способами восстановления исходного сигнала при дельта-модуляции в случаях использования лишь одного аппроксимирующего напряжения, что хорошо видно на сравнении графиков фиг. 20 [где этот способ реализован] в сравнении с известным способом при ДМ с двойным интегрированием [ДМДИ], для случая той же последовательности импульсов входного ДМ-сигнала [фиг. 19].

Искажения типа "перегрузки по крутизне" на графике [фиг. 20] получаются заметно меньше, нежели на графике [фиг. 19], что видно из сравнения заштрихованных участков площадей, находящимися между кривыми исходного сигнала x(t) и аппроксимирующего напряжения U1(t).

Границы интервалов T1, T2, T3 для нового способа и являются теми точками дискретизации, в которых формируется апрроксимирующее напряжение U1(t).

В то же время предлагаемый в заявке способ восстановления исходного сигнала при ДМ позволяет не только уменьшить искажения "перегрузки по крутизне" при формировании лишь одного аппроксимирующего напряжения, что выше было показано, но позволяет также уменьшить еще и шумы квантования в результате дополнительной обработки содержимого регистра сравнения, проводимой после первой его обработки [методом, отмеченным выше], теперь уже с целью выделения и обработки разнополярных импульсов, имеющихся в последовательности L(t) по алгоритму, приведенному на фиг. 16.

Для того, чтобы понять почему использован именно такой, а не иной алгоритм обработки пачек разнополярных импульсов, надо принять во внимание то обстоятельство, что при одинаковом алгоритме обработки как четного, так и нечетного количества разнополярных импульсов, уменьшение уровня шумов квантования получается не одинаковым [в одном случае лучше, в другом хуже].

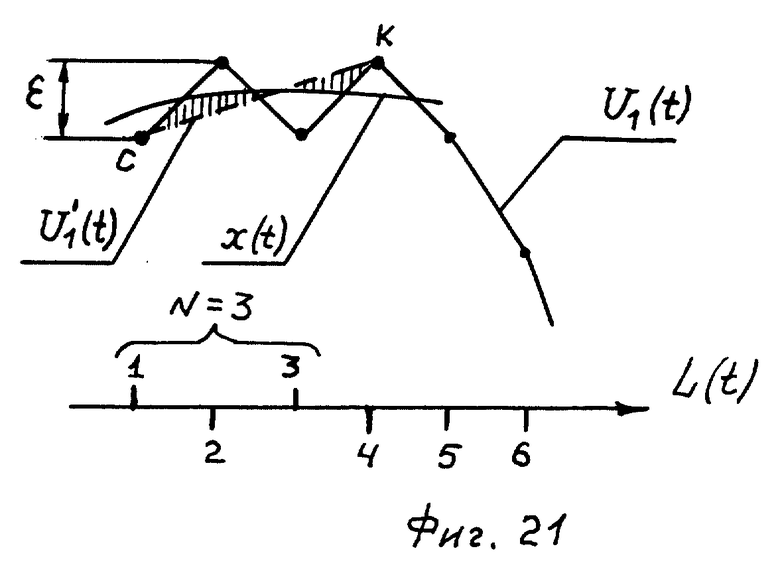

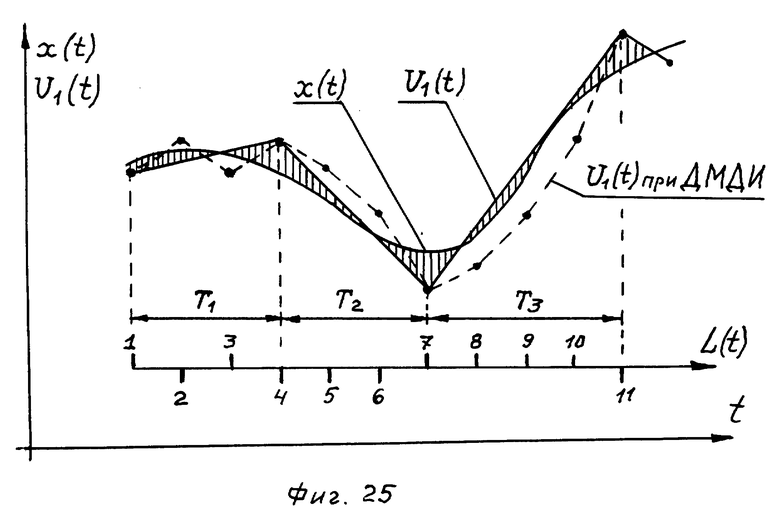

Это можно проиллюстрировать графически, как показано на фиг. 21...23. Так, в случае нечетного количества разнополярных импульсов в пачке, как это имеет место, например, в рассматриваемой последовательности L(t) вида [фиг. 14а] , где их число равно трем [N=3], трудностей при обработке в АЛУ не возникает, а сами шумы квантования заметно уменьшаются [фиг. 21].

Действительно, при замене нечетного количества участков аппроксимации, соответствующих разнополярным импульсам, одним итоговым участком нового аппроксимирующего напряжения  [участок "ск"], кривая напряжения

[участок "ск"], кривая напряжения  пересекает среднюю линию, отвечающую условию ±ε/2, где ε - значение ступеньки квантования.

пересекает среднюю линию, отвечающую условию ±ε/2, где ε - значение ступеньки квантования.

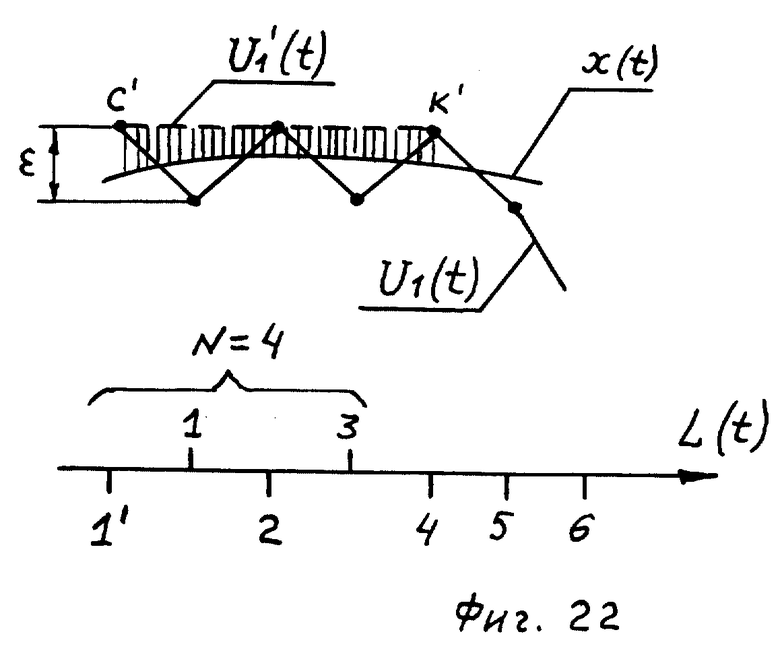

В тоже время при четном количестве разнополярных импульсов в пачке ситуация изменяется в более худшую сторону [но все же лучше, чем при известном способе, когда об уменьшении шумов квантования речь вообще не идет]. Например, если предположить, что к рассматриваемой последовательности [фиг. 14а] на входе последовательности добавился бы еще один отрицательный импульс [в точке 1'], то число разнополярных импульсов стало бы четным и равным четырем [N=4], то картина, с точки зрения уменьшения шумов квантования, станет иной [фиг. 22].

Действительно, в этом случае кривая итогового напряжения U1(t), соответствующая участку пачки разнополярных импульсов, уже не будет пересекать среднюю линию, отвечающую условию ±ε/2, что приводит к появлению некоторой систематической погрешности по шумам квантования, которая, однако, получается все же меньше исходного уровня этих шумов.

В то же время ситуацию с четным количеством разнополярных импульсов можно свести к случают нечетного их количества [когда шумы квантования могут быть уменьшены сильнее], если число "N" четного количества разнополярных импульсов представить как число (N-1) нечетного их количества плюс еще один последний по счету импульс из этой пачки, рассматриваемый при обработке отдельно от других импульсов, как это показано на фиг. 23, для случая шести разнополярных импульсов в пачке.

При этом пять из них заменяются в процессе обработки одним итоговым напряжением  а шестой рассматривается как отдельный импульс.

а шестой рассматривается как отдельный импульс.

Помимо сказанного выше, следует учесть и еще одно обстоятельство, относящееся в равной мере как к случаю четного, так и нечетного количества разнополярных импульсов в пачке.

Дело в том, что при замене пачки разнополярных импульсов одним аппроксимирующим напряжением  скорость его нарастания при обработке этой пачки импульсов должна быть уменьшена в N раз [где N - число разнополярных импульсов в пачке] по сравнению со скоростью, которую оно имеет на одном тактовом интервале в случае известного вида ДМ, который и обрабатывается с приходящей последовательностью L(t), что видно из сравнения углов α и α′, как это показано на фиг. 23.

скорость его нарастания при обработке этой пачки импульсов должна быть уменьшена в N раз [где N - число разнополярных импульсов в пачке] по сравнению со скоростью, которую оно имеет на одном тактовом интервале в случае известного вида ДМ, который и обрабатывается с приходящей последовательностью L(t), что видно из сравнения углов α и α′, как это показано на фиг. 23.

Эта несложная операция осуществляется в блоке переработки и перекодирования информации БППИ [фиг. 12] и сводится к простому уменьшению значения двоичного числа, подаваемого на вход ЦАП 49 в процессе обработки пачки разнополярных импульсов.

3-ий этап работы АЛУ.

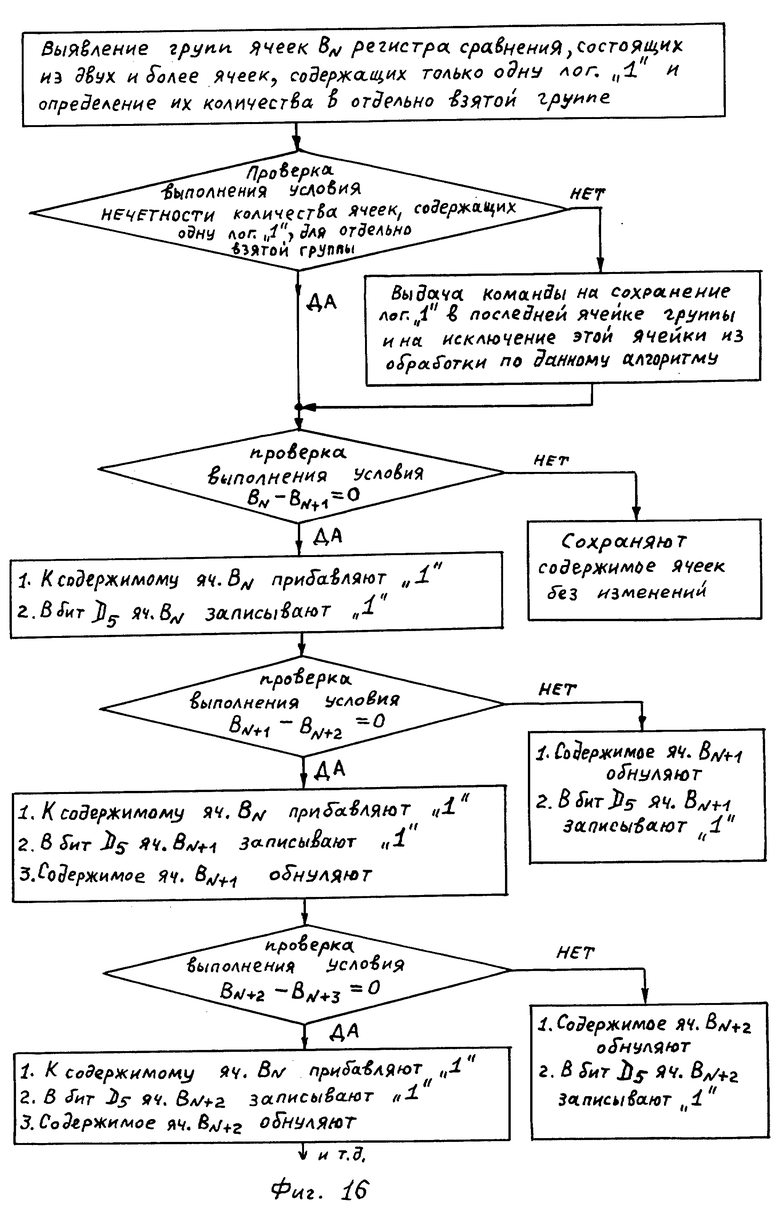

Как уже выше указывалось, этот этап необходим для обнаружения и обработки пачек разнополярных импульсов, имеющихся в последовательности L(t). При этом осуществляют следующий алгоритм обработки содержимого ячеек памяти BN регистра сравнения Р2 [но не знаковых битов, что было на предыдущем этапе при обработке регистра данных Р1].

Определяют группы ячеек BN этого регистра Р2 для случаев, когда их содержимое представляет собой только одну лог. "1", причем не менее чем в 2-х расположенных подряд одна за другой ячейках BN определяют также количество ячеек BN в отдельно взятой группе и осуществляют проверку найденного количества ячеек в отдельной группе на нечетность и далее в случае нечетного из количества осуществляют обработку регистра сравнения Р2 по алгоритму, приведенному на фиг. 16, который включает в себя следующее.

Осуществляют проверку выполнения условия BN - BN+1 = 0, и если условие выполняется, то к содержащему яч. BN прибавляют "1", а в бит D5 яч. BN записывают "1" [что служит признаком наличия в последовательности L(t) пачки резнополярных импульсов].

При невыполнении указанного условия содержимое ячеек сохраняют без изменения.

Затем осуществляют проверку выполнения условия: BN+1 - BN+2 = 0, и если условие выполняется, то к содержимому яч. BN прибавляют еще одну лог. "1", в бит D5 яч. BN+1 записывают "1", а содержимое яч. BN+1 обнуляют.

При невыполнении условия BN+1 - BN+2 = 0 содержимое яч. BN+1 обнуляют, а в бит D5 яч. BN+1 записывают "1".

Затем осуществляют проверку выполнения условия: BN+2 - BN+3 = 0, и если это условие выполняется, то к содержимому яч. BN прибавляют "1", в бит D5 яч. BN+2 записывают "1", а содержимое яч. BN+2 обнуляют.

При невыполнении условия: BN+2 - BN+3 = 0 содержимое яч. BN+2 обнуляют, а в бит D5 яч. BN+2 записывают "1" и т.д.

В случае же четного количества ячеек BN, содержащих только одну лог. "1" и входящих в состав отдельно взятой группы таких ячеек, дают команду на сохранение лог. "1" в последней ячейке группы и на исключение этой ячейки из обработки по данному алгоритму, для всех же остальных ячеек рассматриваемой группы, осуществляют алгоритм обработки, аналогичный описанному выше для случая нечетного количества ячеек, содержащих одну лог. "1" и входящих в эту группу, с последующим опрашиванием ячеек памяти регистра сравнения Р2 с частотой тактового генератора, затем формируют двоичный код в соответствии с обрабатываемым видом ДМ, подают этот код на вход знакопеременного цифроаналогового преобразователя [ЦАП], выходное напряжение которого интегрируют, после чего фильтруют полученный аналоговый сигнал.

Бывшее ранее содержимое регистра сравнения Р2 [фиг. 24б] в результате обработки по описанному выше алгоритму [фиг. 16] изменится и примет вид, который приведен на фиг. 24в, для случая обработки рассматриваемой в качестве примера последовательности L(t) из 11 импульсов /фиг. 24а/.

Конечные результаты обработки могут быть зафиксированы, естественно, не только в самом регистре Р2, но и любым другим, если это потребуется.

На фиг. 25 приведена кривая аппроксимирующего напряжения U1(t), полученная по предложенному в данной заявке способу, в соответствии с содержимым регистра Р2, приведенном на фиг. 24в.

Здесь же [на фиг. 25] приведена пунктиром для сравнения еще и кривая аппроксимирующего напряжения  соответствующая случаю обработки рассматриваемой последовательности L(t) при известном способе дельта-модуляции с двойным интегрированием [ДМДИ].

соответствующая случаю обработки рассматриваемой последовательности L(t) при известном способе дельта-модуляции с двойным интегрированием [ДМДИ].

Вид обеих кривых соответствует времени, когда их фильтрация в фильтре нижних частот [ФНЧ] еще не была проведена. После прохождения через ФНЧ эти кривые, естественно, окажутся сглаженными, однако сравнительный характер рисунка стал бы менее наглядным.

Как видно из графиков [фиг. 25], предложенный способ по сравнению с известным в случае использования только одного аппроксимирующего напряжения, позволяет уменьшить как искажения "перегрузки по крутизне", так и уменьшить шумы квантования.

Как выше отмечалось, устройство по реализации предложенного способа восстановления исходного сигнала при дельта-модуляции может быть выполнено в 2-х вариантах: с последовательной связью между блоком АЛУ и блоком БППИ и с параллельной связью между этими блоками.

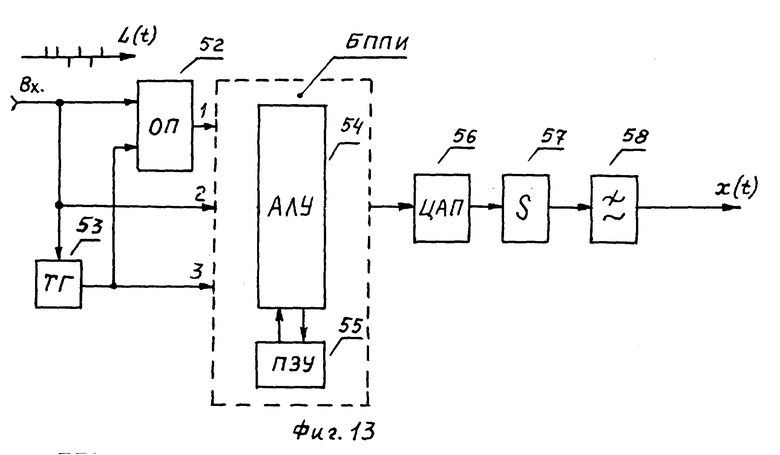

Структурная схема 2-го варианта схемы устройства, когда арифметико-логический узел [АЛУ] входит составной частью в блок переработки и перекодирования информации [БППИ], представлен на фиг. 13. Такое схемное решение позволяет осуществить параллельный обмен информацией между АЛУ и ПЗУ, что расширяет функциональные возможности устройства. Тогда в качестве блока БППИ может быть использован, например, микроконтроллер. В остальном же устройство [фиг. 13] содержит те же блоки, что и устройство [фиг. 12], рассмотренное ранее, а именно определитель полярности ОП 52, тактовый генератор ТГ 53, знакопеременный ЦАП 56, интегратор 57, ФНЧ 58, АЛУ 54, ПЗУ 55.

Работа устройства [фиг. 13] аналогична работе устройства [фиг. 12] и потому не требует дополнительных пояснений.

При этом для работы устройства с любым видом тактируемой ДМ в ПЗУ предусматриваются соответствующие шины данных.

Работа устройства [фиг. 12] была проверена экспериментально, при этом в качестве исходного брался обычный синусоидальный сигнал. Положительные результаты эксперимента подтверждают рассмотренные выше теоретические предпосылки по осуществлению способа ДМ с переменной дискретизацией временного участка.

Перечисленные блоки, входящие в состав устройства [фиг. 12], выполнены по известным схемам в виде готовых изделий, что не вызывает трудностей по практической реализации устройства, о чем выше уже упоминалось. К сказанному можно добавить еще следующее.

Так, в качестве опознавателя полярности ОП может быть использован логический элемент типа К155ЛИ1, или К555ЛИ1, а в качестве тактового генератора может быть использована микросхема типа К580ГФ24. В качестве АЛУ [фиг. 12] можно использовать готовый микропроцессор, например типа КР580ИК80А, или любой другой.

Что касается схемы устройства [фиг. 13], то блок БППИ, содержащий АЛУ и ПЗУ, может быть выполнен на микроконтроллере, например типа 1816ВЕ48, или 1816ВЕ51.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ восстановления исходного сигнала при дельта-модуляции и устройство для дельта-демодуляции | 1987 |

|

SU1571766A1 |

| Способ дельта-модуляции | 1989 |

|

SU1672568A1 |

| Дельта-модулятор | 1983 |

|

SU1129732A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Устройство связи с дельта-модуляцией | 1986 |

|

SU1365364A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| ВЫСОКОИНФОРМАТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ИСПОЛЬЗОВАНИЕМ ДЕЛЬТА-МОДУЛЯЦИИ ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 1997 |

|

RU2128880C1 |

| Дельта-модулятор | 1984 |

|

SU1203707A1 |

| Дельта-модулятор | 1987 |

|

SU1474850A1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

Изобретение относится к технике связи и вычислительной технике и может быть использовано в системах передачи информации при любых видах дельта-модуляции (ДМ). Способ восстановления исходного сигнала при ДМ и устройство для дельта-демодуляции решают задачу повышения точности восстановления исходного сигнала при формировании только одного аппроксимирующего напряжения для любого вида ДМ путем уменьшения как искажений "перегрузки по крутизне", так и шумов квантования. Устройство для дельта-демодуляции содержит определитель полярности приходящих импульсов, арифметико-логический узел, тактовый генератор, знакопеременный цифроаналоговый преобразователь, интегратор, фильтр нижних частот, блок переработки и перекодирования информации. 2 с.п. ф-лы, 25 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Р | |||

| Стил | |||

| Принципы дельта-модуляций | |||

| Перевод с англ | |||

| Под ред | |||

| В.В | |||

| Маркова | |||

| - М.: Связь, 1979, с.17 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| RU, авторское свидетельство 1571766, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1999-04-20—Публикация

1994-11-08—Подача