Изобретение относится к вычислительной технике. Известен процессор (Калабеков Б.А, Микропроцессоры и их применение в системах передачи и обработки сигналов, М.: Радио и связь, 1988, с. 30, рис. 1.3), содержащий управляющий узел, операционный узел, первая группа входов управляющего узла является входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы которого являются входами данных, а вторые выходы являются выходами данных.

Недостатком устройства является недостаточная отказоустойчивость процессора, так как не обеспечивается обнаружение и коррекция возникающих ошибок.

Наиболее близким по техническому решению является резервированная ЭВМ с постоянным замещением (Щербаков Н.С. Достоверность работы цифровых устройств. М.: Машиностроение, 1989. с. 35, рис. 1.1.), содержащая в своем составе две ЭВМ, каждая из которых контролируется схемами встроенного контроля, выходы которых подключены к входам решающего органа, который, в случае отказа одной из ЭВМ, подключает к выходам устройства исправный канал.

Недостатком устройства является большая аппаратурная избыточность схем встроенного контроля и дублирующего канала процессора ЭВМ.

Задачей изобретения является сокращение аппаратурных затрат на резервирование за счет использования для обнаружения ошибок в ЭВМ алгебраического линейного кода с минимальной избыточностью и использования результатов кодирования информации для формирования дублирующего канала за счет функциональной избыточности процессора.

Сущность изобретения заключается в том, отказоустойчивая ЭВМ, содержащая управляющий узел, узел обмена, первый запоминающий узел, арифметико-логический узел, блок регистров, сумматор, блок сумматоров по mod 2, блок элементов И, блок элементов ИЛИ, отличающееся тем, что дополнительно содержит второй запоминающий узел, первый кодирующий блок, второй кодирующий блок, третий кодирующий блок, четвертый кодирующий блок, коммутатор, первую схему сравнения, вторую схему сравнения, резервный блок сумматоров по mod 2, блок формирования функции переносов, блок формирования функции сдвига, резервный регистр сдвига, причем первые входы узла обмена являются входами ЭВМ, первые выходы узла обмена являются выходами ЭВМ, вторые выходы узла обмена подключены к входам коммутатора, к входам первого кодирующего блока, к первым входам первого запоминающего узла, к первым входам второго запоминающего узла, к первому и второму входам блока суммирования поправки, к входам управляющего узла, третий выход узла обмена подключен к первым входам блока регистров, к первым входам резервного регистра сдвига, к первым входам сумматора, к первым входам блока сумматоров по mod 2, к первым входам резервного блока сумматоров по mod 2, к первым входам блока элементов И, к первым входам блока элементов ИЛИ, к первым входам блока формирования функции переносов, к первым входам блока формирования функции сдвига, выход управляющего узла подключен к вторым входам первого и второго запоминающих узлов, к вторым входам блока регистров, к вторым входам резервного регистра сдвига, к вторым входам сумматора, к вторым входам блока сумматоров по mod 2, к вторым входам резервного блока сумматоров по mod 2, к вторым входам блока элементов И, к вторым входам блока элементов ИЛИ, к вторым входам блока формирования функции переносов, к вторым входам блока формирования функции сдвига, к вторым входам коммутатора, к вторым входам узла обмена, выходы первого кодирующего блока подключены к третьим входам узла обмена и третьим входам первого запоминающего узла, выходы которого подключены к третьим входа коммутатора, выходы второго кодирующего блока подключены к третьим входам второго запоминающего узла, выходы которого подключены к четвертым входам коммутатора, выходы блока суммирования поправки подключены к пятым входам коммутатора, первые выходы которого подключены к четвертым входам узла обмена и к входам третьего кодирующего блока, а вторые входы подключены к первым входам первой схемы сравнения, третьи выходы коммутатора подключены к пятым входам узла обмена и к входам четвертого кодирующего блока, а четвертые выходы подключены к первым входам второй схемы сравнения, выходы третьего кодирующего блока подключены к вторым входам первой схемы сравнения, выходы четвертого кодирующего блока подключены к вторым входам второй схемы сравнения, выходы первой и второй схем сравнения подключены к шестым входам узла обмена, выходы блока регистров, резервного регистра сдвига, сумматора, блока сумматоров по mod 2, резервного блока сумматоров по mod 2, блока элементов И, блока элементов ИЛИ, блока формирования функции переносов, блока формирования функции сдвига, подключены к седьмым входам узла обмена, первый кодирующий блок, в зависимости от команд, поступающих с выходов управляющего узла на узел обмена, формирует значения контрольных разрядов относительно информационных символов yiЗУ1, поступающих с выходов узла обмена в первый запоминающий узел, или значения разрядов поправки относительно информационных символов yiФП функции переносов, или значения разрядов поправки относительно информационных символов уiФС функции сдвига, или значения разрядов поправки относительно информационных символов уiИ при выполнении логической операции ИЛИ, или значения разрядов поправки относительно информационных символов уiИЛИ при выполнении логической операции И, на своем первом r1, втором r2 и третьем r3 выходе путем сложения по модулю 2 информационных символов y1i j, у2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1=y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j, ⊕ y9i j, ⊕ y10i j ⊕ y11i j, r2=y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3=y1i j ⊕ y4i j ⊕ y5 j ⊕ y6i j, ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j, второй кодирующий блок, в зависимости от команд, поступающих с выходов управляющего узла на узел обмена, формирует значения контрольных разрядов относительно информационных символов yiЗУ2, поступающих с выходов узла обмена в второй запоминающий узел на своем первом r12, втором r22 и третьем r32 выходе путем сложения по модулю 2 информационных символов y1ЗУ2, у2ЗУ2, y3ЗУ2, y4ЗУ2, y5ЗУ2, y6ЗУ2, y7ЗУ2, y8ЗУ2, y9ЗУ2, y10ЗУ2, y11ЗУ2, y12ЗУ2 в соответствии с правилом: r12=у3ЗУ2 ⊕ у5ЗУ2 ⊕ y7ЗУ2 ⊕ y8ЗУ2, ⊕ y9ЗУ2 ⊕ y10ЗУ2 ⊕ y11ЗУ2, r22=у2ЗУ2 ⊕ y4ЗУ2 ⊕ y5ЗУ2 ⊕ y8ЗУ2, ⊕ y9ЗУ2 ⊕ y10 ЗУ2 ⊕ у11ЗУ2, r32=y1ЗУ2 ⊕ y4ЗУ2 ⊕ y5ЗУ2 ⊕ y6ЗУ2, ⊕ y7ЗУ2 ⊕ y10ЗУ2 ⊕ y11ЗУ2 ⊕ y12ЗУ2, третий кодирующий блок, в зависимости от команд, поступающих с выходов управляющего узла на входы коммутатора, формирует значения контрольных разрядов относительно информационных символов yiЗУ1, считываемых с первого запоминающего узла, или значения разрядов суммы yiАУ, поступающих с выходов сумматора, или информационных разрядов уim, поступающих с выходов блока сумматоров по mod 2, или значений информационных разрядов уiИ, поступающих с выходов блока элементов И, или значений информационных разрядов yiИЛИ, поступающих с выходов блока элементов ИЛИ, или значений информационных разрядов yiC, поступающих с выходов блока регистров на своем первом r1ф1, втором r2ф1 и третьем r3ф1 выходе путем сложения по модулю 2 информационных символов y1i j, y2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1ф1=y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r2ф1=y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3ф1=y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j, четвертый кодирующий блок, в зависимости от команд, поступающих с выходов управляющего узла на входы коммутатора, формирует значения контрольных разрядов относительно информационных символов yiЗУ2, считываемых с второго запоминающего узла, или значения разрядов суммы yim, поступающих с выходов блока сумматоров по mod 2 при выполнении арифметической операции, или информационных разрядов yimp, поступающих с выходов резервного блока сумматоров по mod 2 при выполнении логической операции суммирования по mod2, или значений информационных разрядов yimИ, поступающих с выходов блока сумматоров по mod 2 при выполнении логической операции И, или значений информационных разрядов уimИЛИ, поступающих с выходов блока сумматоров по mod 2, при выполнении логической операции ИЛИ, или значений информационных разрядов yimc при выполнении операции сдвига, поступающих с выходов резервного блока сумматоров по mod 2 на своем первом r1ф2, втором r2ф2 и третьем r3ф2 выходе путем сложения по модулю 2 информационных символов y1i j, y2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1ф2=y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j , ⊕ y9i j ⊕ y10i j ⊕ y11i j, r2ф2=y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3ф2=y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j, ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j, блок 13 формирования функции переносов формирует значение функции переносов относительно значений информационных разрядов слагаемых yiA и yiB в соответствии с правилом: s1=0, s2=y1A^y1B, s3=y2A^y2B v (y2A v y2B) ^ s2, s4=y3A^y3B v (y3A v y3B) ^ s3, s5=y4A^y4B v (y4A v y4B) ^ s4, s6=y5A^y5B v (y5A v y5B) ^ s5, s7=y6A^y6 В v (y6A v y6B) ^ s5, s8=y7A^y7B v (y7A v y7В) ^ s7, s9=y8A^y8B v (у8А v у8В) ^ s8, s10=y9A^y9B v (у9А v у9В) ^ s9, s11=y10A^y10B v (у10А v y10B) ^ s10, s12=y11A^y11B v (у11А v у11В) ^ s11, блок формирования функции сдвига формирует значение функции сдвига вправо относительно исходных значений информационных разрядов yi регистра сдвига в соответствии с правилом: s12=y12, s11=y12⊕y11, s10=y11⊕y10, s9=y10⊕y9, s8=y9⊕y8, s7=y8⊕y7, s6=y7⊕y6, s5=y6⊕y5, s4=y5⊕y4, s3=y4⊕y3, s2=y3⊕y2, s1=y2⊕y1 и значение функции сдвига влево в соответствии с правилом: s1=y1, s2=y1⊕y2, s3=y2⊕y3, s4=y3⊕y4, s5=y4⊕y5, s6=y5⊕y6, s7=y6⊕y7, s8=y7⊕y8, s9=y8⊕y9, s10=y9⊕y10, s11=y10⊕y9, s12=y11⊕y12.

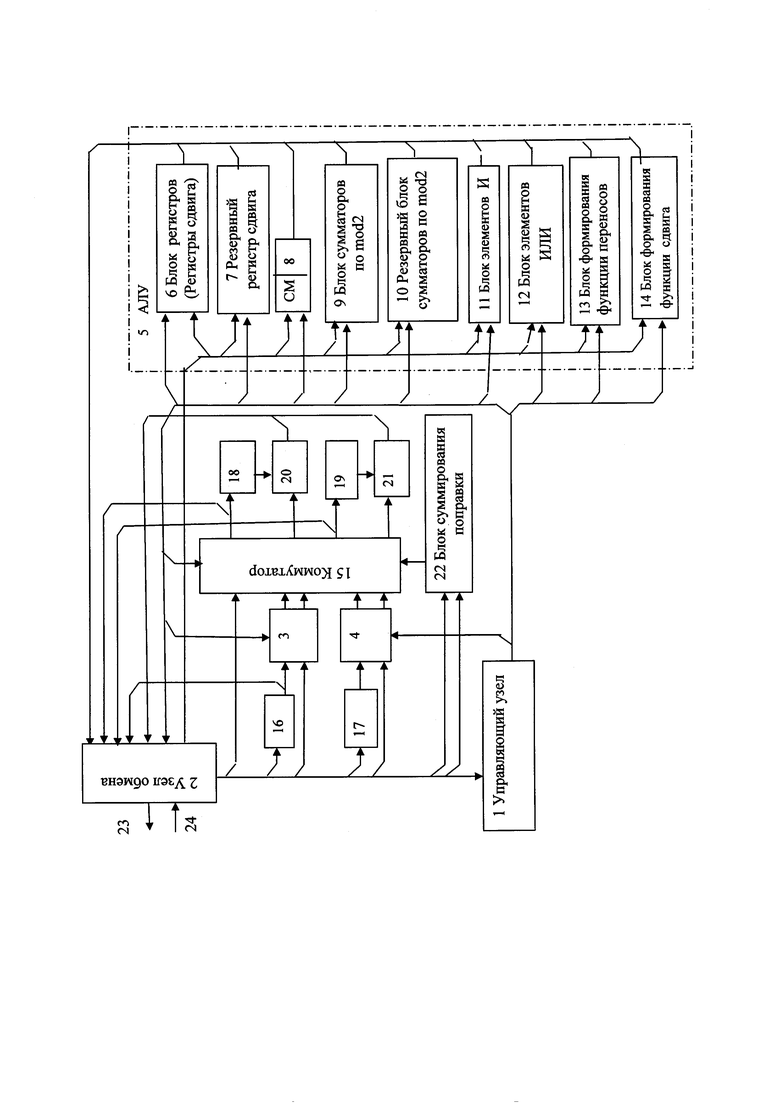

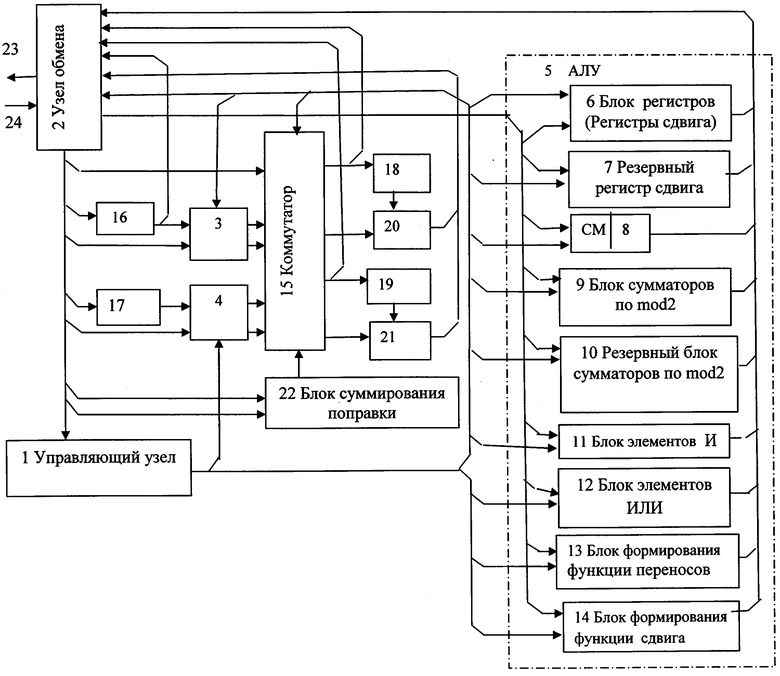

На фиг. 1 представлена блок-схема устройства.

Отказоустойчивая ЭВМ (фиг. 1) управляющий узел 1, узел 2 обмена, первый запоминающий узел 3, второй запоминающий узел 4, арифметико-логический узел 5, блок 6 регистров, резервный регистр 7 сдвига, сумматор 8, блок 9 сумматоров по mod 2, резервный блок 10 сумматоров по mod 2, блок 11 элементов И, блок 12 элементов ИЛИ, блок 13 формирования функции переносов, блок 14 формирования функции сдвига, коммутатор 15, первый кодирующий блок 16, второй кодирующий блок 17, третий кодирующий блок 18, четвертый кодирующий блок 19, первая схема 20 сравнения, вторая схема 21 сравнения, блок 22 суммирования поправки, вход 23 отказоустойчивой ЭВМ, выход 24 отказоустойчивой ЭВМ.

Первые входы узла 2 обмена являются входами ЭВМ, первые выходы узла 2 обмена являются выходами ЭВМ, вторые выходы узла 2 обмена подключены к входам коммутатора 15, к входам первого кодирующего блока 16, к первым входам первого запоминающего узла 3, к первым входам второго запоминающего узла 4, к первому и второму входам блока 22 суммирования поправки, к входам управляющего узла 1, третий выход узла 2 обмена подключен к первым входам блока 6 регистров, к первым входам резервного регистра 7 сдвига, к первым входам сумматора 8, к первым входам блока 9 сумматоров по mod 2, к первым входам резервного блока 10 сумматоров по mod 2, к первым входам блока 11 элементов И, к первым входам блока 12 элементов ИЛИ, к первым входам блока 13 формирования функции переносов, к первым входам блока 14 формирования функции сдвига, выход управляющего узла 1 подключен к вторым входам первого 3 и второго 4 запоминающих узлов, к вторым входам блока 6 регистров, к вторым входам резервного регистра 7 сдвига, к вторым входам сумматора 8, к вторым входам блока 9 сумматоров по mod 2, к вторым входам резервного блока 10 сумматоров по mod 2, к вторым входам блока 11 элементов И, к вторым входам блока 12 элементов ИЛИ, к вторым входам блока 13 формирования функции переносов, к вторым входам блока 14 формирования функции сдвига, к вторым входам коммутатора 15, к вторым входам узла 2 обмена, выходы первого кодирующего блока 16 подключены к третьим входам узла 2 обмена и третьим входам первого запоминающего узла 3, выходы которого подключены к третьим входа коммутатора 15, выходы второго кодирующего блока 17 подключены к третьим входам второго запоминающего узла 4, выходы которого подключены к четвертым входам коммутатора 15, выходы блока 22 суммирования поправки подключены к пятым входам коммутатора 15, первые выходы которого подключены к четвертым входам узла 2 обмена и к входам третьего кодирующего блока 18, а вторые входы подключены к первым входам первой схемы 20 сравнения, третьи выходы коммутатора 15 подключены к пятым входам узла 2 обмена и к входам четвертого кодирующего блока 19, а четвертые выходы подключены к первым входам второй схемы 21 сравнения, выходы третьего кодирующего блока 18 подключены к вторым входам первой схемы 20 сравнения, выходы четвертого кодирующего блока 19 подключены к вторым входам второй схемы 21 сравнения, выходы первой 20 и второй 21 схем сравнения подключены к шестым входам узла 2 обмена, выходы блока 6 регистров, резервного регистра 7 сдвига, сумматора 8, блока 9 сумматоров по mod 2, резервного блока 10 сумматоров по mod 2, блока 11 элементов И, блока 12 элементов ИЛИ, блока 13 формирования функции переносов, блока 14 формирования функции сдвига, подключены к седьмым входам узла 2 обмена, первый кодирующий блок 16, в зависимости от команд, поступающих с выходов управляющего узла 1 на узел 2 обмена, формирует значения контрольных разрядов относительно информационных символов yiЗУ1, поступающих с выходов узла 2 обмена в первый запоминающий узел 3, или значения разрядов поправки относительно информационных символов уiФП функции переносов, или значения разрядов поправки относительно информационных символов yiФC функции сдвига, или значения разрядов поправки относительно информационных символов yiИ при выполнении логической операции ИЛИ, или значения разрядов поправки относительно информационных символов yiИЛИ при выполнении логической операции И, на своем первом r1, втором r2 и третьем r3 выходе путем сложения по модулю 2 информационных символов y1i j, y2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1=y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j ⊕ y9i j ⊕ y10i j ⊕ y11i j r2=y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3= y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j, второй кодирующий блок 17, в зависимости от команд, поступающих с выходов управляющего узла 1 на узел 2 обмена, формирует значения контрольных разрядов относительно информационных символов yiЗУ2, поступающих с выходов узла 2 обмена в второй запоминающий узел 4 на своем первом r12, втором r22 и третьем r32 выходе путем сложения по модулю 2 информационных символов y1ЗУ2, y2ЗУ2, y3ЗУ2, у4ЗУ2, y5ЗУ2, y6ЗУ2, y7ЗУ2, y8ЗУ2, y9ЗУ2, y10ЗУ2, y11ЗУ2,y12ЗУ2 в соответствии с правилом: r12=y3ЗУ2 ⊕ y5ЗУ2 ⊕ y7ЗУ2 ⊕ y8ЗУ2, ⊕ y9ЗУ2 ⊕ y10ЗУ2 ⊕ y11ЗУ2, r22=у2ЗУ2 ⊕ y4ЗУ2 ⊕ y5ЗУ2 ⊕ y8ЗУ2, ⊕ y9ЗУ2 ⊕ y10ЗУ2 ⊕ y11ЗУ2, r32=у1ЗУ2 ⊕ y4ЗУ2 ⊕ y5ЗУ2 ⊕ y6ЗУ2, ⊕ y7ЗУ2 ⊕ у10ЗУ2 ⊕ у11ЗУ2 ⊕ y12ЗУ2, третий кодирующий блок 18, в зависимости от команд, поступающих с выходов управляющего узла 1 на входы коммутатора 15, формирует значения контрольных разрядов относительно информационных символов yiЗУ1, считываемых с первого запоминающего узла 3, или значения разрядов суммы уiАУ, поступающих с выходов сумматора 8, или информационных разрядов yim, поступающих с выходов блока 9 сумматоров по mod 2, или значений информационных разрядов yiИ, поступающих с выходов блока 11 элементов И, или значений информационных разрядов yiИЛИ, поступающих с выходов блока 12 элементов ИЛИ, или значений информационных разрядов yiC, поступающих с выходов блока 6 регистров на своем первом r1ф1, втором r2ф1 и третьем r3ф1 выходе путем сложения по модулю 2 информационных символов y1i j, у2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1ф1=y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r2ф1=у2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3ф1=y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j, ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j, четвертый кодирующий блок 19, в зависимости от команд, поступающих с выходов управляющего узла 1 на входы коммутатора 15, формирует значения контрольных разрядов относительно информационных символов yiЗУ2, считываемых с второго запоминающего узла 4, или значения разрядов суммы уim, поступающих с выходов блока 9 сумматоров по mod 2 при выполнении арифметической операции, или информационных разрядов yimp, поступающих с выходов резервного блока 7 сумматоров по mod 2 при выполнении логической операции суммирования по mod2, или значений информационных разрядов yimИ, поступающих с выходов блока 9 сумматоров по mod 2 при выполнении логической операции И, или значений информационных разрядов уimИЛИ, поступающих с выходов блока 9 сумматоров по mod 2, при выполнении логической операции ИЛИ, или значений информационных разрядов yimc при выполнении операции сдвига, поступающих с выходов резервного блока 10 сумматоров по mod 2 на своем первом r1ф2, втором r2ф2 и третьем r3ф2 выходе путем сложения по модулю 2 информационных символов y1i j, y2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j, в соответствии с правилом: r1ф2=y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j , ⊕ y9i j ⊕ y10i j ⊕ y11i j, r2ф2=y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3ф2=y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j, ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j, блок 13 формирования функции переносов формирует значение функции переносов относительно значений информационных разрядов слагаемых yiА и yiB в соответствии с правилом: s1=0, s2=y1A^y1B, s3=y2A^y2B v (y2A v y2В) ^ s2, s4=y3A^y3B v (у3А v у3В) ^ s3, s5=y4A^y4B v (у4А v y4B) ^ s4, s6=y5A^y5B v (y5A v у5B) ^ s5, s7=y6A^y6B v (у6А v у6В) ^ s5, s8=y7A^y7B v (у7А v у7В) ^ s7, s9=y8A^y8B v (у8А v у8В) ^ s8, s10=y9A^y9B v (у9А v у9В) ^ s9, s11=y10A^y10B v (у10А v у10В) ^ s10, s12=y11A^y11B v (y11A v у11B) ^ s11, блок 14 формирования функции сдвига формирует значение функции сдвига вправо относительно исходных значений информационных разрядов уi регистра сдвига в соответствии с правилом: s12=y12, s11=y12⊕y11, s10=y11⊕y10, s9=y10⊕y9, s8=y9⊕y8, s7=y8⊕y7, s6=y7⊕y6, s5=y6⊕y5, s4=y5⊕y4, s3=у4⊕у3, s2=y3⊕y2, s1=y2⊕y1 и значение функции сдвига влево в соответствии с правилом: s1=y1, s2=y1⊕y2, s3=y2⊕у3, s4=y3⊕y4, s5=y4⊕y5, s6=y5⊕y6, s7=y6⊕y7, s8=y7⊕y8, s9=y8⊕y9, s10=y9⊕y10, s11=y10⊕y9, s12=y11⊕y12.

Управляющий узел 1 координирует действия узлов операционного узла 2 между собой и с другими узлами ЭВМ, а также выполняет набор операций, включающих команды обращения к памяти. Он вырабатывает в определенной временной последовательности управляющие сигналы, под действием которых в узлах арифметико-логического узла 5 выполняются требуемые действия.

Таким образом, управляющий узел 1 осуществляет преобразование команды в соответствующий набор управляющих сигналов и обеспечивает:

запись информации в первый 3 и второй 4 запоминающий узел;

считывание команды, находящейся в очередной ячейке памяти запоминающих узлов;

расшифровку кода операции (команды);

отыскание операндов (чисел) по указанному адресу, содержащемуся в команде;

установку в нулевое состояние элементов памяти;

синхронизацию работы функциональных узлов ЭВМ;

коммутацию с помощью узла 2 обмена и коммутатора 15 входов и выходов функциональных узлов ЭВМ между собой;

обеспечивает выдачу управляющих сигналов в операционный узел для выполнения над операндами действий, указанных в коде операции команды.

В данном случае используется микропрограммный управляющий узел 1, в котором микрокоманды хранятся в управляющей памяти.

Узел 2 обмена предназначен для организации обмена информацией между функциональными узлами и периферийными устройствами ЭВМ.

Первый 3 и второй 4 запоминающие узлы представляют собой статические полупроводниковые запоминающие устройства.

Арифметико-логический узел 5 включает блок 6 регистров, резервный регистр 7 сдвига, которые предназначенны для выполнения арифметических операций.

Блок 6 регистров содержит: регистр числа, регистр сумматора (аккумулятора), регистр дополнительный, регистр дополнительного кода.

Регистр числа представляет собой регистр памяти и предназначен для хранения операндов при выполнении арифметических и логических операций (хранения множимого, при выполнении операции умножения и делителя при выполнении операции деления).

Регистр сумматора (аккумулятора) представляет собой регистр сдвига (вправо -при выполнении операции умножения и влево - при выполнении операции деления), и предназначен для хранения делимого старших разрядов результата умножения.

Заметим, что при выполнении операции деления, в управляющем узле 1 анализируется значение знакового разряда регистра числа и регистра дополнительного.

Регистр дополнительный представляет собой регистр сдвига (вправо -при выполнении операции умножения и влево - при выполнении операции деления), и предназначен для хранения множителя и младших разрядов результата умножения при выполнении операции умножения и результата деления при выполнении операции деления).

Заметим, что при выполнении операции умножения, в управляющем узле 1 анализируется значение младшего разряда регистра дополнительного.

Регистр дополнительного кода представляет собой регистр памяти и предназначен для хранения отрицательного числа в дополнительном коде (при выполнении операции вычитания и операции деления).

Резервный регистр 7 сдвига, осуществляет сдвиг исходной информации с задержкой на один такт и предназначен для хранения исходной информации регистра сумматора (регистра дополнительного) при выполнении ими операции сдвига для формирования в этот период функции сдвига.

Сумматор 8 представляет собой параллельный n- разрядный сумматор и предназначен для выполнения операции сложения чисел.

Блок 9 сумматоров по mod 2 реализует функцию неравнозначности относительно информационных разрядов операндов. Резервный блок 10 сумматоров по mod 2 реализует функцию неравнозначности относительно информационных разрядов и контрольных разрядов операндов и является резервным блоком для блока 9 сумматоров по mod 2.

Блок 11 элементов И, блок 12 логических элементов ИЛИ предназначены соответственно для выполнения операций логического сложения и умножения, формирования значений поправки к контрольным разрядам при выполнении данных операций и совместно с блоком 9 сумматоров по mod 2 формирования дублирующего канала.

Блок 13 формирования функции переносов предназначен для формирования поправки к значениям контрольных разрядов для контроля выполнения арифметических операций в сумматоре 8 и совместно с резервным боком 10 сумматоров по mod 2 формирования дублирующего канала выполнения арифметической операции сложения.

Блок 14 формирования функции сдвига предназначен для формирования поправки к значениям контрольных разрядов при выполнении операции сдвига вправо (влево) и формирования дублирующего канала при выполнении данной операции.

Коммутатор 15 предназначен для коммутации входов и выходов функциональных узлов ЭВМ.

Первый 16, второй 17, третий 18, четвертый 19 кодирующие блоки, в зависимости от команд, поступающих с выходов управляющего узла 1, формируют значения контрольных разрядов на своем первом r1, втором r2 и третьем r3 выходе путем сложения по модулю 2 информационных символов y1i j, y2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1=y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j, ⊕ y9i j ⊕ у10i j ⊕ y11i j, r2=y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j ⊕,y9i j ⊕ y10i j ⊕ y11i j, r3=y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j,⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j.

Первая 20 и вторая 21 схемы сравнения предназначены для поразрядного сравнения (суммирования по mod 2) значений контрольных разрядов, которые должны соответствовать рассматриваемой операции с значениями контрольных разрядов сформированных после выполнения операции.

Блок 22 суммирования поправки осуществляет поразрядное сложение по mod 2 значений поправки, сформированной в первом кодирующем блоке 16 и значений контрольных разрядов, поступающих с выходов резервного блока 10 сумматоров по mod 2 и резервного регистра 7 сдвига.

Работа ЭВМ начинается с приходом сигнала "Пуск" по входной группе входов узла 2 обмена.. По этой команде управляющий узел 1 выдает команду на считывание с управляющей памяти содержимого первой ячейки памяти.

В первой ячейке памяти расположена команда "Сброс системы", которая устанавливает в исходное состояние регистры и блоки процессора.

Далее, в зависимости от вида операции, узел 1 управления выдает микрокоманды на функциональные узлы ЭВМ.

При записи информации в первый 3 и второй 4 узлы памяти информационные разряды одновременно поступают на входы первого 16 и второго 17 кодирующих блоков, где формируются значения контрольных разрядов, которые записываются соответственно в первом 3 и втором 4 узлах памяти одновременно с значениями информационных разрядов.

При считывании информации с первого 3 и второго 4 узлов памяти, значения информационных разрядов, через коммутатор 15, поступают соответственно на входы третьего 18 и четвертого 19 кодирующих блоков, а значения контрольных разрядов поступают на первые входы первой 20 и второй 21 схем сравнения, на вторые входы которых поступают значения контрольных разрядов, сформированные относительно считываемых из узлов памяти значений информационных разрядов.

Первая 20 и вторая 21 схемы сравнения осуществляют поразрядное сравнении считываемых и сформированных значений контрольных разрядов. Если в считываемой информации ошибок не обнаружено, тона выходах схем сравнения имеем нулевые значения сигналов. В работе ЭВМ используется информации, считываемая с первого узла 3 памяти.

Появление единичного значения сигнала на выходе схемы сравнения свидетельствует о наличии ошибки. В этом случае, в зависимости от значений сигналов, поступающих с выходов схем сравнения, выбирается исправный канал.

При выполнении логической операции по mod 2 результат сложения по mod 2 контрольных разрядов слагаемых соответствует результату сложения по mod 2 информационных разрядов слагаемых.

Для формирования дублирующего канала для блока 9 сумматоров по mod 2 используем идентичный резервный бок 10 сумматоров по mod 2 в котором осуществляется поразрядное сложение информационных и контрольных разрядов.

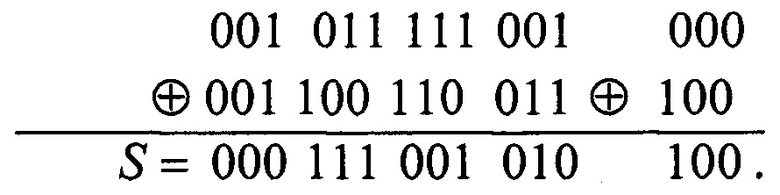

Пример. Допустим, требуется сложить два кодовых набора, содержащих 12 информационных и три контрольных разряда.

При сложении значений информационных и контрольных разрядов кодовых наборов Ак=001 011 111 001 000; Вк=001 100 110 011 100 в резервном блоке 10 сумматоров по mod 2 получим результат:

В основном блоке сумматоров по mod 2 осуществляется сложение значений только информационных разрядов.

Результаты суммирования значений информационных разрядов блоком 9 сумматоров по mod 2 и резервным блоком 10 сумматоров по mod 2 через узел 2 обмена и коммутатор 15 поступают соответственно на входы третьего 18 и четвертого 19 кодирующих устройств, выходы которых подключены к первым входам первой 20 и второй 21 схем сравнения. На вторые входы первой и второй схем сравнения поступают значения контрольных разрядов сформированных в резервном блоке 10 сумматоров по mod 2.

Совпадение переданных и сформированных значений контрольных разрядов в схемах сравнения свидетельствует об отсутствии ошибок. При отказе одного из блоков сумматоров по mod 2, по значениям сигналов, поступающих с первой 20 и второй 21 схем сравнения в узле 2 обмена осуществляется подключение выходов исправного блока. При отказе двух каналов формируется сигнал «Отказ устройства».

Организация контроля выполнения арифметических операций и формирование дублирующего канала для выполнения арифметических операций основана на свойстве, которое заключается в том, что результат поразрядного суммирования по mod 2 значений функции переносов с результатом сложения по mod 2 слагаемых получим арифметическую сумму слагаемых.

Функция формирования переносов определяется выражением: s1=0, s2=y1A^y1B, s3=y2A^y2B v (у2А v у2В) ^ s2, s4=y3A^y3B v (у3А v у3В) ^ s3, s5=y4A^y4B v (у4А v y4B) ^ s4, s6=y5A^y5B v (у5А v у5В) ^ s5, s7=y6A^y6B v (у6А v y6B) ^ s5, s8=y7A^y7B v (у7А v у7В) ^ s7, s9=y8A^y8B v (у8А v у8В) ^ s8, s10=y9A^y9B v (у9А v у9В) ^ s9, s11=у10А^у10В v (y10A v y10B) ^ s10, s12=y11A^y11B V (y11A v у11В) ^ s11,

Для рассматриваемого примера, значения разрядов функции переносов имеют вид: Sп=011 111 100 110.

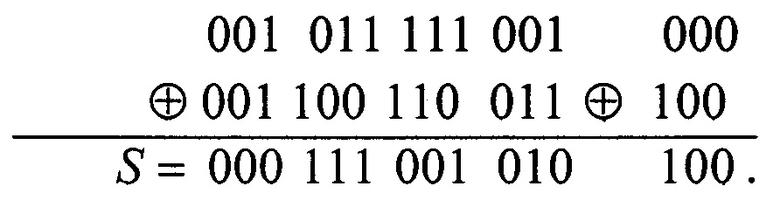

В результате суммирования слагаемых в резервном блоке 10 по mod 2, получим значения суммы:

Арифметическая сумма слагаемых определяется сложением в блоке 9 сумматоров по mod 2 результаты суммы значений информационных разрядов, поступающих с выходов резервного блока 10 сумматоров по mod 2, с значениями функции переносов (SА=S⊕SП):

В результате имеем арифметическую сумму рассматриваемых слагаемых, однако полученное значение контрольных разрядов не соответствует полученной сумме.

Формирование поправки Пк к значению контрольных разрядов Sкmod2 осуществляется кодированием функции переносов Sп выбранным методом кодирования информации в перв кодирующем блоке 16.

Для рассматриваемого примера, кодирование значения Sп=011 111 100 110 с помощью предложенного метода кодирования, приведет к значению поправки Пк=110.

Значения контрольных разрядов с выходов резервного блока 10 сумматоров по mod 2, через узел 2 обмена, поступают на первые входы блока 22 суммирования поправки, на вторые входы которого поступают значения поправки с выходов первого кодирующего блока 16.

В результате поразрядного сложения по mod 2 в блоке 22 суммирования поправки значений контрольных разрядов, поступающих с выходов резервного блока 10 сумматоров по mod 2: Sкmod2=100 и значений разрядов поправки: Пк=110, получим правильное значение контрольных разрядов для найденной арифметической суммы. Оно примет вид

Sк=011 000 101 100 010.

Значения информационных разрядов сумматора 8 и блока 9 сумматоров по mod 2 (резервного канала) поступают на входы узла обмена и через коммутатор 15 поступают соответственно и на входы третьего 18 и четвертого 19 блоков, где формируются значения контрольных разрядов относительно полученной арифметической суммы, которые поступают соответственно на первые входы первой 20 и второй 21 схем сравнения. На вторые входы первой 20 и второй схем сравнения поступают значения контрольных разрядов с выходов блока 22 суммирования поправки. Выбор исправного канала осуществляется по алгоритму описанному выше.

Организация контроля и формирование дублирующего канала для выполнения операции сдвига основана том, что результат поразрядного суммирования по mod 2 значений функции сдвига вправо (влево) с исходным значением информационных разрядов определяет значение информационных разрядов при сдвиге вправо (влево).

Блок 14 формирования функции сдвига формирует значение функции сдвига вправо относительно исходных значений информационных разрядов yi регистра сдвига в соответствии с правилом: s12=y12, s11=y12⊕y11, s10=y11⊕y10, s9=y10⊕y9, s8=y9⊕y8, s7=y8⊕y7, s6=y7⊕y6, s5=y6⊕y5, s4=y5⊕y4, s3=y4⊕y3, s2=y3⊕y2, s1=y2⊕y1 и значение функции сдвига влево в соответствии с правилом: s1=у1, s2=y1⊕y2, s3=y2⊕y3, s4=y3⊕y4, s5=y4⊕y5, s6=y5⊕y6, s7=y6⊕y7, s8=y7⊕y8, s9=y8⊕y9, s10=y9⊕y10, s11=y10⊕y9, s12=y11⊕y12.

Формирование дублирующего канала для выполнения операции сдвига включает следующие действия:

1. Исходная информация записывается в основной 6 и резервный 7 регистры сдвига;

2. Считывание информации с резервного регистра 7 сдвига осуществляется с задержкой на один такт.

3. Блок 14 формирования функции сдвига формирует функцию сдвига вправо (влево) относительно значений информационных разрядов, поступающих с выходов резервного регистра 7 сдвига.

4. Значения разрядов функции сдвига поступают на вход первого кодирующего блока 16.

5. Значения контрольных разрядов, с выходов резервного регистра 7 сдвига, соответствующие исходной информации поступают на первые входы блока 22 суммирования поправки, на вторые входы которого поступает значение поправки с выходов первого кодирующего блока 16.

6. В резервном блоке 10 сумматоров по mod 2 осуществляется поразрядное сложение по mod 2 исходного значения информационных разрядов, поступающих с выходов резервного регистра 7 сдвига и значений разрядов функции сдвига, поступающих с выходов блока 14 формирования функции сдвига. В результате получим значения информационных разрядов при сдвиге вправо (влево).

7. Значения информационных разрядов с выходов основного регистра 6 сдвига поступают на вход третьего кодирующего блока 18, а значения информационных разрядов резервного блока 10 суммировании по mod 2 поступают на вход четвертого кодирующего блока 19.

8. Значения контрольных разрядов, соответствующие операции сдвига с выходов блока 22 суммирования поправки поступают на первые входы соответственно первой 20 и второй 21 схем сравнения, на вторые входы которых поступают значения контрольных разрядов, сформированных в третьем 18 и четвертом к 19 кодирующих блоках.

9. В зависимости от значений выходных сигналов первой 20 и второй 21 схем сравнения, к выходам узла обмена подключаются выходы основного или дублирующего канала.

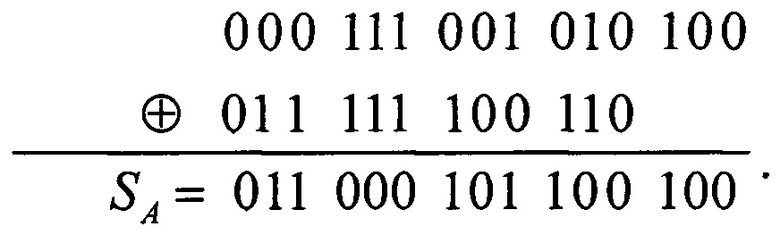

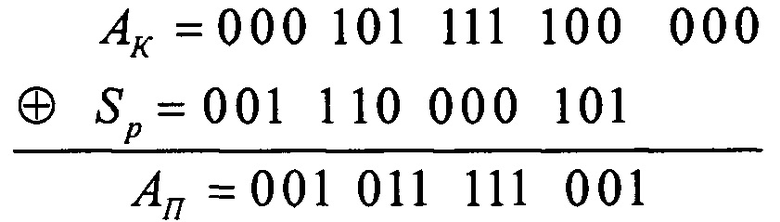

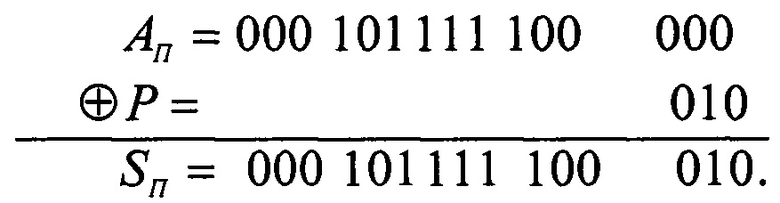

При сдвиге вправо кодового набора Ак=001 011 111 001 000 получим кодовый набор АП=000 101 111 100 000.

Значение функции сдвига вправо имеет вид: SP=001 110 000 101.

В результате поразрядного сложения в резервном блоке 9 сумматоров по mod 2 значений исходного кодового набора с значениями разрядов функции сдвига получим значения информационных разрядов при сдвиге вправо.

При кодировании функции сдвига с помощью предложенного метода значение поправки составит Р=010.

Сложение значений поправки с значениями контрольных разрядов приводит к правильному значению контрольных разрядов при сдвиге информационных разрядов вправо:

Контроль и формирование дублирующего канала для выполнения операции ИЛИ (И) основаны на том, что результат поразрядного суммирования по mod 2 результата выполнения логической операции И (ИЛИ) с результатом сложения по mod 2 исходных кодовых наборов определяет результат выполнения логической операции ИЛИ (И).

Формирование дублирующего канала для выполнения операции ИЛИ (И) реализует следующий алгоритм:

1. В блоке 12 элементов ИЛИ (блоке 11 элементов И) осуществляется выполнение логической операции ИЛИ относительно информационных разрядов;

2. Параллельно, в блоке 11 элементов И, относительно информационных разрядов осуществляется логическая операция И (ИЛИ);

3. В резервном блоке 10 сумматоров по mod 2 производится суммирование исходных кодовых наборов и суммирование по mod 2 контрольных разрядов;

4. Значения контрольных разрядов поступают на блок 22 суммирования поправки,

5. Значения информационных разрядов, полученных при выполнении логической операции И в блоке 11 элементов И, поступают на входы первого кодирующего блока 16 и на входы блока 9 сумматоров по mod 2 где суммируются с результатом, полученным на выходе резервного блока 10 сумматоров по mod 2 (результат сложения соответствует выполнению логической операции ИЛИ);

6. Полученный результат, поступает на вход четвертого кодирующего блока 19;

7. Значение поправки, поступающее с выходов первого кодирующего блока 16, поступающее на входы блока 22 суммирования поправки, обеспечивает формирование значений контрольных разрядов, соответствующих рассматриваемой логической операции ИЛИ, которые поступают на первые входы первой20 и второй 21 схем сравнения.

8. Первая 20 и вторая 21 схемами сравнения соответственно, осуществляют сравнение значений контрольных разрядов сформированных относительно основного и резервного каналов выполнения логической операции ИЛИ и выбора рабочего канала.

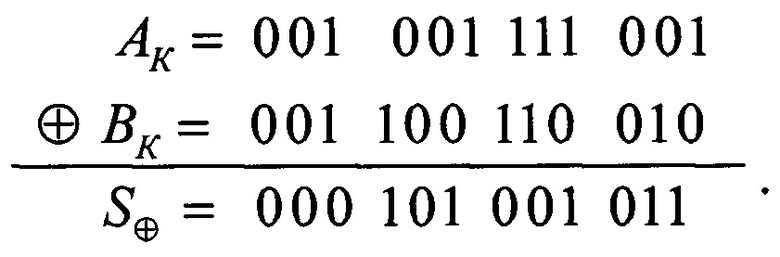

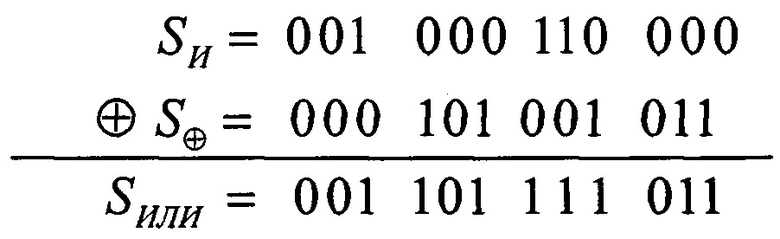

Для примера, рассматриваемого при организации контроля выполнения логической операции ИЛИ относительно двух 12-разрядных кодовых слов: Ак=001 001 111 001 110; Вк=001 100 110 010 101, при выполнении логической операции ИЛИ относительно информационных разрядов и суммирования по mod 2 контрольных разрядов получен результат: SИЛИ=001 101 111 011 011, у которого значения контрольных разрядов не соответствует полученному результату. Для формирования поправки к полученным значениям контрольных разрядов осуществляется выполнение логической операции И, обеспечивающей получение результата: SИ=001 000 110 000 на основе которого формируется значение поправки к значениям контрольных разрядов при выполнении логической операции ИЛИ: РИЛИ=001.

При сложении по mod 2 исходных кодовых наборов получим результат:

Суммирование по mod 2 информационных разрядов, полученных при выполнении логической операции И, с результатом сложения по mod 2 исходных кодовых наборов, позволяет получить результат выполнения логической операции ИЛИ:

В результате суммирования по mod 2 значения результата поправки РИЛИ=001 с значениями контрольных разрядов, сформированных при выполнении операции ИЛИ, получим значение контрольных соответствующее данной операции: SИЛИ. П=001101 111 011 010.

Таким образом предлагаемое изобретение позволяет обеспечить сокращение аппаратурных затрат на резервирование за счет использования для обнаружения ошибок в ЭВМ алгебраического линейного кода с минимальной избыточностью и использования результатов кодирования информации для формирования дублирующего канала за счет функциональной избыточности процессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| УСТРОЙСТВО ДИНАМИЧЕСКОГО ИЗМЕНЕНИЯ АДРЕСОВ ПАМЯТИ | 1993 |

|

RU2115160C1 |

| Устройство для вычисления контрольного кода | 1982 |

|

SU1101826A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для вычисления функции @ | 1986 |

|

SU1335987A2 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1332321A2 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

Изобретение относится к вычислительной технике. Технический результат – сокращение аппаратурных затрат на резервирование за счет использования для обнаружения ошибок ЭВМ алгебраического линейного кода с минимальной избыточностью. Отказоустойчивая ЭВМ использует алгебраический линейный код для обнаружения ошибок с минимальной информационной и аппаратурной избыточностью, который адаптирован для контроля арифметических и логических операций процессора. Для обеспечения отказоустойчивости ЭВМ осуществляется формирование дублирующего канала на основе использования результатов кодирования информации и функциональной избыточности процессора. 1 ил.

Отказоустойчивая ЭВМ, содержащая управляющий узел, узел обмена, первый запоминающий узел, арифметико-логический узел, блок регистров, сумматор, блок сумматоров по mod 2, блок элементов И, блок элементов ИЛИ, отличающаяся тем, что дополнительно содержит второй запоминающий узел, первый кодирующий блок, второй кодирующий блок, третий кодирующий блок, четвертый кодирующий блок, коммутатор, первую схему сравнения, вторую схему сравнения, резервный блок сумматоров по mod 2, блок формирования функции переносов, блок формирования функции сдвига, резервный регистр сдвига, причем первые входы узла обмена являются входами ЭВМ, первые выходы узла обмена являются выходами ЭВМ, вторые выходы узла обмена подключены к входам коммутатора, к входам первого кодирующего блока, к первым входам первого запоминающего узла, к первым входам второго запоминающего узла, к первому и второму входам блока суммирования поправки, к входам управляющего узла, третий выход узла обмена подключен к первым входам блока регистров, к первым входам резервного регистра сдвига, к первым входам сумматора, к первым входам блока сумматоров по mod 2, к первым входам резервного блока сумматоров по mod 2, к первым входам блока элементов И, к первым входам блока элементов ИЛИ, к первым входам блока формирования функции переносов, к первым входам блока формирования функции сдвига, выход управляющего узла подключен к вторым входам первого и второго запоминающих узлов, к вторым входам блока регистров, к вторым входам резервного регистра сдвига, к вторым входам сумматора, к вторым входам блока сумматоров по mod 2, к вторым входам резервного блока сумматоров по mod 2, к вторым входам блока элементов И, к вторым входам блока элементов ИЛИ, к вторым входам блока формирования функции переносов, к вторым входам блока формирования функции сдвига, к вторым входам коммутатора, к вторым входам узла обмена, выходы первого кодирующего блока подключены к третьим входам узла обмена и третьим входам первого запоминающего узла, выходы которого подключены к третьим входа коммутатора, выходы второго кодирующего блока подключены к третьим входам второго запоминающего узла, выходы которого подключены к четвертым входам коммутатора, выходы блока суммирования поправки подключены к пятым входам коммутатора, первые выходы которого подключены к четвертым входам узла обмена и к входам третьего кодирующего блока, а вторые входы подключены к первым входам первой схемы сравнения, третьи выходы коммутатора подключены к пятым входам узла обмена и к входам четвертого кодирующего блока, а четвертые выходы подключены к первым входам второй схемы сравнения, выходы третьего кодирующего блока подключены к вторым входам первой схемы сравнения, выходы четвертого кодирующего блока подключены к вторым входам второй схемы сравнения, выходы первой и второй схем сравнения подключены к шестым входам узла обмена, выходы блока регистров, резервного регистра сдвига, сумматора, блока сумматоров по mod 2, резервного блока сумматоров по mod 2, блока элементов И, блока элементов ИЛИ, блока формирования функции переносов, блока формирования функции сдвига подключены к седьмым входам узла обмена, первый кодирующий блок, в зависимости от команд, поступающих с выходов управляющего узла на узел обмена, формирует значения контрольных разрядов относительно информационных символов yiЗУ1, поступающих с выходов узла обмена в первый запоминающий узел, или значения разрядов поправки относительно информационных символов yiФП функции переносов, или значения разрядов поправки относительно информационных символов уiФС функции сдвига, или значения разрядов поправки относительно информационных символов yiИ при выполнении логической операции ИЛИ, или значения разрядов поправки относительно информационных символов yiИЛИ при выполнении логической операции И, на своем первом r1, втором r2 и третьем r3 выходе путем сложения по модулю 2 информационных символов y1i j, y2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1 = y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r2 = y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3 = y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j, ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j, второй кодирующий блок, в зависимости от команд, поступающих с выходов управляющего узла на узел обмена, формирует значения контрольных разрядов относительно информационных символов yiЗУ2, поступающих с выходов узла обмена в второй запоминающий узел на своем первом r12, втором r22 и третьем r32 выходе путем сложения по модулю 2 информационных символов y1ЗУ2, y2ЗУ2, y3ЗУ2, y4ЗУ2, y5ЗУ2, y6ЗУ2, y7ЗУ2, y8ЗУ2, y9ЗУ2, y10ЗУ2, y11ЗУ2, y12ЗУ2 в соответствии с правилом: r12 = y3ЗУ2 ⊕ y5ЗУ2 ⊕ y7ЗУ2 ⊕ y8ЗУ2, ⊕ y9ЗУ2 ⊕ y10ЗУ2 ⊕ y11ЗУ2, r22 = y2ЗУ2 ⊕ y4ЗУ2 ⊕ y5ЗУ2 ⊕ y8ЗУ2, ⊕ y9ЗУ2 ⊕ y10ЗУ2 ⊕ y11ЗУ2, r32 = y1ЗУ2 ⊕ y4ЗУ2 ⊕ y5ЗУ2 ⊕ y6ЗУ2, ⊕ y7ЗУ2 ⊕ y10ЗУ2 ⊕ y11ЗУ2 ⊕ y12ЗУ2, третий кодирующий блок, в зависимости от команд, поступающих с выходов управляющего узла на входы коммутатора, формирует значения контрольных разрядов относительно информационных символов yiЗУ1, считываемых с первого запоминающего узла, или значения разрядов суммы y1АУ, поступающих с выходов сумматора, или информационных разрядов yim, поступающих с выходов блока сумматоров по mod 2, или значений информационных разрядов yiИ, поступающих с выходов блока элементов И, или значений информационных разрядов yiИЛИ, поступающих с выходов блока элементов ИЛИ, или значений информационных разрядов yiC, поступающих с выходов блока регистров на своем первом r1ф1, втором r2ф1 и третьем r3ф1 выходе путем сложения по модулю 2 информационных символов y1i j, y2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1ф1 = y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r2ф1 = y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3ф1 = y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j, ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j, четвертый кодирующий блок, в зависимости от команд, поступающих с выходов управляющего узла на входы коммутатора, формирует значения контрольных разрядов относительно информационных символов yiЗУ2, считываемых с второго запоминающего узла, или значения разрядов суммы yim, поступающих с выходов блока сумматоров по mod 2 при выполнении арифметической операции, или информационных разрядов yimp, поступающих с выходов резервного блока сумматоров по mod 2 при выполнении логической операции суммирования по mod2, или значений информационных разрядов yimИ, поступающих с выходов блока сумматоров по mod 2 при выполнении логической операции И, или значений информационных разрядов yimИЛИ, поступающих с выходов блока сумматоров по mod 2, при выполнении логической операции ИЛИ, или значений информационных разрядов yimc при выполнении операции сдвига, поступающих с выходов резервного блока сумматоров по mod 2 на своем первом r1ф2, втором r2ф2 и третьем r3ф2 выходе путем сложения по модулю 2 информационных символов y1i j, y2i j, y3i j, y4i j, y5i j, y6i j, y7i j, y8i j, y9i j, y10i j, y11i j, y12i j в соответствии с правилом: r1ф2 = y3i j ⊕ y5i j ⊕ y7i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r2ф2 = y2i j ⊕ y4i j ⊕ y5i j ⊕ y8i j, ⊕ y9i j ⊕ y10i j ⊕ y11i j, r3ф2 = y1i j ⊕ y4i j ⊕ y5i j ⊕ y6i j, ⊕ y7i j ⊕ y10i j ⊕ y11i j ⊕ y12i j блок 13 формирования функции переносов формирует значение функции переносов относительно значений информационных разрядов слагаемых yiA и yiB в соответствии с правилом: s1=0, s2=y1A^y1B, s3=y2A^y2B v (y2А v y2B) ^ s2, s4=y3A^y3B v (y3A v y3B) ^ s3, s5=y4A^y4B v (y4A v y4B) ^ s4, s6=y5A^y5B v (y5A v y5B) ^ s5, s7=y6A^y6B v (y6A v у6В) ^ s5, s8=y7A^y7B v (y7A v y7B) ^ s7, s9=y8A^y8B v (y8A v y8B) ^ s8, s10=y9A^y9B v (y9A v y9B) ^ s9, s11=y10A^y10B v (y10A v y10B) ^ s10, s12=y11A^y11B v (y11A v y11B) ^ s11, блок формирования функции сдвига формирует значение функции сдвига вправо относительно исходных значений информационных разрядов yi регистра сдвига в соответствии с правилом: s12=y12, s11=y12⊕y11, s10=y11⊕y10, s9=y10⊕y9, s8=y9⊕y8, s7=y8⊕y7, s6=y7⊕y6, s5=y6⊕y5, s4=y5⊕y4, s3=y4⊕y3, s2=y3⊕y2, s1=y2⊕y1 и значение функции сдвига влево в соответствии с правилом: s1=y1, s2=y1⊕y2, s3=y2⊕y3, s4=y3⊕y4, s5=y4⊕y5, s6=y5⊕y6, s7=y6⊕y7, s8=y7⊕y8, s9=y8⊕y9, s10=y9⊕y10, s11=y10⊕y9, s12=y11⊕y12.

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Прибор для опробования нефтяных пластов в буровых скважинах | 1934 |

|

SU51428A1 |

| US 6654909 B1, 25.11.2003 | |||

| US 7979783 B2, 12.07.2011. | |||

Авторы

Даты

2019-10-29—Публикация

2018-10-16—Подача