Изобретение относится к области вычислительной техники и предназначено для повышения достоверности функционирования ЭВМ, за счет обнаружения 100% одиночных ошибок и максимального количества двойных ошибок при минимальных временных и аппаратурных затратах.

Известен процессор (Калабеков Б.А, Микропроцессоры и их применение в системах передачи и обработки сигналов, М.: Радио и связь, 1988, 368 с. (стр. 30, рис. 1.3)), содержащий управляющий узел, операционный узел, первая группа входов управляющего узла является входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы, которого являются входами данных, а вторые выходы являются выходами данных.

Недостатком устройства является низкая достоверность функционирования процессора, так как не обеспечивается обнаружение ошибок при выполнении арифметических и логических операций - преобразователей информации сумматора, регистров сдвига, устройств выполнения логических операций.

Наиболее близким по техническому решению является процессор повышенной достоверности функционирования по патенту №2439667 от 2012 г., содержащий управляющий узел, операционный узел, дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок контроля, управляющую память, блок логических операций и контроля, включающий блок логического сложения по mod2, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И, первые входы управляющего узла является входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы которого являются входами данных, а вторые выходы являются выходами данных, выходы устройства обмена подключены к первому входу блока управления и к первому входу второго коммутатора, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика команд, счетчика сдвигов, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к входам дешифратора кода операции, к вторым входам блока управления, к первому входу первого коммутатора, первый выход которого подключен к первому входу регистра адреса, третий вход блока управления подключен к выходам дешифратора кода операции а четвертый вход подключен к выходам генератора тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти, первый выход блока управления подключен к входу управляющей памяти, первые выходы которой подключены к первым входам блока контроля, второй выход блока управления подключен к второму входу первого коммутатора, третьи и четвертые входы которого подключены соответственно к выходам регистра адреса и счетчика команд, а с второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока управления подключен соответственно к вторым входам блока контроля, к вторым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и является выходом синхроимпульсов, второй, третий, четвертый пятый выходы управляющей памяти подключены к третьим и четвертым пятым и шестым входам блока контроля при этом второй выход подключен к четвертому входу второго коммутатора, а третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым пятым и шестым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и являются выходам управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, шестой выход блока управляющей памяти подключен к пятому входу блока управления, выходы регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода подключены к вторым входам третьего коммутатора и к пятым входам второго коммутатора, выход счетчика сдвигов подключен к шестым входам второго коммутатора, первые выходы третьего коммутатора подключены соответственно к входам сумматора и к вторым входам блока логических операций и контроля, выходы сумматора подключены к третьим входам блока логических операций и контроля, вторые, третьи, четвертые, пятые, шестые и седьмые выходы третьего коммутатора подключены к четвертым, пятым, шестым, седьмым, восьмым и девятым входам блока логических операций и контроля, выходы которого подключены к седьмым, восьмым и девятым входам второго коммутатора.

Недостатком устройства является низкая обнаруживающая способность двойных ошибок при выполнении арифметических и логических операций.

Задачей изобретения является повышение обнаруживающей способности двойных ошибок в работе процессора встроенными средствами контроля при выполнении арифметических и логических операций.

Сущность изобретения заключается в том, что в процессоре повышенной достоверности функционирования, содержащем управляющий узел, операционный узел, дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок контроля, управляющую память, первый блок кодирования, второй блок кодирования, блок логических операций и контроля, включающий блок логического сложения по mod2, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, элемент задержки, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И, первые входы управляющего узла является входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы которого являются входами данных, а вторые выходы являются выходами данных, выходы устройства обмена подключены к первому входу блока управления и к первому входу второго коммутатора, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика команд, счетчика сдвигов, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к входам дешифратора кода операции, к вторым входам блока управления, к первому входу первого коммутатора, первый выход которого подключен к первому входу регистра адреса, третий вход блока управления подключен к выходам дешифратора кода операции, а четвертый вход подключен к выходам генератора тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти, первый выход блока управления подключен к входу управляющей памяти, первые выходы которой подключены к первым входам блока контроля, второй выход блока управления подключен к второму входу первого коммутатора, третьи и четвертые входы которого подключены соответственно к выходам регистра адреса и счетчика команд, а с второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока управления подключен соответственно к вторым входам блока контроля, к вторым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и является выходом синхроимпульсов, второй, третий, четвертый пятый выходы управляющей памяти подключены к третьим и четвертым пятым и шестым входам блока контроля при этом второй выход подключен к четвертому входу второго коммутатора, а третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым пятым и шестым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к второй группе входов блока логических операций и контроля и являются выходам управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, сигналов сдвига, шестой выход блока управляющей памяти подключен к пятому входу блока управления, выходы регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода подключены к вторым входам третьего коммутатора и к пятым входам второго коммутатора, выход счетчика сдвигов подключен к шестым входам второго коммутатора, первые выходы третьего коммутатора подключены соответственно к входам сумматора и к третьим входам блока логических операций и контроля, выходы сумматора подключены к четвертым входам блока логических операций и контроля, вторые, третьи, четвертые, пятые, шестые и седьмые выходы третьего коммутатора подключены к пятым, шестым, седьмым, восьмым, девятым и десятым входам блока логических операций и контроля, первые выходы блока логических операций и контроля подключены к входам первого блока кодирования, первый и второй выходы первого блока кодирования подключены соответственно к двенадцатому и тринадцатому входам блока логических операций и контроля, вторые выходы блока логических операций и контроля подключены к входам второго блока кодирования, первый и второй выходы второго блока кодирования подключены соответственно к четырнадцатому и пятнадцатому входам блока логических операций и контроля, третий, четвертый и пятый выходы блока логических операций и контроля подключены к входам второго коммутатора.

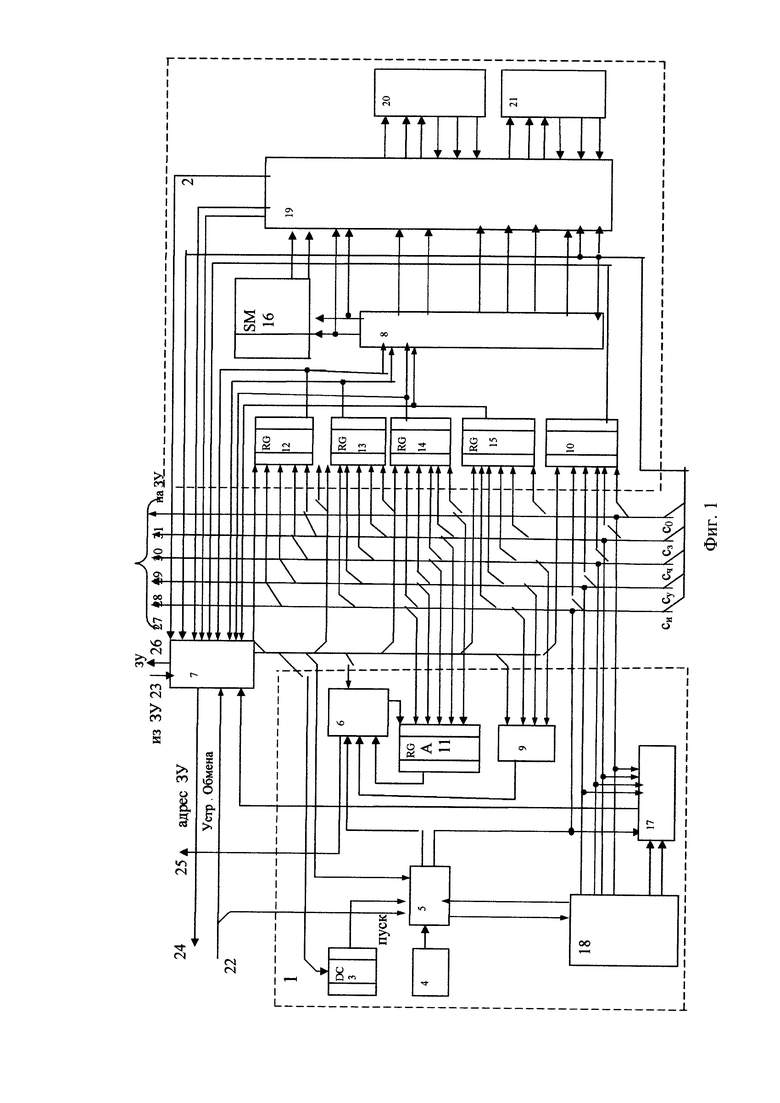

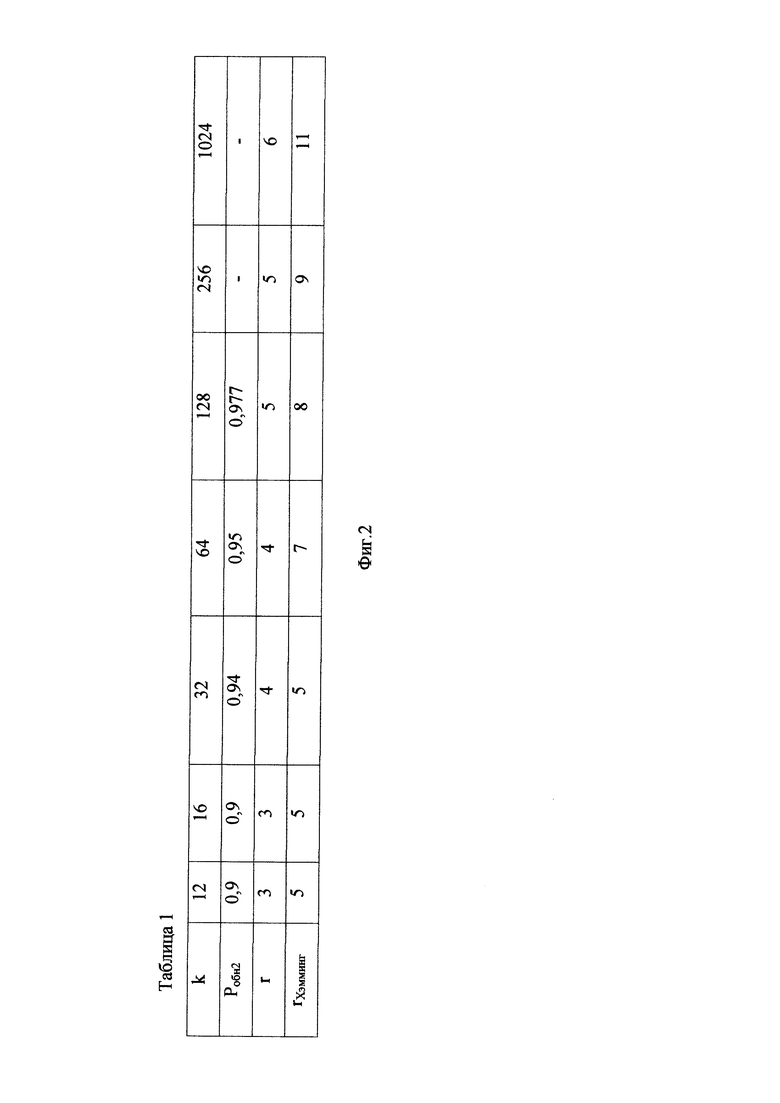

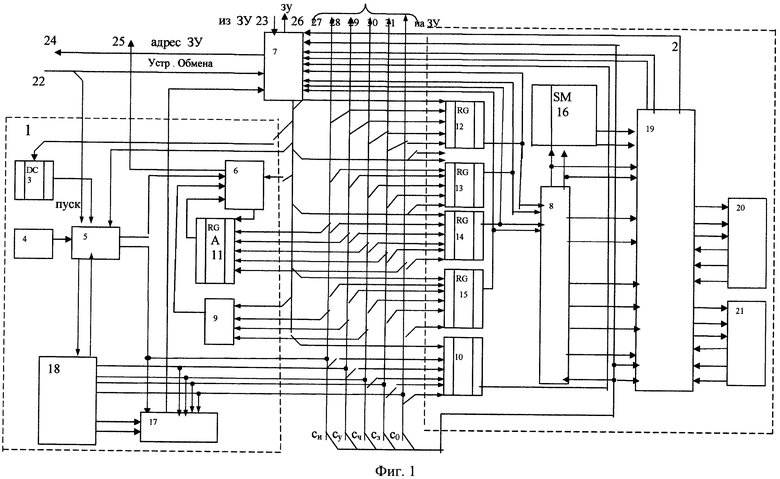

На фиг. 1 представлена блок-схема устройства, на фиг. 2 - таблица 1, где представлены сравнительные характеристики предлагаемого кода.

В процессоре повышенной достоверности функционирования первый и второй блоки кодирования содержат по третьему выходу, причем первый блок 20 кодирования формирует значения разрядов поправки на своем первом p1, втором р2 и третьем р3 выходе путем сложения по модулю 2 информационных символов s1, s2, s3, s4, s5, s6, s7, s8, s9, s10, s11, s12, поступающих с первых выходов блока 19 логических операций и контроля на входы первого блока кодирования, в соответствии с правилом: p1=s3 ⊕ s6 ⊕ s7 ⊕ s8 ⊕ s9 ⊕ s10 ⊕ s11, р2=s2 ⊕ s4 ⊕ s5 ⊕ s8 ⊕ s9 ⊕ s10 ⊕ s11, р3=s1 ⊕ s4 ⊕ s5 ⊕ s6 ⊕ s7 ⊕ s10 ⊕ s11 ⊕ s12, первый, второй выходы первого блока 20 кодирования подключены соответственно к двенадцатому и тринадцатому входам блока 19 логических операций и контроля, а третий выход подключен к шестнадцатому входу блока 19 логических операций и контроля, второй блок 21 кодирования, формирующий значения проверочных контрольных разрядов на первом r1C, втором r2C и третьем r3C выходах путем сложения по модулю 2 значений информационных символов y1C, y2C, y3C, y4C, y5C, y9C, y7C, y8C, у9С, y10C, y11C, y12C, полученных при выполнении арифметических и логических операций и поступающих со вторых выходов блока 19 логических операций и контроля на входы второго блока кодирования в соответствии с правилом: r1C=y3C ⊕ y6C ⊕ y7C ⊕ y8C ⊕ y9C ⊕ y10C ⊕ y11C, r2C=y2C ⊕ y4C ⊕ y5C ⊕ y8C ⊕ y9C ⊕ y10C ⊕ y11C, r3C=y1C ⊕ y4C ⊕ y5C ⊕ y6C ⊕ y7C ⊕ y10C ⊕ y11C ⊕ y12C, первый и второй выходы второго блока 21 кодирования подключены соответственно к четырнадцатому и пятнадцатому входам блока 19 логических операций и контроля, а третий выход подключен к семнадцатому входу блока 19 логических операций и контроля.

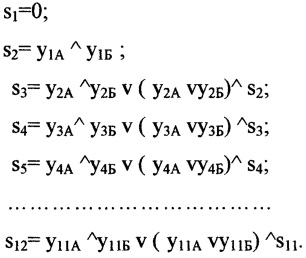

Работа схемы формирования поправки при выполнении арифметических операций аналогична работе схемы формирования поправки при выполнении арифметических операций прототипа и формирует значения переносов по правилу:

Так, при выполнении арифметических операций, результат суммы с выхода сумматора 16, поступает на второй вход блока 19 логических операций и контроля. Одновременно значения информационных разрядов слагаемых поступают на четвертый вход блока 19 логических операций и контроля при этом, схема формирования поправки при выполнении арифметических операций формирует вектор переносов s1, s2…s12.

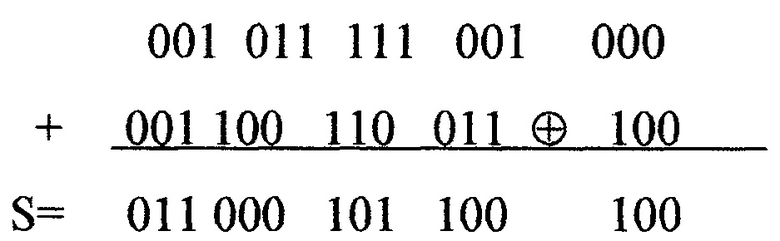

Требуется сложить два числа, содержащих по 12 информационных разрядов:

АК=001 011 111 001 000, ВК=001 100 110 011 100.

Номера разрядов проставлены справа налево, начиная с первого по двенадцатый не считая контрольные разряды.

Сложение по mod 2 значений контрольных разрядов первым блоком элементов неравнозначности и арифметическое суммирование значений информационных разрядов сумматором 16, с учетом переносов, даст результат:

При сложении информационных разрядов перенос единичных значений сигналов осуществляется во второй, третий, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый разряды.

В результате на выходе схемы формирования поправки при выполнении арифметических операций получаем значения разрядов переносов: SП=011 111 100 110, которые через первый блок 61 элементов ИЛИ поступают на вход первого блока 20 кодирования.

Первый блок 20 кодирования формирует значения разрядов поправки на своем первом p1, втором р2 и третьем р3 выходе путем сложения по модулю 2 информационных символов s1, s2, s3, s4, s5, s6, s7, s8, s9, s10, s11, s12, поступающих с первых выходов блока 19 логических операций и контроля, в соответствии с правилом: p1=s3 ⊕ s6 ⊕ s7 ⊕ s8 ⊕ s9 ⊕ s10 ⊕ s11 , р2=s2 ⊕ s4 ⊕ s5 ⊕ s8 ⊕ s9 ⊕ s10 ⊕ s11, р3=s1 ⊕ s4 ⊕ s5 ⊕ s6 ⊕ s7 ⊕ s10 ⊕ s11 ⊕ s12

- разряды переносов пронумерованы слева направо.

Кодирование значений переносов предлагаемым кодом даст значение поправки Рк=110.

Поразрядное сложение по mod2 вторым блоком элементов неравнозначности значения поправки Рк=110 и значения Sk mod2=100, полученного на выходе первого блока элементов неравнозначности и даст правильное значение контрольных разрядов для полученной арифметической суммы: Sк=011 000 101 100 010.

Второй блок 21 кодирования формирует значения проверочных контрольных разрядов на первом r1C, втором r2C и третьем r3C выходах путем сложения по модулю 2 значений информационных символов y1C, у2, y3C, y4C, y5C, y9C, y7C, y8C, у9С, y10C, y11C, y12C, полученных при выполнении арифметической операции (результата суммы S=011 000 101 100) в соответствии с правилом: r1C= y3C ⊕ y6C ⊕ y7C ⊕ y8C ⊕ y9C ⊕ y10C ⊕ y11C, r2C=y2C ⊕ y4C ⊕ y5C ⊕ y8C ⊕ y9C ⊕ y10C ⊕ y11C ⊕ y12C, r3C=y1C ⊕ y4C ⊕ y5C ⊕ y6C ⊕ y7C ⊕ y10C ⊕ y11C ⊕ y12C. В результате получим значения проверочных разрядов: r1C=0; r2C=1; r3C=0.

Сравнение контрольных разрядов сформированных относительно результата суммирования вторым блоком 21 кодирования с значением переданных контрольных разрядов с учетом поправки третьим блоком элементов неравнозначности даст нулевой результат, что свидетельствует об отсутствии ошибки. При контроле операции сдвига вправо, схема формирования поправки при выполнении операции сдвига формирует относительно исходной информации значения разрядов для вычисления поправки в соответствии с выражениями:

s12=z1⊕y12; s11=y12⊕y11; s10=y11⊕y10; s9=y10⊕y9; s8=y9⊕y8; s7=y8⊕y7; s6=y7⊕y6; s5=y6⊕y5; s4=y5⊕y4; s3=y4⊕y3; s2=y3⊕y2; s1=y2⊕y1.

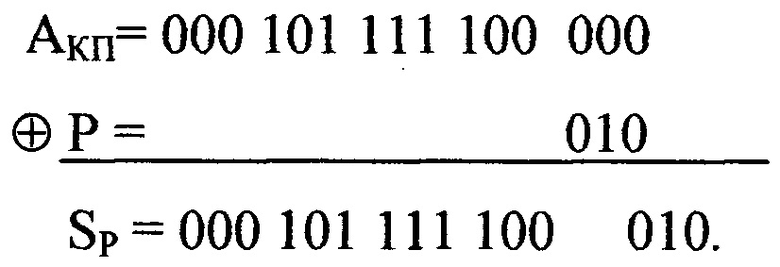

При сдвиге вправо, при отсутствии переноса из другого регистра АК=001 011 111 001 000 получим двоичный набор для получения поправки Р равный: SP=001 110 000 101.

При кодировании данного набора первым блоком 20 кодирования получим значение поправки Р=010.

Сложение по mod2 вторым блоком элементов неравнозначности значений контрольных разрядов с значением поправки даст правильное значение контрольных разрядов при сдвиге информационных разрядов вправо:

Второй блок 21 кодирования формирует значения контрольных разрядов относительно информации, полученной при сдвиге вправо.

Третьим блоком элементов неравнозначности осуществляется сравнение значений контрольных разрядов полученных при операции сдвига информации вправо и сформированных значений контрольных разрядов с учетом поправки относительно исходной информации.

Значение символов для формирования поправки при сдвиге влево, формируются на основе исходного значения информационных разрядов следующим образом: s1=z1⊕y1; s2=y1⊕y2; s3=y2⊕y3; xs4=y3⊕y4; s5=y4⊕y5; s6=y5⊕y6; s7=y6⊕y7; s8=y7⊕y8; s9=y8⊕y9; s10=y9⊕y10; s11=y10⊕y11; s12=y11⊕y12.

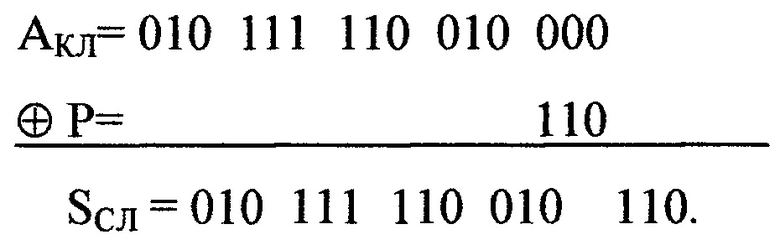

При проведении операции сдвига влево, при отсутствии переноса из другого регистра, на один разряд для двоичного набора АК=001 011 111 001 000, получаем кодовый набор: АКЛ=010 111 110 010 000, у которого значение контрольных разрядов не соответствует полученному результату, значению контрольных разрядов равного 110.

Информация на выходе схемы формирования поправки при выполнении операции сдвига имеет вид: SL=011 100 001 010. При кодировании данного набора первым блоком 20 кодирования получим значение поправки Р=110.

Сложение по mod2 вторым блоком элементов неравнозначности исходного значения контрольных разрядов с значением поправки даст правильное значение контрольных разрядов при сдвиге информационных разрядов влево:

Второй блок 21 кодирования формирует значения контрольных разрядов относительно информации, полученной при сдвиге влево.

Третьим блоком элементов неравнозначности осуществляется сравнение значений контрольных разрядов, полученных при операции сдвига информации влево и сформированных значений контрольных разрядов с учетом значения поправки относительно исходной информации.

При выполнении логического сложения, значение вектора для вычисления поправки к контрольным разрядам осуществляется схемой формирования поправки при выполнении операции ИЛИ, путем выполнения операции И относительно одноименных разрядов слагаемых.

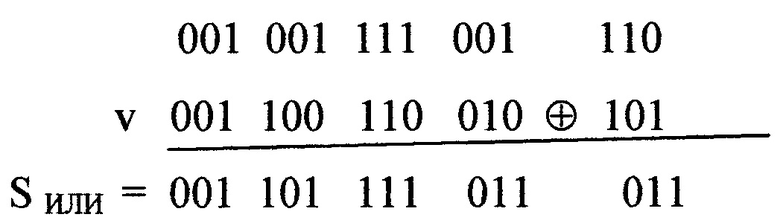

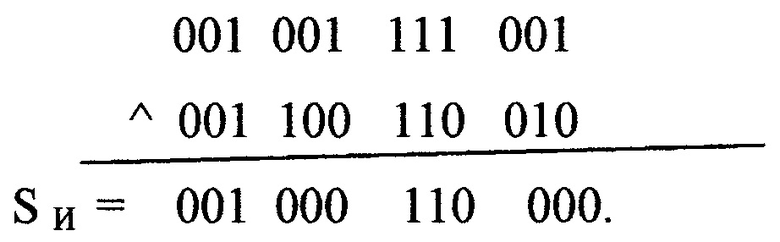

Так, например, при выполнении операции ИЛИ относительно информационных разрядов и сложения по mod2 контрольных разрядов первым блоком элементов неравнозначности чисел АК=001 001 111 001 110 и ВК=001 100 110 010 101.

Логическое сложение информационных разрядов кодовых наборов и сложение по mod 2 контрольных разрядов даст результат:

В данном случае полученное значение контрольных разрядов 011 не соответствует требуемому значению контрольных разрядов: 010.

Функциональная схема формирования поправки при выполнении операции ИЛИ выполняет логическую операцию И относительно информационных разрядов рассматриваемых чисел, в результате получим кодовый набор:

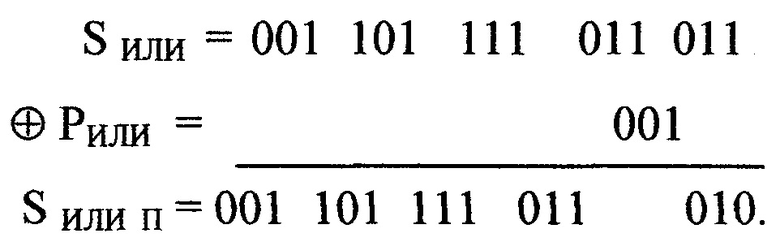

Кодирование полученного двоичного набора первым блоком 20 кодирования даст значения поправки к контрольным разрядам при выполнении операции ИЛИ: РИЛИ=001.

Сложение по mod2 полученного значения контрольных разрядов с значением поправки даст правильное значение контрольных разрядов для рассматриваемого примера.

Аналогичным образом формируется поправка при выполнении логического умножения, только при формировании вектора поправки схемой формирования поправки при выполнении операции И, реализуется поразрядная операция ИЛИ относительно одноименных разрядов множимого и множителя. Для операций сложения по mod2 блоком сложения по mod2 формирование поправки к контрольным разрядам не требуется.

Значения контрольных разрядов, сформированные вторым блоком кодирования относительно информационных разрядов, полученных при выполнении арифметических и логических операций, поразрядно сравниваются третьим блоком элементов неравнозначности с переданными значениями контрольными разрядами с учетом поправки. При отсутствии ошибок на его выходах получаем нулевое значение сигналов.

Работа процессора начинается с приходом сигнала "Пуск" по входной группе 22 входов устройства обмена процессора с периферийными блоками. По этой команде блок 5 выдает команду на считывание с управляющей памяти 18 содержимого первой ячейки памяти.

В первой ячейке памяти расположена команда "Сброс системы", которая устанавливает в исходное состояние регистры и блоки процессора, В счетчик 9 команд записывается "1", устройство управления 1 выдает микрокоманды в следующей последовательности:

1) На первом такте сигналы микрокоманды и значения контрольных разрядов поступают на выход блока 17 контроля, где проводится обнаружение и коррекция возникающих ошибок.

В этом случае, при считывании микрокоманды, кодирующей схемой блока 17 контроля проводится формирование контрольных разрядов принятого кодового набора.

Схемой обнаружения ошибки блока 17 контроля производится поразрядное сравнения сформированных и переданных значений контрольных разрядов.

В случае возникновения ошибок, на выходе блока 17 контроля, появится единичный сигнал, свидетельствующий о ее наличии, который при поступлении синхроимпульса через второй коммутатор 7 поступает на устройство обмена.

Если ошибок нет, набор микрокоманд поступает на вход считывания счетчика 9 команд и на вход записи регистра 11 адреса, при этом содержимое счетчика 9 команд пересылается в регистр 11 адреса или через первый коммутатор 6 на адресные входы запоминающего устройства при естественной выборке команд непосредственно со счетчика 9 команд;

2) На втором такте к содержимому счетчика 9 команд прибавляется единица - подготавливается адрес следующей команды;

3) На третьем такте сигналы микрокоманды поступают на вход считывания регистра 11 адреса и на вход считывания содержимого ячейки памяти запоминающего устройства по указанному адресу. При этом команда, хранящаяся в первой ячейке памяти, записывается в регистр 12 числа;

4) На четвертом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа, вход второго коммутатора 7 и на вход дешифратора 3 кода операции, где раскодируются, после чего управляющий узел 1 переходит ко второму этапу работы.

Для примера рассмотрим порядок исполнения одной из команд, записанной в регистре 12 числа после выполнения первых четырех тактов.

Пусть в поле кода операции команды содержимого регистра 12 числа записана команда сложения содержимого регистра 13 сумматора с числом расположенным запоминающем устройстве по адресу, указанному в поле адреса регистра 12 числа, при использовании одноадресной команды. Управляющий узел 1 при этом выдает следующие микрокоманды:

5) на пятом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа, на вход второго коммутатора 7, первого коммутатора 6 и на вход записи регистра 11 адреса при этом адрес, хранящийся в регистре 12 числа записывается в регистр 11 адреса, содержимое регистра 12 числа обнуляется;

6) На шестом такте сигналы микрокоманды подаются на вход считывания регистра 11 адреса, на вход первого коммутатора 6, на вход считывания запоминающего устройства и на вход записи регистра 12 числа, в этом случае из запоминающего устройства в регистр 12 числа записывается второе слагаемое при этом полагаем, что первое слагаемое уже находится в регистре 13 сумматора;

7) На седьмом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа и регистра 13 сумматора, при этом арифметико-логическое устройство осуществляет операцию сложения и запись результата сложения в регистр 13 сумматора следующим образом.

Результат суммы с выхода сумматора 16, поступает на блок 19 логических операций и контроля, далее устройство работает в соответствии с примером выполнения арифметических операций, приведенном выше. При этом сформированные значения контрольных разрядов относительно полученной операции сравниваются с переданными значениями контрольных разрядов в блоке 19 логических операций и контроля. При отсутствии ошибки на его выходах имеем нулевые значения сигналов. При наличии ошибки на выходе блока 19 логических операций и контроля появится единичное значение сигнала.

Аналогичным образом процессор функционирует при выполнении логических операций.

8) На восьмом такте выдается микрокоманда "Конец операций" осуществляется переход на следующую операцию, блок 5 управления приводится в исходное состояние и выдает разрешение на начало выполнения следующей команды, адрес которой указан в счетчике 9 команд.

Алгебраический линейный код, используемый в предлагаемом изобретении, имеет большую обнаруживающую способность двойных ошибок по отношению к коду, используемому в прототипе.

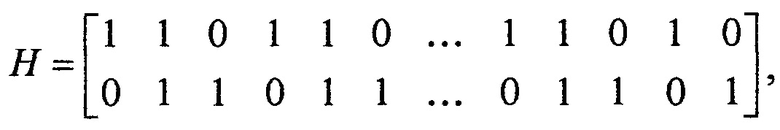

В прототипе изобретения представлен алгебраический линейный код с двумя контрольными разрядами, проверочная матрица которого имеет вид:

где два последних столбца соответствуют контрольным разрядам.

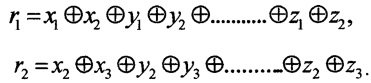

В аналитическом виде, значений двух контрольных разрядов формируется по правилу:

.

.

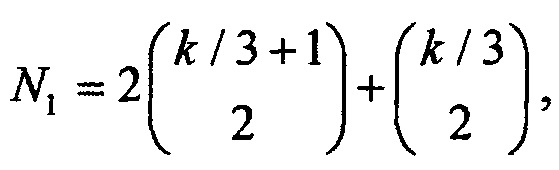

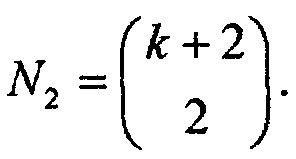

Число N1- не обнаруживаемых двойных ошибок кодом равно:  где k - число информационных разрядов.

где k - число информационных разрядов.

Общее число двойных ошибок N2 равно:  Следовательно, процент обнаруживаемых двойных ошибок равен

Следовательно, процент обнаруживаемых двойных ошибок равен

Представленный линейный код обнаруживает 100% одиночных ошибок и, в зависимости от числа информационных разрядов, следующий процент двойных ошибок: в шестиразрядном двоичном коде - PO6=75%, для девятиразрядного двоичного кода - PO9=74,5%, для двенадцатиразрядного - PO12=74%, пятнадцатиразрядного - PO15=73%, восемнадцатиразрядного - PO18=72%, двадцатиодногоразрядного -PO21=70%, для двадцатичетырехразрядного - PO24=69,5%, для двадцатисемиразрядного - PO27=69%„ для шестидесятиразрядного -PO60=67%.

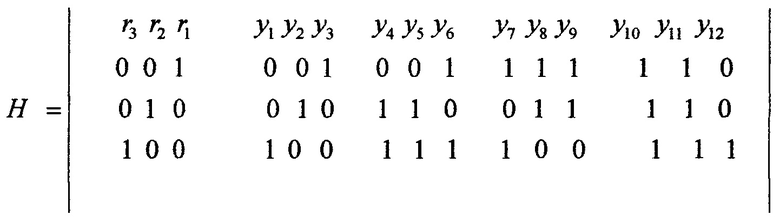

Проверочная матрица H для предлагаемого кода имеет вид:

Проверки для формирования значений контрольных разрядов определяются выражением:

r1=y3 ⊕ y6 ⊕ y7 ⊕ y8 ⊕ y9 ⊕ y10 ⊕ y11;

r2=y2 ⊕ y4 ⊕ y5 ⊕ y8 ⊕ y9 ⊕ y10 ⊕ y11;

r3=y1 ⊕ y4 ⊕ y5 ⊕ y6 ⊕ y7 ⊕ y10 ⊕ y11 ⊕ y12.

на фигуре 2 представлены сравнительные обнаруживающие способности двойных ошибок (Робн2) предлагаемого кода с кодом Хэмминга, алгебраического линейного кода с кодовым расстоянием d=3, обнаруживающим 100% двойных ошибок, в зависимости от числа информационных разрядов- k (проверочных разрядов-r).

Рассматриваемый код, по сравнению с кодом используемым в прототипе, имеет большую обнаруживающую способность, а по отношению к линейному коду с кодовым расстоянием d=3, при незначительном снижении вероятности обнаружения двойных ошибок, код имеет меньше проверочных разрядов, меньше аппаратурных затрат на построение кодирующего и декодирующего устройства, а также меньше аппаратурных затрат, связанных с хранение значений проверочных разрядов, что позволяет обеспечить выигрыш в достоверности функционирования контролируемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ОТКАЗОУСТОЙЧИВАЯ ЭВМ | 2018 |

|

RU2704325C1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2211492C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

Изобретение относится к области вычислительной техники. Технический результат заключается в повышении обнаруживающей способности двойных ошибок в работе процессора. Технический результат достигается за счет процессора повышенной достоверности функционирования, первый и второй блоки кодирования которого дополнительно содержат по третьему выходу, причем первый блок кодирования формирует значения разрядов поправки на своем первом, втором и третьем выходе путем сложения по модулю 2 информационных символов, поступающих с первых выходов блока логических операций и контроля на входы первого блока кодирования, второй блок кодирования, формирует значения проверочных контрольных разрядов на первом, втором и третьем выходах путем сложения по модулю 2 значений информационных символов, полученных при выполнении арифметических и логических операций и поступающих со вторых выходов блока логических операции и контроля на входы второго блока кодирования. 2 ил.

Процессор повышенной достоверности функционирования, содержащий управляющий узел, операционный узел, дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок контроля, управляющую память, первый блок кодирования, второй блок кодирования, блок логических операций и контроля, включающий блок логического сложения по mod2, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И, первые входы управляющего узла является входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы которого являются входами данных, а вторые выходы являются выходами данных, выходы устройства обмена подключены к первому входу блока управления и к первому входу второго коммутатора, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика команд, счетчика сдвигов, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к входам дешифратора кода операции, к вторым входам блока управления, к первому входу первого коммутатора, первый выход которого подключен к первому входу регистра адреса, третий вход блока управления подключен к выходам дешифратора кода операции, а четвертый вход подключен к выходам генератора тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти, первый выход блока управления подключен к входу управляющей памяти, первые выходы которой подключены к первым входам блока контроля, второй выход блока управления подключен к второму входу первого коммутатора, третьи и четвертые входы которого подключены соответственно к выходам регистра адреса и счетчика команд, а с второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока управления подключен соответственно к вторым входам блока контроля, к вторым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и является выходом синхроимпульсов, второй, третий, четвертый пятый выходы управляющей памяти подключены к третьим и четвертым пятым и шестым входам блока контроля, при этом второй выход подключен к четвертому входу второго коммутатора, а третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым, пятым и шестым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к второй группе входов блока логических операций и контроля и являются выходами управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, сигналов сдвига, шестой выход блока управляющей памяти подключен к пятому входу блока управления, выходы регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода подключены к вторым входам третьего коммутатора и к пятым входам второго коммутатора, выход счетчика сдвигов подключен к шестым входам второго коммутатора, первые выходы третьего коммутатора подключены соответственно к входам сумматора и к третьим входам блока логических операций и контроля, выходы сумматора подключены к четвертым входам блока логических операций и контроля, вторые, третьи, четвертые, пятые, шестые и седьмые выходы третьего коммутатора подключены к пятым, шестым, седьмым, восьмым, девятым и десятым входам блока логических операций и контроля, первые выходы блока логических операций и контроля подключены к входам первого блока кодирования, первый и второй выходы которого подключены соответственно к двенадцатому и тринадцатому входам блока логических операций и контроля, вторые выходы блока логических операций и контроля подключены к входам второго блока кодирования, первый и второй выходы которого подключены соответственно к четырнадцатому и пятнадцатому входам блока логических операций и контроля, третий, четвертый и пятый выходы блока логических операций и контроля подключены к входам второго коммутатора, отличающийся тем, что первый и второй блоки кодирования дополнительно содержат по третьему выходу, причем первый блок кодирования формирует значения разрядов поправки на своем первом p1, втором р2 и третьем р3 выходе путем сложения по модулю 2 информационных символов s1, s2, s3, s4, s5, s6, s7, s8, s9, s10, s11, s12, поступающих с первых выходов блока логических операций и контроля на входы первого блока кодирования, в соответствии с правилом: p1=s3 ⊕ s6 ⊕ s7 ⊕ s8 ⊕ s9 ⊕ s10 ⊕ s11, р2=s2 ⊕ s4 ⊕ s5 ⊕ s8 ⊕ s9 ⊕ s10 ⊕ s11, р3=s1 ⊕ s4 ⊕ s5 ⊕ s6 ⊕ s7 ⊕ s10 ⊕ s11 ⊕ s12, первый, второй выходы первого блока кодирования подключены соответственно к двенадцатому и тринадцатому входам блока логических операций и контроля, а третий выход подключен к шестнадцатому входу блока логических операций и контроля, второй блок кодирования, формирующий значения проверочных контрольных разрядов на первом r1C, втором r2C и третьем r3C выходах путем сложения по модулю 2 значений информационных символов y1C, y2C, y3C, y4C, y5C, y6C, y7C, y8C, y9C, y10C, y11C, y12C, полученных при выполнении арифметических и логических операций и поступающих со вторых выходов блока логических операций и контроля на входы второго блока кодирования в соответствии с правилом: r1C=y3C ⊕ y6C ⊕ y7C ⊕ y8C ⊕ y9C ⊕ y10C ⊕ Y11C, r2C=y2C ⊕ y4C ⊕ y5C ⊕ y8C ⊕ y9C ⊕ y10C ⊕ y11C, r3C=y1C ⊕ y4C ⊕ y5C ⊕ y6C ⊕ y7C ⊕ y10C ⊕ y11C ⊕ y12C, первый и второй выходы второго блока кодирования подключены соответственно к четырнадцатому и пятнадцатому входам блока логических операций и контроля, а третий выход подключен к семнадцатому входу блока логических операций и контроля.

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Прибор для опробования нефтяных пластов в буровых скважинах | 1934 |

|

SU51428A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Способ изготовления бесконечных лент из полос шлифовальной шкурки | 1955 |

|

SU102407A1 |

| JP 2014229130 A, 08.12.2014. | |||

Авторы

Даты

2019-12-12—Публикация

2018-05-07—Подача