Изобретение относится к вычислительной технике и может быть использовано для повышения достоверности функционирования запоминающих устройств.

Известно самокорректирующееся устройство [1], использующее корректирующий код (наиболее часто используется код Хемминга, корректирующий одиночную ошибку и обнаруживающий двойную ошибку).

Недостатком устройства является низкая обнаруживающая способность кода, так как обнаруживаются только двойные ошибки.

Наиболее близким по техническому решению является отказоустойчивое устройство хранения и передачи данных, реализующие коды, исправляющие одиночные байты ошибок, обнаруживающие двойные байты ошибок [2], содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, коммутаторы ошибок байтов, корректор, входы устройства подключены к входам узла памяти и к входам входного кодирующего устройства, выходы которого подключены к первым входам блока вычисления синдрома, выходы узла памяти подключены к вторым входам блока вычисления синдрома и к первым входам корректора, выходы блока вычисления синдрома подключены к входам дешифратора, соединенного своими выходами со вторыми входами корректора, выходы корректора являются выходами устройства.

Недостатком устройства является низкая обнаруживающая способность ошибок в устройстве, так как обнаруживаются только двойные байты ошибок.

Целью изобретения является повышение достоверности функционирования устройства за счет коррекции одиночных байтов и обнаружения ошибок в байтах информации.

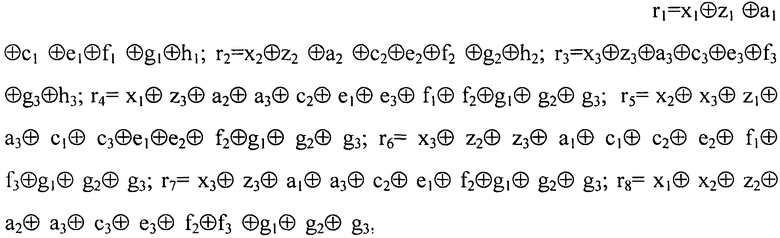

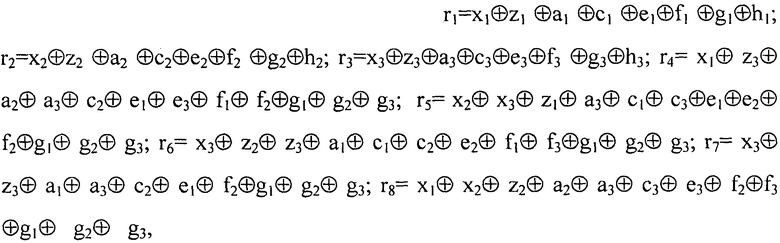

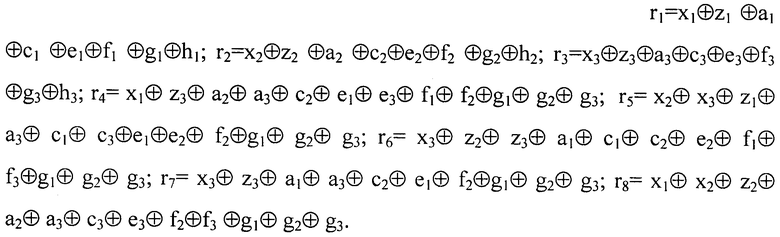

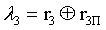

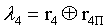

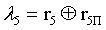

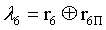

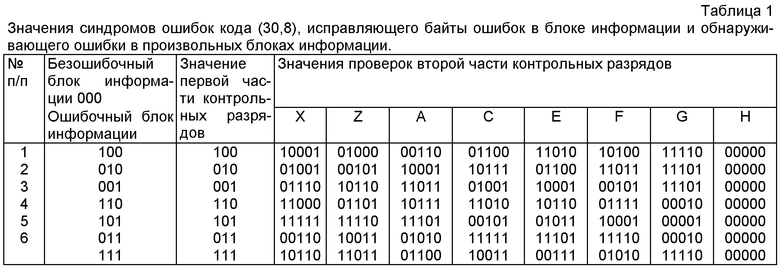

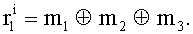

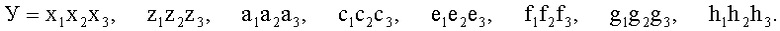

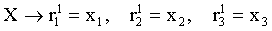

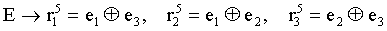

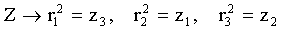

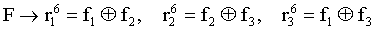

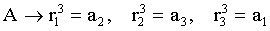

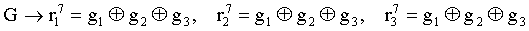

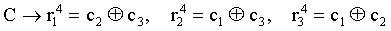

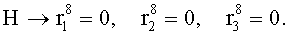

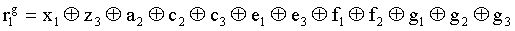

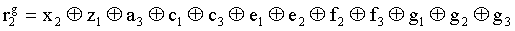

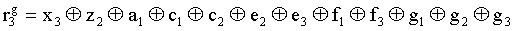

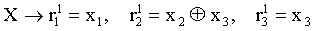

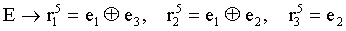

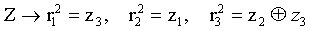

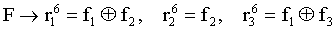

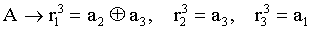

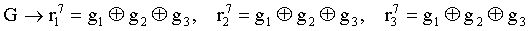

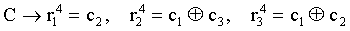

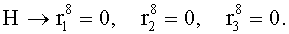

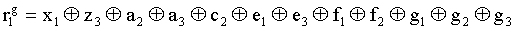

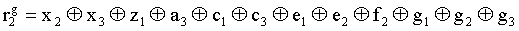

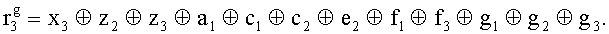

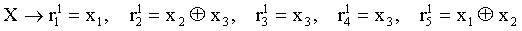

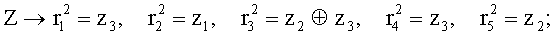

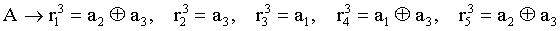

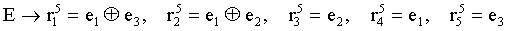

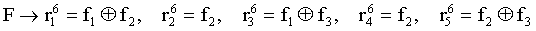

Поставленная цель достигается тем, что устройство, содержащее узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, коммутатор, блок коммутаторов, корректор, блок корректоров, отличается тем, что оно дополнительно содержит первый блок элементов ИЛИ, второй блок элементов ИЛИ, инвертор, элемент И, блок элементов И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, двадцатичетырехразрядные информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, вход синхронизации подключен к пятому входу узла памяти и к первому входу блока элементов И, информационные входы подключены к шестым входам узла памяти и к входам входного блока кодирования, который формирует значения контрольных разрядов r1, r2, r3, r4, r5, r6, r7, r8 путем сложения по модулю 2 информационных символов x1 x2 x3, z1 z2 z3, a1 a2 а3, c1 c2 c3, e1 е2 е3, f1 f2 f3, g1 g2 g3, h1 h2 h3, поступающих на входы входного блока кодирования, в соответствии с правилом:

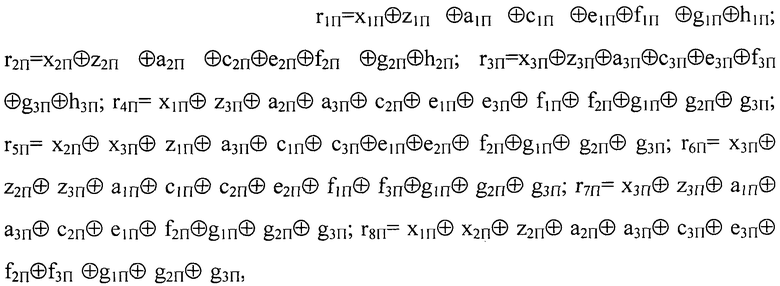

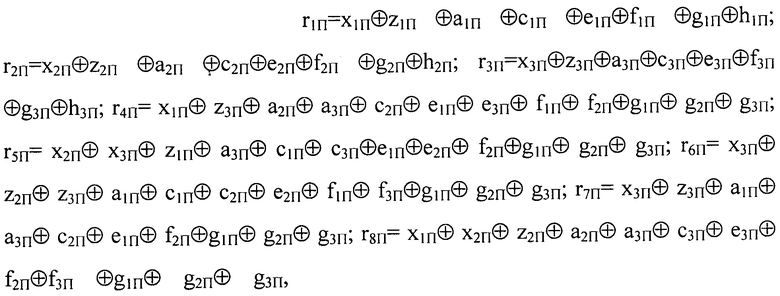

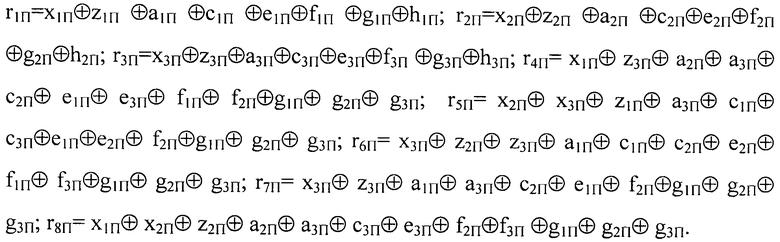

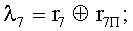

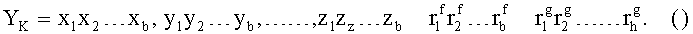

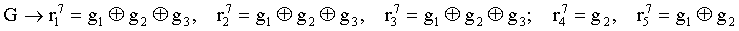

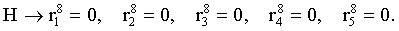

которые поступают на седьмые входы узла памяти, информационные выходы узла памяти подключены соответственно к первым входам корректора, блока корректоров и к входам выходного блока кодирования, который формирует значения проверочных контрольных разрядов r1П, r2П, r3П, r4П, r5П, r6П, r7П, r8П путем сложения по модулю 2 информационных символов x1П x2П x3П, z1П z2П z3П, a1П а1П а3П, с1П c2П с3П, е1П е2П e3П, f1П f2П f3П, g1П g2П g3П, h1П h2П h3П, поступающих на входы входного блока кодирования с информационных выходов узла памяти, в соответствии с правилом:

выходы выходного блока кодирования подключены к первым входам блока вычисления синдрома ошибки, к вторым входам которого подключены выходы контрольных разрядов узла памяти, первые выходы блока вычисления синдрома ошибки подключены к первым входам дешифратора, к первым входам коммутатора, к входам первого блока элементов ИЛИ и к первым входам блока коммутаторов, вторые выходы блока вычисления синдрома ошибки подключены к вторым входам дешифратора и к вторым входам первого блока элементов ИЛИ, выходы дешифратора подключены к входам второго блока элементов ИЛИ, при этом первый выход дешифратора подключен к второму входу коммутатора, а вторые выходы подключены к вторым входам блока коммутаторов, выход второго блока элементов ИЛИ черeз инвертор подключен к первому входу элемента И, второй вход которого подключен к выходу первого блока элементов ИЛИ, выход элемента И является выходом сигнала «ошибка», выходы коммутатора подключены к вторым входам корректора, выходы блока коммутаторов подключены к вторым входам блока корректоров, выходы корректора и блока корректоров подключены к вторым входам блока элементов И, выходы которого являются информационными выходами устройства.

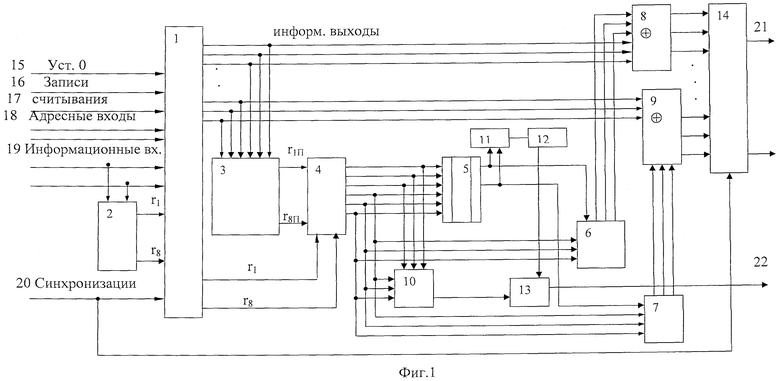

На фиг.1 представлена блок-схема устройства. Устройство хранения и передачи данных с исправлением ошибок в байте информации и обнаружением ошибок в байтах информации содержит: узел 1 памяти, входной блок 2 кодирования, выходной блок 3 кодирования, блок 4 вычисления синдрома ошибки, дешифратор 5, коммутатор 6, блок 7 коммутаторов, корректор 8, блок 9 корректоров, первый элемент 10 ИЛИ, второй элемент 11 ИЛИ, инвертор 12, элемент 13 И, блок 14 элементов И, вход 15 установки в нулевое состояние, вход 16 записи, вход 17 считывания, адресные входы 18, информационные входы 19, вход 20 синхронизации, информационные выходы 21, выход 22 сигнала "ошибка".

Вход 15 установки в нулевое состояние, вход 16 записи, вход 17 считывания, адресные входы 18 подключены соответственно к первому, второму, третьему и четвертому входам узла 1 памяти, вход 20 синхронизации подключен к пятому входу узла 1 памяти и к первому входу блока 14 элементов И, информационные входы 19 подключены к шестым входам узла 1 памяти и к входам входного блока 2 кодирования, который формирует значения контрольных разрядов r1, r2, r3, r4, r5, r6, r7, r8 путем сложения по модулю 2 информационных символов x1 x2 x3, z1 z2 z3, a1 a2 а3, c1 c2 c3, e1 e2 e3, f1 f2 f3, g1 g1 g3, h1 h2 h3, поступающих на входы входного блока 2 кодирования, в соответствии с правилом:

которые поступают на седьмые входы узла 1 памяти, информационные выходы узла памяти подключены соответственно к первым входам корректора 8, блока 9 корректоров и к входам выходного блока 3 кодирования, который формирует значения проверочных контрольных разрядов r1П, r2П, r3П, r4П, r5П, r6П, r7П, r8П путем сложения по модулю 2 информационных символов x1П x2П x3П, z1П z2П z3П, a1П а2П а3П, с1П c2П с3П, е1П е2П e3П, f1П f2П f3П, g1П g2П g3П, h1П h2П h3П, поступающих на входы входного блока 3 кодирования с информационных выходов узла 1 памяти, в соответствии с правилом:

выходы выходного блока 3 кодирования подключены к первым входам блока 4 вычисления синдрома ошибки, к вторым входам которого подключены выходы контрольных разрядов узла 1 памяти, первые выходы блока 4 вычисления синдрома ошибки подключены к первым входам дешифратора 5, к первым входам коммутатора 6, к входам первого блока 10 элементов ИЛИ и к первым входам блока 7 коммутаторов, вторые выходы блока 4 вычисления синдрома ошибки подключены к вторым входам дешифратора 5 и к вторым входам первого блока 10 элементов ИЛИ, выходы дешифратора 5 подключены к входам второго блока 11 элементов ИЛИ, при этом первый выход дешифратора 5 подключен к второму входу коммутатора 6, а вторые выходы подключены к вторым входам блока 7 коммутаторов, выход второго блока 11 элементов ИЛИ черeз инвертор 12 подключен к первому входу элемента 13 И, второй вход которого подключен к выходу первого блока 10 элементов ИЛИ, выход элемента 13 И является выходом сигнала «ошибка», выходы коммутатора 6 подключены к вторым входам корректора 8, выходы блока 7 коммутаторов подключены к вторым входам блока 9 корректоров, выходы корректора 8 и блока 9 корректоров подключены к входам блока 14 элементов И, выходы которого являются информационными выходами 21 устройства.

Узел 1 памяти, в данном случае, представляет собой статическое полупроводниковое оперативное устройство памяти и предназначен для хранения кодовых наборов: УК=x1 x2 x3, z1 z2 z3, a1 a2 а3, c1 c2 c3, e1 e2 e3, f1 f2 f3, g1 g2 g3, h1 h2 h3, r1 r2 r3 r4 r5 r6 r7 r8, полученных при кодировании исходных двадцатичетырехразрядных двоичных наборов.

Входной блок 2 кодирования предназначен для формирования значений контрольных разрядов r1, r2, r3, r4, r5, r6, r7, r8, путем сложения по mod2 информационных символов в соответствии с правилом:

Выходной блок 3 кодирования предназначен для формирования значений проверочных контрольных разрядов r1П, r2П, r3П, r4П, r5П, r6П, r7П, r8П путем сложения по mod2 информационных символов, полученных при считывании информации с узла 1 памяти в соответствии с правилом:

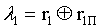

Блок 4 вычисления синдрома ошибки предназначен для обнаружения ошибки в кодовом наборе при считывании информации с узла 1 памяти путем сложения по mod2 значений контрольных разрядов r1, r2, r3, r4, r5, r6, r7, r8, считываемых с вторых выходов узла 1 памяти, соответственно со значениями контрольных разрядов r1П, r2П, r3П, r4П, r5П, r6П, r7П, r8П, сформированных на выходах выходного блока 3 кодирования.

Результат поразрядного сложения:

;

;

;

;

;

;

;

;

;

;

;

;

Нулевой результат суммы свидетельствует об отсутствии ошибки и ее наличии в противном случае.

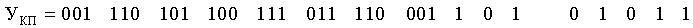

Выходы λ1 λ2 λ3 блока 4 вычисления синдрома ошибки позволяют определять конфигурацию ошибки (вектор ошибки λ1 λ2 λ3, содержащий единичные значения в тех разрядах, которые соответствуют ошибочным разрядам в блоке информации), выходы λ4 λ5 λ6 λ7 λ8 определяют блок информационных разрядов, в котором произошла ошибка.

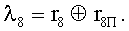

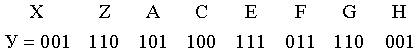

Дешифратор 7 формирует единичное значение сигнала на одном из своих выходов в соответствии с таблицей 1.

Если значение синдрома ошибки не соответствует значениям, представленным в таблице, то произошла не корректируемая ошибка (сигналы на выходе дешифратора имеют нулевые значения).

В этом случае, о наличии не корректируемой ошибки свидетельствует наличие единичного значения сигнала на выходе первого блока 10 элементов ИЛИ и отсутствие единичного значения сигнала на выходе второго элемента 11 ИЛИ.

Корректор 8 (блок 9 корректоров) предназначен для исправления корректируемой ошибки, путем сложения по mod2 одноименных разрядов блока информации, имеющего ошибку со значением вектора ошибки.

Устройство работает следующим образом. Перед началом работы устройства на вход 15 "установки в нулевое состояние" подается единичный сигнал, который переводит устройство в нулевое состояние.

При записи информации в узел 1 памяти, подаются единичные сигналы на вход 20 синхронизации, вход 16 записи, адресные входы 18 и информационные входы 19.

Входной блок 2 информации формирует значения контрольных разрядов по правилу:

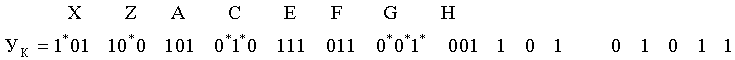

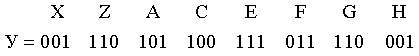

Пример. Допустим, необходимо закодировать двоичный набор:

.

.

Тогда первая часть и вторая часть контрольных разрядов, сформированных относительно полученного кодового набора, соответственно равны:

r1=1, r2=0, r3=1, r4=0, r5=1, r6=0, r7=1, r8=1.

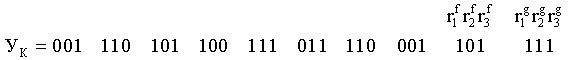

.

.

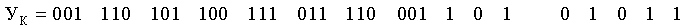

При отсутствии ошибки, значение кодового набора, записанного в узле 1 памяти, равно считанному (переданному кодовому набору):

.

.

В этом случае на выходе блока 4 вычисления синдрома ошибки имеем нулевые значения сигналов.

Пусть, произошла одиночная ошибка в первом разряде третьего блока информации (А=0*01), тогда выходной блок 3 кодирования сформирует относительно полученного кодового набора значения контрольных разрядов:

r1П=0, r2П=0, r3П=1, r4П=1, r5П=1, r6П=0, r7П=1, r8П=0.

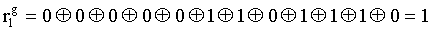

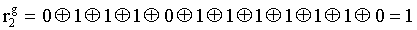

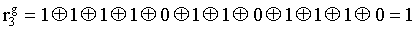

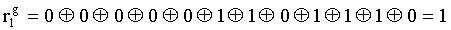

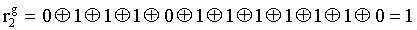

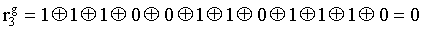

В блоке 4 вычисления синдрома ошибки складываются переданные контрольные разряды с контрольными разрядами, сформированными относительно полученного кодового набора, в результате получим синдром ошибки:

В этом случае, первая часть синдрома указывает на ошибочный разряд блока информации, вторая часть синдрома указывает ошибочный блок А (см. табл.1).

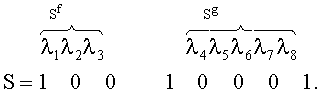

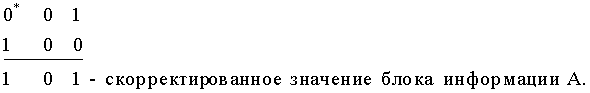

На выходе дешифратора 7 появится единичное значение сигнала, которое открывает элементы И блока 7 коммутаторов, при этом значения вектора ошибки поступают на входы блока корректоров 9, где складывается по mod2 со значениями разрядов третьего блока информации:

В результате имеем правильное значение информации.

Пусть, произошла одиночная ошибка в первом разряде первого блока информации, одиночная ошибка во втором разряде второго блока информации, двойная ошибка в первом и втором разрядах четвертого блока информации и тройная ошибка в восьмом блоке информации.

В этом случае, значения контрольных разрядов, сформированные выходным блоком 3 кодирования относительно полученного двоичного набора, равны:

r1П=1, r2П=1, r3П=1,

r3П=1, r4П=1, r6П=1, r7П=1, r8П=0.

Значение синдрома ошибки, полученное блоком 4 вычисления синдрома ошибки, равно:  .

.

В этом случае, на выходе первого блока 10 элементов ИЛИ появится единичное значение сигнала, на всех выходах дешифратора 7 присутствует нулевое значение сигнала, поэтому на выходе второго блока 11 элементов ИЛИ так же имеем нулевое значение сигнала, а на выходе инвертора 12 - единичное значение сигнала, которое открывает элемент 12 И, с выхода которого снимается сигнал «ошибка».

Таким образом, в предлагаемом устройстве хранения информации корректируются одиночные ошибки в отдельном блоке информации и обнаруживаются байты ошибок, за исключением ошибок, трансформируемых в корректируемые.

Источники информации

1. Щербаков Н.С. Достоверность работы цифровых устройств. М.: Машиностроение, 1989, с.82, рис.39, 224 с.

2. Щербаков Н.С. Достоверность работы цифровых устройств. М.: Машиностроение, 1989, с.122, рис.45, 224 с.

Приложение

1. Введение и постановка задачи

Во многих случаях для обнаружения и исправления ошибок используются коды с обнаружением и исправлением байтов ошибок (в этом случае, под байтом ошибок понимаются ошибки, кратность которых не превышает число разрядов b блока информации).

К таким кодам следует отнести коды [1]:

- исправляющие одиночные ошибки и обнаруживающие одиночные байты ошибок;

- коды, исправляющие одиночные ошибки, обнаруживающие двойные независимые ошибки и обнаруживающие одиночные байты ошибок;

- коды, исправляющие одиночные байты ошибок;

- коды, исправляющие одиночные и обнаруживающие двойные байты ошибок.

Широкое распространение получили коды Рида-Соломона, обладающие циклическими свойствами и имеющие наибольшую обнаруживающую и корректирующую способность.

Код Рида-Соломона (PC) - это блочный код (w, N), позволяющий обнаруживать и исправлять ошибки в байтах. Входным словом для него является блок из w байтов, выходным - кодовое слово из N байтов, состоящее из w исходных и N-w проверочных байтов. При этом гарантировано, что при декодировании в кодовом слове будут обнаружены и исправлены t=(N-w)/2 байтов независимо от их расположения внутри кодового слова. Кодирующее устройство PC реализуется на основе регистра сдвига с 2t байтовыми элементами памяти и обратными связями. Процесс кодирования и декодирования сводится к операциям сложения и умножения по модулю.

Использование данных кодов связано с большими временными затратами, что является существенным недостатком при их использовании для систем, работающих в реальном масштабе времени, поэтому существует необходимость в разработке более простой линейной процедуры построения корректирующих кодов, решающих данную задачу.

2. Разработка линейного корректирующего кода с исправлением одиночных ошибок в байте информации и обнаружением ошибок в байтах информации

Предлагается метод построения корректирующего кода, исправляющего одиночные и обнаруживающего двойные байты ошибок, реализующий линейную процедуру построения корректирующего кода с синдромным декодированием.

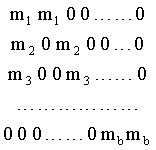

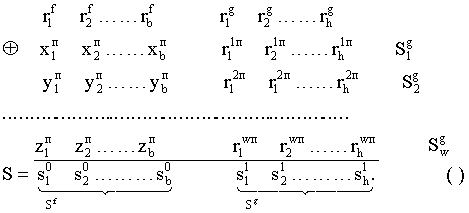

Для получения кодового расстояния, позволяющего обеспечить исправление одиночных и обнаружение двойные байтов ошибок, используем 2b контрольных разрядов (оптимальное число контрольных разрядов для кодов Рида-Соломона, решающих данную задачу), в которых реализуется сложение по mod2 одноименных разрядов блоков (байтов) информации.

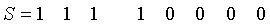

В результате получим кодовый набор:

Значения контрольных разрядов  ,

,  позволяют сформировать значение синдрома ошибки, при этом первая часть контрольных разрядов

позволяют сформировать значение синдрома ошибки, при этом первая часть контрольных разрядов  определяет вектор ошибки (ошибочные разряды в блоке информации), а значение второй части контрольных разрядов

определяет вектор ошибки (ошибочные разряды в блоке информации), а значение второй части контрольных разрядов  предназначено для определения номера ошибочного блока (байта) информации.

предназначено для определения номера ошибочного блока (байта) информации.

В этом случае число байтов информации определяется по формуле:

В связи с этим возникает необходимость формирования совокупности проверок (разработки правила кодирования информации), позволяющих определить блок информации, содержащий ошибку.

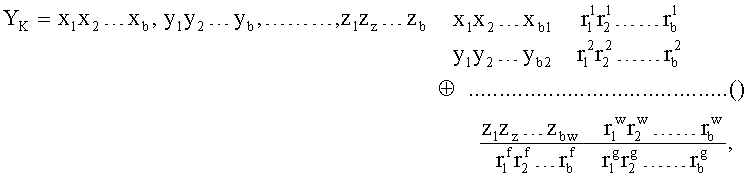

С этой целью, для каждого блока информации выберем свою совокупность проверок, обнаруживающих ошибку, используя матрицу кодирования размерности

.

.

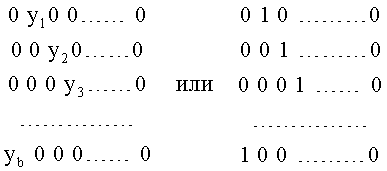

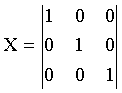

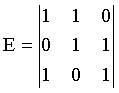

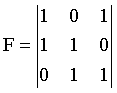

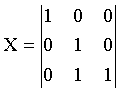

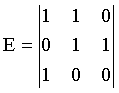

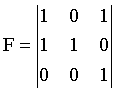

Для первого блока информации матрица кодирования имеет вид:

В этом случае, для первого блока информации значения контрольных разрядов соответственно равны  ;

;  ; ……

; ……  .

.

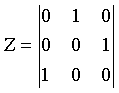

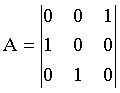

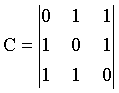

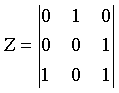

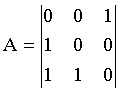

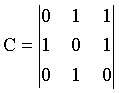

Для второго и третьего информационных блоков матрицы кодирования имеют вид соответственно:

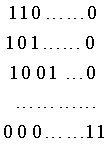

Не трудно заметить, что очередная матрица кодирования получается в результате циклической замены строк матрицы кодирования.

В результате получаем b исходных матриц кодирования, содержащих в своих строках по одной единице.

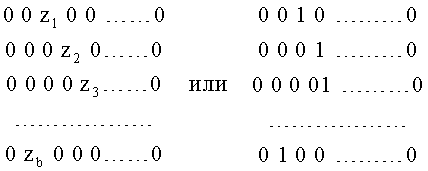

Для информационных блоков, начиная с b+1 блока, матрицы кодирования включают различные сочетания двух единиц в блоке информации:

Значения контрольных разрядов формируются сложением по mod2 элементов столбцов, соответствующих единичным значениям.

Так, например, если первый столбец больше не содержит единиц, то значение первого контрольного разряда равно:

Каждая очередная матрица кодирования для блоков информации, начиная с b+2 блока по  информации, получается циклической заменой строк матрицы по аналогии с матрицей, содержащей в своих строках по одной единице.

информации, получается циклической заменой строк матрицы по аналогии с матрицей, содержащей в своих строках по одной единице.

Аналогичным образом строятся матрицы кодирования, содержащие в своих строках различные сочетания из трех единиц и т.д.

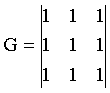

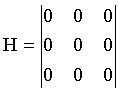

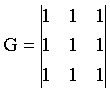

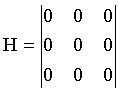

Окончательно имеем матрицу кодирования, каждый элемент которой содержит единицу. Построим также дополнительную матрицу кодирования, каждый элемент которой содержит нули.

Полученные таким образом значения контрольных разрядов позволяют построить код, корректирующий одиночные ошибки и обнаруживающий ошибки большей кратности.

Объединяя по модулю по mod2 одноименные контрольные проверки для всех блоков информации, получим значения контрольных разрядов  для второй части контрольных разрядов кодового набора.

для второй части контрольных разрядов кодового набора.

Таким образом, кодовый набор передается в виде:

Результат сложения по mod2 переданных значений контрольных разрядов

и контрольных разрядов

и контрольных разрядов

сформированных относительно полученных информационных разрядов, даст значение синдрома ошибки, включающего две части:

сформированных относительно полученных информационных разрядов, даст значение синдрома ошибки, включающего две части:

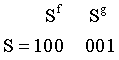

Значение синдрома ошибки Sf определяет вектор ошибки (ошибочные разряды в блоке информации), а значение синдрома ошибки Sg определяет номер ошибочного блока (байта) информации.

Стратегия декодирования заключается на следующих положениях:

1. Sf=0; Sg=0. Ошибок нет.

2. Sf=0; Sg≠0. Произошла ошибка в контрольных разрядах или не корректируемая ошибка в байтах информации.

3. Sf≠0; Sg≠0 (Sg=0). Произошла ошибка в информационных байтах (в одном байте - корректируемая, в двух - обнаруживаемая).

Таким образом, разработанный код, при оптимальном числе контрольных разрядов обладает свойствами, характерными для кодов Рида-Соломона, и при этом позволяет:

- использовать процедуру линейного кодирования;

- повысить быстродействие кодирования и декодирования информации.

Пример: Допустим, имеем двадцатичетырехразрядный двоичный набор, который разобьем на блоки информации по три разряда в каждом блоке:

Построим исходные матрицы кодирования для каждого блока информации:

,

,  ,

,  ,

,  ,

,

,

,  ,

,  ,

,  .

.

Складывая по mod2 элементы столбцов матриц, соответствующие единичным значениям, получим проверки, позволяющие получить значения контрольных разрядов для соответствующих блоков информации.

;

;  ;

;

;

;  ;

;

;

;  ;

;

;

;

В результате значение второй части контрольных разрядов формируется проверками:

;

;

;

;

.

.

Полученные значения контрольных разрядов, совместно со значениями первой части контрольных разрядов, сформированных путем сложения одноименных информационных разрядов блоков информации, позволяют иметь корректирующий код, исправляющий одиночные ошибки в любом блоке информации, и обнаруживать ошибки большей кратности.

В результате имеем код (30,6), корректирующий одиночные ошибки и обнаруживающий ошибки большей кратности.

Анализ таблицы 1 показывает, что в случае возникновения одиночной ошибки, значения второй части синдромов для блоков информации различаются между собой, что позволяет корректировать данные ошибки.

При возникновении ошибок большей кратности или в нескольких информационных блоках значения синдромов неразличимы, в этом случае ошибка обнаруживается.

При этом выделенные синдромы указывают на наличие не корректируемой ошибки, не выделенные синдромы указывают блок информации, содержащий соответствующую одиночную корректируемую ошибку.

Пример. Допустим, необходимо закодировать двоичный набор:

.

.

Подставляя в полученные выражения формирования второй части контрольных разрядов значения соответствующих разрядов двоичного набора, получим:

;

;

;

;

Складывая одноименные информационные разряды блоков информации, получим первую часть контрольных разрядов 101.

Таким образом, бeзошибочный кодовый набор передается в виде:

.

.

Пусть, произошла одиночная ошибка в первом разряде третьего блока информации (А), тогда первая часть и вторая часть контрольных разрядов, сформированных относительно полученного кодового набора, равны соответственно:

,

,  ,

,  .

.

;

;

;

;

.

.

Складывая переданные контрольные разряды с контрольными разрядами, сформированными относительно полученного кодового набора, получим синдром ошибки:

.

.

В этом случае первая часть синдрома указывает на ошибочный разряд блока информации, вторая часть синдрома указывает ошибочный блок (см. табл.1).

3. Разработка линейного корректирующего кода с исправлением ошибок в байте и обнаружением ошибок в произвольных байтах информации

Для коррекции ошибок в блоке информации кратности b, проведем модификацию полученных матриц () кодирования (за исключением матриц, содержащих все единицы и все нули), для чего разобьем полученную совокупность матриц кодирования попарно и в каждой паре изменим (инвертируем) по одному одноименному элементу.

Например, попарно разобьем исходную совокупность матриц кодирования информации на пары: XF; EZ; АС.

В матрицах XF инвертируем элементы второго столбца третьей строки, в матрицах EZ инвертируем элементы третьего столбца третьей строки, в матрицах АС инвертируем элементы первого столбца третьей строки.

В результате получим совокупность модифицированных матриц кодирования информации:

,

,  ,

,  ,

,  ,

,

,

,  ,

,  ,

,  .

.

Используя полученные матрицы, выпишем проверки для контрольных разрядов соответствующих блоков информации (складываются по mod2 элементы столбцов матриц, имеющие единичные значения, при этом номер элемента соответствует номеру строки матрицы):

;

;  ;

;

;

;  ;

;

;

;  ;

;

;

;

В результате значение второй части контрольных разрядов формируется проверками:

;

;

;

;

В табл.2 представлены соответствующие значения синдромов кода (30,6) для ошибок различной кратности.

Анализ таблицы показывает, что данный код может исправлять все одиночные и тройные ошибки в отдельном блоке информации и корректировать часть двойных ошибок.

Заметим, что использование исходных матриц для построения кода, корректирующего одиночные ошибки, порождает 32 неразличимых синдрома ошибок (см. табл.2). При использовании приведенных выше модифицированных матриц для построения кода, корректирующего одиночные байты ошибок и обнаруживающего ошибки в двух байтах, имеем 18 неразличимых синдрома ошибок.

Если изменить порядок построения модифицированных матриц кодирования информации, например, попарно объединить исходные матрицы на ХЕ, FZ, АС и в матрицах ХЕ инвертировать элементы первого столбца третьей строки, в матрицах FZ инвертировать элементы третьего столбца третьей строки, в матрице А инвертировать элемент второго столбца первой строки, а в матрице С инвертировать элемент второго столбца третьей строки, то получим 26 неразличимых синдромов ошибок.

В связи с этим, при построении корректирующего кода необходимо обеспечить рациональный выбор построения модифицированных матриц, обеспечивающих требуемый уровень обнаружения и исправления ошибок.

Для повышения корректирующей способности кода, необходимо ввести дополнительные проверки (контрольные разряды).

Так, например, для рассматриваемого примера потребуется два дополнительных контрольных разряда  ,

,  :

:

;

;

;

;

;

;

;

;

;

;

;

;

В табл.3 представлены значения синдромов ошибок кода (30,8), исправляющего кратные ошибки в блоке информации и обнаруживающего ошибки в произвольных блоках информации.

Введение дополнительных проверок существенно повышает обнаруживающие способности кода. Так, например, при возникновении одиночной ошибки в первом разряде блока информации X, одиночной ошибки во втором разряде блока Z, двойной ошибки в первом и втором разрядах блока S, тройной ошибки в блоке G получим значение синдрома ошибки  , характеризующего наличие некорректируемой ошибки.

, характеризующего наличие некорректируемой ошибки.

При необходимости полученный код допускает минимизацию контрольных разрядов, так, удаляя первый контрольный разряд второй части контрольных разрядов  , получим корректирующий код (30,7), корректирующий ошибки в байте информации и обнаруживающий ошибки в двух блоках информации (см. табл.4).

, получим корректирующий код (30,7), корректирующий ошибки в байте информации и обнаруживающий ошибки в двух блоках информации (см. табл.4).

Таким образом, предлагаемый метод построения корректирующих кодов, обнаруживающих и корректирующих ошибки в байтах информации, позволяет исключить процедуру деления и умножения, необходимую при использовании циклических кодов, и заменить ее на линейную, повысить быстродействие кодирования и декодирования информации, обеспечить требуемый уровень обнаружения и коррекции ошибок.

Источник информации

1. Щербаков Н.С. Достоверность работы цифровых устройств. М.: Машиностроение, 1989, с.122, рис.45, 224 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2014 |

|

RU2542665C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И СЧИТЫВАНИЯ ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК | 2023 |

|

RU2816550C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОДИНОЧНЫХ И ДВОЙНЫХ ОШИБОК | 2011 |

|

RU2450332C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК И ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2024 |

|

RU2826822C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ОБНАРУЖЕНИЕМ ОШИБОК | 2016 |

|

RU2637426C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2013 |

|

RU2534499C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

Изобретение относится к области телемеханики, автоматики и вычислительной техники и предназначено для повышения достоверности функционирования запоминающих устройств. Техническим результатом является повышение достоверности функционирования устройства за счет коррекции одиночных ошибок в отдельных байтах информации и обнаружения произвольных ошибок в байтах информации. Устройство содержит узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, коммутаторы, корректоры, элементы ИЛИ, инвертор, элементы И. 1 ил., 5 табл., 1 приложение.

Устройство хранения и передачи данных с исправлением ошибок в байте информации и обнаружением ошибок в байтах информации, содержащее узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, коммутатор, блок коммутаторов, корректор, блок корректоров, отличающееся тем, что оно дополнительно содержит первый блок элементов ИЛИ, второй блок элементов ИЛИ, инвертор, элемент И, блок элементов И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, двадцатичетырехразрядные информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», вход установки в нулевое состояние, вход записи, вход считывания, адресные входы подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, вход синхронизации подключен к пятому входу узла памяти и к первому входу блока элементов И, информационные входы подключены к шестым входам узла памяти и к входам входного блока кодирования, который формирует значения контрольных разрядов r1, r2, r3, r4, r5, r6, r7, r8 путем сложения по модулю 2 информационных символов x1 x2 x3, z1 z2 z3, a1 a2 a3, c1 c2 c3, e1 e2 e3, f1 f2 f3, g1 g2 g3, h1 h2 h3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=x1⊕z1⊕a1⊕c1⊕e1⊕f1⊕g1⊕h1; r2=x2⊕z2⊕a2⊕c2⊕e2⊕f2⊕g2⊕h2; r3=x3⊕z3⊕a3⊕c3⊕е3⊕f3⊕g3⊕h3; r4=x1⊕z3⊕a2⊕a3⊕c2⊕e1⊕e3⊕f1⊕f2⊕g1⊕g2⊕g3; r5=x2⊕x3⊕z1⊕a3⊕c1⊕c3⊕e1⊕e2⊕f2⊕g1⊕g2⊕g3;

r6=x3⊕z2⊕z3⊕a1⊕c1⊕c2⊕e2⊕f1⊕f3⊕g1⊕g2⊕g3;

r7=x3⊕z3⊕a1⊕a3⊕c2⊕e1⊕f2⊕g1⊕g2⊕g3;

r8=x1⊕x2⊕z2⊕a2⊕a3⊕c3⊕e3⊕f2⊕f3⊕g1⊕g2⊕g3, которые поступают на седьмые входы узла памяти, информационные выходы узла памяти подключены соответственно к первым входам корректора, блока корректоров и к входам выходного блока кодирования, который формирует значения проверочных контрольных разрядов r1П, r2П, r3П, r4П, r5П, r6П, r7П, r8П путем сложения по модулю 2 информационных символов x1П x2П x3П, z1П z2П z3П, a1П а2П а3П, c1П c2П c3П, e1П е2П е3П, f1П f2П f3П, g1П g2П g3П, h1П h2П h3П, поступающих на входы входного блока кодирования с информационных выходов узла памяти, в соответствии с правилом:

r1П=x1П⊕z1П⊕a1П⊕с1П⊕e1П⊕f1П⊕g1П⊕h1П;

r2П=x2П⊕z2П⊕а2П⊕c2П⊕e2П⊕f2П⊕g2П⊕h2П;

r3П=x3П⊕z3П⊕а3П⊕с3П⊕e3П⊕f3П⊕g3П⊕h3П;

r4П=x1П⊕z3П⊕а2П⊕а3П⊕c2П⊕e1П⊕e3П⊕f1П⊕f1П⊕g1П⊕g2П⊕g3П;

r5П=x2П⊕x3П⊕z1П⊕а3П⊕с1П⊕с3П⊕е1П⊕е2П⊕f2П⊕g1П⊕g2П⊕g3П;

r6П=x3П⊕z2П⊕z3П⊕а1П⊕с1П⊕c2П⊕е2П⊕f1П⊕f3П⊕g1П⊕g2П⊕g3П;

r7П=x3П⊕z3П⊕а1П⊕а3П⊕с2П⊕f2П⊕f2П⊕g1П⊕g2П⊕g3П;

r8П=x1П⊕x2П⊕z2П⊕а2П⊕а3П⊕с3П⊕e3П⊕f2П⊕f3П⊕g1П⊕g2П⊕g3П, выходы выходного блока кодирования подключены к первым входам блока вычисления синдрома ошибки, к вторым входам которого подключены выходы контрольных разрядов узла памяти, первые выходы блока вычисления синдрома ошибки подключены к первым входам дешифратора, к первым входам коммутатора, к входам первого блока элементов ИЛИ и к первым входам блока коммутаторов, вторые выходы блока вычисления синдрома ошибки подключены к вторым входам дешифратора и к вторым входам первого блока элементов ИЛИ, выходы дешифратора подключены к входам второго блока элементов ИЛИ, при этом первый выход дешифратора подключен к второму входу коммутатора, а вторые выходы подключены к вторым входам блока коммутаторов, выход второго блока элементов ИЛИ через инвертор подключен к первому входу элемента И, второй вход которого подключен к выходу первого блока элементов ИЛИ, выход элемента И является выходом сигнала «ошибка», выходы коммутатора подключены к вторым входам корректора, выходы блока коммутаторов подключены к вторым входам блока корректоров, выходы корректора и блока корректоров подключены к вторым входам блока элементов И, выходы которого являются информационными выходами устройства.

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2211492C2 |

| Тележка для подъема, например, рулонов ткани, и перевода настилочной машины с рельсов одного настилочного стола на рельсы другого | 1955 |

|

SU102403A1 |

| Устройство для обнаружения и коррекции ошибок | 1990 |

|

SU1783583A1 |

| Способ определения неисправного усилительного участка на магистрали связи с частотным разделением каналов | 1974 |

|

SU527025A1 |

| JP 58041499 A, 10.03.1983. | |||

Авторы

Даты

2012-04-20—Публикация

2011-04-05—Подача