Уровень техники

[0001] При написании кода во время разработки приложений системы программного обеспечения разработчики обычно тратят значительное количество времени на "отладку" кода, чтобы искать ошибки при исполнении в коде. При этом разработчики могут предпринимать несколько подходов, чтобы воспроизводить и локализовать ошибку в исходном коде, таких как наблюдение за поведением программы на основе различных входных данных, вставка кода отладки (например, чтобы печатать значения переменных, отслеживать ветви выполнения и т.д.), временное удаление фрагментов кода и т.д. Выслеживание ошибок при исполнении, чтобы точно определять ошибки кода, может занимать значительную долю времени для разработки приложения.

[0002] Множество типов приложений отладки ("отладчиков") было разработано для того, чтобы помогать разработчикам с процессом отладки кода. Эти инструменты предлагают разработчикам способность отслеживать, визуализировать и изменять выполнение компьютерного кода. Например, отладчики могут визуализировать выполнение инструкций кода, могут представлять значения переменных в различные моменты во время выполнения кода, могут предоставлять возможность разработчикам изменять пути выполнения кода и/или могут предоставлять возможность разработчикам устанавливать "точки останова" и/или "точки наблюдения" на интересующих элементах кода (которые, когда достигаются во время исполнения, инструктируют приостановку исполнения кода), среди прочего. В целом, "точка останова" относится к местоположению в памяти, хранящему конкретный фрагмент исполняемого кода (например, строку кода, определение переменной, определение функции и т.д.), в то время как "точка наблюдения" относится к местоположению в памяти, хранящему данные (например, местоположению в памяти, хранящему значение переменной, константы, структуры данных и т.д.). Для простоты в данном документе использование термина "точка останова" соответствует как точке останова, так и на точке наблюдения.

[0003] Появляющаяся форма приложений отладки предоставляет возможность "путешествия во времени", "обратного хода" или "исторической" отладки, в которой исполнение программы записывается/трассируется посредством трассирующего программного обеспечения и/или аппаратных средств в один или более файлов трассировки, которые могут быть затем использованы для воспроизведения выполнения программы позже для прямого и обратного анализа. Например, отладчики с "путешествием во времени" могут предоставлять возможность разработчику устанавливать прямые точки останова (аналогично традиционным отладчикам), а также обратные точки останова.

[0004] Одна проблема в реализации отладчиков с "путешествием во времени" подразумевает то, как обнаружить, когда интересующий адрес памяти (например, соответствующий точке останова) встретился во время воспроизведения файла трассировки, гибким и эффективным образом. Одним механизмом, который был изучен для отслеживания интересующих адресов памяти во время воспроизведения, является использование реализованных с помощью процессора аппаратных точек останова. Тогда как является эффективным, использование аппаратных точек останова имеет недостаток существенного ограничения числа адресов памяти, за которыми можно одновременно следить. Например, архитектура INTEL x86 предоставляет только четыре регистра отладки (т.е. DR0-DR3) для хранения адресов памяти для отслеживания. Использование аппаратных точек останова также имеет недостаток неотъемлемой привязки реализации отладчика к специально поддерживаемым аппаратным средствам (например, полагаясь на регистры отладки x86).

[0005] Другим механизмом, который был изучен, является использование программных точек останова, в котором каждая отслеживаемая операция, которая осуществляет доступ к памяти (например, чтение или запись в память, хранящую данные, или чтение/выборка для исполнения из памяти, хранящей код программы), практически осуществляется с дополнительными инструкциями кода, которые проверяют, осуществлять или нет доступ к интересующему адресу памяти. Однако инструментальное оснащение имеет серьезный недостаток вызывания проверки для возникновения точки останова, которая должна выполняться для каждого доступа к памяти, независимо от того, будет или нет доступ к памяти фактически соответствовать точке останова. Во многих окружениях исполнение оснащенных инструментальными средствами инструкций кода приводит в результате к использованию от десятков до сотен дополнительных циклов процессора для каждого доступа к памяти, что имеет значительное отрицательное воздействие на производительность воспроизведения, которое является заметным для пользователя-человека.

[0006] Предыдущие решения автора изобретения должны устранять вышеупомянутые проблемы посредством использования кэшей (например, кэша аппаратных средств или эмулируемого процессора, либо некоторой другой структуры кэш-памяти) как части обнаружения точки останова. Эти решения в значительной степени ограничивают число циклов процессора, необходимых для выполнения проверки точки останова, по сравнению с инструментальным оснащением, и описываются в патентной заявке США порядковый номер 15/405,849, поданной 13 января 2017 г. и озаглавленной "EFFICIENT BREAKPOINT DETECTIONS VIA CACHES".

[0007] Эти решения используют кэш для ограничения проверок точек останова только адресами памяти, которые вызывают возникновение кэш-промах (отсутствий нужных данных в кэше), вместо выполнения проверки точки останова по каждому доступу в память. Эти решения могут предлагать значительные улучшения производительности по сравнению с решениями обнаружения точек останова не на основе кэша, в то же время предоставляя практически неограниченное число точек останова. Они подразумевают исключение строки кэша, если она перекрывается с адресом памяти, который соответствует точке останова, и затем "пошаговую трассировку" процессором по каждому отсутствию нужных данных в кэше для того, чтобы определять, была ли встречена точка останова. В то время как являются преимуществом над инструментальным оснащением для обнаружения точки останова, эти решения значительно влияют на производительность выполнения, когда возникают отсутствия нужных данных в кэше (даже если точка останова не была достигнута в связи с отсутствием нужных данных в кэше), а также вызывают возникновения отсутствий нужных данных в кэше более часто по сравнению с отсутствием использования кэша для обнаружения точки останова (т.е. поскольку они заранее исключают строки кэша, которые перекрываются с наблюдаемым адресом памяти).

Сущность изобретения

[0008] По меньшей мере, некоторые варианты осуществления, описанные в данном документе, улучшают обнаружение точки останова способом, который избегает исключения строк кэша, перекрывающихся с адресами памяти, которые наблюдаются, в то же время сохраняя преимущества предыдущих технологий обнаружения на основе кэша. В частности, вместо исключения строки кэша, которая перекрывается с наблюдаемым адресом памяти, эти варианты осуществления используют один или более "зарезервированных" (или иначе неиспользуемых) битов в поле тэга строки кэша (или аналогичный механизм) для того, чтобы сигнализировать о том, что строка кэша перекрывается с наблюдаемым адресом памяти. Такая практика не только уменьшает число отсутствий нужных данных в кэше, которые возникают, но также предоставляет возможность выполнять эффективные проверки точек останова, когда имеет место последующий доступ в память, затрагивающий строку кэша (т.е. в противоположность исключительно во время отсутствия нужных данных в кэше). В частности, вместо необходимости повторно импортировать строку кэша при последующем доступе к памяти вследствие отсутствия нужных данных в кэше, эффективная проверка точки останова может быть выполнена, когда имеет место попадание в какую-либо строку кэша, которая имеет зарезервированный бит, установленный в поле тега строки кэша. Таким образом, варианты осуществления в данном документе избегают исключений строк кэша в целях обнаружения точки останова и добавляют новый эффективный механизм обнаружения точки останова для существующих строк кэша - то и другое из которых может значительно уменьшать непроизводительные затраты, вызванные отладчиком для обнаружения точек останова во время воспроизведения трассировки.

[0009] В некоторых вариантах осуществления конфигурирование кэша для обнаружения точки останова включает в себя идентификацию адреса памяти, который должен наблюдаться, и затем определение того, действительно ли строка кэша, перекрывающаяся с адресом памяти, уже существует в кэше. Если так, вариант осуществления включает в себя установку флага в поле тега строки кэша. Иначе, вариант осуществления может обрабатывать отсутствие нужных данных в кэше и устанавливать флаг в поле тега вновь импортированной строки кэша или может просто заканчиваться.

[0010] В других вариантах осуществления выполнение обнаружения точки останова через кэш включает в себя обнаружение события доступа к памяти и затем идентификацию того, совпадает ли какая-либо строка кэша из кэша с адресом, ассоциированным с доступом к памяти. Когда строка кэша не совпадает с адресом, ассоциированным с доступом к памяти, вариант осуществления включает в себя определение того, что точка останова не была встречена. Когда строка кэша не совпадает с адресом, ассоциированным с доступом к памяти, вариант осуществления включает в себя идентификацию того, совпадает ли какая-либо строка кэша с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируется. Когда строка кэша не совпадает с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются, вариант осуществления включает в себя выполнение проверки для того, была ли встречена точка останова. Иначе, вариант осуществления выполняет обработку непопадания в кэш, в то же время потенциально выполняя проверку точки останова и/или устанавливая флаг в поле тега вновь импортированной строки кэша.

[0011] Это краткое изложение сущности изобретения приведено для того, чтобы представить в упрощенной форме подборку концепций, которые дополнительно описываются ниже в подробном описании. Данное краткое изложение сущности изобретения не предназначен ни для идентификации ключевых признаков или важнейших признаков заявляемого изобретения, ни для использования в качестве помощи при определении объема заявляемого изобретения.

Краткое описание чертежей

[0012] Чтобы описать способ, которым могут быть получены вышеупомянутые и другие преимущества и признаки изобретения, более подробное описание изобретения, вкратце описанного выше, должно быть представлено посредством ссылки на его конкретные варианты осуществления, которые проиллюстрированы на прилагаемых чертежах. При условии того, что эти чертежи изображают только типичные варианты осуществления изобретения и поэтому не должны рассматриваться как ограничивающие область его применения, изобретение описывается и поясняется с помощью дополнительной специфики и подробностей посредством использования прилагаемых чертежей, на которых:

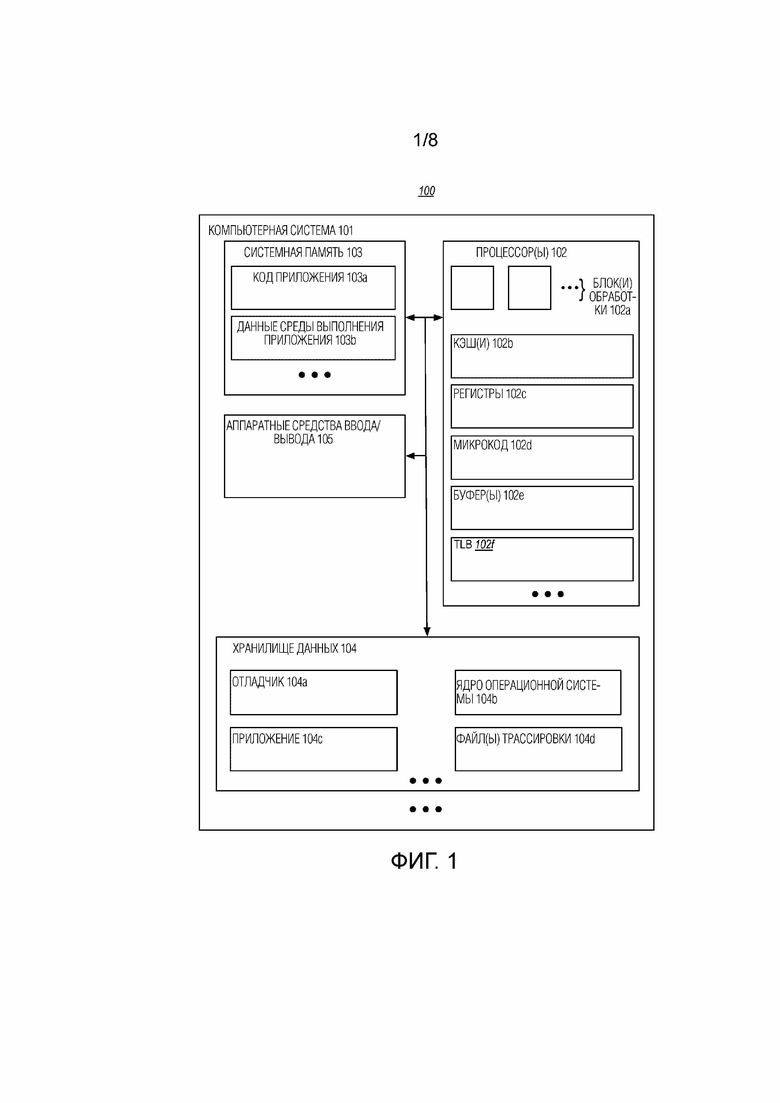

[0013] Фиг. 1 иллюстрирует примерное вычислительное окружение, которое обеспечивает точки останова воспроизведения трассировки на основе кэша, использующие зарезервированные биты поля тега;

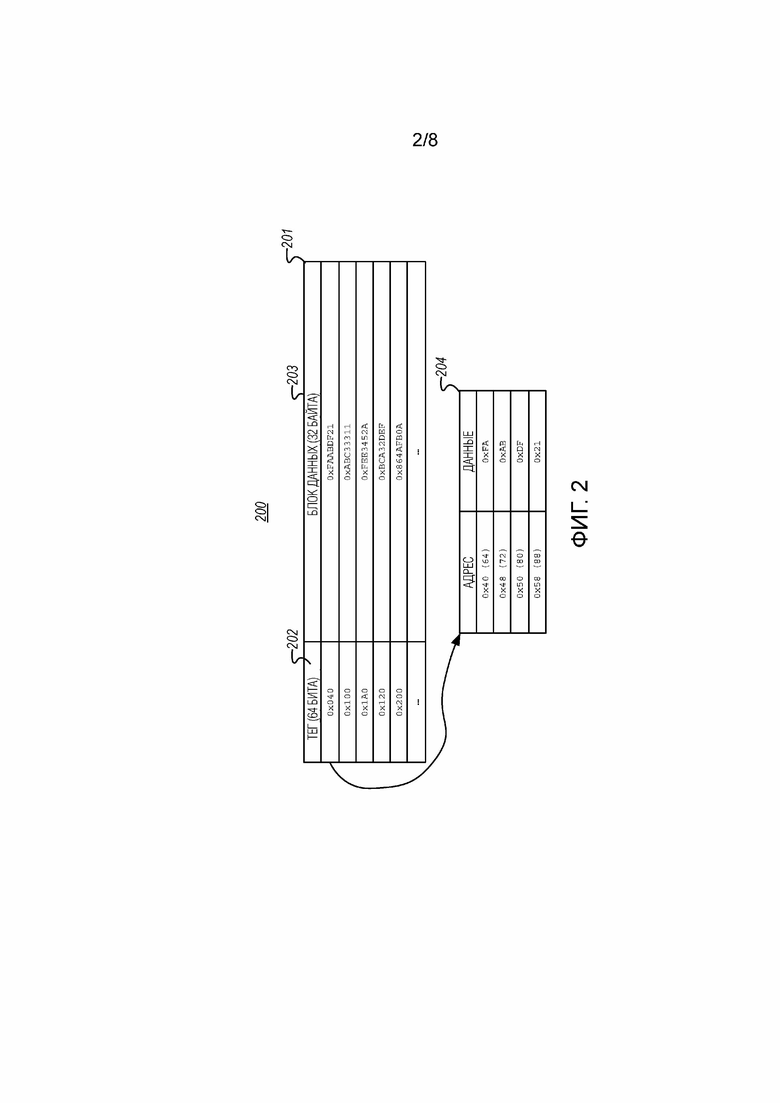

[0014] Фиг. 2 иллюстрирует пример работы кэша;

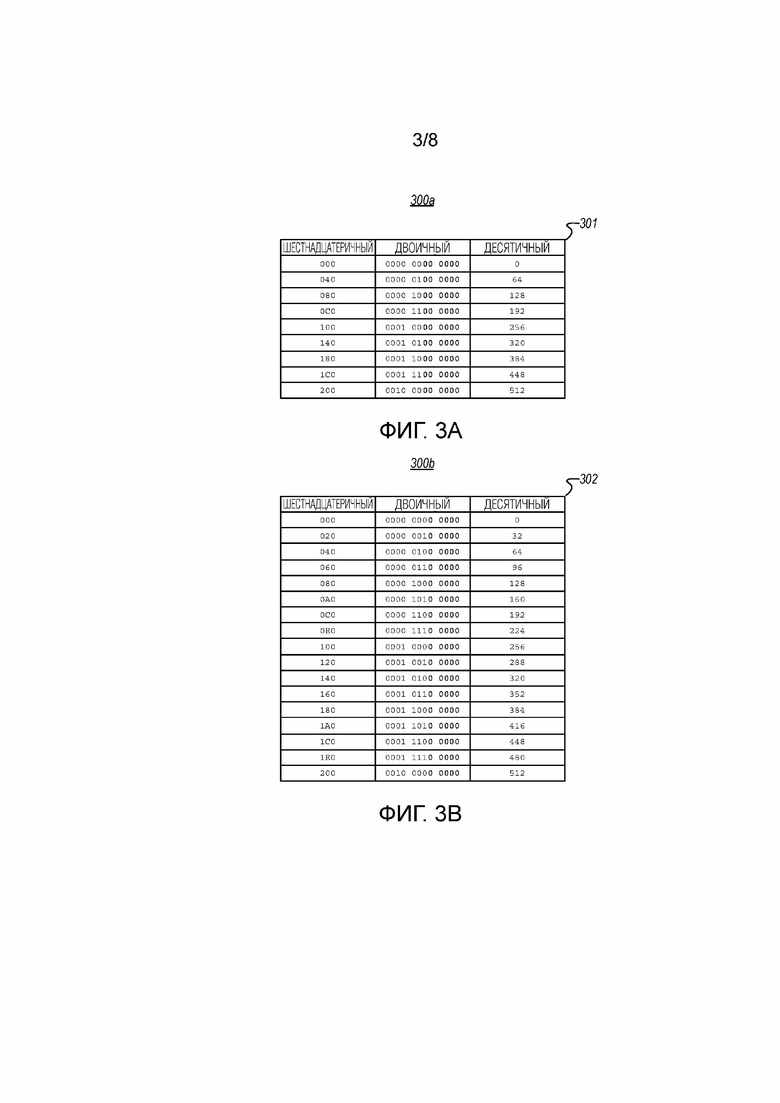

[0015] Фиг. 3A иллюстрирует пример адресов памяти, использующих 64-байтное выравнивание в памяти;

[0016] Фиг. 3B иллюстрирует пример адресов памяти, использующих 32-байтное выравнивание в памяти;

[0017] Фиг. 3C иллюстрирует пример использования меньшего числа битов тегов, чем необходимо для предоставления фактического адреса памяти, на основе пропуска битов, которые всегда являются нулевыми вследствие выравнивания в памяти;

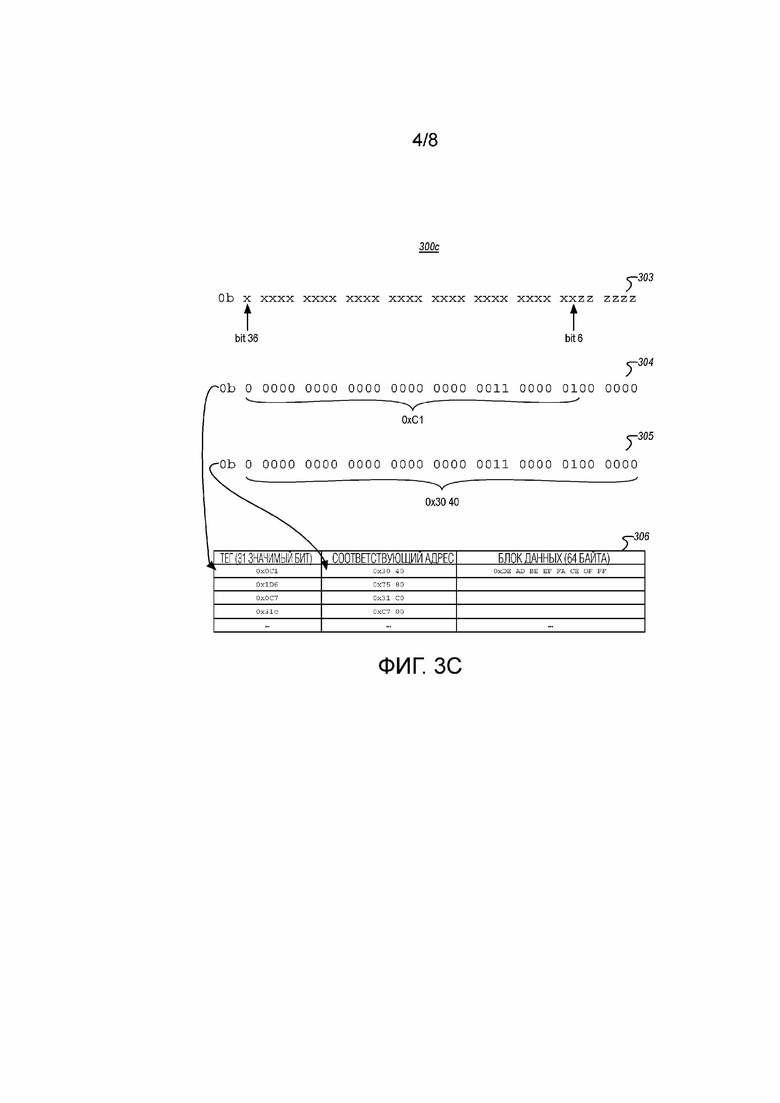

[0018] Фиг. 4 иллюстрирует пример работы точек останова на основе кэша, использующих зарезервированные биты поля тега;

[0019] Фиг. 5 иллюстрирует блок-схему последовательности операций примерного способа для конфигурирования кэша для обнаружения точки останова;

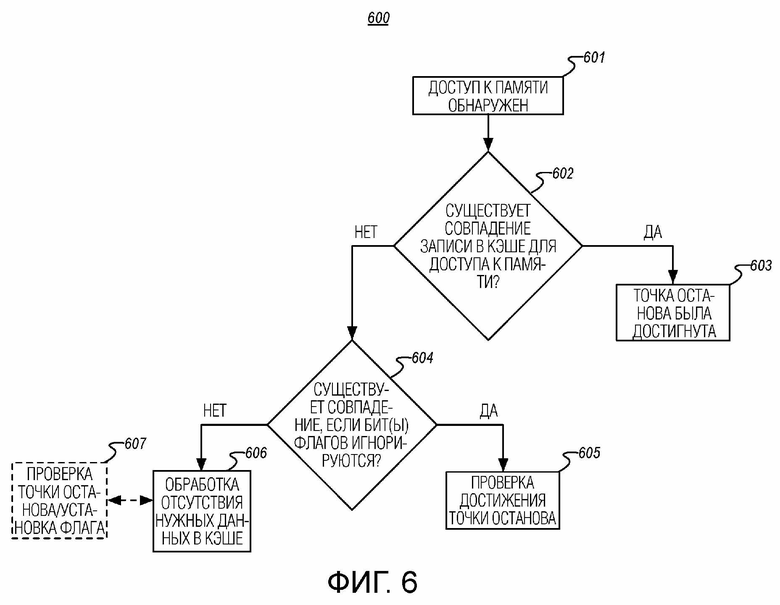

[0020] Фиг. 6 иллюстрирует блок-схему последовательности операций примерного способа для выполнения обнаружения точки останова через кэш; и

[0021] Фиг. 7 иллюстрирует блок-схему последовательности операций примерного способа для выполнения обнаружения точки останова во время отмены инструкции.

Подробное описание изобретения

[0022] По меньшей мере, некоторые варианты осуществления, описанные в данном документе, улучшают обнаружение точки останова способом, который избегает исключения строк кэша, перекрывающихся с адресами памяти, которые наблюдаются, в то же время сохраняя преимущества предыдущих технологий обнаружения на основе кэша. В частности, вместо исключения строки кэша, которая перекрывается с наблюдаемым адресом памяти, эти варианты осуществления используют один или более "зарезервированных" (или иначе неиспользуемых) битов в поле тега строки кэша (или аналогичный механизм) для того, чтобы сигнализировать о том, что строка кэша перекрывается с наблюдаемым адресом памяти. Такая практика не только уменьшает число отсутствий нужных данных в кэше, которые возникают, но также предоставляет возможность выполнять эффективные проверки точек останова, когда существует последующий доступ в память, затрагивающий строку кэша (т.е. в противоположность исключительно во время отсутствия нужных данных в кэше). В частности, вместо необходимости повторно импортировать строку кэша при последующем доступе к памяти вследствие отсутствия нужных данных в кэше, эффективная проверка точки останова может быть выполнена, когда имеет место попадание в какую-либо строку кэша, которая имеет зарезервированный бит, установленный в поле тега строки кэша. Таким образом, варианты осуществления в данном документе избегают исключений строки кэша в целях обнаружения точки останова и добавляют новый эффективный механизм обнаружения точки останова для существующих строк кэша - то и другое из которых может значительно уменьшать непроизводительные затраты, вызванные отладчиком для обнаружения точек останова во время воспроизведения трассировки.

[0023] Первоначально, фиг. 1 иллюстрирует примерное вычислительное окружение 100, которое обеспечивает точки останова воспроизведения трассировки на основе кэша, использующие зарезервированные биты поля тега. Как изображено, варианты осуществления могут содержать или использовать компьютерную систему 101 специального или общего назначения, которая включает в себя компьютерные аппаратные средства, такие как, например, один или более процессоров 102, системную память 103, одно или более хранилищ 104 данных и/или аппаратные средства 105 ввода/вывода. В некотором варианте осуществления компьютерная система 101, и компоненты в ней, могут содержать виртуализированное окружение.

[0024] Варианты осуществления в области применения настоящего изобретения включают в себя физические и другие компьютерно-читаемые носители для переноса или хранения компьютерно-исполняемых инструкций и/или структур данных. Такие компьютерно-читаемые носители могут быть любыми доступными носителями, к которым можно осуществлять доступ посредством компьютерной системы 101. Компьютерно-читаемые носители, которые хранят компьютерно-исполняемые инструкции и/или структуры данных, являются компьютерными устройствами хранения. Компьютерно-читаемые носители, которые переносят компьютерно-исполняемые инструкции и/или структуры данных, являются средой передачи данных. Таким образом, в качестве примера, но не ограничения, варианты осуществления изобретения могут содержать, по меньшей мере, два определенно разных вида компьютерно-читаемых носителей: компьютерные устройства хранения и среду передачи данных.

[0025] Компьютерные носители хранения являются физическими и материальными аппаратными устройствами, которые хранят компьютерно-исполняемые инструкции и/или структуры данных. Компьютерные устройства хранения включают в себя различные компьютерные аппаратные средства, такие как RAM, ROM, EEPROM, твердотельные накопители ("SSD"), флэш-память, память на фазовых переходах ("PCM"), накопитель на оптических дисках, накопитель на магнитных дисках или другие магнитные устройства хранения, или любые другие аппаратные устройство(а), которые могут быть использованы для хранения программного кода в форме компьютерно-исполняемых инструкций или структур данных, и к которым можно осуществлять доступ и исполнять их посредством компьютерной системы 101, чтобы реализовывать описанную функциональность изобретения. Таким образом, например, компьютерные устройства хранения могут включать в себя изображенную системную память 103, изображенное хранилище 104 данных, которое может хранить компьютерно-исполняемые инструкции и/или структуры данных, или другое хранилище, такое как хранилище процессора, как обсуждается позже.

[0026] Среда передачи данных может включать в себя сеть и/или линии передачи данных, которые могут быть использованы для передачи программного кода в форме компьютерно-исполняемых инструкций или структур данных, и к которым можно осуществлять доступ посредством компьютерной системы 101. "Сеть" определена как одна или более линий передачи данных, которые предоставляют возможность передачи электронных данных между компьютерными системами и/или модулями и/или другими электронными устройствами. Когда информация передается или предоставляется по сети или другому коммуникационному соединению (либо проводному, беспроводному, либо комбинации проводного или беспроводного) в компьютерную систему, компьютерная система может рассматривать соединение как среду передачи данных. Комбинации вышеперечисленного также следует включать в число машиночитаемых носителей. Например, аппаратные средства 105 ввода/вывода могут содержать аппаратные средства сетевого взаимодействия (например, проводной или беспроводной модуль сетевого интерфейса), которые соединяют с сетью и/или линией передачи данных, которая может быть использована для передачи программного кода в форме компьютерно-исполняемых инструкций или структур данных.

[0027] Дополнительно, при достижении различных компонентов компьютерной системы программный код в форме компьютерно-исполняемых инструкций или структур данных может передаваться автоматически из среды передачи данных на компьютерные устройства хранения (или наоборот). Например, компьютерно-исполняемые инструкции или структуры данных, принятые по сети или линии передачи данных, могут быть буферизованы в RAM в аппаратных средствах сетевого взаимодействия и затем, в конечном счете, переданы в системную память 103 и/или в менее энергозависимые компьютерные устройства хранения (например, хранилище 104 данных) в компьютерной системе 101. Таким образом, следует понимать, что компьютерные устройства хранения могут быть включены в компоненты компьютерной системы, которые также (или даже главным образом) используют среду передачи данных.

[0028] Компьютерно-исполняемые инструкции содержат, например, инструкции и данные, которые, когда исполняются в процессоре(ах) 102, инструктируют компьютерной системе 101 выполнять некую функцию или группу функций. Компьютерно-исполняемые инструкции могут быть, например, двоичными кодами, инструкциями промежуточного формата, такими как на языке ассемблера, или даже исходным кодом.

[0029] Специалисты в данной области техники поймут, что изобретение может быть применено на практике в сетевых вычислительных окружениях со многими типами конфигураций компьютерной системы, включающими в себя персональные компьютеры, настольные компьютеры, портативные компьютеры, процессоры для обработки сообщений, карманные устройства, многопроцессорные системы, микропроцессорную или программируемую бытовую электронную аппаратуру, сетевые ПК, миникомпьютеры, мейнфреймы, мобильные телефоны, PDA, планшеты, пейджеры, маршрутизаторы, коммутаторы и т.п. Изобретение также может быть применено на практике в распределенных системных окружениях, где локальная и вытесненная компьютерные системы, которые связаны (либо проводными линиями передачи данных, беспроводными линиями передачи данных или комбинацией проводных и беспроводных линий передачи данных) через сеть, обе выполняют задачи. По существу, в распределенном системном окружении компьютерная система может включать в себя множество составляющих компьютерных систем. В распределенном системном окружении программные модули могут размещаться как на локальных, так и на удаленных запоминающих устройствах.

[0030] Как иллюстрировано, хранилище 104 данных может хранить компьютерно-исполняемые инструкции и/или структуры данных, представляющие код приложения, такого как, например, отладчик 104a, ядро 104b операционной системы и приложение 104c. Хранилище 104 данных может также хранить другие типы данных, такие как один или более файл(ов) 104d отладки. Когда код приложения исполняется (например, с помощью процессора(ов) 102), системная память 103 может хранить соответствующие данные среды выполнения, такие как структуры данных среды выполнения, компьютерно-исполняемые инструкции и т.д. Таким образом, фиг. 1 иллюстрирует системную память 103 как включающую в себя код 103a приложения и данные 103b среды выполнения приложения. В то время как файл(ы) 104d трассировки изображаются как хранящиеся в хранилище 104 данных, они могут также быть записаны исключительно или временно в системной памяти 103, или на некотором другом устройстве хранения (например, в буфере(ах) 102e в процессоре(ах) 102).

[0031] Отладчик 104a может осуществлять трассировку выполнения в процессоре(ах) 102 и/или воспроизводить трассировку, записанную в файле(ах) 104d трассировки. Например, отладчик 104a может трассировать выполнение приложения 104c и сохранять результирующие данные трассировки (например, значения регистров, значения памяти и т.д.) в файле(ах) 104d трассировки. Дополнительно, или альтернативно, отладчик 104a может воспроизводить трассированное исполнение приложения 104c из файла(ов) 104d трассировки, выполняя код приложения 104c в процессоре(ах) 102, в то же время предоставляя этот код с трассированными данными (например, значениями регистров, значениями памяти и т.д.) из файла(ов) 104d трассировки в соответствующие моменты времени. Тогда как, для краткости, эта функциональность записи и воспроизведения изображается как одни блок (т.е., отладчик 104a), будет понятно, что эта функциональность может быть разделена на различные приложения или компоненты.

[0032] Например, модуль записи трассировки может быть частью отладчика 104a, или он может быть отдельным приложением или встроенным в другой компонент программного обеспечения, такой как ядро 104b операционной системы, гипервизор и т.д. Модуль записи трассировки может также существовать в полностью другой компьютерной системе. Таким образом, файл(ы) 104d трассировки могут происходить из другой компьютерной системы и передаваться (например, с помощью аппаратных средств 105 ввода/вывода) в компьютерную систему 101 для воспроизведения посредством отладчика 104. В целом, модуль записи трассировки записывает выполнение одного или более фрагментов кода приложения 104c в процессоре(ах) 102 или в некоторой другой компьютерной системе, в то же время сохраняя файлы трассировки (например, значения памяти, считанные посредством инструкций кода, значения регистров, дополняющих инструкции кода, и т.д.) в файл(ы) 104d трассировки. Затем, компонент воспроизведения трассировки может повторно выполнять фрагмент(ы) кода в процессоре(ах) 102, в то же время дополняя этот код данными трассировки из файла(ов) 104d трассировки, так что код исполняется практически таким же образом, как он выполнялся во время трассировки.

[0033] Фиг. 1 также включает в себя упрощенное представление внутренних компонентов аппаратных средств процессора(ов) 102, часто называемых центральным процессором (CPU). Как иллюстрировано, каждый процессор 102 включает в себя множество блоков 102a обработки. Каждый блок обработки может быть физическим (т.е., физическим ядром процессора) и/или логическим (т.е., логическим ядром, представленным физическим ядром, которое поддерживает гиперпоточность, в которой более чем один поток приложения выполняется одновременно в физическом ядре). Таким образом, например, даже если процессор 102 может в некоторых вариантах осуществления включать в себя единственный физический блок обработки (ядро), он может включать в себя два или более блоков 102a обработки, представленных посредством этого единственного физического блока обработки.

[0034] Каждый блок 102a обработки выполняет процессорные инструкции, которые определяются приложениями, и при этом инструкции выбираются среди предварительно определенной архитектуры набора инструкций процессора. Конкретная архитектура набора инструкций каждого процессора 102 изменяется на основе производителя процессора и модели процессора. Общеизвестные архитектуры набора инструкций включают в себя IA-64 и IA-32 архитектуры от INTEL, INC., архитектуру AMD64 от ADVANCED MICRO DEVICES, INC., и различные архитектуры RISC Machine ("ARM") от ARM HOLDINGS, PLC, хотя значительное число других архитектур наборов инструкций существует и может быть использовано настоящим изобретением. В целом, "инструкция" является наименьшим внешне видимым (т.е. внешним по отношению к процессору) блоком кода, который является исполняемым посредством процессора.

[0035] Каждый блок 102a обработки получает процессорные инструкции из одного или более процессорных кэша(ей) 102b и выполняет процессорные инструкции на основе данных в кэше(ах) 102b, на основе данных в регистрах 102c (т.е. основывающиеся на аппаратных средствах места хранения, которые определяются на основе архитектуры набора инструкций процессора(ов) 102), и/или без входных данных. В целом, кэш(и) 102b включают в себя небольшой объем (т.е. небольшой относительно физического объема системной памяти 103) оперативного запоминающего устройства, которое хранит процессорные копии фрагментов системной памяти 103. Например, когда выполняется приложение 104c, кэш(и) 102b хранят подмножество кода 103a приложения среды выполнения в секции кэша кода для кэша(ей) 102b и хранит данные 103b приложения среды выполнения (например, переменные, структуры данных и т.д.) в секции кэша данных для кэша(ей) 102b. Если блок(и) 102a обработки требуют данные, еще не сохраненные в кэше(ах) 102b, тогда возникает "отсутствие нужных данных в кэше", и эти данные выбираются из системной памяти 103 (потенциально исключая некоторые другие данные из кэша(ей) 102b).

[0036] В то время как большая часть работы процессора(ов) 102 определяется в жестко закодированной логике (т.е. схеме), некоторая часть работы процессора(ов) 102 может быть определена с помощью микрокода 102d процессора. В целом, микрокод 102d содержит инструкции, сохраненные в процессорной памяти (например, на компьютерном носителе хранения), которые являются исполняемыми процессором(ами) 102 для управления работой процессора(ов) 102. В некоторых процессорах микрокод 102d может быть перепрограммируемым, так что микрокод 102d может быть перепрограммирован после производства. Кроме того, процессор(ы) 102 могут включать в себя другие аппаратные средства, которые могут использоваться одной или более реализациями точек останова воспроизведения трассировки на основе кэша с помощью зарезервированных (или иначе неиспользуемых) битов поля тега. Эти другие аппаратные средства, включающие в себя буфер(ы) 102 и буфер быстрой переадресации (TLB) 102f, обсуждаются позже в связи с описанием таких реализаций.

[0037] В соответствии с вариантами осуществления в данном документе, отладчик 104a использует кэш для того, чтобы обнаруживать, когда доступ к памяти встречает определенную точку останова. Если реализовано в программном обеспечении, этот кэш может быть кэшем в оперативной памяти, таким как кэш, сохраненный в системной памяти 103. Если реализовано в аппаратных средствах, этот кэш может быть аппаратным кэшем, таким как один или более кэш(ей) 102b. Для иллюстрации этих идей, в качестве вступительной части фиг. 2 иллюстрирует пример 200 работы кэша 201 согласно одному или более вариантам осуществления.

[0038] В частности, фиг. 2 представляет кэш 201 как множество строк кэша (т.е. изображенные строки), каждая из которых включает в себя множество полей (т.е. изображенные столбцы). Как указано эллипсами, кэш 201 может хранить значительное число строк кэша и не ограничивается пятью показанными. Как показано, каждая строка кэша может включать в себя, по меньшей мере, тег 202 и блок 203 данных (хотя дополнительные столбцы могут быть возможны). Когда используется в этом описании и в формуле изобретения, тег 202 может включать в себя любые метаданные строки кэша (включая неадресные данные), которые используются для идентификации строки кэша, сопоставленной для рассматриваемого адреса памяти. Отдельная конфигурация кэша 201 может изменяться в зависимости от архитектуры процессора и модели памяти, хотя в изображенном примере каждая строка кэша включает в себя 64-битный тег 202 и 32-байтовый блок 203 данных. В целом, тег 202 хранит, по меньшей мере, адрес памяти (например, физический адрес в системной памяти 103), в то время как блок 203 данных хранит текущее значение для этого адреса памяти.

[0039] Когда отсутствие нужных данных в кэше возникает для отдельного адреса памяти во время выполнения в процессоре(ах) 102, этот адрес памяти (и, в необязательном порядке, дополнительные метаданные) помещается в тег 202 отдельной строки кэша в кэше 201, и значение, сохраненное по этому адресу памяти в системной памяти 103 (или значение, сохраненное по этому адресу памяти в некотором другом кэше), помещается в блок 203 данных для этой строки кэша. Это значение может изменяться во время выполнения программы, и обновленное значение помещается обратно в системную память 103 (или некоторый другой кэш), когда строка кэша исключается. На фиг. 2 для кэша 201 показаны пять примерных адресов памяти (например, 0×040, 0×100, 0×1A0, 0×120 и 0×200) и соответствующие значения памяти.

[0040] Отметим, единственная строка кэша может "охватывать" множество адресов памяти. Для иллюстрации, в кэше 201 каждая строка кэша хранит 32 байта данных, которые начинаются по адресу, сохраненному в теге 202. Однако, архитектура процессора и модель памяти могут разрешать указание адресов памяти более детально по сравнению с каждыми 32 байтами. Например, предположим в целях этого примера, что только архитектура процессора и модель памяти предоставляют возможность указания адресов памяти с 8-байтовой детальностью. Это означает, что каждая строка кэша в кэше 201 фактически "охватывает" четыре адресуемых адреса памяти (каждый соответствует 8-байтовому значению). Для того, чтобы иллюстрировать это, фиг. 2 включает в себя таблицу 204, которая разбивает первую строку кэша для кэша 201 на эти четыре сегмента. Как показано в таблице 204, и предполагая архитектуру с прямым порядком байтов, эта строка кэша фактически "охватывает" адрес памяти 0×40 (десятичный 64), хранящий 8-байтовое значение 0xFA, адрес памяти 0×48 (десятичный 72), хранящий 8-байтовое значение 0xAB, адрес памяти 0×50 (десятичный 80), хранящий 8-байтовое значение 0xDF, и адрес памяти 0×58 (десятичный 88), хранящий 8-байтовое значение 0×21.

[0041] Как кратко упомянуто, варианты осуществления в данном документе используют один или более "зарезервированных" или иначе неиспользуемых битов адреса в поле тега строки кэша в качестве флагов, чтобы указывать, перекрывается ли строка кэша с наблюдаемым адресом памяти. Как будет объяснено более подробно ниже, эти биты могут иметь возможность резервирования или неиспользования на основе одного или обоих из выравнивания в памяти (т.е., приводящего в результате к зарезервированным "младшим" битам) или использования процессором меньшего числа битов для адресации памяти по сравнению с физически доступным в кэше (т.е., приводящего в результате к зарезервированным "старшим" битам). Как будет понятно с учетом последующего описания, бит может быть "зарезервирован" или неиспользуемым для использования в качестве флага, когда бит (a) не используется для однозначного решения о том, существует ли адрес в кэше, и когда бит (b) является доступным для выполнения определений, после того как проверка первой строки кэша указывает несовпадение в кэше, и/или доступным для выполнения определений о том, существует ли адрес в кэше.

[0042] Первоначально, фиг. 3A и 3B иллюстрируют примеры зарезервированных битов вследствие выравнивания в памяти. Будет понятно, что, в то время как многие запоминающие устройства являются детально адресуемыми (например, такими как с 8-байтовыми приращениями в простом примере выше, хотя фактические процессоры могут разрешать более детальные доступы к памяти), кэши могут разрешать тегам строки кэша лишь адресацию на более грубом уровне, таком как каждые 32 или 64 байта. Таким образом, кэш часто называется "выровненной памятью" с 32 или 64-байтовыми границами. Такое выравнивание в памяти может упрощать реализации шин кэша и памяти (т.е. физические компоновки аппаратных средств) и может увеличивать скорости доступа к памяти. Побочным эффектом выравнивания в памяти является то, что адреса, сохраненные в поле тега строки кэша, всегда будут иметь некоторое число "младших" битов, которые равны нулю. В некоторых реализациях CPU эти всегда нулевые младшие биты фактически не хранятся в поле тега. В некоторых реализациях CPU эти всегда нулевые младшие биты не проверяются, когда исследуется, существует ли адрес памяти в строке кэша. Точное число этих битов изменяется на основе числа байтов, используемых для выравнивания в памяти. Фиг. 3A иллюстрирует пример 300a адресов памяти, использующих 64-байтовое выравнивание в памяти, в то время как фиг. 3B иллюстрирует пример 300b адресов памяти, использующих 32-байтовое выравнивание в памяти.

[0043] В частности, фиг. 3A иллюстрирует таблицу 301, которая иллюстрирует девять примерных адресов памяти - выраженных в шестнадцатеричной, двоичной и десятичной формах - начинающихся с нулевого адреса и идущих до адреса 512 в 64-байтовых приращениях. Как показано жирным в двоичном представлении, когда используется 64-байтовое (т.е. 26) выравнивание в памяти, самые младшие шесть битов адреса всегда являются нулевыми. Фиг. 3B, с другой стороны, включает в себя таблицу 302, которая иллюстрирует семнадцать примерных адресов памяти - выраженных в шестнадцатеричной, двоичной и десятичной формах - также начинающихся с нулевого адреса и идущих до адреса 512 в 32-байтовых приращениях. Как показано жирным в двоичном представлении, когда используется 32-байтовое (т.е. 25) выравнивание в памяти, самые младшие пять битов адреса всегда являются нулевыми. В любом случае, эти младшие биты могут быть обработаны как "зарезервированные" в силу того, что они всегда являются нулевыми вследствие выравнивания в памяти.

[0044] Как было упомянуто, данный процессор может использовать меньшее число битов для адресации памяти по сравнению с числом, которое архитектура процессора теоретически поддерживает. Например, даже если архитектура CPU может поддерживать 64-битную адресацию и указатель (и даже использовать таковую с виртуальными адресами памяти), CPU может использовать меньше 64 бит для адресов памяти в кэше. В качестве примера, если существуют 64 бита, физически доступных в каждом теге кэша, современный CPU INTEL может фактически использовать только 48 или 56 этих битов для адресов памяти, приводя в результате к 16 или 8 битам (соответственно), неиспользуемым процессором для адресации. В качестве другого примера, для CPU, который поддерживает максимум 128 ГБ (т.е. 237) физической памяти и имеет кэш с 64-байтовым (т.е. 26), выровненным на основе физических адресов памяти, тогда тегу кэша будут необходимы, по меньшей мере, 31 бит (т.е. 37-6), чтобы уникально идентифицировать каждую возможную строку кэша, начинающуюся с физического адреса памяти.

[0045] В целом, число битов, используемых для тега кэша, является проектным решением, выполняемым, чтобы упрощать реализацию процессора. В зависимости от реализации кэша, любые дополнительные биты верхнего порядка, выделенные для тега кэша, но не требуемые проектом реализации кэша для однозначной идентификации адреса памяти, могут всегда обрабатываться как нулевые, или они могут полностью игнорироваться. Независимо от их числа, эти старшие биты могут также быть обработаны как "зарезервированные" в силу фактических характеристик адресации памяти процессора.

[0046] Фиг. 3C иллюстрирует пример 300c использования меньшего числа битов тегов, чем необходимо для предоставления фактического адреса памяти, на основе пропуска битов, которые всегда являются нулевыми вследствие выравнивания в памяти. В частности, фиг. 3C показывает возможные биты тега, используемые в CPU, который поддерживает максимум 128 ГБ физической памяти, и который использует 64-байтовые блоки данных в своих строках кэша. Как продемонстрировано в обсуждении выше, 37 битов являются необходимыми, чтобы уникально идентифицировать каждый адрес в 128 ГБ памяти, и нижние шесть битов из этих 37 битов гарантировано должны быть нулевыми при представлении выровненных по 64-байтам адресам памяти. На фиг. 3C это представлено адресом 303, который показывает, что, когда самый значимый бит считается как бит 36, а наименее значимый бит считается как бит 0, 31 бит с бита 36 по бит 6 (указаны как x) являются "значимыми" битами в адресе строки кэша, в то время как шесть битов с бита 5 по бит 0 (указаны как z) гарантировано должны быть нулевыми в адресе строки кэша. По существу, реализации кэша могут выбирать невключение таких нижних шести битов (т.е., битов с 5 по 0) вообще.

[0047] На фиг. 3C каждый из адресов 304 и 305 показывает одинаковое двоичное представление адреса строки кэша. Как показано в адресе 304, когда рассматривается только 31 "значимый" бит этого адреса строки кэша, эти биты могут быть представлены в шестнадцатеричной форме как 0xC1. Как показано в адресе 305, однако, когда рассматриваются все биты этого адреса строки кэша, адрес представляется в шестнадцатеричной форме как 0×30 40. Таблица 306 показывает, в своей первой строке, что тег строки кэша может хранить только эти 31 "значимых" бита (т.е. 0xC1) вместо всех 37 битов (т.е., 0×30 40) адреса строки кэша. Таблица 306 также показывает некоторые другие шестнадцатеричные представления адресов строки кэша, вместе с их соответствующими "значимыми битами".

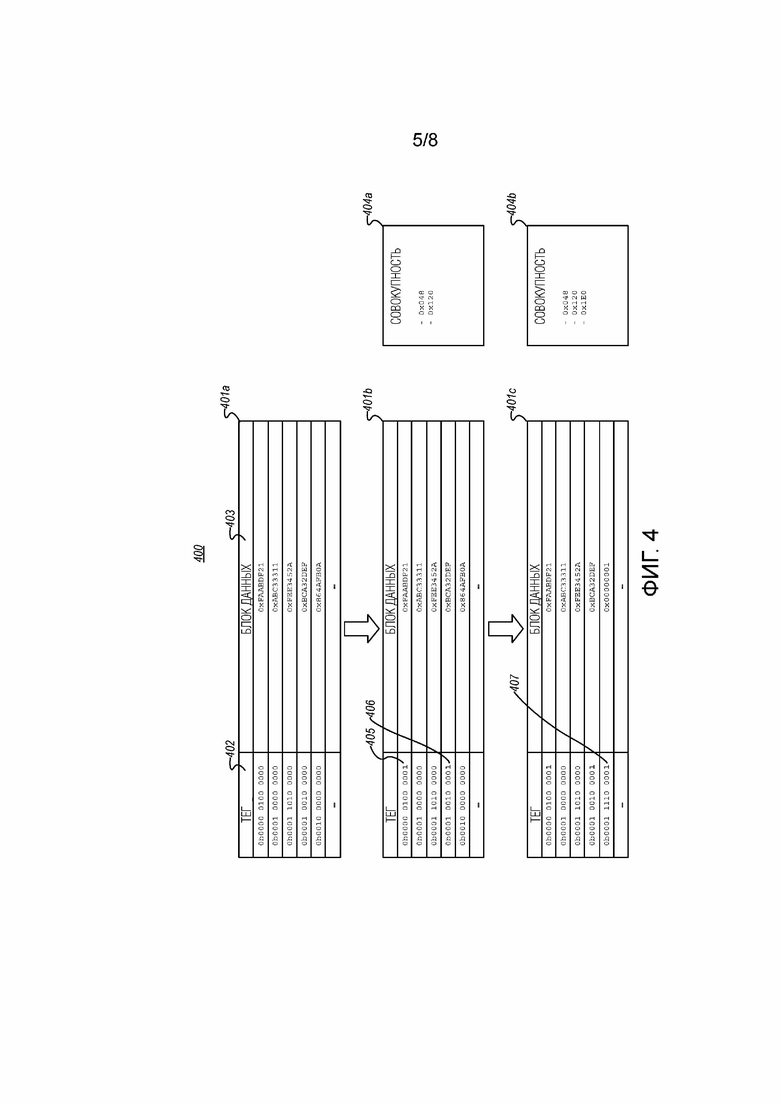

[0048] В контексте кэша 301 на фиг. 3 и только что описанных резервирований битов адреса, фиг. 4 иллюстрирует пример 400 работы точек останова на основе кэша, использующих зарезервированные биты поля тега. Первоначально, пример 400 включает в себя примерный кэш 401a, который соответствует кэшу 201 на фиг. 2. Отметим, каждое значение, показанное в кэше 401a, является идентичным значению, показанному в кэше 201, за исключением того, что значения в теге 402 кэша 401a выражаются в двоичной форме, тогда как значения в теге 202 кэша 201 были выражены в шестнадцатеричной форме. Фиг. 4 опять предполагает архитектуру с прямым порядком байтов.

[0049] Пример 400 также включает в себя кэш 401b, который представляет состояние кэша 401a в последующее время, после того как две точки останова были добавлены в совокупность 404a, содержащую адреса, имеющие точки останова. Как показано в совокупности 404a, эти точки останова включают в себя адреса 0×048 и 0×120, оба из которых соответствуют данным, уже находящимся в кэше 401b. Например, как обсуждалось в связи с фиг. 2, адрес 0×048 охватывается первой строкой кэша, которая хранит 32 байта, начинающихся по адресу 0×040, а адрес 0×120 охватывается четвертой строкой кэша. Вследствие добавления этих точек останова, в кэше 401b зарезервированный младший бит 405 в первой строке кэша был установлен в 1. Этот бит служит в качестве флага, чтобы указывать, что строка кэша охватывает адрес памяти, имеющий точку останова. Аналогично, в кэше 401b зарезервированный младший бит 406 в четвертой строке кэша был установлен в 1, поскольку ее адрес (0×120) также находится в совокупности 404a. В то время как самый младший бит в каждом адресе был использован в качестве флага в этом примере, будет понятно, что реализации могут использовать любой зарезервированный бит в качестве флага.

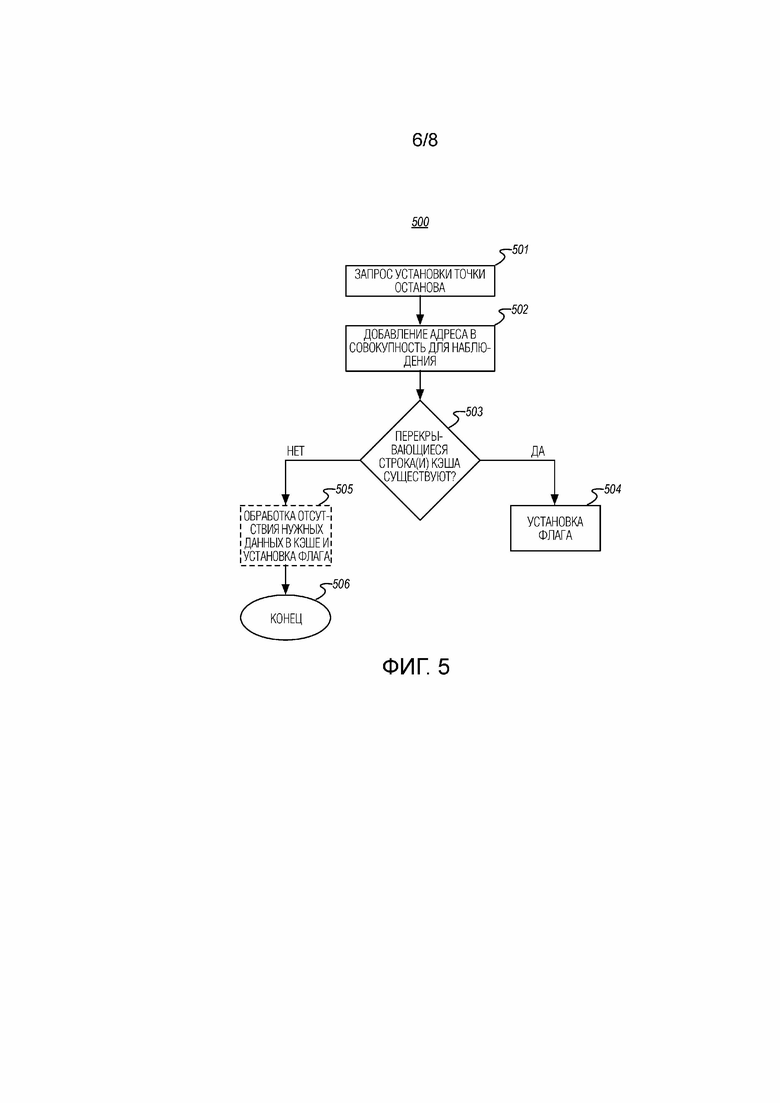

[0050] Фиг. 5 иллюстрирует блок-схему 500 последовательности операций способа 500 для конфигурирования кэша для обнаружения точки останова, причем этот способ может, например, быть использован для установки битов 405 и 406 флагов в кэше 401b. Способ 500 может быть выполнен, например, отладчиком 104a (например, в программной реализации) или может быть выполнен процессором(ами) 102 (например, в аппаратной реализации).

[0051] Способ 500 начинается с этапа 501, когда существует запрос на установку точки останова. Этап 501 может содержать идентификацию адреса памяти, который должен наблюдаться. Например, на основе пользовательского ввода в отладчике 104a, адрес, соответствующий элементу кода, может быть идентифицирован для установки точки останова, или адрес, соответствующий элементу данных, может быть идентифицирован для установки точки наблюдения. В контексте фиг. 4, например, адрес 0×048 или 0×120 может быть идентифицирован в качестве адреса памяти, который должен наблюдаться.

[0052] Способ 500 переходит к этапу 502, когда идентифицированный адрес добавляется в совокупность для наблюдения (т.е. совокупность наблюдаемых адресов). Например, адрес 0×048 и/или 0×120 может быть добавлен в совокупность 404a.

[0053] Способ 500 затем переходит к этапу 503, когда определяется, существуют ли перекрывающие строка(и) кэша для идентифицированного адреса. Другими словами, этап 503 может содержать, на основе, по меньшей мере, идентификации адреса памяти, который должен наблюдаться, определение того, существует ли уже строка кэша, перекрывающаяся с адресом памяти, в кэше. Как обсуждалось выше, такие строки кэша не существуют для адресов 0×048 и 0×120. По сути, когда способ 500 выполняется для каждого из этих адресов, способ 500 перейдет к этапу 504, когда биты флагов для этих строк кэша установлены в поле тега каждой строки кэша (т.е. как отражено в кэше 401b). Если существующая строка кэша не должна была существовать, тогда способ 500 может заканчиваться на этапе 506, без установки каких-либо битов флагов (как показано). Однако, как показано на этапе 505, он может, в необязательном порядке, обрабатывать отсутствие нужных данных в кэше по идентифицированному адресу и устанавливает флаг в теге вновь импортированной строки кэша.

[0054] Например, предположим, что существует запрос на добавление нового адреса 0×1E0 в качестве точки останова. При выполнении способа 500 по адресу 0×1E0, адрес будет добавлен в совокупность на этапе 502 (т.е. как показано в совокупности 404b). Затем, на этапе 503 будет определено, что перекрывающая строка кэша не существует для адреса 0×1E0. Способ 500 может просто заканчиваться на этапе 506, либо способ 500 может выполнять обработку отсутствия нужных данных в кэше по адресу 0×1E0 и устанавливать флаг на импортированной строке кэша на этапе 505. Выполнение этапа 505 отражается в кэше 401c, где пятая строка кэша (соответствующая адресу 0×200) была исключена и заменена новой строкой кэша, соответствующей адресу 0×1E0, с флагом 407, установленным в теге строки кэша.

[0055] Когда способ 500 устанавливает биты флагов в полях тегов строк кэша, эти биты флагов могут быть зарезервированы на основе поля тега, содержащего больше битов, чем необходимо, чтобы адресовать полное адресное пространство посредством одного или более процессоров, и/или могут быть зарезервированы на основе выравнивания в памяти.

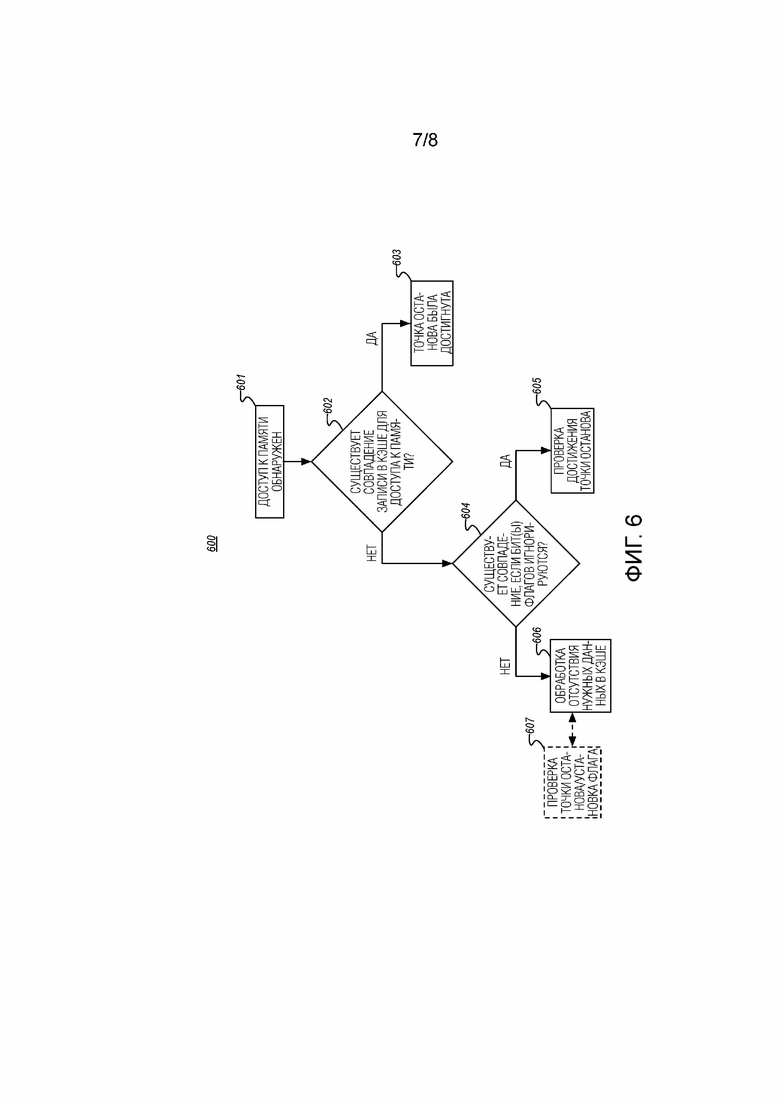

[0056] В контексте кэшей 401b и 401c, которые теперь конфигурируются с флагами точек останова, и в контексте совокупностей 404a и 404b, фиг. 6 иллюстрирует блок-схему последовательности операций примерного способа 600 для выполнения обнаружения точки останова через кэш. Способ 600 может быть выполнен, например, отладчиком 104a (например, в программной реализации) или может быть выполнен процессором(ами) 102 (например, в аппаратной реализации).

[0057] Способ 600 начинается на этапе 601, когда событие доступа к памяти обнаруживается. Это может быть любая операция доступа к памяти к конкретному адресу памяти, но может, более конкретно, быть операцией чтения или записи по адресу памяти. После того как доступ к памяти обнаружен, способ 600 переходит к этапу 602, которое определяет, существует ли совпадение записи в кэше для доступа к памяти. Другими словами, этап 602 может содержать, на основе, по меньшей мере, обнаружения события доступа к памяти, идентификацию того, совпадает ли какая-либо строка кэша для кэша с адресом, ассоциированным с доступом к памяти.

[0058] Например, предположим, что доступ к памяти существует по адресу 0×100, который соответствует второй строке кэшей 401b/401c. Здесь, тег этой второй строки кэша (т.е. 0b0001 0000 0000 или 0×100) будет совпадать с адресом доступа к памяти (т.е. 0×100). Поскольку существует совпадение, способ 600 переходит к этапу 603, где определяется, что точка останова не была достигнута. Другими словами, этап 603 может содержать, когда строка кэша совпадает с адресом доступа к памяти, определение того, что точка останова не была встречена.

[0059] Во втором примере предположим вместо этого, что доступ к памяти существует по адресу 0×120, который, как обсуждалось, хранится в четвертой строке кэшей 401b/401c. Однако, даже если адрес 0×120 действительно кэшируется в кэшах 401b/401c, запрошенный адрес памяти не будет совпадать с каким-либо тегом кэшей 401b/401c. Причина состоит в том, что установка бита флага во второй строке кэша изменила значение тега этой строки кэша на 0×121 вместо 0×120.

[0060] Поскольку, в этом втором примере, не существует совпадения для адреса 0×120, способ 600 переходит к этапу 604, когда определяется, существует ли совпадение, если бит(ы) флагов игнорируются. Другими словами, этап 604 может содержать, когда строка кэша не совпадает с адресом доступа к памяти, идентификацию того, совпадает ли какая-либо строка кэша с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются. Например, биты флагов в каждом теге кэшей 401b/401c могут быть приняты как нулевые или могут быть иначе маскированы, и проверка совпадения может быть повторена. В этом случае, тег второй строки кэша будет теперь предполагаться как 0×120, когда бит(ы) флагов игнорируются, который теперь совпадает с адресом, ассоциированным с доступом к памяти.

[0061] Поскольку теперь существует совпадение, способ 600 переходит к этапу 605, которое проверяет достижение точки останова. Другими словами, этап 605 может содержать, когда строка кэша совпадает с адресом доступа к памяти, когда один или более битов флагов игнорируются, выполнение проверки относительно того, была ли встречена точка останова. Здесь, проверка достижения точки останова может включать в себя сравнение адреса памяти, к которому осуществлен доступ (включающего в себя любой охваченный адрес памяти), с адресами, перечисленными в совокупности 404a/404b. Таким образом, способ 600 может включать в себя определение того, перекрывается ли какой-либо адрес из совокупности наблюдения с множеством адресов памяти, охваченных строкой кэша. Поскольку адрес 0×120 действительно находится в совокупности 404a/404b, точка останова была достигнута.

[0062] В третьем примере предположим, что доступ к памяти существует по адресу 0×048. Данные по этому адресу существуют в первой строке кэшей 401b/401c, который был адресом 0×040 в теге (например, как обсуждалось в связи с таблицей 204 на фиг. 2). Вследствие 32-байтового выравнивания в памяти для кэшей 401b/401c, в этом втором примере этап 602 будет использовать адрес 0×040 в качестве адреса, который "ассоциирован с" доступом к памяти, даже если оригинальный адрес, к которому осуществляется доступ, был 0×048. Аналогично второму примеру, даже если адрес 0×040 действительно кэшируется в кэше 401b, запрашиваемый адрес памяти не будет совпадать с каким-либо тегом кэшей 401b/401c. Причина состоит в том, что установка бита флага в первой строке кэша изменила значение тега этой строки кэша на 0×041 вместо 0×040.

[0063] Поскольку, в этом третьем примере, не существует совпадения для адреса 0×040, способ 600 переходит к этапу 604, когда определяется, существует ли совпадение, если бит(ы) флагов игнорируются. В этом случае, тег второй строки кэша будет теперь предполагаться как 0×040, когда бит(ы) флагов игнорируются, который теперь совпадает с адресом, ассоциированным с доступом к памяти. Поскольку теперь имеет место совпадение на этапе 604, способ 600 переходит к этапу 605, которое проверяет достижение точки останова. Опять, проверка достижения точки останова может включать в себя сравнение адреса памяти, к которому осуществлен доступ (включающего в себя любой охваченный адрес памяти), с адресами, перечисленными в совокупности 404a/404b. В то время как адрес 0×040 не находится в совокупности 404a/404b, охваченный адрес 0×048 находится. Поскольку 0×048 был первоначально адресом, к которому осуществлен доступ, точка останова была достигнута.

[0064] В четвертом примере предположим, что доступ к памяти существует по адресу 0×1E0, и что способ 600 выполняется в отношении кэша 401b и совокупности 404b (т.е. в ситуации, в которой способ 500 закончился на этапе 506 без выполнения этапа 505). Здесь, способ 600 будет выполняться до этапа 604, когда не будет совпадения, даже если бит(ы) флагов игнорируются. По существу, способ 600 перейдет к процессам обработки отсутствия нужных данных в кэше на этапе 606 (т.е. импорту строки кэша в кэш). Другими словами, этап 606 может содержать, когда строка кэша не совпадает с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются, обработку отсутствия нужных данных в кэше.

[0065] В связи с обработкой отсутствия нужных данных в кэше способ 600 может выполнять этап 607, который включает в себя выполнение "проверки строки кэша для точки останова" (например, определение того, перекрывается ли строка кэша, импортированная в кэш на основе обработки отсутствия нужных данных в кэше, с каким-либо адресом из наблюдаемой совокупности) и/или установку флага на вновь импортированной строке кэша. Результатом этапа 607 может быть кэш 401c, в котором пятая строка кэша соответствует 0×1E0 и имеет установленный флаг 407. При выполнении проверки строки кэша для точки останова этап 607 может сравнивать адрес памяти, к которому осуществлен доступ (включающий в себя любой охваченный адрес памяти), с адресами, перечисленными в совокупности 404b, чтобы идентифицировать, что точка доступа была встречена. При выполнении проверки строки кэша для точки останова этап 607 определяет, что адреса находятся в совокупности для наблюдения. Реализации могут всегда проверять всю совокупность адресов или могут включать в себя оптимизации аппаратных средств и/или программного обеспечения, чтобы избегать проверки адресов в совокупности, если соответствующие строки кэша уже находятся в кэше. Например, программное обеспечение может реализовывать такую оптимизацию с помощью двух совокупностей (например, одна с полным списком наблюдения, а другая только с теми адресами, которые не находятся в кэше), или аппаратные средства могут реализовывать такую оптимизацию с помощью флагов в совокупности (например, флаг для каждого адреса, который используется для указания того, находится ли адрес в кэше или нет).

[0066] Принимая во внимание этот четвертый пример, будет понятно, что точки останова могут быть обнаружены посредством способа 600, даже если этап 505 пропускается в способе 500, и даже если строка кэша, охватывающая адрес в совокупности точки останова, была исключена, после того как ее флаг был установлен. Соответственно, реализации могут выбирать пропуск этапа 505 в способе 500 для того, чтобы избегать обработки потенциально ненужных отсутствий данных в кэше.

[0067] Отметим, что, в то время как только один бит флага был использован в вышеупомянутых примерах (т.е. чтобы сигнализировать о том, перекрывается ли строка кэша с адресом, который находится в наблюдаемой совокупности адресов), некоторые реализации могут использовать множество битов флагов, чтобы предоставлять дополнительную функциональность. Например, один или более зарезервированных битов могут быть использованы для указания типа операции доступа к памяти, который будет инициировать достижение точки останова. Таким образом, например, дополнительные зарезервированные биты могут быть использованы, чтобы сигнализировать о том, должна ли точка останова, соответствующая строке кэша, быть остановом по записи, остановом по чтению, остановом по доступу и т.д. Затем, какой-либо из вышеупомянутых этапов, который выполняет проверку строки кэша для точки останова (т.е. этапов 605 и 607) может также использовать эти дополнительные зарезервированные биты, чтобы определять, должен ли тип доступа к памяти инициировать достижение точки останова. Дополнительно, любой из вышеупомянутых этапов, который устанавливает флаг (например, этапов 504 и 607), может содержать установку одного или более флагов в поле тега строки кэша, которые указывают тип точки останова, и в которых тип точки останова может содержать останов по записи, останов по чтению или останов по доступу.

[0068] В некоторых реализациях решение относительно того, какие биты в каждом теге могут быть использованы в качестве зарезервированных битов, выполняется во время загрузки системы, на основе физических характеристик аппаратных средств компьютерной системы 101. Например, если используются младшие биты на основе выравнивания в памяти, число битов, которые могут быть зарезервированы, может быть идентифицировано на основе физических характеристик кэша(ей) 102b (например, используют ли они 32-байтовое или 64-байтовое выравнивание адресов памяти). В другом варианте осуществления, если используются старшие биты на основе числа битов адреса, которые фактически используются для адресации, варианты осуществления могут определять объем физической системной памяти 103, который устанавливается. Поскольку процессор(ы) 102 не могут физически адресовать больше памяти, чем установлено, но проектируются, чтобы поддерживать, по меньшей мере, максимальный объем памяти этого CPU на уровне кэша, число старших битов может быть зарезервировано на основе числа битов, которые будут необходимы, чтобы адресовать установленную физическую память. Это может приводить в результате к тому, что больше старших битов являются доступными по сравнению с просто опорой на число битов адреса, которые используются по умолчанию процессором (например, 48 или 56, как обсуждалось выше) для физической адресации памяти. Таким образом, будет понятно, что в способах 500 и 600 биты флагов могут быть зарезервированы во время загрузки на основе объема доступной физической памяти. Отметим, что зарезервированные биты не должны использоваться только в целях обнаружения точки останова. Скорее, они могут быть использованы, например, как часть механизмов трассировки на основе кэша, используемых отладчиком 104a. На некоторых CPU, по меньшей мере, одно из следующих условий может быть справедливым (a) всегда нулевые младшие биты не хранятся в теге кэша, (b) всегда нулевые младшие биты являются недоступными в целях сравнения совпадения записи в кэше, (c) биты адреса, неиспользуемые по умолчанию процессором для физической адресации памяти, не хранятся в теге кэша, и (d) биты адреса, неиспользуемые по умолчанию процессором для физической адресации памяти, являются недоступными в целях сравнения совпадения записи в кэше. Даже на CPU, где все четыре из вышеописанных условий являются справедливыми, когда CPU конфигурируется, чтобы использовать память менее порогового значения (например, менее 1/2 или 1/4 максимальной физической памяти, которую CPU был спроектирован адресовать), по меньшей мере один бит, доступный в целях сравнения совпадения записи в кэше и сохраненный в теге, становится доступным для использования в качестве флага. Это пороговое значение может быть обнаружено вследствие объема установленной памяти для CPU, посредством BIOS, ограничивающей раскрытую память для CPU меньшим по сравнению с установленным объемом, или посредством инструкции, предоставленной для CPU, указывающей максимальную память для использования (даже если память в ином случае является доступной для CPU).

[0069] Ссылка повсеместно выполнялась на совокупности наблюдаемых адресов памяти (например, совокупности 404a и 404b). В то время как в программных реализациях совокупность может быть сохранена в различных структурах данных в системной памяти 103, аппаратные реализации могут извлекать выгоду из совокупностей, сохраненных в самих процессоре(ах) 102, или которые раскрываются посредством существующих механизмов доступа к памяти. Например, некоторые процессоры реализуют протоколы когерентности кэша (CCP), которые используют каталог. В этих процессорах такие совокупности могут быть сохранены в каталоге CCP. Альтернативно, некоторые процессорные реализации могут включать в себя процессорные буферы (например, буфер(ы) 102e), которые могут быть использованы для хранения этих совокупностей. Например, некоторые аппаратные механизмы трассировки могут включать в себя процессорные буферы, которые могут временно хранить данные трассировки, прежде чем они записываются в файл(ы) 104d трассировки. Некоторые реализации могут также использовать такие буферы для хранения этих совокупностей адресов. В некоторых реализациях доля кэша(ей) 102b может даже использоваться для таких буферов. Принимая во внимание вышесказанное, будет понятно, что в способах 500 и 600 совокупность наблюдаемых адресов может быть сохранена в процессорной памяти, такой как каталог CCP или любой другой процессорный буфер 102e.

[0070] Другие реализации могут использовать TLB 102f процессора(ов) 102 для доступа к данным совокупности адресов. Как будет понятно обычным специалистам в области техники, TLB, в целом, является частью блока управления памятью процессора, и он, в целом, хранит недавние преобразования между виртуальными адресами памяти (например, как видно из процессов, выполняющихся в процессоре(ах) 102) в физические адреса памяти в системной памяти 103 (например, которые фактически используются процессором(ами) 102, включая кэш(и) 102b). Когда процессор(ы) 102 осуществляют доступ по физическому адресу памяти, который не имеет TLB-записи, возникает отсутствие таблицы страниц, которое вызывает доступ к одной или более таблицам страниц в системной памяти 103 для того, чтобы находить соответствующее сопоставление виртуального и физического адресов. Реализации могут хранить совокупность адресов в системной памяти 103 и указывать в каждой записи таблицы страниц, включен ли какой-либо адрес памяти в таблице страниц в совокупность адресов. Таким образом, записи таблицы страниц (которые кэшируются в TLB 102f) могут быть использованы для решения о том, может ли совокупность адресов содержать релевантную запись для данного доступа к памяти. Таким образом, в способе 600 выполнение проверки относительно того, была ли встречена точка останова, может содержать обращение за информацией в TLB, чтобы определять, содержит ли таблица страниц, соответствующая адресу памяти, какой-либо наблюдаемый адрес памяти. Затем, когда таблица страниц, соответствующая адресу памяти, содержит наблюдаемый адрес памяти, способ 600 может включать в себя определение того, перекрывается ли какой-либо адрес из наблюдаемой совокупности с множеством адресов памяти, охваченных строкой кэша.

[0071] Если используются многоуровневые таблицы страниц, вышеупомянутые данные могут быть сохранены только в конечных элементах, что приведет к постоянному времени выполнения. Альтернативно, вышеупомянутые данные могут быть сохранены только в таблицах страниц более верхнего уровня (например, указывающих, что, по меньшей мере, одна таблица страниц более низкого уровня содержит адрес в совокупности адресов), что может выполняться более быстро по сравнению с сохранением в конечных элементах, но что может приводить к большему числу ложных результатов (т.е. поиски в совокупности адресов в ситуациях, когда адрес, по которому осуществляется доступ, фактически не находится в совокупности). Таким образом, этап 502 способа 500 может включать в себя конфигурирование записи таблицы страниц для таблицы страниц, чтобы указывать, что одна или более таблиц страниц или дочерних таблиц страниц содержит наблюдаемый адрес памяти.

[0072] Некоторые реализации могут взаимодействовать с существующими аппаратными механизмами обнаружения точки останова, такими как регистры отладки процессора (например, DR0-DR3 в архитектурах INTEL). Эти реализации предоставляют преимущества обнаружения точки останова на основе кэша (например, фактически неограниченное число точек останова с низкими непроизводительными издержками обнаружения), в то же время сохраняя совместимость с существующим программным обеспечением (например, программным обеспечением, которое использует регистры отладки процессора). Как будет понятно специалистам, множество процессорных архитектур включают в себя быстрые аппаратные средства "сравнения", которые сравнивают адрес памяти, к которому был осуществлен доступ, отменяя инструкцию с адресом памяти, который был помещен в соответствующий регистр отладки. Если имеет место совпадение, тогда достижение точки останова может быть сигнализировано программному обеспечению отладки (например, через регистр, прерывание и т.д.). Реализации могут использовать этот же самый процесс, чтобы сигнализировать когда достижение точки останова было обнаружено через кэш. Например, после того как точка останова на основе кэша была обнаружена, реализации могут вставлять адрес памяти точки останова в соответствующий регистр (например, DR0-DR3 в архитектурах INTEL) и сигнализировать о возникновении точки останова с помощью существующих механизмов (например, через регистр, прерывание и т.д.). По существу, программное обеспечение принимает уведомление о точке останова через традиционные механизмы, но не ограничивается в числе точек останова, которые могут наблюдаться на основе числа доступных регистров отладки. Альтернативно, реализация может устанавливать ловушку для соответствующего регистра отладки (который может не существовать) и реализовывать функциональность регистра отладки полностью через обнаружение точки останова на основе кэша.

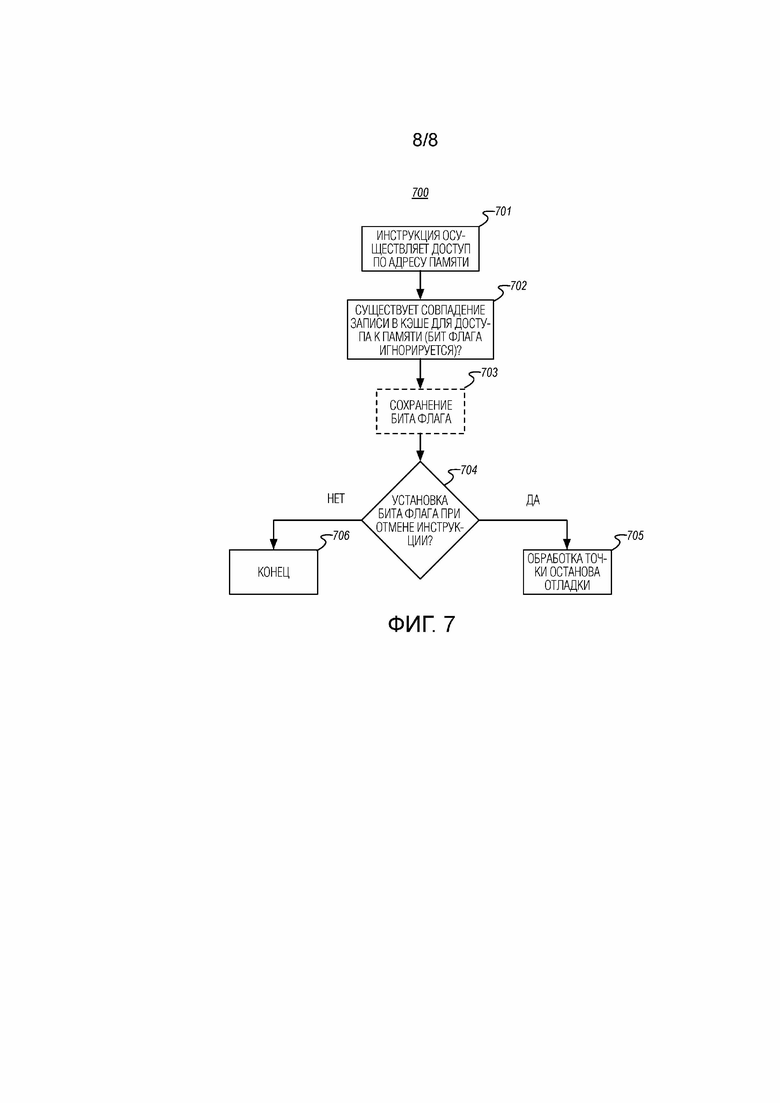

[0073] В некоторых реализациях бит флага проверяется во время отмены инструкции, а не в ответ на определение, что адрес не имеет совпадения в кэше (например, этап 604 способа 600). Например, фиг. 7 иллюстрирует блок-схему последовательности операций примерного способа 700 для выполнения обнаружения точки останова во время отмены инструкции. Способ 700 начинается с этапа 701, в котором инструкция осуществляет доступ по адресу памяти. Например, во время выполнения приложения 104c в процессоре(ах) 102 на основе файла(ов) 104d трассировки, блок 102a обработки может выполнять инструкцию приложения 104c, которая осуществляет доступ к адресу памяти.

[0074] На основе доступа к памяти способ 700 переходит к этапу 702, на котором проверяют, есть ли совпадение записи в кэше для доступа к памяти, если бит(ы) флага игнорируются. Например, процессор(ы) 102 могут проверять кэш(и) 102b, чтобы определять, имеет ли место совпадение строки кэша для доступа к памяти, предполагая, что флаг(и) не установлены (например, как предполагается, должны быть равны нулю). Хотя не показано на фиг. 7, процессор(ы) 102 может предпринимать различные действия в зависимости от результата проверки на этапе 702, такие как чтение данных строки кэша, уже находящихся в кэше(ах) 102b (т.е. если было совпадение), или обработку отсутствия нужных данных в кэше, чтобы создавать приток соответствующих данных строки кэша в кэш(и) 102b (т.е. если не было совпадения). Независимо от того, были ли уже соответствующие данные строки кэша в кэше(ах) 102b или отсутствие нужных данных в кэше было обработано, процессор(ы) 102 могут инициировать выполнение инструкции на основе данных строки кэша (например, посредством инициирования выполнения микроопераций, соответствующих инструкции).

[0075] Как показано на этапе 703, способ 700 может включать в себя этап сохранения бита флага. Например, если было совпадение на этапе 702, процессор(ы) 102 могут сохранять бит флага (независимо от того, установлен он или нет) из тега строки кэша в регистр, как часть микрооперации, или в любом другом месте, которое является доступным во время отмены инструкции. Если не было совпадения на этапе 702, процессор(ы) 102 могут устанавливать включенное состояние бита флага в теге строки кэша как часть обработки отсутствия нужных данных в кэше. Затем, процессор(ы) 102 могут сохранять этот бит флага (установлен он или нет) из тега строки кэша в регистр, как часть микрооперации, или в любом другом месте, которое является доступным во время отмены инструкции.

[0076] Позднее, во время отмены инструкции, этап 704 определяет, был ли бит флага установлен по строке кэша. Например, процессор(ы) 102 могут осуществлять доступ к биту флага по строке кэша, чтобы определять, был ли он задан, или может осуществлять доступ к биту флага из местоположения, в которое он был сохранен на этапе 703 (если он был выполнен). На основе результата этапа 704 способ 700 может заканчиваться на этапе 706 (т.е. если бит флага не был задан), или он может обрабатывать точку останова отладки на этапе 705 (т.е. если бит флага был установлен). Обработка точки останова отладки на этапе 705 может включать в себя установку состояния регистра отладки, как описано выше.

[0077] В частности, как будет понятно обычным специалистам, кэш(и) 102b, как правило содержит многоуровневые кэши, имеющие, например, уровень L1, который поддерживается уровнем L2, который может, в свою очередь, поддерживаться уровнем L3 (и т.д.). В таких многоуровневых кэшах, когда строки кэша перемещаются между уровнями, состояние битов флагов может перемещаться со строками кэша. Таким образом, например, если кэш 401b представляет L1-кэш, и первая строка кэша перемещается в L2-кэш, состояние флага 405 может оставаться внутри в экземпляре строки кэша, которая находится в L2-кэше. Альтернативно, биты флага могут использоваться только в подмножестве уровней кэша (например, только на уровне L1).

[0078] Некоторые варианты осуществления могут учитывать дополнительные типы кэшированных данных (т.е. сверх кэшированного местоположения в памяти), которые внешне не видны. Например, некоторые процессоры могут поддерживать кэш декодированных процессорных инструкций (т.е. их соответствующий микрокод). В этих ситуациях, когда инструкция декодируется, процессор может подтверждать, что инструкция все еще находится в кэше кода (и проверять бит флага) для обнаружения точки останова. Альтернативно, последовательность микрокода может быть модифицирована, чтобы содержать тот факт, что точка останова может быть достигнута, избегая необходимости опрашивать кэш.

[0079] Соответственно, по меньшей мере, некоторые варианты осуществления ускоряют обнаружение точки останова на основе кэша способом, который избегает исключения строк кэша, перекрывающихся с адресами памяти, которые наблюдаются, и, по меньшей мере, некоторые варианты осуществления ускоряют обнаружение точки останова на основе кэша способом, который избегает событий притока в кэш для строк кэша, перекрывающихся с адресами памяти, которые наблюдаются. В частности, вместо исключения строки кэша, которая перекрывается с наблюдаемым адресом памяти, эти варианты осуществления используют один или более "зарезервированных" или неиспользуемых в настоящий момент битов адреса в поле тэга строки кэша для того, чтобы сигнализировать о том, что строка кэша перекрывается с наблюдаемым адресом памяти. Такая практика не только уменьшает число отсутствий нужных данных в кэше и/или притоки в кэш, которые возникают, но также предоставляет возможность выполнять эффективные проверки строк кэша для точек останова, когда существует последующий доступ в память, затрагивающий строку кэша (т.е. в противоположность исключительно во время отсутствия нужных данных в кэше). В частности, вместо необходимости повторно импортировать строку кэша (приток в кэш) при последующем доступе к памяти вследствие отсутствия нужных данных в кэше, эффективная проверка строки кэша для точки останова может быть выполнена, когда существует попадание в какую-либо строку кэша, которая имеет зарезервированный бит, установленный в поле тега строки кэша. Таким образом, варианты осуществления в данном документе избегают вытеснений строки кэша в целях обнаружения точки останова и добавляют новый эффективный механизм обнаружения точки останова для существующих строк кэша - то и другое из которых может значительно уменьшать непроизводительные затраты, вызванные отладчиком для обнаружения точек останова во время воспроизведения трассировки.

[0080] Действие этих преимуществ над предыдущими решениями обнаружения точки останова на основе кэша может наблюдаться в контексте фиг. 4. Например, обращаясь к кэшам 401a и 401b и совокупности 404a, при настройке останова по доступу к восьмибайтовому значению по адресу 0×120 предыдущие решения исключали бы четвертую строку кэша в теге 0×120 из кэша 401a. Настоящие варианты осуществления, однако, избегают этого и вместо этого модифицируют тег строки кэша, чтобы устанавливать бит 406 флага, приводя в результате к тегу 0×121 в кэше 401b.

[0081] Далее, предположим, что выполняющаяся инструкция кода осуществляет доступ по адресу 0×128. В то время как этот адрес не находится в совокупности 404a, он "охватывается" строкой кэша с адресом 0×120. Поскольку предыдущее решение исключит четвертую строку при настройке точки останова для адреса 0×120, этот доступ приведет в результате к отсутствию нужных данных в кэше и притоку в кэш, за которым следует исключение из кэша, после того как инструкция отменяется. Настоящие варианты осуществления, однако, сохраняют строку кэша при настройке точки останова. Таким образом, в то время как существует отсутствие первоначального адреса вследствие установки флага 406, строка кэша позже будет обнаружена с помощью установки флага (т.е. этапа 604). По существу, в настоящих вариантах осуществления инструкция может отменяться без необходимости выполнять какой-либо приток в кэш.

[0082] Наконец, предположим, что другая выполняющаяся инструкция кода осуществляет доступ по адресу 0×120 - который находится в совокупности 404a. Опять, предыдущее решение приведет в результате к другому отсутствию нужных данных в кэше и притоку в кэш. Настоящие варианты осуществления, однако, будут опять иметь отсутствие первоначального адреса вследствие установки флага 406, но строка кэша будет позже обнаружена с помощью установки флага (т.е. этапа 604). По существу, в настоящих вариантах осуществления инструкция может опять отменяться без необходимости выполнять какой-либо приток в кэш.

[0083] Хотя изобретение было описано на языке, характерном для структурных признаков и/или методологических действий, следует понимать, что объем изобретения, определяемый прилагаемой формулой изобретения, необязательно ограничен описанными признаками или этапами, описанными выше, или порядком действий, описанным выше. Наоборот, описанные признаки и этапы раскрываются как примерные формы реализации формулы изобретения.

[0084] Настоящее изобретение может быть осуществлено в других характерных формах без отступления от своего духа или неотъемлемых характеристик. Описанные варианты осуществления должны рассматриваться во всех отношениях только как иллюстративные, а не ограничивающие. Объем изобретения, следовательно, определяется скорее приложенной формулой изобретения, чем предшествующим описанием. Все изменения, которые подпадают под смысл и рамки эквивалентности формулы изобретения, должны охватываться определяемым ею объемом.

Изобретение относится к вычислительной технике. Технический результат заключается в улучшении обнаружения точки останова. Способ, реализуемый в компьютерной системе, которая включает в себя один или более процессоров, для выполнения обнаружения точки останова через кэш, содержит этапы, на которых обнаруживают событие доступа к памяти; на основе обнаружения события доступа к памяти, идентифицируют, совпадает ли какая-либо строка кэша упомянутого кэша с адресом, ассоциированным с доступом к памяти, и когда строка кэша не совпадает, определяют, что точка останова не была встречена; или когда нет строк кэша, совпадающих с адресом, идентифицируют, совпадает ли какая-либо строка кэша с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются, и когда строка кэша не совпадает, когда один или более битов флагов игнорируются, выполняют проверку того, была ли встречена точка останова; или когда нет строк кэша, совпадающих с адресом, ассоциированным с доступом к памяти, когда один или более битов флага игнорируются, обрабатывают отсутствие нужных данных в кэше. 2 н. и 13 з.п. ф-лы, 9 ил.

1. Способ, реализуемый в компьютерной системе, которая включает в себя один или более процессоров, для выполнения обнаружения точки останова через кэш, при этом способ содержит этапы, на которых:

обнаруживают событие доступа к памяти; и

на основе, по меньшей мере, обнаружения события доступа к памяти идентифицируют то, совпадает ли какая-либо строка кэша упомянутого кэша с адресом, ассоциированным с доступом к памяти, и

когда строка кэша не совпадает с адресом, ассоциированным с доступом к памяти, определяют, что точка останова не была встречена; или

когда нет строк кэша, совпадающих с адресом, ассоциированным с доступом к памяти, идентифицируют то, совпадает ли какая-либо строка кэша с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются, и

когда строка кэша не совпадает с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются, выполняют проверку того, была ли встречена точка останова; или

когда нет строк кэша, совпадающих с адресом, ассоциированным с доступом к памяти, когда один или более битов флага игнорируются, обрабатывают отсутствие нужных данных в кэше.

2. Способ по п.1, дополнительно содержащий, когда нет строк кэша, совпадающих с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются, этап, на котором определяют, перекрывается ли строка кэша, импортированная в кэш на основе обработки отсутствия нужных данных в кэше, с каким-либо адресом из совокупности для наблюдения.

3. Способ по п.2, дополнительно содержащий, когда строка кэша, импортированная в кэш, перекрывается с адресом из совокупности для наблюдения, этап, на котором устанавливают бит флага в этой строке кэша.

4. Способ по п.1, в котором выполнение проверки того, была ли встречена точка останова, содержит определение того, перекрывается ли какой-либо адрес из совокупности для наблюдения с множеством адресов памяти, охватываемых строкой кэша.

5. Способ по п.4, в котором совокупность для наблюдения сохраняется в системной памяти.

6. Способ по п.4, в котором совокупность для наблюдения сохраняется в памяти процессора.

7. Способ по п.6, в котором память процессора содержит каталог протоколов поддержки когерентности кэша.

8. Способ по п.1, в котором выполнение проверки того, была ли встречена точка останова, содержит этап, на котором обращаются к буферу быстрого преобразования адреса, чтобы определить, содержит ли таблица страниц, соответствующая адресу памяти, какой-либо наблюдаемый адрес памяти.

9. Способ по п.8, дополнительно содержащий этап, на котором, когда таблица страниц, соответствующая адресу памяти, содержит наблюдаемый адрес памяти, определяют, перекрывается ли какой-либо адрес из совокупности наблюдения с множеством адресов памяти, охватываемых строкой кэша.

10. Способ по п.1, в котором выполнение проверки того, была ли встречена точка останова, содержит помещение адреса строки кэша в аппаратный регистр отладки.

11. Вычислительная система, содержащая:

один или более процессоров; и

один или более машиночитаемых носителей, на которых сохранены машиноисполняемые инструкции, которые конфигурируют один или более процессоров выполнять обнаружение точки останова через кэш, включая, по меньшей мере:

обнаружение события доступа к памяти; и

на основе, по меньшей мере, обнаружения события доступа к памяти идентификацию того, совпадает ли какая-либо строка кэша упомянутого кэша с адресом, ассоциированным с доступом к памяти, и

когда строка кэша не совпадает с адресом, ассоциированным с доступом к памяти, определение того, что точка останова не была встречена; или

когда нет строк кэша, совпадающих с адресом, ассоциированным с доступом к памяти, идентификацию того, совпадает ли какая-либо строка кэша с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются, и

когда строка кэша не совпадает с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются, выполнение проверки того, была ли встречена точка останова; или

когда нет строк кэша, совпадающих с адресом, ассоциированным с доступом к памяти, когда один или более битов флага игнорируются, обработку отсутствия нужных данных в кэше.

12. Компьютерная система по п.11, в которой один или более процессоров содержат упомянутые машиночитаемые носители и упомянутый кэш, и при этом упомянутые машиноисполняемые инструкции содержат микрокод процессора.

13. Компьютерная система по п.11, в которой машиноисполняемые инструкции также конфигурируют один или более процессоров определять, перекрывается ли строка кэша, импортированная в кэш на основе обработки отсутствия нужных данных в кэше, с каким-либо адресом из совокупности для наблюдения, когда нет строк кэша, совпадающих с адресом, ассоциированным с доступом к памяти, когда один или более битов флагов игнорируются.

14. Компьютерная система по п.11, в которой выполнение проверки того, была ли встречена точка останова, содержит определение того, перекрывается ли какой-либо адрес из совокупности для наблюдения с множеством адресов памяти, охватываемых строкой кэша.

15. Компьютерная система по п.14, при этом совокупность для наблюдения сохраняется в памяти процессора.

| Способ получения цианистых соединений | 1924 |

|

SU2018A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| СХЕМА ОТЛАДКИ, СРАВНИВАЮЩАЯ РЕЖИМ ОБРАБОТКИ НАБОРА КОМАНД ПРОЦЕССОРА | 2007 |

|

RU2429525C2 |

Авторы

Даты

2022-04-06—Публикация

2019-06-18—Подача