Перекрестная ссылка

Настоящая заявка испрашивает приоритет по заявкам на выдачу патента Китая №202010037846.8 и 202020081575.1, поданных 14 января 2020 года и озаглавленных как «Схема выборки данных, устройство выборки данных». Содержимое данной заявки на выдачу патента Китая включено в материалы настоящей заявки посредством ссылки.

Область техники

Настоящее изобретение относится к технической области памяти и, в частности, к схеме выборки данных и устройству выборки данных.

Уровень техники

По мере стремительного увеличения скорости передачи сигнала в оперативной памяти LPDDR (Low Power Double Data Rate, с низким энергопотреблением и удвоенной скоростью передачи данных), потери канала связи все больше влияют на качество сигнала, а также могут привести к межсимвольной интерференции.

В предшествующем уровне техники схема эквалайзера (Equalizer) обычно используется на клемме приема (RX) с целью компенсации канала связи. Схема эквалайзера может выбирать CTLE (Continuous Time Linear Equalizer, схема стационарного линейного эквалайзера) или DFE (Decision Feedback Equalizer, схема эквалайзера с решающей обратной связью по решению).

Однако отдельная установка схемы эквалайзера увеличит энергопотребление LPDDR, так что LPDDR не сможет удовлетворить требования к низкому энергопотреблению.

Следует отметить, что информация, раскрытая в приведенном выше разделе «Уровень техники», предназначена только для усиления понимания предпосылок настоящего изобретения. В связи с этим, в данной заявке содержится информация, которая не образует предшествующий уровень техники и уже известна техническому специалисту в данной области.

Раскрытие сущности изобретения

В соответствии с аспектом настоящего изобретения предусмотрена схема выборки данных, схема выборки данных включает в себя: первый модуль выборки данных, второй модуль выборки данных, модуль триггера и модуль эквалайзера с решающей обратной связью. Первый модуль выборки данных подключен к клемме сигнала данных, клемме опорного сигнала, первому узлу, второму узлу, и выполнен с возможностью реагирования на сигналы клеммы сигнала данных и клеммы опорного сигнала, а также воздействия на первый узел и второй узел; второй модуль выборки подключен к первому узлу, второму узлу, третьему узлу и четвертому узлу и выполнен с возможностью реагирования на сигналы первого узла и второго узла, а также воздействия на третий узел и четвертый узел; модуль триггера подключен к третьему узлу, четвертому узлу, первой выходной клемме и второй выходной клемме, и выполнен с возможностью ввода сигнала высокого уровня на первую выходную клемму, ввода сигнала низкого уровня на вторую выходную клемму или ввода сигнала низкого уровня на первую выходную клемму, ввода сигнала высокого уровня на вторую выходную клемму в соответствии с сигналами третьего узла и четвертого узла; модуль эквалайзера с решающей обратной связью параллельно подключен ко второму модулю выборки данных с целью уменьшения межсимвольной интерференции.

В примерном варианте осуществления настоящего изобретения схема выборки данных также включает в себя модуль компенсации дисбаланса, модуль компенсации дисбаланса параллельно подключен ко второму модулю выборки данных и выполнен с возможностью компенсации дисбаланса напряжения во втором модуле выборки данных.

В примерном варианте осуществления настоящего изобретения первый модуль выборки данных также подключен к первой клемме тактового сигнала и выполнен с возможностью запуска действия по выборке данных в ответ на сигнал, поступающий от первой клеммы тактового сигнала; схема выборки данных также включает модуль сброса, причем модуль сброса подключен к первой клемме тактового сигнала, второй клемме тактового сигнала, первому узлу, второму узлу, третьему узлу, четвертому узлу, первой выходной клемме и второй выходной клемме и выполнен с возможностью сброса первого узла и второго узла в ответ на сигнал, поступающий от первой клеммы тактового сигнала, и сброса третьего узла, четвертого узла, первой выходной клеммы и второй выходной клеммы в ответ на сигнал, поступающий от второй клеммы тактового сигнала.

В примерном варианте осуществления настоящего изобретения первый модуль выборки данных включает: первый транзистор P-типа, второй транзистор P-типа и третий транзистор P-типа, первая клемма первого транзистора P-типа подключена к клемме сигнала высокого уровня, управляющая клемма к первой клемме тактового сигнала, а вторая клемма к пятому узлу; первая клемма второго транзистора P-типа подключена ко второй клемме первого транзистора P-типа, управляющая клемма к клемме сигнала данных, а вторая клемма ко второму узлу; первая клемма третьего транзистора P-типа подключена ко второй клемме первого транзистора P-типа, управляющая клемма к клемме опорного сигнала, а вторая клемма к первому узлу.

В примерном варианте осуществления настоящего изобретения второй модуль выборки данных включает: четвертый транзистор N-типа и пятый транзистор N-типа, первая клемма четвертого транзистора N-типа подключена к клемме сигнала низкого уровня, управляющая клемма ко второму узлу, а вторая клемма к третьему узлу; первая клемма пятого транзистора N-типа подключена к клемме сигнала низкого уровня, управляющая клемма к первому узлу, а вторая клемма к четвертому узлу.

В примерном варианте осуществления настоящего изобретения модуль триггера включает: шестой транзистор P-типа, седьмой транзистор N-типа, восьмой транзистор P-типа и девятый транзистор N-типа, первая клемма шестого транзистора P-типа подключена к клемме сигнала высокого уровня, управляющая клемма ко второй выходной клемме, а вторая клемма к первой выходной клемме; первая клемма седьмого транзистора N-типа подключена к третьему узлу, вторая клемма к первой выходной клемме, а управляющая клемма ко второй выходной клемме; первая клемма восьмого транзистора P-типа подключена к клемме сигнала высокого уровня, управляющая клемма к первой выходной клемме, а вторая клемма ко второй выходной клемме; первая клемма девятого транзистора N-типа подключена к четвертому узлу, вторая клемма ко второй выходной клемме, а управляющая клемма к первой выходной клемме.

В примерном варианте осуществления настоящего изобретения модуль эквалайзера с решающей обратной связью включает в себя: первый модуль эквалайзера с решающей обратной связью и второй модуль эквалайзера с решающей обратной связью, первый модуль эквалайзера с решающей обратной связью параллельно подключен между клеммой истока и клеммой стока четвертого транзистора N-типа и выполнен с возможностью компенсации параметров четвертого транзистора N-типа; второй модуль эквалайзера с решающей обратной связью параллельно подключен между клеммой истока и клеммой стока пятого транзистора N-типа и выполнен с возможностью компенсации параметров пятого транзистора N-типа; при этом первый модуль эквалайзера с решающей обратной связью и второй модуль эквалайзера с решающей обратной связью управляются двумя сигналами, обратными друг к другу, для попеременного управления.

В примерном варианте осуществления настоящего изобретения первый модуль эквалайзера с решающей обратной связью включает в себя: множество десятых транзисторов N-типа, множество одиннадцатых транзисторов и множество двенадцатых транзисторов N-типа, первая клемма каждого из множества десятых транзисторов N-типа подключена к третьему узлу, а управляющая клемма ко второму узлу; множество одиннадцатых транзисторов расположено во взаимно-однозначном соответствии с множеством десятых транзисторов N-типа, первая клемма одиннадцатого транзистора подключена ко второй клемме десятого транзистора N-типа, а управляющие клеммы множества одиннадцатых транзисторов подключены к различным клеммам управляющего сигнала; двенадцатый транзистор N-типа расположен во взаимно-однозначном соответствии с одиннадцатым транзистором, первая клемма двенадцатого транзистора N-типа подключена ко второй клемме одиннадцатого транзистора, управляющая клемма подключена к первой клемме управляющего сигнала, а вторая клемма подключена к клемме сигнала низкого уровня.

В примерном варианте осуществления настоящего изобретения второй модуль эквалайзера с решающей обратной связью включает в себя: множество тринадцатых транзисторов N-типа, множество четырнадцатых транзисторов и множество пятнадцатых транзисторов N-типа, первая клемма тринадцатого транзистора N-типа подключена к четвертому узлу, а управляющая клемма к первому узлу; четырнадцатый транзистор расположен во взаимно-однозначном соответствии с тринадцатым транзистором N-типа, первая клемма четырнадцатого транзистора подключена ко второй клемме тринадцатого транзистора N-типа, а управляющие клеммы подключены к разным клеммам управляющего сигнала; пятнадцатый N-транзистор расположен во взаимно-однозначном соответствии с четырнадцатым транзистором, первая клемма пятнадцатого N-транзистора подключена ко второй клемме четырнадцатого транзистора, управляющая клемма к клемме второго управляющего сигнала, а вторая клемма к клемме сигнала низкого уровня; при этом сигналы первой клеммы управляющего сигнала и второй клеммы управляющего сигнала являются взаимно обратными.

В примерном варианте осуществления настоящего изобретения количество десятых транзисторов N-типа, одиннадцатых транзисторов и двенадцатых транзисторов N-типа равно двум.

В примерном варианте осуществления настоящего изобретения количество тринадцатых транзисторов N-типа, четырнадцатых транзисторов и пятнадцатых транзистора N-типа равно двум.

В примерном варианте осуществления настоящего изобретения модуль компенсации дисбаланса включает в себя: первый модуль компенсации дисбаланса и второй модуль компенсации дисбаланса, первый модуль компенсации дисбаланса параллельно подключен между клеммой истока и клеммой стока четвертого транзистора N-типа и выполнен с возможностью компенсации параметров четвертого транзистора N-типа; второй модуль компенсации дисбаланса параллельно подключен между клеммой истока и клеммой стока пятого транзистора N-типа и выполнен с возможностью компенсации параметров пятого транзистора N-типа.

В примерном варианте осуществления настоящего изобретения первый модуль компенсации дисбаланса включает в себя: множество шестнадцатых транзисторов и множество первых конденсаторов, первые клеммы шестнадцатых транзисторов подключены к клеммам сигнала низкого уровня, а управляющие клеммы к разным клеммам управляющего сигнала; первый конденсатор расположен во взаимно-однозначном соответствии с шестнадцатым транзистором, первый конденсатор подключен между второй клеммой шестнадцатого транзистора и третьим узлом.

В примерном варианте осуществления настоящего изобретения второй модуль компенсации дисбаланса включает в себя: множество семнадцатых транзисторов и множество вторых конденсаторов, первые клеммы семнадцатых транзисторов подключены к клеммам сигнала низкого уровня, а управляющие клеммы к разным клеммам управляющего сигнала; второй конденсатор расположен во взаимно-однозначном соответствии с семнадцатым транзистором, причем второй конденсатор подключен между второй клеммой семнадцатого транзистора и четвертым узлом.

В примерном варианте осуществления настоящего изобретения модуль сброса включает в себя: восемнадцатый транзистор N-типа, девятнадцатый транзистор N-типа, двадцатый транзистор P-типа, двадцать первый транзистор P-типа, двадцать второй транзистор P-типа, двадцать третий транзистор P-типа, первая клемма восемнадцатого транзистора N-типа подключена к клемме сигнала низкого уровня, вторая клемма ко второму узлу, а управляющая клемма к клемме первого тактового сигнала; первая клемма девятнадцатого транзистора N-типа подключена к клемме сигнала низкого уровня, вторая клемма к первому узлу, а управляющая клемма к клемме первого тактового сигнала; первая клемма двадцатого транзистора P-типа подключена к клемме сигнала высокого уровня, вторая клемма к третьему узлу, а управляющая клемма ко второй клемме тактового сигнала; первая клемма двадцать первого транзистора P-типа подключена к клемме сигнала высокого уровня, вторая клемма к первому выходу, а управляющая клемма ко второй клемме тактового сигнала; первая клемма двадцать второго транзистора P-типа подключена к клемме сигнала высокого уровня, вторая клемма ко второй выходной клемме, а управляющая клемма ко второй клемме тактового сигнала; первая клемма двадцать третьего транзистора P-типа подключена к клемме сигнала высокого уровня, вторая клемма к четвертому узлу, а управляющая клемма ко второй клемме тактового сигнала.

В соответствии с аспектом настоящего изобретения представлено устройство выборки данных, которое включает в себя множество каскадных схем выборки данных, в которых первая выходная клемма схемы выборки данных верхнего каскада подключена к первой управляющей клемме схемы выборки данных нижнего каскада, вторая выходная клемма схемы выборки данных верхнего каскада подключена ко второй управляющей клемме схемы выборки данных нижнего каскада; первая выходная клемма схемы выборки данных последнего каскада подключена к первой управляющей клемме схемы выборки данных первого каскада, вторая выходная клемма схемы выборки данных последнего каскада подключена ко второй управляющей клемме схемы выборки данных первого каскада.

В примерном варианте осуществления настоящего изобретения устройство выборки данных также содержит множество триггеров. Триггеры расположены во взаимно-однозначном соответствии со схемами выборки данных и выполнены с возможностью фиксации данных с первой выходной клеммы на третьей выходной клемме схемы выборки данных, а также данных с второй выходной клеммы на четвертой выходной клемме схемы выборки данных.

В примерном варианте осуществления настоящего изобретения триггер включает в себя: двадцать четвертый транзистор P-типа, двадцать пятый транзистор P-типа, двадцать шестой транзистор P-типа, двадцать седьмой транзистор P-типа, двадцать восьмой транзистор N-типа, двадцать девятый транзистор N-типа, тридцатый транзистор N-типа, тридцать первый транзистор N-типа, первая клемма двадцать четвертого транзистора P-типа подключена к клемме сигнала высокого уровня, вторая клемма к третьей выходной клемме, а управляющая клемма к первой выходной клемме схемы выборки данных; первая клемма двадцать пятого транзистора P-типа подключена к клемме сигнала высокого уровня, вторая клемма к третьей выходной клемме, а управляющая клемма к четвертой выходной клемме; первая клемма двадцать шестого транзистора P-типа подключена к клемме сигнала высокого уровня, вторая клемма к четвертой выходной клемме, а управляющая клемма к третьей выходной клемме; первая клемма двадцать седьмого транзистора P-типа подключена к клемме сигнала высокого уровня, вторая клемма к четвертой выходной клемме, а управляющая клемма ко второй выходной клемме схемы выборки данных; первая клемма двадцать восьмого транзистора N-типа подключена к клемме сигнала низкого уровня, вторая клемма к третьей выходной клемме, а управляющая клемма к первой выходной клемме схемы выборки данных; первая клемма двадцать девятого транзистора N-типа подключена к клемме сигнала низкого уровня, вторая клемма к третьей выходной клемме, а управляющая клемма к четвертой выходной клемме; первая клемма тридцатого транзистора N-типа подключена к клемме сигнала низкого уровня, вторая клемма к четвертой выходной клемме, а управляющая клемма к третьей выходной клемме; первая клемма тридцать первого транзистора N-типа подключена к клемме сигнала низкого уровня, вторая клемма к четвертой выходной клемме, а управляющая клемма ко второй выходной клемме схемы выборки данных.

В примерном варианте осуществления настоящего изобретения устройство выборки данных содержит четыре схемы выборки данных, устройство выборки данных также содержит схему тактового сигнала, схема тактового сигнала выполнена с возможностью подачи тактовых сигналов выборки на первые клеммы тактового сигнала четырех схем выборки данных. Разность фаз сигналов на первой клемме тактового сигнала соседних схем выборки данных составляет 90 градусов, а период сигнала на первой клемме тактового сигнала в 2 раза больше периода сигнала на клемме сигнала данных.

Следует понимать, что вышеприведенное и последующее описание представлено в качестве примера с целью пояснения и не ограничивают объем настоящего изобретения.

Краткое описание чертежей

Чертежи, представленные здесь, являются составной частью данного описания, которые демонстрируют примерные варианты осуществления, соответствующие настоящему изобретению, а также применяются с целью пояснения принципов работы настоящего изобретения. Очевидно, что графические материалы, представленные в последующем описании являются лишь некоторыми вариантами осуществления настоящего изобретения. Технические специалисты в данной области могут получить прочие графические материалы основываясь на данных графических материалах без применения созидательного труда.

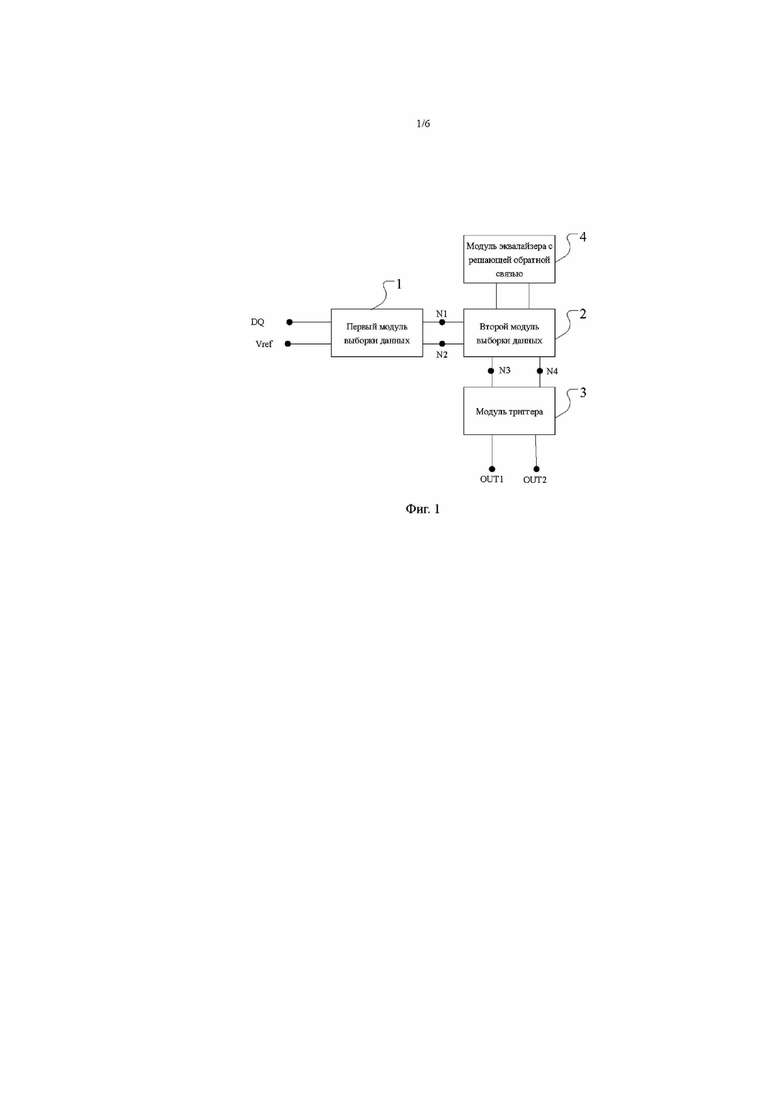

На фиг. 1 показана блок-схема выборки данных, представленная в примерном варианте осуществления настоящего изобретения;

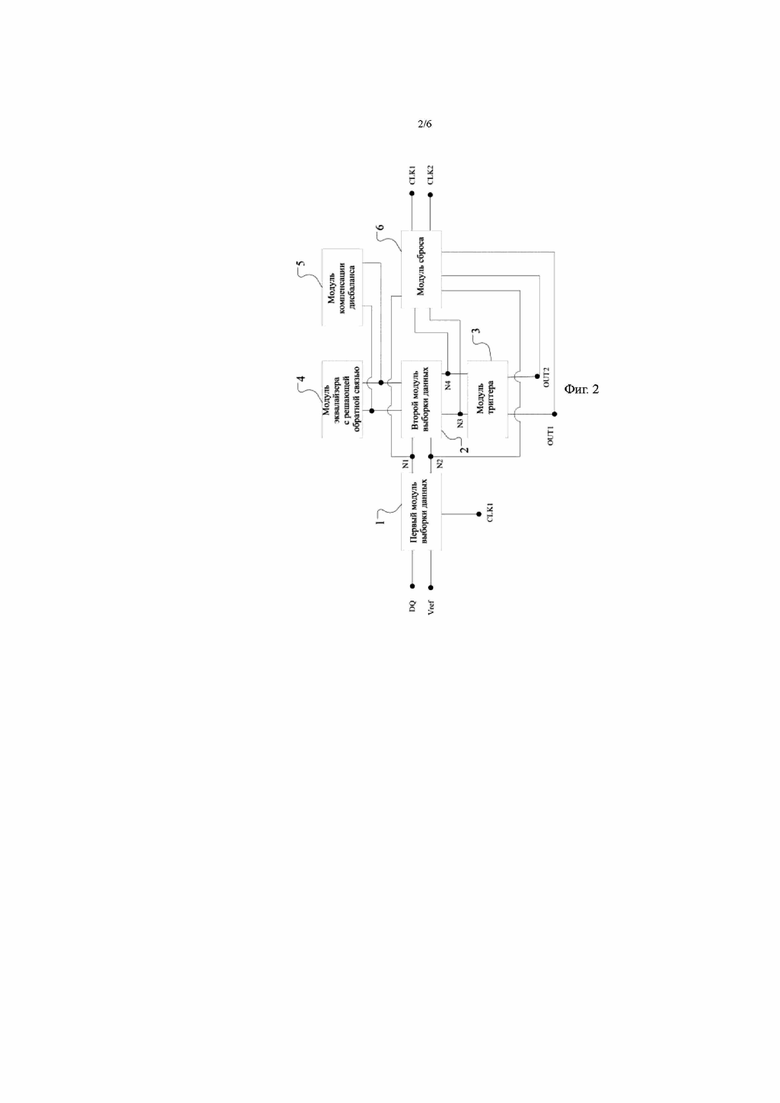

на фиг. 2 показана блок-схема выборки данных, представленная в другом примерном варианте осуществления настоящего изобретения;

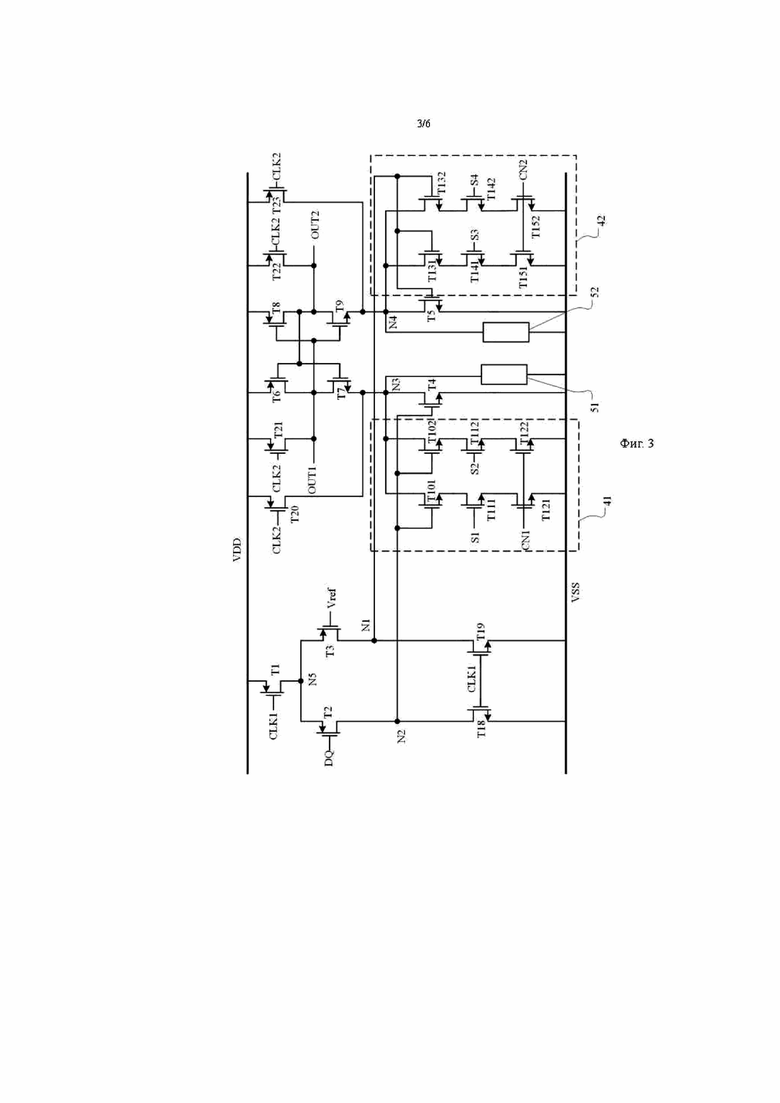

на фиг. 3 показана блок-схема выборки данных, представленная в другом примерном варианте осуществления настоящего изобретения;

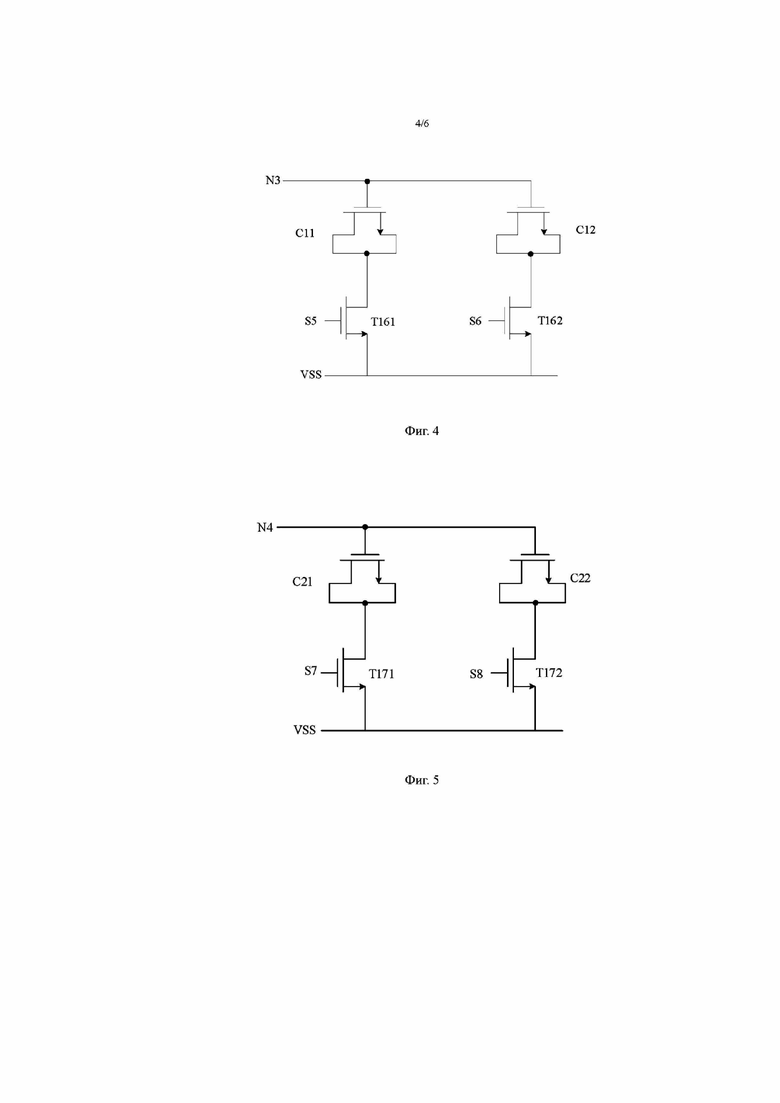

на фиг. 4 показана блок-схема первого модуля компенсации дисбаланса схемы выборки данных, представленного в примерном варианте осуществления настоящего изобретения;

на фиг. 5 показана блок-схема второго модуля компенсации дисбаланса схемы выборки данных, представленного в варианте осуществления настоящего изобретения;

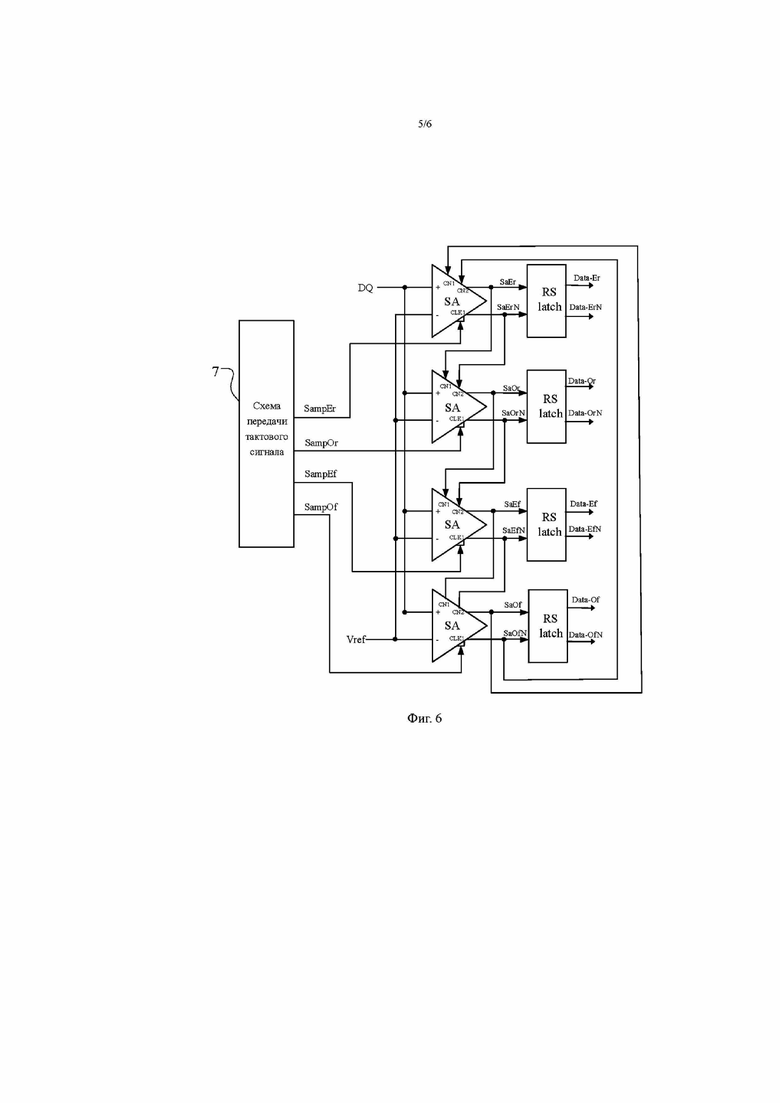

на фиг. 6 показана блок-схема устройства выборки данных, представленного в варианте осуществления настоящего изобретения;

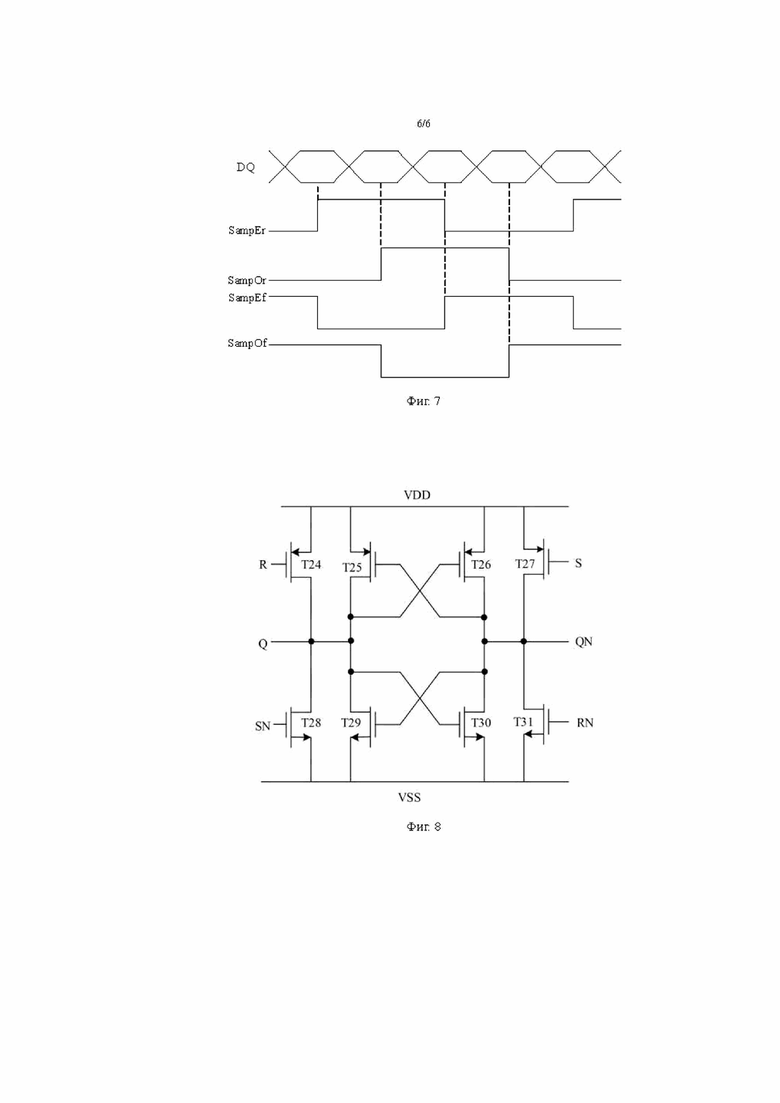

на фиг. 7 показана диаграмма последовательности тактового сигнала выборки устройства выборки данных, представленного в варианте осуществления настоящего изобретения;

на фиг. 8 показана блок-схема триггера устройства выборки данных, представленной в варианте осуществления настоящего изобретения.

Осуществление изобретения

Далее будет представлено подробное описание примерных вариантов осуществления со ссылкой на графические материалы. Стоит отметить, что примерные варианты осуществления могут быть реализованы в различных формах и не ограничивают диапазон настоящего изобретения; напротив, данные варианты осуществления представлены для того, чтобы дополнить настоящее изобретение, а также передать техническим специалистам в данной области концепцию примерных вариантов осуществления. Аналогичные отметки на графических материалах обозначают одинаковые или схожие конструкции, в связи с этим подробное описание данных конструкций будет опущено.

Относительные термины, такие как «вверху», «внизу», используются в данном описании не только с целью описания относительного отношения компонентов на графических материалах, но также и для удобства демонстрации направления данных компонентов. Следует понимать, что если устройство, отмеченное на графических материалах перевернуть вниз головой, компоненты, описанные как «вверху», станут компонентами, расположенными «внизу». Прочие относительные термины, такие как «высокий», «низкий», «верхний», «нижний», «левый», «правый», также применяются с целью описания подобных значений. Когда определенная конструкция находится ««вверху» другой конструкции, это может означать, что определенная конструкция полностью сформирована на другой конструкции, или что определенная конструкция «непосредственно» установлена на другой конструкции, или же что определенная конструкция «косвенно» установлена на другой конструкции с помощью прочих элементов.

Термины «один», «первый», «упомянутый» используются для обозначения наличия одного или нескольких элементов/компонентов/и т.д.; термины «содержать» и «иметь» используются для обозначения того, что в дополнение к перечисленным элементам/компонентам/и прочим деталям могут присутствовать дополнительные элементы/компоненты/и т.д.

Данный примерный вариант осуществления в первую очередь представляет схему выборки данных. Согласно фиг. 1, на которой показана блок-схема выборки данных, представленная в примерном варианте осуществления настоящего изобретения, схема выборки данных включает: первый модуль выборки данных 1, второй модуль выборки данных 2, модуль триггера 3 и модуль эквалайзера с решающей обратной связью 4. Первый модуль выборки данных 1 подключен к клемме сигнала данных DQ, клемме опорного сигнала Vref, первому узлу N1 и второму узлу N2 и используется для реагирования на сигналы клеммы сигнала данных DQ и клеммы опорного сигнала Vref, а также воздействуют на первый узел N1 и второй узел N2; второй модуль выборки данных 2 подключен к первому узлу N1, второму узлу N2, третьему узлу N3 и четвертому узлу N4 и используется для реагирования на сигналы первого узла N1 и второго узла N2, а также воздействует на третий узел N3 и четвертый узел N4; модуль триггера 3 подключен к третьему узлу N3, четвертому узлу N4, первой выходной клемме OUT1 и второй выходной клемме OUT2 и используется для отправки сигналов третьему узлу N3 и четвертому узлу N4, на первую выходную клемму OUT1 подается сигнал высокого уровня, а на вторую выходную клемму OUT2 подается сигнал низкого уровня, или на первую выходную клемму OUT1 подается сигнал низкого уровня и на вторую выходную клемму OUT2 подается сигнал высокого уровня; модуль эквалайзера с решающей обратной связью 4 параллельно подключен ко второму модулю выборки данных и используется для уменьшения межсимвольной интерференции посредством эквивалентной регулировки сигнала клеммы сигнала данных DQ.

В одном аспекте в настоящем изобретении модуль эквалайзера с решающей обратной связью интегрируется в схему выборки данных и регулирует параметры транзисторов во втором модуле выборки данных через модуль эквалайзера с решающей обратной связью, что эквивалентно регулировке сигнала клеммы сигнала данных. Таким образом, уменьшается межсимвольная интерференция между сигналами выходных клемм нескольких схем выборки данных. По сравнению с предшествующим уровнем техники, модуль эквалайзера с решающей обратной связью в настоящем изобретении может уменьшать межсимвольную интерференцию за счет простой конструкции схемы, а также сокращать энергопотребление памяти. С другой стороны, схема выборки данных согласно настоящему изобретению использует двухкаскадные модули выборки данных, а именно первый модуль выборки данных и второй модуль выборки данных с целью уменьшения шума обратной связи первой выходной клеммы и второй выходной клеммы, клеммы сигнала данных и клеммы опорного сигнала. С другой стороны, в настоящем изобретении модуль эквалайзера с решающей обратной связью находится параллельно со вторым модулем выборки, таким образом влияние модуля эквалайзера с решающей обратной связью на скорость схемы выборки данных может быть сведено к минимуму.

В данном примерном варианте осуществления, согласно фиг. 2, показана блок-схема выборки данных, представленная в другом примерном варианте осуществления настоящего изобретения. Схема выборки данных также включает модуль компенсации дисбаланса 5, модуль компенсации дисбаланса 5 параллельно подключен ко второму модулю выборки данных 2 и может использоваться с целью компенсации дисбаланса напряжения во втором модуле выборки данных 2 путем компенсации параметров транзисторов второго модуля выборки данных 2.

В данном примерном варианте осуществления настоящего изобретения, согласно фиг. 2, первый модуль выборки данных также подключен к первой клемме тактового сигнала CLK1 с целью запуска выборки в ответ на сигнал первой клеммы тактового сигнала CLK1; схема выборки данных также включает в себя модуль сброса 6, модуль сброса 6 подключен к первой клемме тактового сигнала CLK1, второй клемме тактового сигнала CLK2, первому узлу N1, второму узлу N2, третьему узлу N3, четвертому узлу N4, первой выходной клемме OUT1 и второй выходной клемме OUT2 с целью сброса первого узла N1 и второго узла N2 в ответ на сигнал первой клеммы тактового сигнала CLK1 и сброса третьего узла N3, четвертого узла N4, первой выходной клеммы OUT1, а также второй выходной клеммы OUT2 в ответ на сигнал второй клеммы тактового сигнала CLK2.

В данном примерном варианте осуществления, согласно фиг. 3, показана блок-схема выборки данных, представленная в другом примерном варианте осуществления настоящего изобретения. Первый модуль выборки данных включает: первый транзистор P-типа T1, второй транзистор P-типа T2 и третий транзистор P-типа T3, первая клемма первого транзистора P-типа T1 подключена к клемме сигнала высокого уровня VDD, управляющая клемма к первой клемме тактового сигнала CLK1, а вторая клемма к пятому узлу N5; первая клемма второго транзистора P-типа T2 подключена ко второй клемме первого транзистора P-типа T1, управляющая клемма к клемме сигнала данных DQ, а вторая клемма ко второму узлу N2; первая клемма третьего транзистора P-типа T3 подключена ко второй клемме первого транзистора P-типа T1, управляющая клемма к клемме опорного сигнала Vref, а вторая клемма к первому узлу N1.

В примерном варианте осуществления настоящего изобретения, как показано на фиг. 3, второй модуль выборки данных 2 включает: четвертый транзистор N-типа T4 и пятый транзистор N-типа T5, первая клемма четвертого транзистора N-типа T4 подключена к клемме сигнала низкого уровня VSS, управляющая клемма ко второму узлу N2, а вторая клемма к третьему узлу N3; первая клемма пятого транзистора N-типа T5 подключена к клемме сигнала низкого уровня VSS, управляющая клемма к первому узлу N1, а вторая клемма к четвертому узлу N4.

В примерном варианте осуществления настоящего изобретения, как показано на фиг. 3 модуль триггера 3 включает: шестой транзистор P-типа T6, седьмой транзистор N-типа T7, восьмой транзистор P-типа T8 и девятый транзистор N-типа T9, первая клемма шестого транзистора P-типа T6 подключена к клемме сигнала высокого уровня VDD, управляющая клемма ко второй выходной клемме OUT2, а вторая клемма к первой выходной клемме OUT1; первая клемма седьмого транзистора N-типа T7 подключена к третьему узлу N3, вторая клемма к первой выходной клемме OUT1, а управляющая клемма ко второй выходной клемме OUT2; первая клемма восьмого транзистора P-типа T8 подключена к клемме сигнала высокого уровня VDD, управляющая клемма к первой выходной клемме OUT1, а вторая клемма ко второй выходной клемме OUT2; первая клемма девятого транзистора N-типа T9 подключена к четвертому узлу N4, вторая клемма ко второй выходной клемме OUT2, а управляющая клемма к первой выходной клемме OUT1.

В данном примерном варианте осуществления, как показано на фиг. 3, модуль эквалайзера с решающей обратной связью 4 включает: первый модуль эквалайзера с решающей обратной связью 41 и второй модуль эквалайзера с решающей обратной связью 42. Первый модуль эквалайзера с решающей обратной связи 41 параллельно подключен между клеммой истока и клеммой стока четвертого транзистора N-типа T4 и используется для компенсации параметров четвертого транзистора N-типа T4; второй модуль эквалайзера с решающей обратной связью 42 параллельно подключен между клеммой истока и клеммой стока пятого транзистора N-типа T5 и используется для компенсации параметров пятого транзистора N-типа T5; среди них, первый модуль эквалайзера с решающей обратной связью 41 и второй модуль эквалайзера с решающей обратной связью 42 управляются двумя обратными сигналами с целью попеременного управления.

В данном примерном варианте осуществления, как показано на фиг. 3, первый модуль эквалайзера с решающей обратной связью 41 включает: два десятых транзистора N-типа T101 и T102, два одиннадцатых транзистора T111 и T112, два десятых транзистора N-типа T121 и T122. Первая клемма двух десятых транзисторов N-типа T101, T102 подключена к третьему узлу N3, а управляющая клемма ко второму узлу N2; одиннадцатый транзистор T111 расположен во взаимно-однозначном соответствии с десятым транзистором N-типа T101, одиннадцатый транзистор T112 расположен во взаимно-однозначном соответствии с десятым транзистором N-типа T102, первая клемма одиннадцатого транзистора T111 подключена ко второй клемме десятого транзистора N-типа T101, а управляющие клеммы подключены к разным клеммам управляющего сигнала S1, первая клемма одиннадцатого транзистора T112 подключена ко второй клемме десятого транзистора N-типа T102, а управляющие клеммы подключены к разным клеммам управляющего сигнала S2; двенадцатый транзистор N-типа T121 расположен во взаимно-однозначном соответствии с одиннадцатым транзистором 111, двенадцатый транзистор N-типа T122 расположен во взаимно-однозначном соответствии с одиннадцатым транзистором 112, первая клемма двенадцатого транзистора N-типа 121 подключена ко второй клемме одиннадцатого транзистора 111, управляющая клемма подключена к первой клемме управляющего сигнала CN1, вторая клемма подключена к клемме сигнала низкого уровня VSS, первая клемма двенадцатого транзистора N-типа 122 подключена ко второй клемме одиннадцатого транзистора 112, управляющая клемма к первой клемме управляющего сигнала CN1, а вторая клемма к клемме сигнала низкого уровня VSS.

В данном примерном варианте осуществления второй модуль эквалайзера с решающей обратной связью 42 включает: два тринадцатых транзисторов N-типа T131, T132, два четырнадцатых транзисторов T141, T142 и два пятнадцатых транзисторов N-типа T151, T152. Первая клемма тринадцатого транзистора N-типа T131, T132 подключена к четвертому узлу N4, а управляющая клемма к первому узлу N1; четырнадцатый транзистор T141 расположен во взаимно- однозначном соответствии с тринадцатым транзистором N-типа T131, четырнадцатый транзистор T142 расположен во взаимно-однозначном соответствии с тринадцатым транзистором N-типа T132, первая клемма четырнадцатого транзистора T141 подключена ко второй клемме тринадцатого транзистора N-типа T131, а управляющая клемма к клемме управляющего сигнала S3, первая клемма четырнадцатого транзистора T142 подключена ко второй клемме тринадцатого транзистора N-типа T132, а управляющая клемма к клемме управляющего сигнала S4; пятнадцатый N-транзистор T151 расположен во взаимно- однозначном соответствии с четырнадцатым транзистором T141, пятнадцатый N-транзистор T152 расположен во взаимно-однозначном соответствии с четырнадцатым транзистором T142, первая клемма пятнадцатого N-транзистора T151 подключена ко второй клемме четырнадцатого транзистора T141, а управляющая клемма к клемме второго управляющего сигнала CN2, вторая клемма к клемме сигнала низкого уровня VSS, первая клемма пятнадцатого N-транзистора T152 подключена ко второй клемме четырнадцатого транзистора T142, а управляющая клемма к клемме второго управляющего сигнала CN2, вторая клемма к клемме сигнала низкого уровня VSS; среди них, сигналы первой клеммы управляющего сигнала и второй клеммы управляющего сигнала являются обратными, то есть один из сигналов первой клеммы управляющего сигнала и второй клеммы управляющего сигнала находится на высоком уровне, а другой - на низком уровне.

В данном примерном варианте осуществления десятые транзисторы N-типа T101, T102 параллельно подключаются с двух сторон четвертого транзистора N-типа T4 посредством сигналов управляющих клемм S1 и S2 и первой управляющей клеммы CN1 с целью реализации настройки параметров четвертого транзистора N-типа T4 в разных режимах. По аналогии, тринадцатые транзисторы N-типа T131, T132 параллельно подключаются с двух сторон пятого транзистора N-типа T5 посредством сигналов управляющих клемм S3 и S4 и второй управляющей клеммы CN2, с целью реализации настройки параметров пятого транзисторов N-типа T5 в разных режимах. Среди них, величины регулируемых параметров транзистора T101 и транзистора T102 по отношению к четвертому транзистору N-типа T4, могут быть как одинаковыми, так и разными. Среди них, величины регулируемых параметров транзистора T131 и транзистора T132 по отношению к пятому транзистору N-типа T5, могут быть как одинаковыми, так и разными.

Следует понимать, что в прочих вариантах осуществления количество десятых транзисторов N-типа может быть разным и, соответственно, количество одиннадцатых транзисторов и двенадцатых транзисторов N-типа может быть одинаковым. Количество тринадцатых транзисторов N-типа может быть разным и, соответственно, количество четырнадцатых и пятнадцатых транзисторов N-типа может быть одинаковым.

В данном примерном варианте осуществления настоящего изобретения модуль компенсации дисбаланса 5 включает: первый модуль компенсации дисбаланса 51 и второй модуль компенсации дисбаланса 52, первый модуль компенсации дисбаланса 51 параллельно подключен между клеммой истока и клеммой стока четвертого транзистора N-типа T4 и используется для компенсации параметров четвертого транзистора N-типа T4; второй модуль компенсации дисбаланса 52 параллельно подключен между клеммой истока и клеммой стока пятого транзистора N-типа T5 и используется для компенсации параметров пятого транзистора N-типа T5. Первый модуль компенсации дисбаланса 51 и второй модуль компенсации дисбаланса 52 могут регулировать дисбаланс напряжения схемы выборки данных посредством компенсации параметров четвертого транзистора N-типа T4 и пятого транзистора N-типа T5.

В данном примерном варианте осуществления, согласно фиг. 4, показана блок-схема первого модуля компенсации дисбаланса схемы выборки данных, представленного в варианте осуществления настоящего изобретения. Первый модуль компенсации дисбаланса включает: два шестнадцатых транзистора T161, T162, два первых конденсатора C11, C12, первая клемма шестнадцатого транзистора T161 подключена к клемме сигнала низкого уровня VSS, управляющая клемма к клемме управляющего сигнала S5, первая клемма шестнадцатого транзистора T162 к клемме сигнала низкого уровня VSS, а управляющая клемма к клемме управляющего сигнала S6; первый конденсатор C11 расположен во взаимно-однозначном соответствии с шестнадцатым транзистором T161, первый конденсатор C12 распложен во взаимно-однозначном соответствии с шестнадцатым транзистором T162, первый конденсатор C11 подключен между второй клеммой шестнадцатого транзистора T161 и третьим узлом N3, а первый конденсатор C12 между второй клеммой шестнадцатого транзистора T162 и третьим узлом N3.

В данном примерном варианте осуществления, согласно фиг. 5 показана блок-схема второго модуля компенсации дисбаланса схемы выборки данных, представленного в варианте осуществления настоящего изобретения. Второй модуль компенсации дисбаланса включает: два семнадцатых транзистора T171, T172, два вторых конденсатора C21, C22, первая клемма семнадцатого транзистора T171 подключена к клемме сигнала низкого уровня VSS, управляющая клемма к клемме управляющего сигнала S7, первая клемма семнадцатого транзистора T172 к клемме сигнала низкого уровня VSS, а управляющая клемма к клемме управляющего сигнала S8; второй конденсатор C21 расположен во взаимно-однозначном соответствии с семнадцатым транзистором T171, второй конденсатор C22 расположен во взаимно-однозначном соответствии с семнадцатым транзистором T172, второй конденсатор C21 подключен между второй клеммой семнадцатого транзистора T171 и четвертым узлом N4, а второй конденсатор C22 между второй клеммой семнадцатого транзистора T172 и четвертым узлом N4.

В данном примерном варианте осуществления первые конденсаторы C11, C12 параллельно подключаются с двух сторон четвертого транзистора N-типа T4 посредством сигналов управляющих клемм S5 и S6 с целью реализации настройки параметров четвертого транзистора N-типа T4 в разных режимах. По аналогии, вторые конденсаторы C21, C22 параллельно подключаются с двух сторон пятого транзистора N-типа T5 посредством сигналов управляющих клемм S7 и S8 с целью реализации настройки параметров пятого транзистора N-типа T5 в разных режимах. Среди них, величины регулируемых параметров конденсаторов C11 и C12 по отношению к четвертому транзистору N-типа T4, могут быть как одинаковыми, так и разными. Среди них, величины регулируемых параметров конденсаторов C21 и C22 по отношению к пятому транзистору N-типа T5, могут быть как одинаковыми, так и разными.

Следует понимать, что в прочих примерных вариантах осуществления количество шестнадцатых транзисторов может быть разным и, соответственно, количество одиннадцатых первых конденсаторов может быть одинаковым. Количество семнадцатых транзисторов может быть разным и, соответственно, количество вторых конденсаторов может быть одинаковым. Кроме того, модуль компенсации дисбаланса аналогично модулю эквалайзера с решающей обратной связью также может регулировать параметры четвертого транзистора N-типа T4 и пятого транзистора N-типа T5 путем внесения четвертого транзистора N-типа T4 и пятого транзистора N-типа T5.

В данном варианте осуществления, как показано на фиг. 3, модуль сброса включает: восемнадцатый транзистор N-типа T18, девятнадцатый транзистор N-типа T19, двадцатый транзистор P-типа T20, двадцать первый транзистор P-типа T21, двадцать второй транзистор P-типа T22, двадцать третий транзистор P-типа T23, первая клемма восемнадцатого транзистора N-типа T18 подключена к клемме сигнала низкого уровня VSS, вторая клемма ко второму узлу N2, а управляющая клемма к клемме первого тактового сигнала CLK1; первая клемма девятнадцатого транзистора N-типа T19 подключена к клемме сигнала низкого уровня VSS, вторая клемма к первому узлу N1, а управляющая клемма к первой клемме тактового сигнала CLK1; первая клемма двадцатого транзистора P-типа T20 подключена к клемме сигнала высокого уровня VDD, вторая клемма к третьему узлу N3, а управляющая клемма ко второй клемме тактового сигнала CLK2; первая клемма двадцать первого транзистора P-типа T21 подключена к клемме сигнала высокого уровня VDD, вторая клемма к первой выходной клемме OUT1, а управляющая клемма ко второй клемме тактового сигнала CLK2; первая клемма двадцать второго транзистора P-типа T22 подключена к клемме сигнала высокого уровня VDD, вторая клемма ко второй выходной клемме OUT2, а управляющая клемма ко второй клемме тактового сигнала CLK2; первая клемма двадцать третьего транзистора P-типа T23 подключена к клемме сигнала высокого уровня VDD, вторая клемма к четвертому узлу N4, а управляющая клемма ко второй клемме тактового сигнала CLK2.

Рабочий процесс схемы выборки данных, представленной в данном примерном варианте осуществления, разделен на четыре этапа: этап сброса, первый этап выборки данных, второй этап выборки данных и этап фиксирования данных.

На этапе сброса первая клемма тактового сигнала CLK1 находится на высоком уровне, вторая клемма тактового сигнала CLK2 находится на низком уровне, когда восемнадцатый транзистор N-типа T18 и девятнадцатый транзистор N-типа T19 включены, первый узел N1 и второй узел N2 находится на низком уровне, когда включены двадцатый транзистор P-типа T20, двадцать первый транзистор P-типа T21, двадцать второй транзистор P-типа T22 и двадцать третий транзистор P-типа T23, третий узел N3, четвертый узел N4, первая выходная клемма OUT1 и вторая выходная клемма OUT2 находятся на высоком уровне.

На первом этапе выборки данных первая клемма тактового сигнала CLK1 находится на низком уровне, вторая клемма тактового сигнала CLK2 находится на высоком уровне, восемнадцатый транзистор N-типа T18 и девятнадцатый транзистор N-типа T19 выключены, двадцатый транзистор P-типа T20, двадцать первый транзистор P-типа T21, двадцать второй транзистор P-типа T22 и двадцать третий транзистор P-типа T23 выключены. Наряду с этим, при включении первого транзистора P-типа T1, второй транзистор P-типа T2 заряжается до второго узла N2 под действием сигнала клеммы сигнала данных DQ, а третий транзистор P-типа T3 заряжается до первого узла N1 под действием сигнала клеммы опорного сигнала Vref. Данный этап продолжается до тех пор, пока первыми не включатся четвертый транзистор N-типа T4 или пятый транзистор N-типа T5, например, когда напряжение на клемме сигнала данных DQ ниже, чем напряжение на клемме опорного сигнала Vref, четвертый транзистор N-типа T4 включается первым.

На втором этапе выборки данных, например, когда напряжение на клемме сигнала данных DQ ниже, чем напряжение на клемме опорного сигнала Vref, сначала включается четвертый транзистор N-типа T4. Таким образом, третий узел N3 разряжается до тех пор, пока первым не включится седьмой транзистор N-типа T7. На втором этапе выборки данных модуль эквалайзера с решающей обратной связью 4 может компенсировать параметры четвертого транзистора N-типа T4 и пятого транзистора N-типа T5, что эквивалентно управлению напряжением клеммы сигнала данных DQ. Таким образом снижается межсимвольная интерференция между сигналами на выходных клеммах разных схем выборки данных.

На стадии фиксирования данных после включения седьмого транзистора N-типа T7 первая выходная клемма OUT1 устанавливается на низкий уровень; кроме того, восьмой транзистор P-типа T8 включается под действием первой выходной клеммы OUT1, таким образом вторая выходная клемма OUT2 устанавливается на высокий уровень.

Аналогичным образом, когда напряжение на клемме сигнала данных DQ больше, чем напряжение на клемме опорного сигнала Vref, первая выходная клемма OUT1 устанавливается на высокий уровень, а вторая выходная клемма OUT2 на низкий уровень.

В данном примерном варианте осуществления также представлено устройство выборки данных, которое содержит несколько каскадных схем выборки данных, среди них первая выходная клемма схемы выборки данных верхнего каскада подключена к первой клемме управляющего сигнала схемы выборки данных нижнего каскада, вторая выходная клемма схемы выборки данных верхнего каскада подключена ко второй клемме управляющего сигнала схемы выборки данных нижнего каскада; первая выходная клемма схемы выборки данных последнего каскада подключена к первой клемме управляющего сигнала схемы выборки данных первого каскада, вторая выходная клемма схемы выборки данных последнего каскада подключена ко второй клемме управляющего сигнала схемы выборки данных первого каскада.

В данном примерном варианте осуществления, согласно фиг. 6, показана блок-схема устройства выборки данных, представленного в варианте осуществления настоящего изобретения. Данный примерный вариант осуществления описан на примере устройства выборки данных, включающего в себя четыре схемы выборки данных SA, первая выходная клемма SaEr схемы выборки данных SA первого каскада подключена к первой клемме управляющего сигнала CN1 схемы выборки данных SA второго каскада, вторая выходная клемма SaErN схемы выборки данных SA первого каскада подключена ко второй клемме управляющего сигнала CN2 схемы выборки данных SA второго каскада; первая выходная клемма SaOr схемы выборки данных SA второго каскада подключена к первой клемме управляющего сигнала CN1 третьей схемы выборки данных SA, а вторая выходная клемма SaOrN схемы выборки данных SA второго каскада подключена ко второй клемме управляющего сигнала CN2 схемы выборки данных SA третьего каскада; первая выходная клемма SaEf схемы выборки данных SA третьего каскада подключена к первой клемме управляющего сигнала CN1 схемы выборки данных SA четвертого каскада, а вторая выходная клемма SaEfN схемы выборки данных SA третьего каскада подключена ко второй клемме управляющего сигнала CN2 схемы выборки данных SA четвертого каскада; первая выходная клемма SaOf схемы выборки данных SA четвертого каскада подключена к первой клемме управляющего сигнала CN1 схемы выборки данных SA первого каскада, а вторая выходная клемма SaOfN схемы выборки данных SA четвертого каскада ко второй клемме управляющего сигнала CN2 схемы выборки данных SA первого каскада. В данном примерном варианте осуществления первая выходная клемма схемы выборки данных верхнего каскада напрямую подключена к первой клемме управляющего сигнала схемы выборки данных нижнего каскада, вторая выходная клемма схемы выборки данных верхнего каскада напрямую подключена ко второй клемме управляющего сигнала схемы выборки данных нижнего каскада, они не проходят через триггер, что снижает временную задержку передачи данных.

В данном примерном варианте осуществления, как показано на фиг. 6, устройство выборки данных также включает схему передачи тактового сигнала 7, схема передачи тактового сигнала 7 сконфигурирована для подачи тактовых сигналов выборки SampEr, SampOr, SampEf и SampOf на первые клеммы тактового сигнала CLK1 четырех схем выборки данных. На фиг. 7 показана диаграмма последовательности тактовых сигналов выборки устройства выборки данных, представленных в варианте осуществления настоящего изобретения. Разность фаз тактовых сигналов выборки на первой клемме тактового сигнала CLK1 соседних схем выборки данных составляет 90 градусов, а период тактового сигнала выборки на первой клемме тактового сигнала CLK1 в 2 раза больше периода сигнала на клемме сигнала данных DQ. Установка тактового сигнала выборки и на тактовую частоту 2T может облегчить маршрутизацию тактовой частоты и сэкономить энергопотребление. Среди них схема передачи тактового сигнала состоит из схемы приема WCK и квадратурного делителя.

В данном примерном варианте осуществления устройство выборки данных также включает несколько триггеров. Триггеры расположены во взаимно-однозначном соответствии со схемами выборки данных, и используются для фиксирования данных первой выходной клеммы на третьей выходной клемме схемы выборки данных, а также данных второй выходной клеммы на четвертой выходной клемме схемы выборки данных. Как показано на фиг. 6, число триггеров RS latch равно четырем, триггер RS-latch расположен во взаимно-однозначном соответствии со схемой выборки данных SA, триггер, подключенный к схеме SA первого каскада, может фиксировать сигнал первой выходной клеммы SaEr на третьей выходной клемме Data-Er данного триггера и одновременно может фиксировать сигнал второй выходной клеммы SaErN на четвертой выходной клемме Data-ErN данного триггера; триггер, подключенный к схеме выборки данных SA второго каскада, может фиксировать сигнал первой выходной клеммы SaOr на третьей выходной клемме Data-Or данного триггера и может одновременно фиксировать сигнал второй выходной клеммы SaOrN на четвертой выходной клемме Data-OrN данного триггера; триггер, подключенный к схеме выборки данных третьего каскада SA, может фиксировать сигнал первой выходной клеммы SaEf на третьей выходной клемме Data-Ef данного триггера и одновременно может фиксировать сигнал второй выходной клеммы SaEfN на четвертой выходной клемме Data-EfN данного триггера; триггер, подключенный к схеме выборки данных SA четвертого каскада, может фиксировать сигнал первой выходной клеммы SaOf на третьей выходной клемме Data-Of данного триггера и одновременно может фиксировать сигнал второй выходной клеммы SaOfN на четвертой выходной клемме Data-OfN данного триггера.

В данном примерном варианте осуществления, согласно фиг. 8, показана блок-схема триггера схемы выборки данных, представленного в другом варианте осуществления настоящего изобретения. Триггер включает: двадцать четвертый транзистор P-типа T24, двадцать пятый транзистор P-типа T25, двадцать шестой транзистор P-типа T26, двадцать седьмой транзистор P-типа T27, двадцать восьмой транзистор N-типа T28, двадцать девятый транзистор N-типа T29, тридцатый транзистор N-типа T30 и тридцать первый транзистор N-типа T31. Первая клемма двадцать четвертого транзистора P-типа T24 подключена к клемме сигнала высокого уровня VDD, вторая клемма к выходной клемме Q, а управляющая клемма к входной клемме R; первая клемма двадцать пятого транзистора P-типа подключена к клемме сигнала высокого уровня VDD, вторая клемма к выходной клемме Q, а управляющая клемма к выходной клемме QN; первая клемма двадцать шестого транзистора P-типа подключена к клемме сигнала высокого уровня VDD, вторая клемма к выходной клемме QN, а управляющая клемма к выходной клемме Q; первая клемма двадцать седьмого транзистора P-типа подключена к клемме сигнала высокого уровня VDD, вторая клемма к выходной клемме QN, а управляющая клемма к входной клемме S; первая клемма двадцать восьмого транзистора N-типа подключена к клемме сигнала низкого уровня VSS, вторая клемма к выходной клемме Q, а управляющая клемма к входной клемме SN; первая клемма двадцать девятого транзистора N-типа подключена к клемме сигнала низкого уровня VSS, вторая клемма к выходной клемме Q, а управляющая клемма к выходной клемме QN; первая клемма тридцатого транзистора N-типа подключена к клемме сигнала низкого уровня VSS, вторая клемма к выходной клемме QN, а управляющая клемма к выходной клемме Q; первая клемма тридцать первого транзистора N-типа подключена к клемме сигнала низкого уровня VSS, вторая клемма к выходной клемме QN, а управляющая клемма к входной клемме RN. Среди них, сигналы входной клеммы RN и входной клеммы R являются обратными сигналами, сигналы входной клеммы SN и входной клеммы S являются обратными сигналами. Входные клеммы R и SN данного триггера могут быть подключены к первой выходной клемме схемы выборки данных, а входные клеммы S и RN данного триггера ко второй выходной клемме схемы выборки данных. Триггер имеет полностью симметричную конструкцию, в связи с этим выходные сигналы с подтяжкой к питанию и подтяжкой к земле будут полностью симметричными, что увеличит скорость передачи данных.

Техническим специалистам в данной области будут понятны прочие варианты осуществления настоящего изобретения после ознакомления с описанием и примерными вариантами осуществления настоящего изобретения. Настоящее изобретение предназначено для охвата любых модификаций, сфер применения или адаптаций вариантов осуществления, описанных в настоящем изобретении. Данные модификации, сферы применения или адаптации вариантов осуществления соответствуют общему содержанию настоящего изобретения и включают в себя общепринятые знания или традиционные методы в данной технической области, не раскрытые в настоящем изобретении. Описание и примерные варианты осуществления следует рассматривать в качестве образца, подлинный объем настоящего изобретения исходят из формулы изобретения.

Следует понимать, что настоящее изобретение не ограничено точными конструкциями, описанными выше и продемонстрированными на прилагаемых графических материалах, а различные модификации и изменения могут быть внесены, не выходя за рамки настоящего изобретения. Объем настоящего изобретения ограничен только прилагаемой формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕСТОВАЯ ИНТЕГРАЛЬНАЯ СТРУКТУРА | 1990 |

|

RU2034306C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2504896C1 |

| БЛОК СДВИГОВОГО РЕГИСТРА, ВОЗБУЖДАЮЩАЯ СХЕМА ЗАТВОРА И УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2019 |

|

RU2740162C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2507605C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ, ОПРЕДЕЛЯЕМОГО УДВОЕННОЙ ШИРИНОЙ ЗАПРЕЩЁННОЙ ЗОНЫ | 2014 |

|

RU2541915C1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| ЭЛЕКТРОННОЕ УСТРОЙСТВО И СПОСОБ ОПРЕДЕЛЕНИЯ ЦИФРОВОГО ИНТЕРФЕЙСА ДЛЯ ПОДКЛЮЧЕННОГО ВНЕШНЕГО УСТРОЙСТВА | 2011 |

|

RU2553980C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1991 |

|

RU2119243C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

Изобретение относится к области выборки данных, а конкретнее представлены схема выборки данных и устройство выборки данных. Технический результат – уменьшение шума обратной связи первой выходной клеммы и второй выходной клеммы, клеммы сигнала данных и клеммы опорного сигнала, уменьшении межсимвольной интерференции и снижении энергопотребления. Схема выборки содержит: первый модуль выборки данных (1), для реагирования на сигналы от клеммы сигнала данных и клеммы опорного сигнала и воздействия на первый узел и второй узел; второй модуль выборки данных (2), для реагирования на сигналы первого узла и второго узла и воздействия на третий узел и четвертый узел; модуль триггера (3), с возможностью подачи сигнала высокого уровня на первую выходную клемму и подачи сигнала низкого уровня на вторую выходную клемму или подачи сигнала низкого уровня на первую выходную клемму и подачи сигнала высокого уровня на вторую выходную клемму в соответствии с сигналами третьего узла и четвертого узла; модуль эквалайзера с решающей обратной связью (4), подключенный параллельно ко второму модулю выборки данных для уменьшения межсимвольной интерференции. 2 н. и 8 з.п. ф-лы, 8 ил.

1. Схема выборки данных, содержащая:

первый модуль выборки данных (1), подключенный к клемме сигнала данных (DQ), клемме опорного сигнала (Vref), первому узлу (N1) и второму узлу (N2) и выполненный с возможностью реагирования на сигналы от клеммы сигнала данных (DQ) и клеммы опорного сигнала (Vref) и воздействия на первый узел (N1) и второй узел (N2);

второй модуль выборки данных (2), подключенный к первому узлу (N1), второму узлу (N2), третьему узлу (N3) и четвертому узлу (N4) и выполненный с возможностью реагирования на сигналы от первого узла (N1) и второго узла (N2) и воздействия на третий узел (N3) и четвертый узел (N4);

модуль триггера (3), подключенный к третьему узлу (N3), четвертому узлу (N4), первой выходной клемме (OUT1) и второй выходной клемме (OUT2) и выполненный с возможностью, в соответствии с сигналами от третьего узла (N3) и четвертого узла (N4), подачи сигнала высокого уровня на первую выходную клемму (OUT1) и подачи сигнала низкого уровня на вторую выходную клемму (OUT2) или подачи сигнала низкого уровня на первую выходную клемму (OUT1) и подачи сигнала высокого уровня на вторую выходную клемму (OUT2);

модуль эквалайзера с решающей обратной связью (4), подключенный параллельно ко второму модулю выборки данных (2) и выполненный с возможностью уменьшения межсимвольной интерференции.

2. Схема выборки данных по п. 1, дополнительно содержащая

модуль компенсации дисбаланса (5), подключенный параллельно ко второму модулю выборки данных (2) и выполненный с возможностью компенсации дисбаланса напряжения второго модуля выборки данных (2),

при этом второй модуль выборки данных (2) содержит:

четвертый транзистор N-типа (T4), первая клемма которого подключена к клемме сигнала низкого уровня (VSS), управляющая клемма подключена ко второму узлу (N2), а вторая клемма к третьему узлу (N3);

пятый транзистор N-типа (T5), первая клемма которого подключена к клемме сигнала низкого уровня (VSS), управляющая клемма подключена к первому узлу, а вторая клемма к четвертому узлу.

3. Схема выборки данных по п. 1, в которой

первый модуль выборки данных (1) дополнительно подключен к первой клемме тактового сигнала (CLK1) и выполнен с возможностью запуска действия по выборке данных в ответ на сигнал от первой клеммы тактового сигнала (CLK1);

при этом схема выборки данных дополнительно содержит

модуль сброса (6), подключенный к первой клемме тактового сигнала (CLK1), второй клемме тактового сигнала (CLK2), первому узлу (N1), второму узлу (N2), третьему узлу (N3), четвертому узлу (N4), первой выходной клемме (OUT1) и второй выходной клемме (OUT2) и выполненный с возможностью сброса первого узла (N1) и второго узла (N2) в ответ на сигнал от первой клеммы тактового сигнала (CLK1) и сброса третьего узла (N3), четвертого узла (N4), первой выходной клеммы (OUT1) и второй выходной клеммы (OUT2) в ответ на сигнал от второй клеммы такового сигнала (CLK2);

при этом первый модуль выборки данных (1) содержит:

первый транзистор P-типа (T1), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), управляющая клемма к первой клемме тактового сигнала (CLK1), а вторая клемма к пятому узлу (N5);

второй транзистор P-типа (T2), первая клемма которого подключена ко второй клемме первого транзистора P-типа (T1), управляющая клемма к клемме сигнала данных (DQ), а вторая клемма ко второму узлу (N2);

третий транзистор P-типа (T3), первая клемма которого подключена ко второй клемме первого транзистора P-типа (T1), управляющая клемма к клемме опорного сигнала (Vref), а вторая клемма к первому узлу (N1).

4. Схема выборки данных по п. 1, в которой модуль триггера (3) содержит:

шестой транзистор P-типа (T6), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), управляющая клемма ко второй выходной клемме (OUT2), а вторая клемма к первой выходной клемме (OUT1);

седьмой транзистор N-типа (T7), первая клемма которого подключена к третьему узлу (N3), вторая клемма к первой выходной клемме (OUT1), а управляющая клемма ко второй выходной клемме (OUT2);

восьмой транзистор P-типа (T8), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), управляющая клемма к первой выходной клемме (OUT1), а вторая клемма ко второй выходной клемме (OUT2);

девятый транзистор N-типа (T9), первая клемма которого подключена к четвертому узлу (N4), вторая клемма ко второй выходной клемме (OUT2), а управляющая клемма к первой выходной клемме (OUT1).

5. Схема выборки данных по п. 2, в которой модуль эквалайзера с решающей обратной связью (4) содержит:

первый модуль эквалайзера с решающей обратной связью (41), подключенный параллельно между клеммой истока и клеммой стока четвертого транзистора N-типа (T4) и выполненный с возможностью компенсации параметров четвертого транзистора N-типа (T4);

второй модуль эквалайзера с решающей обратной связью (42), подключенный параллельно между клеммой истока и клеммой стока пятого транзистора N-типа (T5) и выполненный с возможностью компенсации параметров пятого транзистора N-типа (T5);

при этом первый модуль эквалайзера с решающей обратной связью (41) и второй модуль эквалайзера с решающей обратной связью (42) управляются двумя сигналами, обратными друг к другу, для попеременного управления;

при этом первый модуль эквалайзера с решающей обратной связью (41) содержит:

множество десятых транзисторов N-типа (T101, T102), причем первая клемма десятых транзисторов N-типа (T101, T102) подключена к третьему узлу (N3), а управляющая клемма ко второму узлу (N2);

множество одиннадцатых транзисторов (T111, T112), расположенных во взаимно-однозначном соответствии с десятыми транзисторами N-типа (T101, T102), причем первая клемма одиннадцатых транзисторов (T111, T112) подключена ко второй клемме десятых транзисторов N-типа (T101, T102), а управляющие клеммы подключены к разным клеммам управляющего сигнала;

множество двенадцатых транзисторов N-типа (T121, T122), расположенных во взаимно-однозначном соответствии с одиннадцатыми транзисторами (T111, T112), причем первая клемма двенадцатых транзисторов N-типа (T121, T122) подключена ко второй клемме одиннадцатых транзисторов (T111, T112), управляющая клемма к первой клемме управляющего сигнала, а вторая клемма к клемме сигнала низкого уровня (VSS);

а второй модуль эквалайзера с решающей обратной связью (42) содержит:

множество тринадцатых транзисторов N-типа (T131, T132), причем первая клемма тринадцатых транзисторов N-типа (T131, T132) подключена к четвертому узлу (N4), а управляющая клемма к первому узлу (N1);

множество четырнадцатых транзисторов N-типа (T141, T142), расположенных во взаимно-однозначном соответствии с тринадцатыми транзисторами N-типа (T131, T132), причем первая клемма четырнадцатых транзисторов (T141, T142) подключена ко второй клемме тринадцатых транзисторов N-типа (T131, T132), а управляющие клеммы подключены к разным клеммам управляющего сигнала;

множество пятнадцатых транзисторов N-типа (T151, T152), расположенных во взаимно-однозначном соответствии с четырнадцатыми транзисторами (T141, T142), причем первая клемма пятнадцатых транзисторов N-типа (T151, T152) подключена ко второй клемме четырнадцатых транзисторов (T141, T142), управляющая клемма ко второй клемме управляющего сигнала, а вторая клемма к клемме сигнала низкого уровня (VSS);

при этом сигналы первой клеммы управляющего сигнала и второй клеммы управляющего сигнала являются взаимно-обратными;

причем количество тринадцатых транзисторов N-типа (T131, T132), четырнадцатых транзисторов (T141, T142) и пятнадцатых транзисторов N-типа (T151, T152) равно двум.

6. Схема выборки данных по п. 5, в которой количество десятых транзисторов N-типа (T101, T102), одиннадцатых транзисторов (T111, T112) и двенадцатых транзисторов N-типа (T121, T122) равно двум.

7. Схема выборки данных по п. 2, в которой модуль компенсации дисбаланса (5) содержит:

первый модуль компенсации дисбаланса (51), подключенный параллельно между клеммой истока и клеммой стока четвертого транзистора N-типа (T4) и выполненный с возможностью компенсации параметров четвертого транзистора N-типа (T4);

второй модуль компенсации дисбаланса (52), подключенный параллельно между клеммой истока и клеммой стока пятого транзистора N-типа (T5) и выполненный с возможностью компенсации параметров пятого транзистора N-типа (T5);

при этом первый модуль компенсации дисбаланса (51) содержит:

множество шестнадцатых транзисторов (T161, T162), причем первая клемма шестнадцатых транзисторов (T161, T162) подключена к клемме сигнала низкого уровня (VSS), а управляющие клеммы подключены к разным клеммам управляющего сигнала;

множество первых конденсаторов (C11, C12), расположенных во взаимно-однозначном соответствии с шестнадцатыми транзисторами (T161, T162), причем первые конденсаторы (C11, C12) подключены между второй клеммой шестнадцатых транзисторов (T161, T162) и третьим узлом (N3);

а второй модуль компенсации дисбаланса (52) содержит:

множество семнадцатых транзисторов (T171, T172), причем первая клемма семнадцатых транзисторов (T171, T172) подключена к клемме сигнала низкого уровня (VSS), а управляющие клеммы к разным клеммам управляющего сигнала;

множество вторых конденсаторов (C21, C22), расположенных во взаимно-однозначном соответствии с семнадцатыми транзисторами (T171, T172), причем вторые конденсаторы подключены между второй клеммой семнадцатых транзисторов (T171, T172) и четвертым узлом (N4).

8. Схема выборки данных по п. 3, в которой модуль сброса (6) содержит:

восемнадцатый транзистор N-типа (T18), первая клемма которого подключена к клемме сигнала низкого уровня (VSS), вторая клемма ко второму узлу (N2), а управляющая клемма к первой клемме тактового сигнала (CLK1);

девятнадцатый транзистор N-типа (T20), первая клемма которого подключена к клемме сигнала низкого уровня (VSS), вторая клемма к первому узлу (N1), а управляющая клемма к первой клемме тактового сигнала (CLK1);

двадцатый транзистор P-типа (T20), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), вторая клемма к третьему узлу (N3), а управляющая клемма ко второй клемме тактового сигнала (CLK2);

двадцать первый транзистор P-типа (T21), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), вторая клемма к первой выходной клемме (OUT1), а управляющая клемма ко второй клемме тактового сигнала (CLK2);

двадцать второй транзистор P-типа (T22), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), вторая клемма ко второй выходной клемме (OUT2), а управляющая клемма ко второй клемме тактового сигнала (CLK2);

двадцать третий транзистор P-типа (T23), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), вторая клемма к четвертому узлу (N4), а управляющая клемма ко второй клемме тактового сигнала (CLK2).

9. Устройство выборки данных, содержащее множество каскадных схем выборки данных по любому из пп. 1-8, причем первая выходная клемма схемы выборки данных верхнего каскада подключена к первой управляющей клемме схемы выборки данных нижнего каскада, а вторая выходная клемма схемы выборки данных верхнего каскада подключена ко второй управляющей клемме схемы выборки данных нижнего каскада;

при этом первая выходная клемма схемы выборки данных последнего каскада подключена к первой управляющей клемме схемы выборки данных первого каскада, а вторая выходная клемма схемы выборки данных последнего каскада подключена ко второй управляющей клемме схемы выборки данных первого каскада.

10. Устройство выборки данных по п. 9, дополнительно содержащее множество триггеров, причем триггеры расположены во взаимно-однозначном соответствии со схемами выборки данных и выполнены с возможностью фиксации данных от первой выходной клеммы на третьей выходной клемме схемы выборки данных и фиксации данных от второй выходной клеммы на четвертой выходной клемме схемы выборки данных;

при этом триггер содержит:

двадцать четвертый транзистор P-типа (T24), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), вторая клемма к третьей выходной клемме (Q), а управляющая клемма к первой выходной клемме (R) схемы выборки данных;

двадцать пятый транзистор P-типа (T25), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), вторая клемма к третьей выходной клемме (Q), а управляющая клемма к четвертой выходной клемме (QN);

двадцать шестой транзистор P-типа (T26), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), вторая клемма к четвертой выходной клемме (QN), а управляющая клемма к третьей выходной клемме (Q);

двадцать седьмой транзистор P-типа (T27), первая клемма которого подключена к клемме сигнала высокого уровня (VDD), вторая клемма к четвертой выходной клемме (QN), а управляющая клемма ко второй выходной клемме (S) схемы выборки данных;

двадцать восьмой транзистор N-типа (T28), первая клемма которого подключена к клемме сигнала низкого уровня (VSS), вторая клемма к третьей выходной клемме (Q), а управляющая клемма к первой выходной клемме (SN) схемы выборки данных;

двадцать девятый транзистор N-типа (T29), первая клемма которого подключена к клемме сигнала низкого уровня (VSS), вторая клемма к третьей выходной клемме (Q), а управляющая клемма к четвертой выходной клемме (QN);

тридцатый транзистор N-типа (T31), первая клемма которого подключена к клемме сигнала низкого уровня (VSS), вторая клемма к четвертой выходной клемме (QN), а управляющая клемма к третьей выходной клемме (Q);

тридцать первый транзистор N-типа (T31), первая клемма которого подключена к клемме сигнала низкого уровня (VSS), вторая клемма к четвертой выходной клемме (QN), а управляющая клемма ко второй выходной клемме (RN) схемы выборки данных;

при этом устройство выборки данных содержит четыре схемы выборки данных и дополнительно содержит

схему передачи тактового сигнала (7), выполненную с возможностью подачи тактовых сигналов выборки на первые клеммы тактового сигнала (CLK1) четырех схем выборки данных, причем разность фаз тактовых сигналов выборки на первых клеммах тактового сигнала (CLK1) соседних схем выборки данных составляет 90 градусов, а период тактового сигнала выборки на первой клемме тактового сигнала (CLK1) в 2 раза больше периода сигнала на клемме сигнала данных (DQ).

| CN 109922394 A, 21.06.2019 | |||

| KR 101222092 B1, 14.01.2013 | |||

| CN 106297726 A, 04.01.2017 | |||

| CN 205140524 U, 06.04.2016 | |||

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ДАННЫХ (ВАРИАНТЫ) | 1994 |

|

RU2093958C1 |

Авторы

Даты

2023-01-17—Публикация

2020-07-21—Подача