Перекрестные ссылки на родственные заявки

[0001] Настоящая заявка притязает на приоритет заявки на патент (Китай) № 201820630007.5, поданной 28 апреля 2018 года, раскрытие сущности которой полностью содержится в данном документе по ссылке в качестве части настоящей заявки.

Область техники

[0002] Варианты осуществления настоящего раскрытия относятся к блоку сдвигового регистра, к возбуждающей схеме затвора и к устройству отображения.

Уровень техники

[0003] В области техники отображения, например, пиксельная матрица жидкокристаллической (ЖК) панели отображения, в общем, включает в себя множество строк линий затвора и включает в себя множество столбцов линий передачи данных, которые пересекают множество строк линий затвора. Возбуждение линий затвора может достигаться посредством связанной интегрированной возбуждающей схемы. В последние годы, в силу непрерывного совершенствования процесса изготовления тонкопленочных транзисторов на основе аморфного кремния (a–Si TFT) или оксидных тонкопленочных транзисторов, возбуждающая схема затвора может непосредственно интегрироваться на подложке на основе TFT–матрицы, чтобы формировать формирователь сигналов управления затвором на матрице (GOA), чтобы возбуждать линии затвора. Например, GOA, сформированный из множества каскадных блоков сдвиговых регистров, может использоваться для того, чтобы предоставлять сигналы напряжения включения и выключения для множества строк линий затвора пиксельной матрицы, за счет этого, например, управляя множеством строк линий затвора таким образом, что они последовательно включаются; и между тем, линии передачи данных предоставляют сигналы данных для пиксельных блоков в соответствующих строках пиксельной матрицы таким образом, чтобы формировать полутоновые напряжения, для шкал полутонов отображаемого изображения, в пиксельных блоках, так что кадр изображения может отображаться. Для текущих панелей отображения, использование GOA–технологии для того, чтобы возбуждать линии затвора, постоянно растет. GOA–технология помогает в реализации узкого обрамления и может уменьшать стоимость изготовления.

Сущность изобретения

[0004] По меньшей мере, один вариант осуществления предоставляет блок сдвигового регистра, который содержит: входную схему, выходную схему, схему сброса, схему управления и стабилизирующую схему сброса. Входная схема выполнена с возможностью записывать входной сигнал в первый узел в ответ на входной пусковой сигнал; выходная схема выполнена с возможностью выводить подготовительный выходной сигнал на выходной контактный вывод под управлением электрического уровня первого узла; схема сброса выполнена с возможностью сбрасывать выходной контактный вывод под управлением электрического уровня второго узла; схема управления выполнена с возможностью прикладывать первый сигнал напряжения ко второму узлу в ответ на управляющий сигнал; стабилизирующая схема сброса выполнена с возможностью прикладывать второй сигнал напряжения к первому узлу в ответ на стабилизирующий сигнал сброса.

[0005] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, стабилизирующая схема сброса содержит первый транзистор и второй транзистор, и стабилизирующий сигнал сброса содержит первый стабилизирующий сигнал сброса и второй стабилизирующий сигнал сброса; электрод затвора первого транзистора выполнен с возможностью соединяться со вторым узлом, чтобы использовать электрический уровень второго узла в качестве первого стабилизирующего сигнала сброса, первый контактный вывод первого транзистора выполнен с возможностью соединяться с линией первого синхросигнала, чтобы принимать первый синхросигнал в качестве второго стабилизирующего сигнала сброса, и второй контактный вывод первого транзистора выполнен с возможностью соединяться с электродом затвора второго транзистора; первый контактный вывод второго транзистора выполнен с возможностью соединяться со вторым контактным выводом напряжения, чтобы принимать второй сигнал напряжения, и второй контактный вывод второго транзистора выполнен с возможностью соединяться с первым узлом.

[0006] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, стабилизирующая схема сброса содержит третий транзистор и четвертый транзистор, и стабилизирующий сигнал сброса содержит первый стабилизирующий сигнал сброса и второй стабилизирующий сигнал сброса; электрод затвора третьего транзистора выполнен с возможностью соединяться со вторым узлом, чтобы использовать электрический уровень второго узла в качестве первого стабилизирующего сигнала сброса, первый контактный вывод третьего транзистора выполнен с возможностью соединяться со вторым контактным выводом напряжения, чтобы принимать второй сигнал напряжения, и второй контактный вывод третьего транзистора выполнен с возможностью соединяться с первым контактным выводом четвертого транзистора; электрод затвора четвертого транзистора выполнен с возможностью соединяться с линией первого синхросигнала, чтобы принимать первый синхросигнал в качестве второго стабилизирующего сигнала сброса, и второй контактный вывод четвертого транзистора выполнен с возможностью соединяться с первым узлом.

[0007] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, входная схема содержит пятый транзистор; и электрод затвора пятого транзистора выполнен с возможностью соединяться с линией второго синхросигнала, чтобы принимать второй синхросигнал в качестве входного пускового сигнала, первый контактный вывод пятого транзистора выполнен с возможностью соединяться с входной сигнальной линией, чтобы принимать входной сигнал, и второй контактный вывод пятого транзистора выполнен с возможностью соединяться с первым узлом.

[0008] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, выходная схема содержит шестой транзистор и первый конденсатор; электрод затвора шестого транзистора выполнен с возможностью соединяться с первым узлом, первый контактный вывод шестого транзистора выполнен с возможностью соединяться с линией первого синхросигнала, чтобы принимать первый синхросигнал в качестве подготовительного выходного сигнала, и второй контактный вывод шестого транзистора рассматривается в качестве выходного контактного вывода; первый электрод первого конденсатора выполнен с возможностью соединяться с электродом затвора шестого транзистора, и второй электрод первого конденсатора выполнен с возможностью соединяться со вторым контактным выводом шестого транзистора.

[0009] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, схема сброса содержит седьмой транзистор и второй конденсатор; электрод затвора седьмого транзистора выполнен с возможностью соединяться со вторым узлом, первый контактный вывод седьмого транзистора выполнен с возможностью соединяться со вторым контактным выводом напряжения, чтобы принимать второй сигнал напряжения, и второй контактный вывод седьмого транзистора выполнен с возможностью соединяться с выходным контактным выводом; первый электрод второго конденсатора выполнен с возможностью соединяться с электродом затвора седьмого транзистора, и второй электрод второго конденсатора выполнен с возможностью соединяться с первым контактным выводом седьмого транзистора.

[0010] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, схема управления содержит восьмой транзистор и девятый транзистор, и управляющий сигнал содержит первый управляющий сигнал и второй управляющий сигнал; электрод затвора восьмого транзистора выполнен с возможностью соединяться с линией второго синхросигнала, чтобы принимать второй синхросигнал в качестве первого управляющего сигнала, первый контактный вывод восьмого транзистора выполнен с возможностью соединяться с первым контактным выводом напряжения, чтобы принимать первый сигнал напряжения, и второй контактный вывод восьмого транзистора выполнен с возможностью соединяться со вторым узлом; электрод затвора девятого транзистора выполнен с возможностью соединяться с входной схемой, чтобы принимать входной сигнал, вводимый из входной схемы, и рассматривать входной сигнал в качестве второго управляющего сигнала, первый контактный вывод девятого транзистора выполнен с возможностью соединяться с линией второго синхросигнала, чтобы принимать второй синхросигнал, и второй контактный вывод девятого транзистора выполнен с возможностью соединяться со вторым контактным выводом восьмого транзистора.

[0011] Например, блок сдвигового регистра, предоставленный посредством некоторого варианта осуществления, дополнительно содержит выходную стабилизирующую схему. Выходная стабилизирующая схема выполнена с возможностью включаться или выключаться, согласно изменению электрического уровня сигнала, выводимого посредством выходного контактного вывода, под управлением первого сигнала напряжения.

[0012] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, выходная стабилизирующая схема содержит десятый транзистор; электрод затвора десятого транзистора выполнен с возможностью соединяться с первым контактным выводом напряжения, чтобы принимать первый сигнал напряжения, первый контактный вывод десятого транзистора выполнен с возможностью соединяться с входной схемой и стабилизирующей схемой сброса, и второй контактный вывод десятого транзистора выполнен с возможностью соединяться с первым узлом.

[0013] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, транзисторы представляют собой транзисторы p–типа, и материал активного слоя каждого из транзисторов p–типа содержит низкотемпературный поликристаллический кремний.

[0014] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, транзисторы представляют собой транзисторы p–типа; материал активного слоя каждого из транзисторов p–типа содержит низкотемпературный поликристаллический кремний; выходная стабилизирующая схема содержит выходной стабилизирующий транзистор, электрод затвора выходного стабилизирующего транзистора выполнен с возможностью соединяться со вторым контактным выводом напряжения, чтобы принимать второй сигнал напряжения, первый контактный вывод выходного стабилизирующего транзистора выполнен с возможностью соединяться с входной схемой и стабилизирующей схемой сброса, и второй контактный вывод выходного стабилизирующего транзистора выполнен с возможностью соединяться с первым узлом; и выходной стабилизирующий транзистор представляет собой транзистор n–типа, и материал активного слоя транзистора n–типа содержит оксид.

[0015] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, когда схема управления содержит девятый транзистор, и выходная стабилизирующая схема содержит десятый транзистор, девятый транзистор и десятый транзистор представляют собой двухзатворные тонкопленочные транзисторы; или когда схема управления содержит девятый транзистор, и выходная стабилизирующая схема содержит выходной стабилизирующий транзистор, девятый транзистор и выходной стабилизирующий транзистор представляют собой двухзатворные тонкопленочные транзисторы.

[0016] По меньшей мере, один вариант осуществления дополнительно предоставляет блок сдвигового регистра, который содержит: одиннадцатый транзистор, в котором электрод затвора одиннадцатого транзистора выполнен с возможностью соединяться с первым узлом, первый контактный вывод одиннадцатого транзистора выполнен с возможностью соединяться с линией первого синхросигнала, чтобы принимать первый синхросигнал, и второй контактный вывод одиннадцатого транзистора выполнен с возможностью соединяться с выходным контактным выводом; третий конденсатор, в котором первый электрод третьего конденсатора выполнен с возможностью соединяться с электродом затвора одиннадцатого транзистора, и второй электрод третьего конденсатора выполнен с возможностью соединяться со вторым контактным выводом одиннадцатого транзистора; двенадцатый транзистор, в котором электрод затвора двенадцатого транзистора выполнен с возможностью соединяться с первым контактным выводом напряжения, чтобы принимать первый сигнал напряжения, двенадцатый транзистор дополнительно содержит первый контактный вывод и второй контактный вывод, и второй контактный вывод двенадцатого транзистора выполнен с возможностью соединяться с первым узлом; тринадцатый транзистор, в котором электрод затвора тринадцатого транзистора выполнен с возможностью соединяться со вторым синхросигналом, чтобы принимать второй синхросигнал, первый контактный вывод тринадцатого транзистора выполнен с возможностью соединяться с входным контактным выводом, чтобы принимать входной сигнал, и второй контактный вывод тринадцатого транзистора выполнен с возможностью соединяться с первым контактным выводом двенадцатого транзистора; четырнадцатый транзистор, в котором электрод затвора четырнадцатого транзистора выполнен с возможностью соединяться со вторым узлом, первый контактный вывод четырнадцатого транзистора выполнен с возможностью соединяться со вторым контактным выводом напряжения, чтобы принимать второй сигнал напряжения, и второй контактный вывод четырнадцатого транзистора выполнен с возможностью соединяться со вторым контактным выводом одиннадцатого транзистора; четвертый конденсатор, в котором первый электрод четвертого конденсатора выполнен с возможностью соединяться с электродом затвора четырнадцатого транзистора, и второй электрод четвертого конденсатора выполнен с возможностью соединяться с первым контактным выводом четырнадцатого транзистора; пятнадцатый транзистор, в котором электрод затвора пятнадцатого транзистора выполнен с возможностью соединяться со вторым узлом, и первый контактный вывод пятнадцатого транзистора выполнен с возможностью соединяться с линией первого синхросигнала, чтобы принимать первый синхросигнал; шестнадцатый транзистор, в котором электрод затвора шестнадцатого транзистора выполнен с возможностью соединяться со вторым контактным выводом пятнадцатого транзистора, первый контактный вывод шестнадцатого транзистора выполнен с возможностью соединяться со вторым контактным выводом напряжения, чтобы принимать второй сигнал напряжения, и второй контактный вывод шестнадцатого транзистора выполнен с возможностью соединяться с первым контактным выводом двенадцатого транзистора; семнадцатый транзистор, в котором электрод затвора семнадцатого транзистора выполнен с возможностью соединяться с линией второго синхросигнала, чтобы принимать второй синхросигнал, первый контактный вывод семнадцатого транзистора выполнен с возможностью соединяться с первым контактным выводом напряжения, чтобы принимать первый сигнал напряжения, и второй контактный вывод семнадцатого транзистора выполнен с возможностью соединяться со вторым узлом; и восемнадцатый транзистор, в котором электрод затвора восемнадцатого транзистора выполнен с возможностью соединяться со вторым контактным выводом тринадцатого транзистора, первый контактный вывод восемнадцатого транзистора выполнен с возможностью соединяться с линией второго синхросигнала, чтобы принимать второй синхросигнал, и второй контактный вывод восемнадцатого транзистора выполнен с возможностью соединяться со вторым узлом.

[0017] По меньшей мере, один вариант осуществления дополнительно предоставляет блок сдвигового регистра, который содержит: девятнадцатый транзистор, в котором электрод затвора девятнадцатого транзистора выполнен с возможностью соединяться с первым узлом, первый контактный вывод девятнадцатого транзистора выполнен с возможностью соединяться с линией первого синхросигнала, чтобы принимать первый синхросигнал, и второй контактный вывод девятнадцатого транзистора выполнен с возможностью соединяться с выходным контактным выводом; пятый конденсатор, в котором первый электрод пятого конденсатора выполнен с возможностью соединяться с электродом затвора девятнадцатого транзистора, и второй электрод пятого конденсатора выполнен с возможностью соединяться со вторым контактным выводом девятнадцатого транзистора; двадцатый транзистор, в котором электрод затвора двадцатого транзистора выполнен с возможностью соединяться с первым контактным выводом напряжения, чтобы принимать первый сигнал напряжения, двадцатый транзистор дополнительно содержит первый контактный вывод и второй контактный вывод, и второй контактный вывод двадцатого транзистора выполнен с возможностью соединяться с первым узлом; двадцать первый транзистор, в котором электрод затвора двадцать первого транзистора выполнен с возможностью соединяться с линией второго синхросигнала, чтобы принимать второй синхросигнал, первый контактный вывод двадцать первого транзистора выполнен с возможностью соединяться с входным контактным выводом, чтобы принимать входной сигнал, и второй контактный вывод двадцать первого транзистора выполнен с возможностью соединяться с первым контактным выводом двадцатого транзистора; двадцать второй транзистор, в котором электрод затвора двадцать второго транзистора выполнен с возможностью соединяться со вторым узлом, первый контактный вывод двадцать второго транзистора выполнен с возможностью соединяться со вторым контактным выводом напряжения, чтобы принимать второй сигнал напряжения, и второй контактный вывод двадцать второго транзистора выполнен с возможностью соединяться со вторым контактным выводом девятнадцатого транзистора; шестой конденсатор, в котором первый электрод шестого конденсатора выполнен с возможностью соединяться с электродом затвора двадцать второго транзистора, и второй электрод шестого конденсатора выполнен с возможностью соединяться с первым контактным выводом двадцать второго транзистора; двадцать третий транзистор, в котором электрод затвора двадцать третьего транзистора выполнен с возможностью соединяться со вторым узлом, и первый контактный вывод двадцать третьего транзистора выполнен с возможностью соединяться со вторым контактным выводом напряжения, чтобы принимать второй сигнал напряжения; двадцать четвертый транзистор, в котором электрод затвора двадцать четвертого транзистора выполнен с возможностью соединяться с линией первого синхросигнала, чтобы принимать первый синхросигнал, первый контактный вывод двадцать четвертого транзистора выполнен с возможностью соединяться со вторым контактным выводом двадцать третьего транзистора, и второй контактный вывод двадцать четвертого транзистора выполнен с возможностью соединяться с первым контактным выводом двадцатого транзистора; двадцать пятый транзистор, в котором электрод затвора двадцать пятого транзистора выполнен с возможностью соединяться с линией второго синхросигнала, чтобы принимать второй синхросигнал, первый контактный вывод двадцать пятого транзистора выполнен с возможностью соединяться с первым контактным выводом напряжения, чтобы принимать первый сигнал напряжения, и второй контактный вывод двадцать пятого транзистора выполнен с возможностью соединяться со вторым узлом; и двадцать шестой транзистор, в котором электрод затвора двадцать шестого транзистора выполнен с возможностью соединяться со вторым контактным выводом двадцать первого транзистора, первый контактный вывод двадцать шестого транзистора выполнен с возможностью соединяться с линией второго синхросигнала, чтобы принимать второй синхросигнал, и второй контактный вывод двадцать шестого транзистора выполнен с возможностью соединяться со вторым узлом.

[0018] По меньшей мере, один вариант осуществления дополнительно предоставляет возбуждающую схему затвора, которая содержит множество блоков сдвиговых регистров, которые размещены каскадом. Множество блоков сдвиговых регистров содержат P первых блоков сдвиговых регистров, каждый из первых блоков сдвиговых регистров реализует блок сдвигового регистра, предоставленный посредством любого варианта осуществления настоящего раскрытия, и P является целым числом, большим единицы.

[0019] По меньшей мере, один вариант осуществления дополнительно предоставляет устройство отображения, которое содержит возбуждающую схему затвора, предоставленную посредством любого варианта осуществления настоящего раскрытия.

[0020] Например, в блоке сдвигового регистра, предоставленном посредством некоторого варианта осуществления настоящего раскрытия, устройство отображения дополнительно содержит множество линий сканирования и множество пиксельных блоков, размещаемых во множестве строк. Множество линий сканирования, соответственно, соединяются с множеством строк пиксельных блоков; выходные контактные выводы множества блоков сдвиговых регистров в возбуждающей схеме затвора, соответственно, соединяются с множеством линий сканирования; и выходной контактный вывод блока сдвигового регистра на (N)–ом каскаде дополнительно соединяется с входной схемой блока сдвигового регистра на (N+1)–ом каскаде, чтобы предоставлять входной сигнал, и N является целым числом, большим нуля.

Краткое описание чертежей

[0021] Чтобы ясно иллюстрировать техническое решение вариантов осуществления раскрытия, ниже кратко описываются чертежи вариантов осуществления; очевидно, что описанные чертежи относятся только к некоторым вариантам осуществления раскрытия и в силу этого не ограничивают раскрытие сущности.

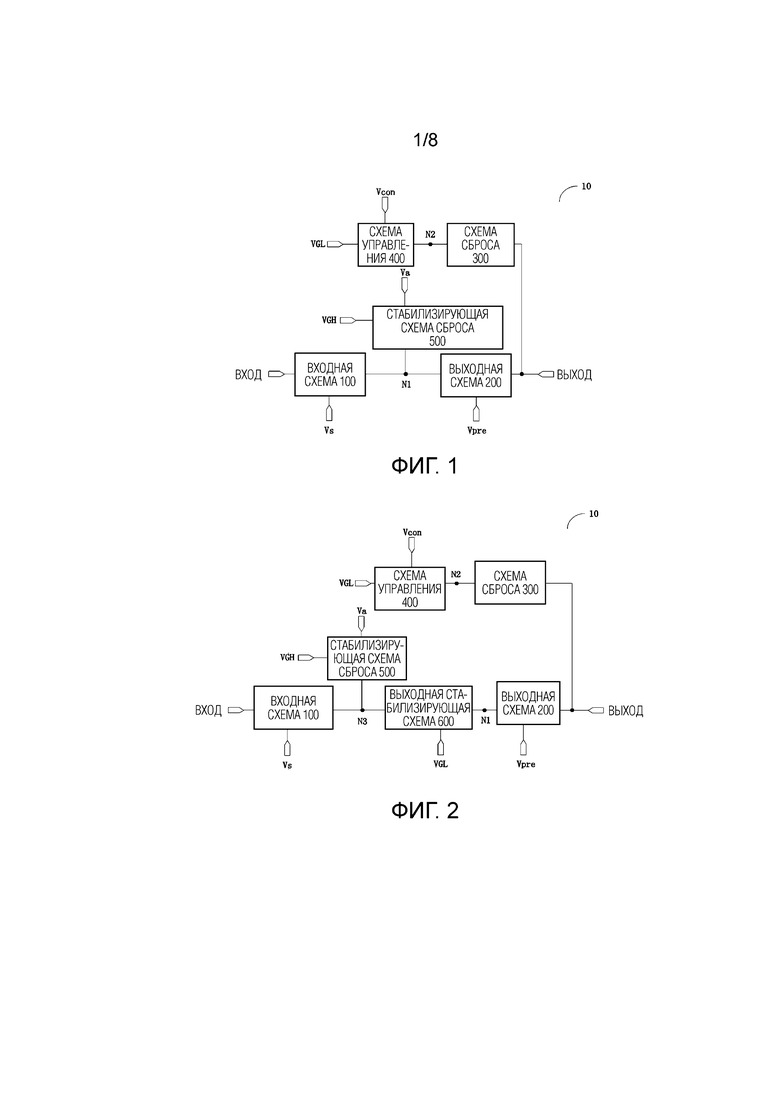

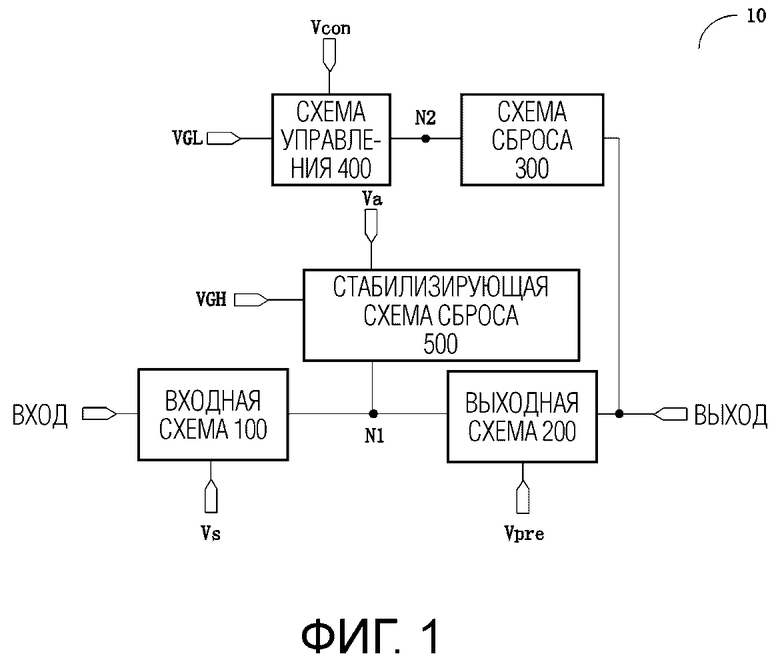

[0022] Фиг. 1 является принципиальной блок–схемой блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия;

[0023] Фиг. 2 является принципиальной блок–схемой другого блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия;

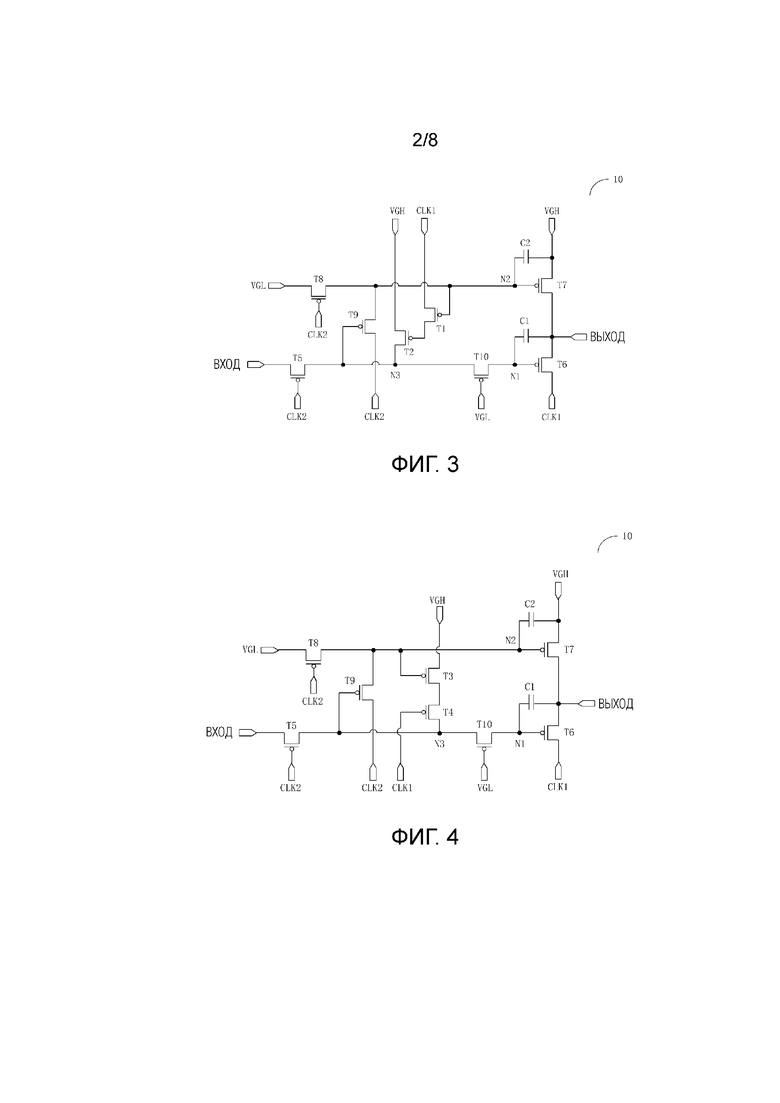

[0024] Фиг. 3 является принципиальной схемой конкретного примера реализации блока сдвигового регистра, как проиллюстрировано на фиг. 2;

[0025] Фиг. 4 является принципиальной схемой другого конкретного примера реализации блока сдвигового регистра, как проиллюстрировано на фиг. 2;

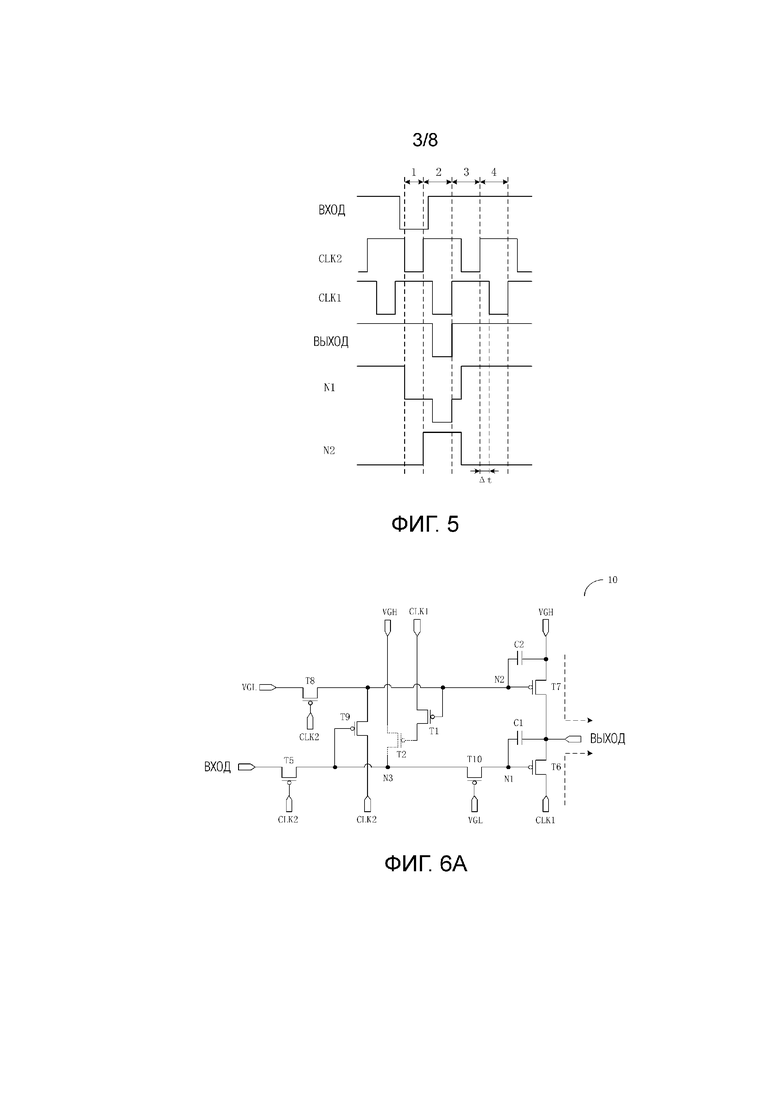

[0026] Фиг. 5 является временной диаграммой последовательности сигналов блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия;

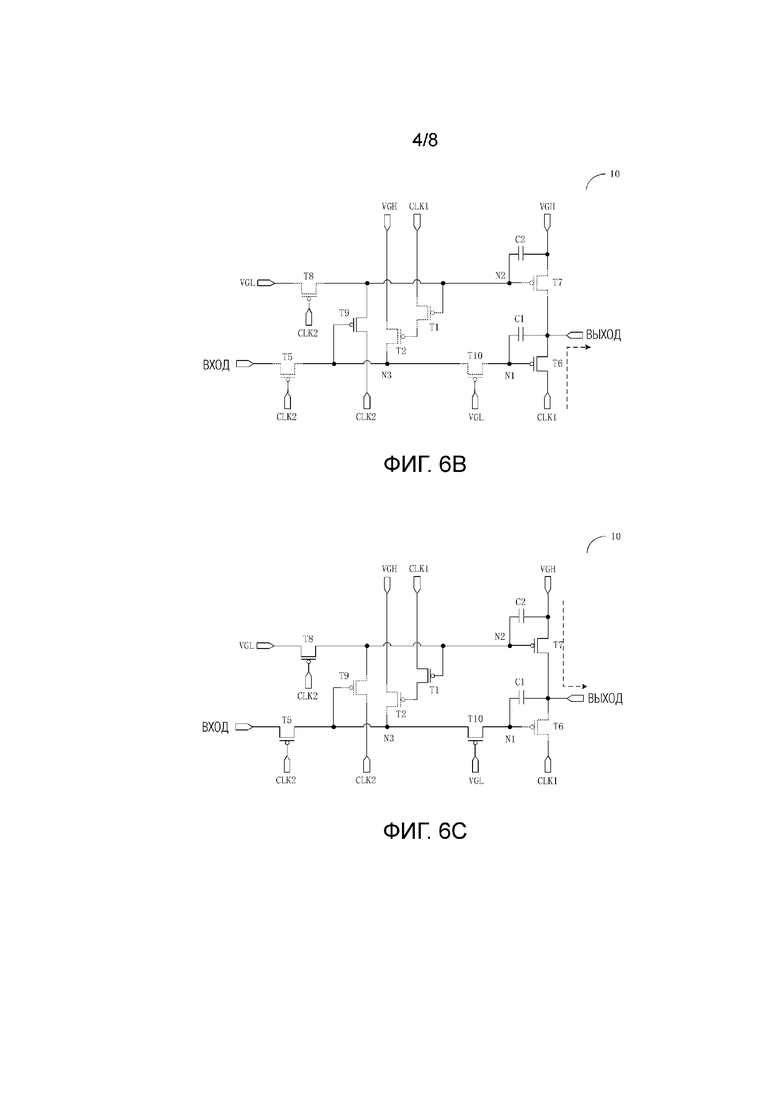

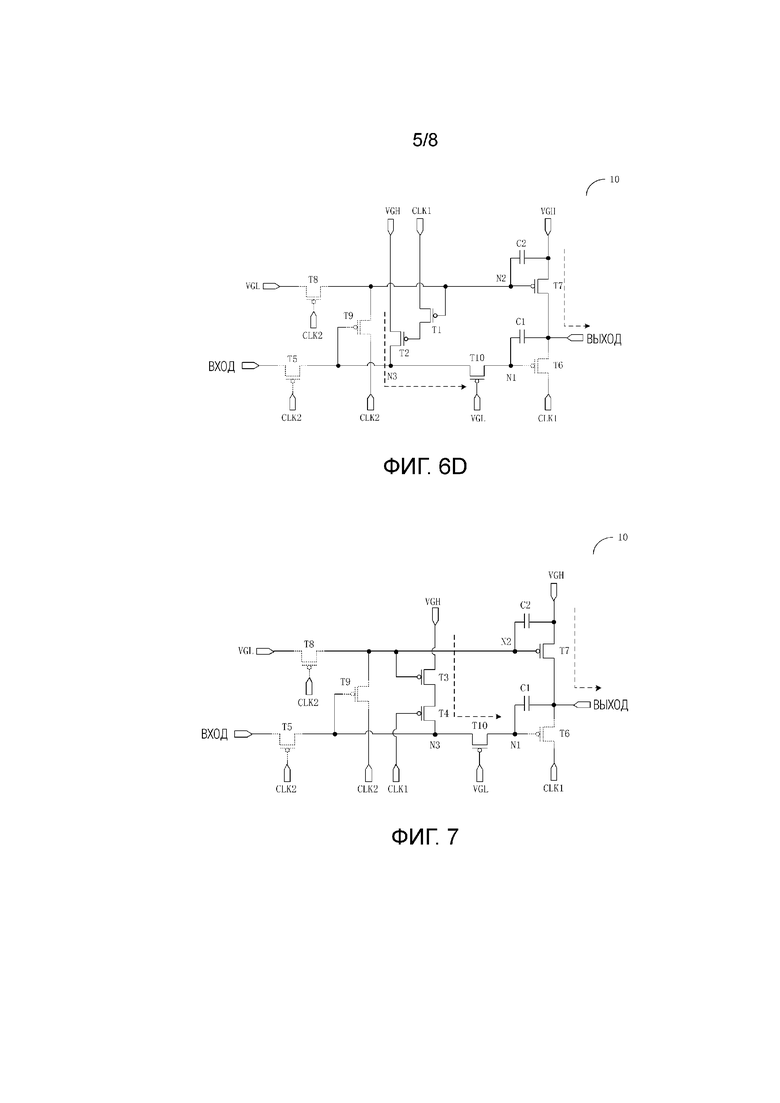

[0027] Фиг. 6A–6D являются, соответственно, принципиальными схемами, соответствующими четырем периодам, как проиллюстрировано на фиг. 5, блока сдвигового регистра, как проиллюстрировано на фиг. 3;

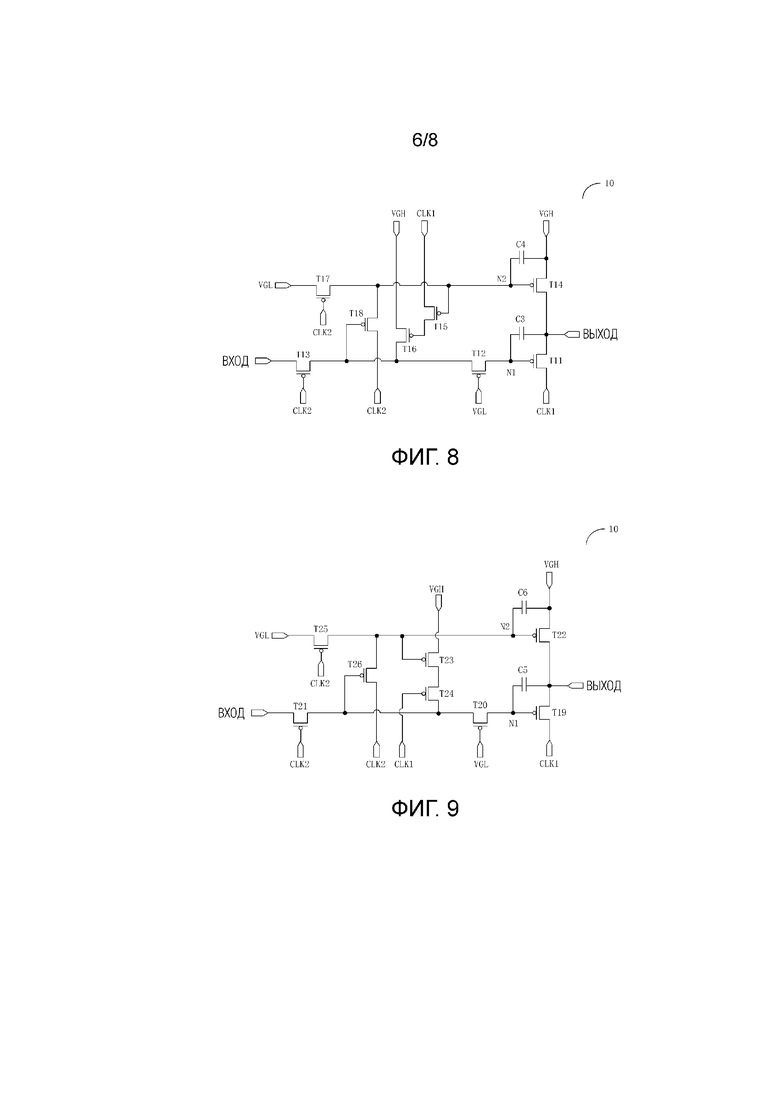

[0028] Фиг. 7 является принципиальной схемой, соответствующей периоду удержания сброса, как проиллюстрировано на фиг. 5, блока сдвигового регистра, как проиллюстрировано на фиг. 4;

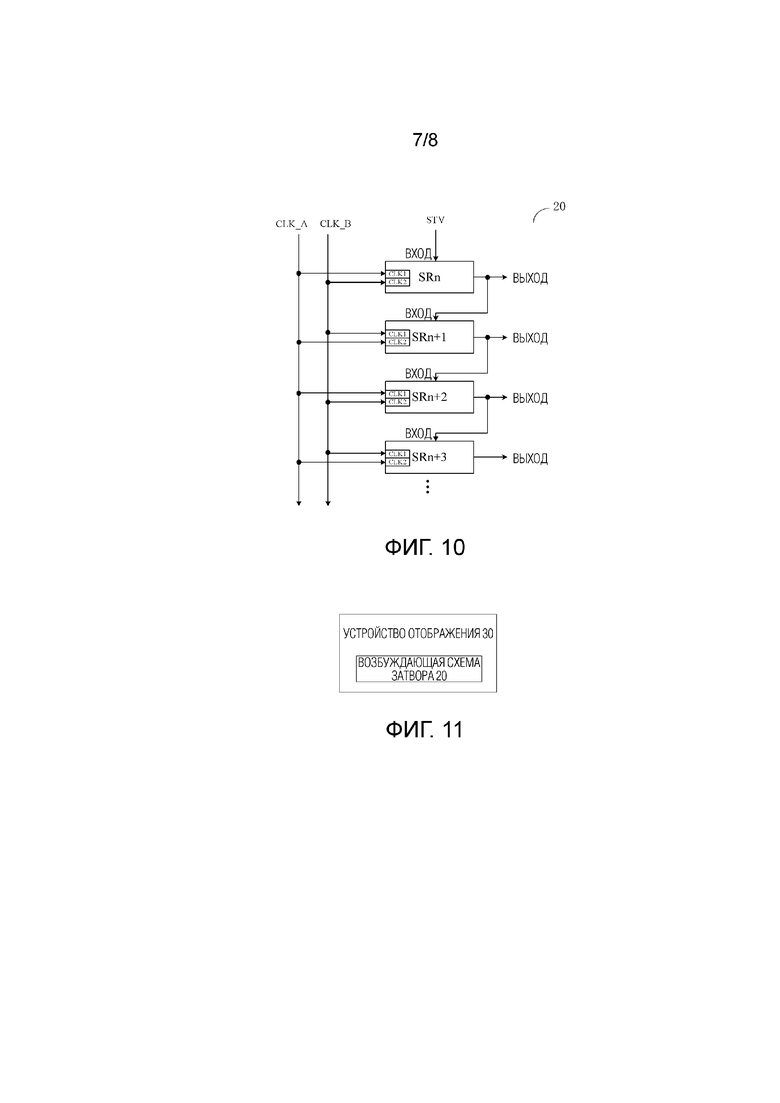

[0029] Фиг. 8 является принципиальной схемой блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия;

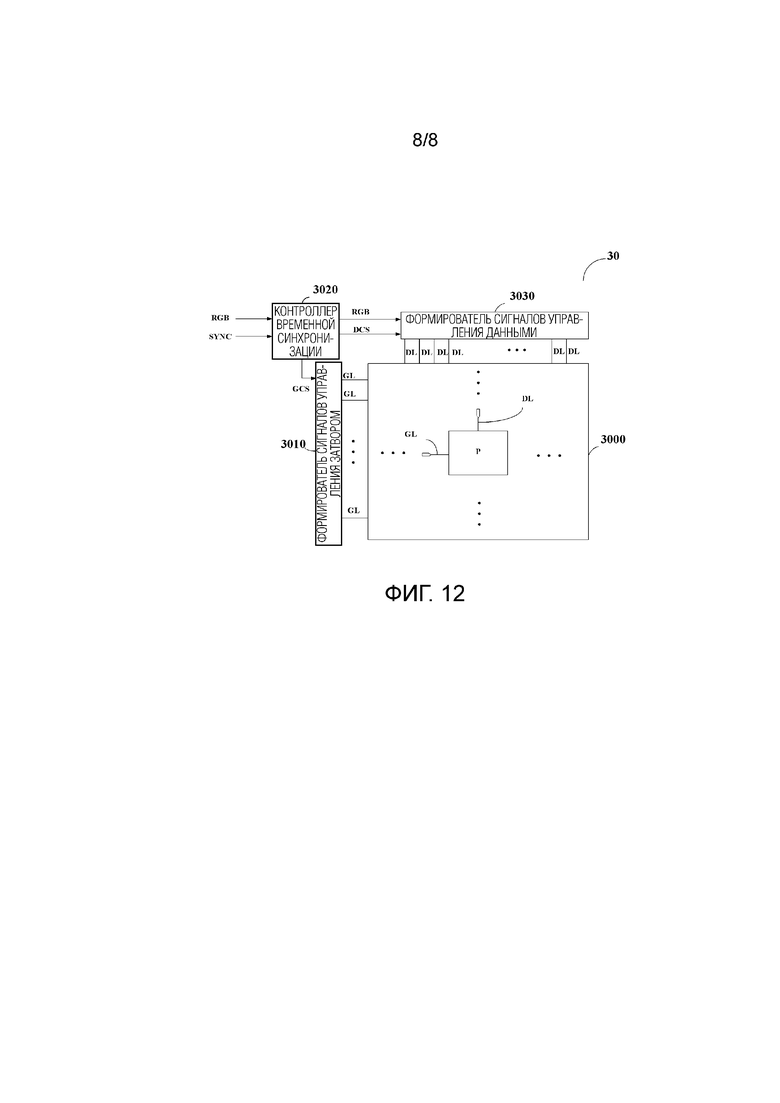

[0030] Фиг. 9 является принципиальной схемой другого блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия;

[0031] Фиг. 10 является принципиальной блок–схемой возбуждающей схемы затвора, предоставленной посредством некоторых вариантов осуществления настоящего раскрытия;

[0032] Фиг. 11 является принципиальной блок–схемой устройства отображения, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия; и

[0033] Фиг. 12 является принципиальной блок–схемой другого устройства отображения, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия.

Подробное описание изобретения

[0034] Чтобы обеспечивать очевидность целей, технических подробностей и преимуществ вариантов осуществления раскрытия, технические решения вариантов осуществления должны описываться четко и понятно в связи с чертежами, связанными с вариантами осуществления раскрытия. Очевидно, что описанные варианты осуществления составляют только часть, а не все варианты осуществления раскрытия. На основе описанных вариантов осуществления в данном документе, специалисты в данной области техники могут получать другой вариант(ы) осуществления без изобретательских усилий, что должно находиться в пределах объема раскрытия.

[0035] Если не указано иное, все технические и научные термины, используемые в данном документе, имеют смысловые значения, идентичные значениям, обычно понимаемым специалистами в области техники, которой принадлежит настоящее раскрытие сущности. Термины "первый", "второй" и т.д., которые используются в описании и формуле изобретения настоящей заявки для раскрытия, имеют намерение не указывать какую–либо последовательность, величину или важность, а отличать различные компоненты. Кроме того, такие термины, как "a", "an" и т.д., имеют намерение не ограничивать величину, а указывать наличие, по меньшей мере, одного. Термины "содержать", "содержащий", "включать в себя", "включающий в себя" и т.д. имеют намерение указывать то, что элементы или объекты, приведенные перед этими терминами, охватывают элементы или объекты и их эквиваленты, перечисленные после этих терминов, но не исключают другие элементы или объекты. Фразы "соединяться", "соединенный" и т.д. имеют намерение не задавать физическое соединение или механическое соединение, а могут включать в себя электрическое соединение, прямо или косвенно. "На", "под", "правый", "левый" и т.п. используются только для того, чтобы указывать относительную позиционную взаимосвязь, и когда позиция объекта, который описывается, изменяется, относительная позиционная взаимосвязь может изменяться, соответственно.

[0036] GOA–схема, например, включает в себя множество TFT. Авторы изобретения настоящего раскрытия отмечают в исследовании, что TFT могут иметь явление утечки вследствие таких факторов, как характеристики материала и процессы изготовления, так что выходной сигнал GOA–схемы имеет плохую стабильность и может легко подвергаться помехам посредством других сигналов. Авторы изобретения настоящего раскрытия также отмечают в исследовании, что другие факторы, такие как взаимная связь компонентов в GOA–схеме, плохая электромагнитная совместимость, схемная структура, также может вызывать такие проблемы, как плохая стабильность выходного сигнала. Вышеуказанные проблемы могут затрагивать эффект отображения панели отображения и снижать качество отображения.

[0037] По меньшей мере, один вариант осуществления настоящего раскрытия предоставляет блок сдвигового регистра, возбуждающую схему затвора и устройство отображения. В некоторых примерах, блок сдвигового регистра может повышать стабильность выходного сигнала, предотвращать подвергание помехам выходного сигнала посредством других сигналов и повышать качество отображения устройства отображения, применяющего возбуждающую схему затвора, с использованием блока сдвигового регистра.

[0038] Ниже приводится подробное описание варианта осуществления настоящего раскрытия со ссылкой на прилагаемые чертежи. Следует отметить, что идентичные ссылки с номерами на различных чертежах используются для того, чтобы означать идентичные компоненты, которые описываются.

[0039] По меньшей мере, один вариант осуществления предоставляет блок сдвигового регистра, который содержит: входную схему, выходную схему, схему сброса, схему управления и стабилизирующую схему сброса. Входная схема выполнена с возможностью записывать входной сигнал в первый узел в ответ на входной пусковой сигнал; выходная схема выполнена с возможностью выводить подготовительный выходной сигнал на выходной контактный вывод под управлением электрического уровня первого узла; схема сброса выполнена с возможностью сбрасывать выходной контактный вывод под управлением электрического уровня второго узла; схема управления выполнена с возможностью прикладывать первый сигнал напряжения ко второму узлу в ответ на управляющий сигнал; стабилизирующая схема сброса выполнена с возможностью прикладывать второй сигнал напряжения к первому узлу в ответ на стабилизирующий сигнал сброса.

[0040] Фиг. 1 является принципиальной блок–схемой блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия. Как проиллюстрировано на фиг. 1, блок 10 сдвигового регистра содержит входную схему 100, выходную схему 200, схему 300 сброса, схему 400 управления и стабилизирующую схему 500 сброса.

[0041] Входная схема 100 выполнена с возможностью записывать входной сигнал в первый узел N1 в ответ на входной пусковой сигнал. Например, входная схема 100 может соединяться с входным контактным выводом Input и входным пусковым контактным выводом Vs, и входная схема 100 выполнена с возможностью электрически соединять первый узел N1 и входной контактный вывод Input под управлением входного пускового сигнала, предоставленного посредством входного пускового контактного вывода Vs таким образом, чтобы записывать входной сигнал, предоставленный посредством входного контактного вывода Input, в первый узел N1. Таким образом, когда входной сигнал имеет допустимый электрический уровень (электрический уровень для включения соответствующего переключающего элемента, например, низкий электрический уровень), электрический уровень первого узла N1 также представляет собой допустимый электрический уровень, с тем чтобы управлять выходной схемой 200 таким образом, что она включается. Конечно, варианты осуществления настоящего раскрытия не ограничены этим. Например, в других примерах, входной пусковой сигнал и входной сигнал могут представлять собой идентичный сигнал, а именно, входной контактный вывод Input и входной пусковой контактный вывод Vs соединяются с идентичной сигнальной линией.

[0042] Выходная схема 200 выполнена с возможностью выводить подготовительный выходной сигнал на выходной контактный вывод Output под управлением электрического уровня первого узла N1 и рассматривать подготовительный выходной сигнал в качестве выходного сигнала блока 10 сдвигового регистра, с тем чтобы возбуждать, например, линии затвора, соединенные с выходным контактным выводом Output. Например, выходная схема 200 может соединяться с подготовительным выходным контактным выводом Vpre, и выходная схема 200 выполнена с возможностью включаться под управлением электрического уровня первого узла N1, с тем чтобы электрически соединять подготовительный выходной контактный вывод Vpre и выходной контактный вывод Output, выводить подготовительный выходной сигнал, предоставленный посредством подготовительного выходного контактного вывода Vpre, на выходной контактный вывод Output, и рассматривать подготовительный выходной сигнал в качестве сигнала сканирования, выводимого посредством блока 10 сдвигового регистра.

[0043] Схема 300 сброса выполнена с возможностью сбрасывать выходной контактный вывод Output под управлением электрического уровня второго узла N2. Например, схема 300 сброса может соединяться с выходным контактным выводом Output, и схема 300 сброса выполнена с возможностью электрически соединять контактный вывод напряжения сброса и выходной контактный вывод Output под управлением электрического уровня второго узла N2, с тем чтобы прикладывать напряжение сброса к выходному контактному выводу Output для сброса. Например, электрический уровневый сигнал второго узла N2 рассматривается в качестве сигнала сброса, так что блок 10 сдвигового регистра не требует дополнительного сигнала сброса, и в таком случае схемная структура упрощается. Например, контактный вывод напряжения сброса соединяется со схемой 300 сброса и, например, может представлять собой контактный вывод высокого напряжения.

[0044] Схема 400 управления выполнена с возможностью прикладывать первый сигнал напряжения ко второму узлу N2 в ответ на управляющий сигнал. Например, схема 400 управления может соединяться с управляющим контактным выводом Vcon и первым контактным выводом VGL напряжения, и схема 400 управления выполнена с возможностью электрически соединять второй узел N2 и первый контактный вывод VGL напряжения под управлением управляющего сигнала, предоставляемого посредством управляющего контактного вывода Vcon, с тем чтобы записывать первый сигнал напряжения, предоставленный посредством первого контактного вывода VGL напряжения, во второй узел N2 и управлять схемой 300 сброса таким образом, что она включается. Следует отметить, что первый контактный вывод VGL напряжения, например, может быть выполнен с возможностью продолжать ввод сигнала постоянного тока с низким электрическим уровнем. Нижеприведенные варианты осуществления являются идентичными в этом отношении, так что дополнительное описание здесь не приводится.

[0045] Стабилизирующая схема 500 сброса выполнена с возможностью прикладывать второй сигнал напряжения к первому узлу N1 в ответ на стабилизирующий сигнал сброса. Например, стабилизирующая схема 500 сброса может соединяться со стабилизирующим контактным выводом Va сброса и вторым контактным выводом VGH напряжения, и стабилизирующая схема 500 сброса выполнена с возможностью электрически соединять первый узел N1 и второй контактный вывод VGH напряжения под управлением стабилизирующего сигнала сброса, предоставленного посредством стабилизирующего контактного вывода Va сброса, с тем чтобы прикладывать второй сигнал напряжения, предоставляемый посредством второго контактного вывода VGH напряжения, к первому узлу N1, прерывисто заряжать первый узел N1 в период удержания сброса и в последующие периоды и удостоверяться в том, что выходная схема 200 отсоединяется. Следует отметить, что второй контактный вывод VGH напряжения, например, может быть выполнен с возможностью продолжать ввод сигнала постоянного тока с высоким электрическим уровнем. Нижеприведенные варианты осуществления являются идентичными в этом отношении, так что дополнительное описание здесь не приводится. Например, интенсивность сигнала, предоставляемого посредством второго контактного вывода VGH напряжения, превышает интенсивность сигнала, предоставляемого посредством первого контактного вывода VGL напряжения. Например, второй контактный вывод VGH напряжения может рассматриваться в качестве контактного вывода напряжения сброса, чтобы предоставлять напряжение сброса.

[0046] Например, посредством обеспечения возможности стабилизирующей схеме 500 сброса прерывисто заряжать первый узел N1 в период удержания сброса и в последующие периоды и обеспечивать то, что выходная схема 200 должна отсоединяться, можно не допускать пониженного качества отображения или анормального отображения устройства отображения с использованием блока 10 сдвигового регистра, когда выходной сигнал выходного контактного вывода Output подвергается помехам посредством других сигналов таким образом, что повышается стабильность выходного сигнала, и повышается качество отображения устройства отображения с использованием блока 10 сдвигового регистра. Например, первый узел N1 заряжается, чтобы удостоверяться в том, что выходная схема 200 отсоединяется, и в этом случае, схема 300 сброса выполняет вывод, и схема 300 сброса выводит напряжение сброса (например, высокое напряжение) на выходной контактный вывод Output, за счет этого предотвращая подвергание помехам выходного сигнала выходного контактного вывода Output посредством подготовительного выходного сигнала.

[0047] Фиг. 2 является принципиальной блок–схемой другого блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия. Как проиллюстрировано на фиг. 2, блок 10 сдвигового регистра дополнительно содержит выходную стабилизирующую схему 600, и другие структуры являются практически идентичными со структурами в блоке 10 сдвигового регистра, как проиллюстрировано на фиг. 1.

[0048] Выходная стабилизирующая схема 600 выполнена с возможностью включаться или выключаться согласно изменению электрического уровня сигнала в выходном контактном выводе Output под управлением первого сигнала напряжения. Например, выходная стабилизирующая схема 600 может соединяться с первым контактным выводом VGL напряжения и соединяться с входной схемой 100, выходной схемой 200 и стабилизирующей схемой 500 сброса (выходная стабилизирующая схема 600 соединяется с первым узлом N1 и третьим узлом N3). Например, выходная стабилизирующая схема 600 включается под управлением первого сигнала напряжения, предоставленного посредством первого контактного вывода VGL напряжения, а именно, первый узел N1 и третий узел N3 электрически соединяются таким образом, что входной сигнал из входной схемы 100 или второй сигнал напряжения из стабилизирующей схемы 500 сброса может записываться в первый узел N1. Когда выходной сигнал выходного контактного вывода Output изменяется с высокого электрического уровня на низкий электрический уровень, выходная стабилизирующая схема 600 может выключаться согласно изменению электрического уровня выходного сигнала, а именно, первый узел N1 и третий узел N3 отсоединяются, и первый узел N1 находится в состоянии поддержания уровня заряда, за счет этого уменьшая утечку первого узла N1, обеспечивая то, что выходная схема 200 включается, не допуская пониженного качества отображения или анормального отображения устройства отображения с использованием блока 10 сдвигового регистра, когда выходной сигнал выходного контактного вывода Output подвергается помехам посредством других сигналов, повышая стабильность выходного сигнала и повышая качество отображения устройства отображения с использованием блока 10 сдвигового регистра.

[0049] Следует отметить, что первый контактный вывод VGL напряжения в варианте осуществления настоящего раскрытия, например, продолжает ввод сигнала постоянного тока с низким электрическим уровнем, и сигнал постоянного тока с низким электрическим уровнем упоминается как первое напряжение; и второй контактный вывод VGH напряжения, например, продолжает ввод сигнала постоянного тока с высоким электрическим уровнем, и сигнал постоянного тока с высоким электрическим уровнем упоминается как второе напряжение. Нижеприведенные варианты осуществления являются идентичными в этом отношении и не описываются снова. Например, значение напряжения второго напряжения превышает значение напряжения первого напряжения.

[0050] Фиг. 3 является принципиальной схемой конкретного примера реализации блока сдвигового регистра, как проиллюстрировано на фиг. 2. В дальнейшем приводится описание посредством рассмотрения случая, в котором транзисторы представляют собой транзисторы p–типа, в качестве примера, что не должно истолковываться в качестве ограничения на варианты осуществления настоящего раскрытия. Как проиллюстрировано на фиг. 3, блок 10 сдвигового регистра содержит первый транзистор T1, второй транзистор T2 и пятый–десятый транзисторы T5–T10 и дополнительно содержит первый конденсатор C1 и второй конденсатор C2.

[0051] Например, как проиллюстрировано на фиг. 3, подробнее, стабилизирующая схема 500 сброса может реализовываться как первый транзистор T1 и второй транзистор T2. В этом варианте осуществления, стабилизирующий сигнал сброса включает в себя два сигнала, а именно, первый стабилизирующий сигнал сброса и второй стабилизирующий сигнал сброса. Электрод затвора первого транзистора T1 выполнен с возможностью соединяться со вторым узлом N2, чтобы использовать электрический уровень второго узла N2 в качестве первого стабилизирующего сигнала сброса; первый контактный вывод первого транзистора T1 выполнен с возможностью соединяться с линией CLK1 первого синхросигнала, чтобы принимать первый синхросигнал и рассматривать первый синхросигнал в качестве второго стабилизирующего сигнала сброса; и второй контактный вывод первого транзистора T1 выполнен с возможностью соединяться с электродом затвора второго транзистора T2. Первый контактный вывод второго транзистора T2 выполнен с возможностью соединяться со вторым контактным выводом VGH напряжения, чтобы принимать второй сигнал напряжения, и второй контактный вывод второго транзистора T2 выполнен с возможностью соединяться с третьим узлом N3 (следует отметить, что когда десятый транзистор T10 включается, это является эквивалентным тому, что второй контактный вывод второго транзистора T2 непосредственно соединяется с первым узлом N1). Следует отметить, что в варианте осуществления настоящего раскрытия, стабилизирующая схема 500 сброса также может представлять собой схему, сформированную из других компонентов (например, режим соединения третьего транзистора T3 и четвертого транзистора T4, как описано ниже). Ограничения не налагаются в варианте осуществления настоящего раскрытия.

[0052] Когда электрический уровень второго узла N2 представляет собой допустимый электрический уровень (например, низкий электрический уровень), и первый синхросигнал также имеет допустимый электрический уровень, и первый транзистор T1 и второй транзистор T2 включаются, с тем чтобы прикладывать второй сигнал напряжения к третьему узлу N3 и первому узлу N1 (в этом случае, десятый транзистор T10 включается), чтобы заряжать первый узел N1, за счет этого обеспечивая то, что выходная схема 200 отсоединяется. В этом случае, схема 300 сброса выводит второй сигнал напряжения (высокий электрический уровень) на втором контактном выводе VGH напряжения на выходной контактный вывод Output. Посредством применения этих компоновок, может повышаться стабильность напряжения, выводимого посредством выходного контактного вывода.

[0053] Входная схема 100 может реализовываться как пятый транзистор T5. Электрод затвора пятого транзистора T5 выполнен с возможностью соединяться с линией CLK2 второго синхросигнала, чтобы принимать второй синхросигнал в качестве входного пускового сигнала; первый контактный вывод пятого транзистора T5 выполнен с возможностью соединяться с входной сигнальной линией (входным контактным выводом Input), чтобы принимать входной сигнал; и второй контактный вывод пятого транзистора T5 выполнен с возможностью соединяться с третьим узлом N3 (следует отметить, что когда десятый транзистор T10 включается, второй контактный вывод пятого транзистора T5 является эквивалентным тому, чтобы непосредственно соединяться с первым узлом N1). Когда второй синхросигнал имеет допустимый электрический уровень, пятый транзистор T5 включается, с тем чтобы записывать входной сигнал в третий узел N3 и первый узел N1. Следует отметить, что входная схема 100 не ограничена этим случаем, и входная схема 100 также может представлять собой схему, сформированную из других компонентов, чтобы реализовывать соответствующие функции.

[0054] Выходная схема 200 может реализовываться как шестой транзистор T6 и первый конденсатор C1. Электрод затвора шестого транзистора T6 выполнен с возможностью соединяться с первым узлом N1; первый контактный вывод шестого транзистора T6 выполнен с возможностью соединяться с линией CLK1 первого синхросигнала, чтобы принимать первый синхросигнал в качестве подготовительного выходного сигнала; и второй контактный вывод шестого транзистора T6 рассматривается в качестве выходного контактного вывода Output или электрически соединяется с выходным контактным выводом Output. Первый электрод первого конденсатора C1 выполнен с возможностью соединяться с электродом затвора (первым узлом N1) шестого транзистора T6, и второй электрод первого конденсатора C1 выполнен с возможностью соединяться со вторым контактным выводом (а именно, выходным контактным выводом Output) шестого транзистора T6. Когда электрический уровень первого узла N1 представляет собой допустимый электрический уровень, шестой транзистор T6 включается, с тем чтобы выводить первый синхросигнал на выходной контактный вывод Output. Следует отметить, что выходная схема 200 не ограничена этим случаем, и выходная схема 200 также может представлять собой схему, сформированную из других компонентов, чтобы реализовывать соответствующие функции.

[0055] Схема 300 сброса может реализовываться как седьмой транзистор T7 и второй конденсатор C2. Электрод затвора седьмого транзистора T7 выполнен с возможностью соединяться со вторым узлом N2; первый контактный вывод седьмого транзистора T7 выполнен с возможностью соединяться со вторым контактным выводом VGH напряжения, чтобы принимать второй сигнал напряжения; и второй контактный вывод седьмого транзистора T7 выполнен с возможностью соединяться с выходным контактным выводом Output. Первый электрод второго конденсатора C2 выполнен с возможностью соединяться с электродом затвора (вторым узлом N2) седьмого транзистора T7, и второй электрод второго конденсатора C2 выполнен с возможностью соединяться с первым контактным выводом седьмого транзистора T7 и второго контактного вывода VGH напряжения. Когда электрический уровень второго узла N2 представляет собой допустимый электрический уровень, седьмой транзистор T7 включается, с тем чтобы прикладывать второй сигнал напряжения к выходному контактному выводу Output, чтобы реализовывать сброс. Компоновка второго конденсатора C2 помогает в стабилизации напряжения второго узла N2, с тем чтобы лучше управлять седьмым транзистором T7. Следует отметить, что схема 300 сброса не ограничена этим случаем, и схема 300 сброса также может представлять собой схему, сформированную из других компонентов, чтобы реализовывать соответствующие функции.

[0056] Схема 400 управления может реализовываться как восьмой транзистор T8 и девятый транзистор T9. В варианте осуществления, управляющий сигнал включает в себя два сигнала, а именно, первый управляющий сигнал и второй управляющий сигнал. Электрод затвора восьмого транзистора T8 выполнен с возможностью соединяться с линией CLK2 второго синхросигнала, чтобы принимать второй синхросигнал и рассматривать второй синхросигнал в качестве первого управляющего сигнала; первый контактный вывод восьмого транзистора T8 выполнен с возможностью соединяться с первым контактным выводом VGL напряжения, чтобы принимать первый сигнал напряжения; и второй контактный вывод восьмого транзистора T8 выполнен с возможностью соединяться со вторым узлом N2. Электрод затвора девятого транзистора T9 выполнен с возможностью соединяться с входной схемой 100 (которая представляет собой пятый транзистор T5 здесь), чтобы принимать входной сигнал (который представляет собой сигнал в третьем узле N3 здесь), вводимый посредством входной схемы 100, и рассматривать входной сигнал в качестве второго управляющего сигнала; первый контактный вывод девятого транзистора T9 выполнен с возможностью соединяться с линией CLK2 второго синхросигнала, чтобы принимать второй синхросигнал; и второй контактный вывод девятого транзистора T9 выполнен с возможностью соединяться со вторым контактным выводом восьмого транзистора T8. Когда второй синхросигнал имеет допустимый электрический уровень для включения переключающего элемента (который представляет собой восьмой транзистор T8 здесь), принимающего второй синхросигнал, восьмой транзистор T8 включается, с тем чтобы записывать первый сигнал напряжения во второй узел N2. Когда электрический уровень третьего узла N3 представляет собой допустимый электрический уровень, девятый транзистор T9 включается, с тем чтобы записывать второй синхросигнал во второй узел N2. Этот способ приспособлен для того, чтобы управлять электрическим уровнем второго узла N2, с тем чтобы управлять схемой 300 сброса. Следует отметить, что схема 400 управления не ограничена этим случаем, и схема 400 управления также может представлять собой схему, сформированную из других компонентов, чтобы реализовывать соответствующие функции.

[0057] Выходная стабилизирующая схема 600 может реализовываться как десятый транзистор T10. Электрод затвора десятого транзистора T10 выполнен с возможностью соединяться с первым контактным выводом VGL напряжения, чтобы принимать первый сигнал напряжения; первый контактный вывод десятого транзистора T10 выполнен с возможностью соединяться с входной схемой 100 и стабилизирующей схемой 500 сброса (соединенной с третьим узлом N3); и второй контактный вывод десятого транзистора T10 выполнен с возможностью соединяться с первым узлом N1. Десятый транзистор T10 включается под управлением первого сигнала напряжения, с тем чтобы электрически соединять первый узел N1 и третий узел N3, и затем входной сигнал из входной схемы 100 или второй сигнал напряжения из стабилизирующей схемы 500 сброса может записываться в первый узел N1. Когда выходной сигнал выходного контактного вывода Output изменяется с высокого электрического уровня на низкий электрический уровень, электрический уровень первого узла N1 также может уменьшаться и может быть ниже первого сигнала напряжения вследствие эффекта использования компенсационной обратной связи первого конденсатора C1. Таким образом, напряжение Vgs затвор–исток десятого транзистора T10 может превышать пороговое напряжение Vth (может составлять отрицательное значение) десятого транзистора T10 таким образом, что десятый транзистор T10 может выключаться, а именно, первый узел N1 и третий узел N3 отсоединяются. Следовательно, первый узел N1 находится в состоянии поддержания уровня заряда, с тем чтобы уменьшать утечку первого узла N1, обеспечивать то, что шестой транзистор T6 включается, и повышать стабильность выходного сигнала выходного контактного вывода Output. Следует отметить, что выходная стабилизирующая схема 600 не ограничена этим случаем, и выходная стабилизирующая схема 600 также может представлять собой схему, сформированную из других компонентов, чтобы реализовывать соответствующие функции. Следует отметить, что в варианте осуществления настоящего раскрытия, выходная стабилизирующая схема 600 (десятый транзистор T10) также может опускаться надлежащим образом, и в этом случае, первый узел N1 и третий узел N3 электрически соединяются непосредственно.

[0058] Следует отметить, что когда выходная стабилизирующая схема 600 реализуется как десятый транзистор T10, электрод затвора десятого транзистора T10 выполнен с возможностью соединяться с первым контактным выводом VGL напряжения, чтобы принимать первый сигнал напряжения. Например, в этом случае, десятый транзистор T10 представляет собой транзистор p–типа. Конечно, вариант осуществления настоящего раскрытия не ограничен этим. Например, в другом примере, выходная стабилизирующая схема 600 также может реализовываться как выходной стабилизирующий транзистор. Электрод затвора выходного стабилизирующего транзистора выполнен с возможностью соединяться со вторым контактным выводом VGH напряжения, чтобы принимать второй сигнал напряжения; первый контактный вывод выходного стабилизирующего транзистора выполнен с возможностью соединяться с входной схемой 100 и стабилизирующей схемой 500 сброса (соединенной с третьим узлом N3); и второй контактный вывод выходного стабилизирующего транзистора выполнен с возможностью соединяться с первым узлом N1. Например, режим соединения выходного стабилизирующего транзистора является аналогичным режиму соединения десятого транзистора T10, при том, что электрический уровень контактного вывода напряжения, соединенного с электродом затвора выходного стабилизирующего транзистора, и электрический уровень контактного вывода напряжения, соединенного с электродом затвора десятого транзистора T10, отличаются. В нижеприведенном описании, десятый транзистор T10 является эквивалентным выходному стабилизирующему транзистору, при том, что электрический уровень контактного вывода напряжения, соединенного с электродом затвора транзистора p–типа, отличается от электрического уровня контактного вывода напряжения, соединенного с электродом затвора транзистора n–типа.

[0059] Фиг. 4 является принципиальной схемой другого конкретного примера реализации блока сдвигового регистра, как проиллюстрировано на фиг. 2. Как проиллюстрировано на фиг. 4, за исключением того, что режим конкретной реализации стабилизирующей схемы 500 сброса отличается, блок 10 сдвигового регистра в этом варианте осуществления является по существу идентичным блоку 100 сдвигового регистра, как описано на фиг. 3. В этом варианте осуществления, стабилизирующая схема 500 сброса реализуется как третий транзистор T3 и четвертый транзистор T4. Стабилизирующая схема сброса включает в себя два сигнала, а именно, первый стабилизирующий сигнал сброса и второй стабилизирующий сигнал сброса.

[0060] Электрод затвора третьего транзистора T3 выполнен с возможностью соединяться со вторым узлом N2, чтобы использовать электрический уровень второго узла N2 в качестве первого стабилизирующего сигнала сброса; первый контактный вывод третьего транзистора T3 выполнен с возможностью соединяться со вторым контактным выводом VGH напряжения, чтобы принимать второй сигнал напряжения; и второй контактный вывод третьего транзистора T3 выполнен с возможностью соединяться с первым контактным выводом четвертого транзистора T4. Электрод затвора четвертого транзистора T4 выполнен с возможностью соединяться с линией CLK1 первого синхросигнала, чтобы принимать первый синхросигнал в качестве второго стабилизирующего сигнала сброса, и второй контактный вывод четвертого транзистора T4 выполнен с возможностью соединяться с третьим узлом N3 (следует отметить, что когда десятый транзистор T10 включается, второй контактный вывод четвертого транзистора T4 является эквивалентным тому, чтобы непосредственно соединяться с первым узлом N1). Когда электрический уровень второго узла N2 представляет собой допустимый электрический уровень, и электрический уровень первого синхросигнала также представляет собой допустимый электрический уровень, и третий транзистор T3 и четвертый транзистор T4 включаются, с тем чтобы прикладывать второй сигнал напряжения к третьему узлу N3 и первому узлу N1 (в этом случае, десятый транзистор T10 включается), чтобы заряжать первый узел N1, за счет этого обеспечивая то, что выходная схема 200 отсоединяется, и повышая стабильность выходного сигнала.

[0061] Следует отметить, что в описании вариантов осуществления настоящего раскрытия, первый узел N1, второй узел N2 и третий узел N3 не представляют компоненты, которые фактически существуют, и имеют намерение представлять соединение связанных электрических соединений на принципиальной схеме.

[0062] Следует отметить, что все транзисторы, применяемые в варианте осуществления настоящего раскрытия, могут представлять собой TFT, полевые транзисторы (FET) или другие переключающие элементы с идентичными характеристиками. В варианте осуществления настоящего раскрытия описание приводится посредством рассмотрения случая, в котором транзисторы, применяемые в варианте осуществления настоящего раскрытия, представляют собой тонкопленочные транзисторы, в качестве примера. Электрод истока и электрод стока транзистора, применяемого в данном документе, могут быть симметричными по структуре, так что электрод истока и электрод стока транзистора являются неотличимыми по структуре. В варианте осуществления настоящего раскрытия, чтобы отличать два контактных вывода транзистора, отличных от электрода затвора, один контактный вывод непосредственно описывается как первый контактный вывод, и другой контактный вывод непосредственно описывается как второй контактный вывод.

[0063] Например, в одном примере, первый–десятый транзисторы T1–T10 представляют собой транзисторы p–типа, и материал активных слоев транзисторов p–типа может представлять собой низкотемпературный поликристаллический кремний (LTPS) или другой подходящий материал. Например, в другом примере, первый–девятый транзисторы T1–T9 представляют собой транзисторы p–типа, и десятый транзистор T10 представляет собой транзистор n–типа. В этом случае, материал активных слоев первого–девятого транзисторов T1–T9 может представлять собой LTPS или другой подходящий материал, и материал активного слоя десятого транзистора T10 может представлять собой оксид, например, материал активного слоя десятого транзистора T10 может представлять собой оксид металла или низкотемпературный поликристаллический оксид (LTPO). Десятый транзистор T10 реализует транзистор n–типа, имеет небольшой ток утечки и может реализовываться посредством технологии на основе низкотемпературного поликристаллического оксида (LTPO).

[0064] Например, девятый транзистор T9 и десятый транзистор T10 могут реализовывать двухзатворные TFT, с тем чтобы дополнительно уменьшать ток утечки. Конечно, и девятый транзистор T9, и десятый транзистор T10 не ограничены этим случаем, в вариантах осуществления настоящего раскрытия, транзисторы могут реализовывать двухзатворные TFT и также могут реализовывать другие типы транзисторов.

[0065] Вариант осуществления настоящего раскрытия описываются посредством рассмотрения случая, в котором все транзисторы представляют собой транзисторы p–типа, в качестве примера. В этом случае, первый контактный вывод транзистора представляет собой электрод истока; и второй контактный вывод представляет собой электрод стока. Следует отметить, что настоящее раскрытие сущности включает в себя, но не ограничено этим. Например, один или более транзисторов в блоке 10 сдвигового регистра, предоставленном посредством варианта осуществления настоящего раскрытия, также могут реализовывать транзистор n–типа. В этом случае, первый контактный вывод транзистора представляет собой электрод стока; и второй контактный вывод представляет собой электрод истока. Соответственно, необходимо только соединять контактные выводы транзисторов выбранного типа со ссылкой на соединения контактных выводов соответствующих транзисторов в варианте осуществления настоящего раскрытия и заменять соответствующий сигнал высокого напряжения сигналом низкого напряжения или заменять соответствующий сигнал низкого напряжения сигналом высокого напряжения. Когда применяется транзистор n–типа , IGZO может реализовываться в качестве активного слоя TFT. По сравнению со случаем, в котором LTPS или аморфный кремний (к примеру, гидрогенизированный аморфный кремний) рассматривается в качестве активного слоя TFT, размер транзистора может эффективно уменьшаться, и ток утечки может не допускаться.

[0066] Фиг. 5 является временной диаграммой последовательности сигналов блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия. Ниже приводится описание принципа работы блока 10 сдвигового регистра, как проиллюстрировано на фиг. 3 со ссылкой на временную диаграмму последовательности сигналов, как проиллюстрировано на фиг. 5, и описание приводится здесь посредством рассмотрения случая, в котором транзисторы представляют собой транзисторы p–типа, в качестве примера, но вариант осуществления настоящего раскрытия не ограничен этим.

[0067] Как проиллюстрировано на фиг. 5, временная последовательность сигналов включает в себя четыре периода: период 1 ввода, период 2 вывода, период 3 сброса и период 4 удержания сброса. Фиг. 5 иллюстрирует временные формы сигнала сигналов в каждый период.

[0068] Следует отметить, что фиг. 6A–6D являются, соответственно, принципиальными схемами, когда блок 10 сдвигового регистра, как проиллюстрировано на фиг. 3, находится в вышеуказанных четырех периодах. Фиг. 6A является принципиальной схемой, когда блок 10 сдвигового регистра, как проиллюстрировано на фиг. 3, находится в периоде 1 ввода. Фиг. 6B является принципиальной схемой, когда блок 10 сдвигового регистра, как проиллюстрировано на фиг. 3, находится в периоде 2 вывода. Фиг. 6C является принципиальной схемой, когда блок 10 сдвигового регистра, как проиллюстрировано на фиг. 3, находится в периоде 3 сброса. Фиг. 6D является принципиальной схемой, когда блок 10 сдвигового регистра, как проиллюстрировано на фиг. 3, находится в периоде 4 удержания сброса.

[0069] Помимо этого, все транзисторы, отмечаемые посредством пунктирных линий на фиг. 6A–6D, указывают то, что транзисторы, отмечаемые посредством пунктирных линий, находятся в отключенном состоянии в соответствующий период(ы), и пунктирные линии со стрелками на фиг. 6A–6D представляют направление тока в блоке сдвигового регистра в соответствующий период(ы). Описание приводится посредством рассмотрения случая, в котором транзисторы, как проиллюстрировано на фиг. 6A–6D, представляют собой транзисторы p–типа, в качестве примера, т.е. транзисторы включаются, когда электроды затвора транзисторов применяются с включенным электрическим уровнем (допустимым электрическим уровнем, который представляет собой низкий электрический уровень здесь), и транзисторы выключаются, когда электроды затвора транзисторов применяются с выключенным электрическим уровнем (недопустимым электрическим уровнем, который представляет собой высокий электрический уровень здесь). Нижеприведенные варианты осуществления являются идентичными в этом отношении, так что дополнительное описание здесь не приводится.

[0070] В период 1 ввода, период 3 сброса и период 4 удержания сброса, выходной контактный вывод Output выводит высокие электрические уровни; и в период 2 вывода, выходной контактный вывод Output выводит высокий электрический уровень сначала и затем выводит низкий электрический уровень. Таким образом, блок сдвигового регистра, предоставленный посредством варианта осуществления настоящего раскрытия, может реализовывать функцию сдвигового регистра.

[0071] В период 1 ввода, как проиллюстрировано на фиг. 5 и 6A, второй синхросигнал имеет низкий электрический уровень, так что пятый транзистор T5 включается. Десятый транзистор T10 включается посредством низкого электрического уровня первого сигнала напряжения. Входной сигнал из входного контактного вывода Input записывается в первый узел N1, и в этом случае, первый узел N1 имеет низкий электрический уровень. Шестой транзистор T6 включается посредством низкого электрического уровня первого узла N1, и первый синхросигнал выводится на выходной контактный вывод Output. Восьмой транзистор T8 включается посредством низкого электрического уровня второго синхросигнала, с тем чтобы записывать первый сигнал напряжения во второй узел N2. Девятый транзистор T9 включается посредством низкого электрического уровня третьего узла N3, с тем чтобы записывать второй синхросигнал во второй узел N2. В этом случае, как второй синхросигнал, так и первый сигнал напряжения имеют низкий электрический уровень, так что второй узел N2 имеет низкий электрический уровень. Седьмой транзистор T7 включается посредством низкого электрического уровня второго узла N2, с тем чтобы выводить второй сигнал напряжения на выходной контактный вывод Output. Первый транзистор T1 включается посредством низкого электрического уровня второго узла N2, с тем чтобы записывать первый синхросигнал в электрод затвора второго транзистора T2. Второй транзистор T2 выключается посредством высокого электрического уровня первого синхросигнала.

[0072] Как проиллюстрировано на фиг. 6A, в период 1 ввода, формируется выходной тракт (как проиллюстрировано посредством пунктирных линий со стрелками на фиг. 6A), и выходной контактный вывод Output выводит высокий электрический уровень (в этом случае, как первый синхросигнал, так и второй синхросигнал имеют высокий электрический уровень).

[0073] В начальный период для периода 2 вывода, как проиллюстрировано на фиг. 5 и 6B, второй синхросигнал изменяется заранее (изменяется на высокий электрический уровень заранее) по сравнению с первым синхросигналом, и как пятый транзистор T5, так и восьмой транзистор T8 выключаются посредством высокого электрического уровня второго синхросигнала. Третий узел N3 поддерживает потенциал (низкий электрический уровень) в предыдущий период, и девятый транзистор T9 поддерживает включенное состояние. Второй синхросигнал повышает электрический уровень второго узла N2, с тем чтобы отключать седьмой транзистор T7. Первый транзистор T1 и второй транзистор T2 также отключаются под действием высокого электрического уровня второго узла N2. Первый узел N1 поддерживает потенциал (низкий электрический уровень) в предыдущий период; шестой транзистор T6 поддерживает включенное состояние; первый синхросигнал выводится на выходной контактный вывод Output; и выходной контактный вывод Output выводит высокий электрический уровень (в этом случае, первый синхросигнал имеет высокий электрический уровень).

[0074] Например, что касается каждого периода повторения импульсов первого синхросигнала и второго синхросигнала (включающего в себя один сигнал высокого электрического уровня и один сигнал низкого электрического уровня), длительность сигнала высокого электрического уровня не равна длительности сигнала низкого электрического уровня, так что второй синхросигнал может изменяться заранее по сравнению с первым синхросигналом, или первый синхросигнал может изменяться заранее по сравнению со вторым синхросигналом. Например, что касается первого синхросигнала и второго синхросигнала, длительность сигнала высокого электрического уровня превышает длительность сигнала низкого электрического уровня.

[0075] Когда первый синхросигнал изменяется на низкий электрический уровень, т.е. в другие периоды для периода 2 вывода (а именно, в период после начального периода для периода 2 вывода и перед периодом 3 сброса), выходной контактный вывод Output выводит сигнал низкого электрического уровня. Два электрода первого конденсатора C1, соответственно, соединяются с первым узлом N1 и выходным контактным выводом Output. В этом случае, первый узел N1 находится в состоянии поддержания уровня заряда, поскольку пятый транзистор T5 и второй транзистор T2 выключаются. Вследствие эффекта использования компенсационной обратной связи первого конденсатора C1, электрический уровень первого узла N1 дополнительно может уменьшаться вместе с уменьшением электрического уровня выходного сигнала выходного контактного вывода Output. После того, как электрический уровень первого узла N1 дополнительно уменьшается, электрический уровень может быть ниже первого сигнала напряжения, с тем чтобы отключать десятый транзистор T10. Эта компоновка позволяет отсоединять первый узел N1 и третий узел N3 в период 2 вывода, чтобы уменьшать утечку первого узла N1 и в таком случае повышать стабильность выходного сигнала выходного контактного вывода Output. Другими словами, блок сдвигового регистра, предоставленный посредством некоторых вариантов осуществления настоящего раскрытия, может повышать стабильность сигнала (например, повышать стабильность сигнала низкого электрического уровня), выводимого в допустимый период вывода электрического уровня (например, в период для вывода низкого электрического уровня в период 2 вывода). Например, пятый транзистор T5 и десятый транзистор T10 также могут реализовывать двухзатворную структуру, чтобы уменьшать утечку первого узла N1, с тем чтобы дополнительно повышать стабильность сигнала, выводимого в допустимый период вывода электрического уровня.

[0076] Например, второй синхросигнал изменяется заранее (изменяется на высокий электрический уровень заранее) по сравнению с первым синхросигналом, и время Δt опережения составляет приблизительно 5–25% от допустимого времени высокого электрического уровня первого синхросигнала или второго синхросигнала и, в качестве другого примера, 10–20% от допустимого времени высокого электрического уровня первого синхросигнала или второго синхросигнала. Конечно, время Δt опережения не ограничено этими случаями, и время Δt опережения также может определяться согласно фактическим потребностям, и ограничения не налагаются в варианте осуществления настоящего раскрытия.

[0077] Как проиллюстрировано на фиг. 6B, формируется выходной тракт (как проиллюстрировано посредством пунктирных линий со стрелками на фиг. 6B) в период 2 вывода; в начальный период для периода 2 вывода, выходной контактный вывод Output выводит высокий электрический уровень (в этом случае, первый синхросигнал имеет высокий электрический уровень); и в другие периоды для периода 2 вывода, за исключением начального периода (а именно, в период после начального периода для периода 2 вывода и перед периодом 3 сброса), выходной контактный вывод Output выводит низкий электрический уровень (в этом случае, первый синхросигнал имеет низкий электрический уровень).

[0078] В период 3 сброса, как проиллюстрировано на фиг. 5 и 6C, первый синхросигнал изменяется заранее (изменяется на высокий электрический уровень заранее) по сравнению со вторым синхросигналом, и выходной сигнал выходного контактного вывода Output изменяется на высокий электрический уровень. Аналогично, вследствие эффекта использования компенсационной обратной связи первого конденсатора C1, электрический уровень первого узла N1 также, соответственно, изменяется, с тем чтобы включать десятый транзистор T10 и электрически соединять первый узел N1 и третий узел N3. Например, первый синхросигнал изменяется заранее (изменяется на высокий электрический уровень заранее) по сравнению со вторым синхросигналом, и время Δt опережения является идентичным со временем опережения, как описано выше.

[0079] Когда второй синхросигнал изменяется на низкий электрический уровень, восьмой транзистор T8 включается; первый сигнал напряжения понижает электрический уровень второго узла N2; седьмой транзистор T7 включается посредством низкого электрического уровня второго узла N2; второй сигнал напряжения выводится на выходной контактный вывод Output; и выходной сигнал Выходного контактного вывода Output по–прежнему поддерживает высокий электрический уровень. Пятый транзистор T5 включается посредством низкого электрического уровня второго синхросигнала, и входной сигнал повышает электрический уровень в третьем узле N3 и первом узле N1, с тем чтобы отключать шестой транзистор T6. В этом случае, первый транзистор T1 включается посредством низкого электрического уровня во втором узле N2; второй транзистор T2 выключается посредством высокого электрического уровня первого синхросигнала; и девятый транзистор T9 выключается посредством высокого электрического уровня в третьем узле N3.

[0080] Как проиллюстрировано на фиг. 6C, в период 3 сброса, формируется тракт сброса (как проиллюстрировано посредством пунктирных линий со стрелками на фиг. 6C), и выходной контактный вывод Output выводит высокий электрический уровень.

[0081] В период 4 удержания сброса, как проиллюстрировано на фиг. 5 и 6D, второй синхросигнал имеет высокий электрический уровень, с тем чтобы отключать пятый транзистор T5 и восьмой транзистор T8. Второй узел N2 поддерживает потенциал (низкий электрический уровень) предыдущего периода, так что седьмой транзистор T7 поддерживает включенное состояние, и выходной сигнал выходного контактного вывода Output по–прежнему имеет высокий электрический уровень. Третий узел N3 поддерживает потенциал (высокий электрический уровень) предыдущего периода, и девятый транзистор T9 выключается посредством высокого электрического уровня в третьем узле N3. Первый транзистор T1 включается посредством низкого электрического уровня во втором узле N2.

[0082] Когда первый синхросигнал изменяется на низкий электрический уровень, второй транзистор T2 включается, с тем чтобы прикладывать второй сигнал напряжения к третьему узлу N3 и первому узлу N1, чтобы заряжать первый узел N1. Шестой транзистор T6 выключается посредством высокого электрического уровня первого узла N1. В последующие периоды, каждый раз, когда первый синхросигнал имеет низкий электрический уровень, второй транзистор T2 включается, и первый узел N1 заряжается. Посредством применения этих компоновок, первый узел N1 может прерывисто заряжаться, чтобы обеспечивать то, что шестой транзистор T6 выключается, и в таком случае повышать стабильность выходного сигнала выходного контактного вывода Output. Например, блок сдвигового регистра, предоставленный посредством некоторых вариантов осуществления настоящего раскрытия, может повышать стабильность сигнала, выводимого в период удержания сброса (например, повышать стабильность сигнала высокого электрического уровня), и в таком случае может продлевать время стабильного вывода, например, сигнала высокого электрического уровня.

[0083] Как проиллюстрировано на фиг. 6D, в период 4 удержания сброса, формируются тракт сброса и тракт для заряда первого узла N1 (как проиллюстрировано посредством пунктирной линии со стрелкой на фиг. 6D); выходной контактный вывод Output продолжает выводить высокий электрический уровень; и первый узел N1 заряжается, чтобы обеспечивать то, что шестой транзистор T6 выключается.

[0084] Фиг. 7 является принципиальной схемой, соответствующей периоду удержания сброса на фиг. 5, блока сдвигового регистра, как проиллюстрировано на фиг. 4. Ниже приводится описание принципа работы блока 10 сдвигового регистра, как проиллюстрировано на фиг. 4 со ссылкой на временную диаграмму последовательности сигналов, как проиллюстрировано на фиг. 5, и здесь приводится описание посредством рассмотрения случая, в котором транзисторы представляют собой транзисторы p–типа, в качестве примера, но вариант осуществления настоящего раскрытия не ограничен этим.

[0085] Помимо этого, все транзисторы, отмечаемые посредством пунктирных линий на фиг. 7 указывают то, что транзисторы, отмечаемые посредством пунктирных линий, находятся в отключенном состоянии в соответствующий период(ы), и пунктирные линии со стрелками на фиг. 7 представляют направление тока в блоке сдвигового регистра в соответствующий период(ы). Описание приводится посредством рассмотрения случая, в котором все транзисторы, как проиллюстрировано на фиг. 7, представляют собой транзисторы p–типа, в качестве примера, т.е. транзисторы включаются, когда электроды затвора транзисторов применяются с включенным электрическим уровнем (допустимым электрическим уровнем, который представляет собой низкий электрический уровень здесь), и транзисторы выключаются, когда электроды затвора транзисторов применяются с выключенным электрическим уровнем (недопустимым электрическим уровнем, который представляет собой высокий электрический уровень здесь). Нижеприведенные варианты осуществления являются идентичными в этом отношении, так что дополнительное описание здесь не приводится.

[0086] Как проиллюстрировано на фиг. 5, временная последовательность сигналов включает в себя четыре периода: период 1 ввода, период 2 вывода, период 3 сброса и период 4 удержания сброса. Фиг. 5 иллюстрирует временные формы сигнала сигналов в каждый период.

[0087] В период 1 ввода, период 2 вывода и период 3 сброса, поскольку электрический уровень первого синхросигнала и второго узла N2 не представляет собой низкий электрический уровень одновременно, третий транзистор T3 и четвертый транзистор T4 не могут одновременно включаться, так что второй сигнал напряжения второго контактного вывода VGH напряжения не может прикладываться к третьему узлу N3. В период 1 ввода, период 2 вывода и период 3 сброса, принцип работы блока 10 сдвигового регистра является аналогичным принципу работы блока 10 сдвигового регистра, как проиллюстрировано на фиг. 3, так что дополнительное описание здесь не приводится.

[0088] В период 4 удержания сброса, как проиллюстрировано на фиг. 5 и 7, второй синхросигнал имеет высокий электрический уровень, с тем чтобы отключать пятый транзистор T5 и восьмой транзистор T8. Второй узел N2 поддерживает потенциал (низкий электрический уровень) предыдущего периода, так что седьмой транзистор T7 поддерживает включенное состояние, и выходной сигнал выходного контактного вывода Output по–прежнему имеет высокий электрический уровень. Третий узел N3 поддерживает потенциал (высокий электрический уровень) предыдущего периода, и девятый транзистор T9 выключается посредством высокого электрического уровня в третьем узле N3. Третий транзистор T3 включается посредством низкого электрического уровня во втором узле N2.

[0089] Когда первый синхросигнал изменяется на низкий электрический уровень, четвертый транзистор T4 включается, с тем чтобы прикладывать второй сигнал напряжения к третьему узлу N3 и первому узлу N1, чтобы заряжать первый узел N1. Шестой транзистор T6 выключается посредством высокого электрического уровня первого узла N1. В последующие периоды, каждый раз, когда первый синхросигнал имеет низкий электрический уровень, четвертый транзистор T4 включается, и первый узел N1 заряжается. Посредством применения этих компоновок, первый узел N1 может прерывисто заряжаться, чтобы обеспечивать то, что шестой транзистор T6 выключается, и в таком случае повышать стабильность выходного сигнала выходного контактного вывода Output.

[0090] Как проиллюстрировано на фиг. 7, в период 4 удержания сброса, формируются тракт сброса и тракт для заряда первого узла N1 (как проиллюстрировано посредством пунктирных линий со стрелками на фиг. 7); выходной контактный вывод Output продолжает выводить высокий электрический уровень; и первый узел N1 заряжается, чтобы обеспечивать то, что шестой транзистор T6 выключается.

[0091] По меньшей мере, один вариант осуществления настоящего раскрытия дополнительно предоставляет блок сдвигового регистра, который содержит одиннадцатый–восемнадцатый транзисторы, третий конденсатор и четвертый конденсатор. Блок сдвигового регистра может повышать стабильность выходного сигнала, предотвращать подвергание помехам выходного сигнала посредством других сигналов и повышать качество отображения.

[0092] Фиг. 8 является принципиальной схемой блока сдвигового регистра, предоставленного посредством некоторых вариантов осуществления настоящего раскрытия. Как проиллюстрировано на фиг. 8, блок 10 сдвигового регистра включает в себя одиннадцатый–восемнадцатый транзисторы T11–T18, третий конденсатор C3 и четвертый конденсатор C4.

[0093] Электрод затвора одиннадцатого транзистора T11 выполнен с возможностью соединяться с первым узлом N1; первый контактный вывод одиннадцатого транзистора T11 выполнен с возможностью соединяться с линией CLK1 первого синхросигнала, чтобы принимать первый синхросигнал; и второй контактный вывод одиннадцатого транзистора T11 выполнен с возможностью соединяться с выходным контактным выводом Output. Первый электрод третьего конденсатора C3 выполнен с возможностью соединяться с электродом затвора (первым узлом N1) одиннадцатого транзистора T11, и второй электрод третьего конденсатора C3 выполнен с возможностью соединяться со вторым контактным выводом (выходным контактным выводом Output) одиннадцатого транзистора T11.

[0094] Электрод затвора двенадцатого транзистора T12 выполнен с возможностью соединяться с первым контактным выводом VGL напряжения, чтобы принимать первый сигнал напряжения; двенадцатый транзистор T12 дополнительно включает в себя первый контактный вывод и второй контактный вывод; и второй контактный вывод двенадцатого транзистора T12 выполнен с возможностью соединяться с первым узлом N1. Электрод затвора тринадцатого транзистора T13 выполнен с возможностью соединяться с линией CLK2 второго синхросигнала, чтобы принимать второй синхросигнал; первый контактный вывод тринадцатого транзистора T13 выполнен с возможностью соединяться с входным контактным выводом Input, чтобы принимать входной сигнал; и второй контактный вывод тринадцатого транзистора T13 выполнен с возможностью соединяться с первым контактным выводом двенадцатого транзистора T12.

[0095] Электрод затвора четырнадцатого транзистора T14 выполнен с возможностью соединяться со вторым узлом N2; первый контактный вывод четырнадцатого транзистора T14 выполнен с возможностью соединяться со вторым контактным выводом VGH напряжения, чтобы принимать второй сигнал напряжения; и второй контактный вывод четырнадцатого транзистора T14 выполнен с возможностью соединяться со вторым контактным выводом (выходным контактным выводом Output) одиннадцатого транзистора T11. Первый электрод четвертого конденсатора C4 выполнен с возможностью соединяться с электродом затвора (вторым узлом N2) четырнадцатого транзистора T14, и второй электрод четвертого конденсатора C4 выполнен с возможностью соединяться с первым контактным выводом (вторым контактным выводом VGH напряжения) четырнадцатого транзистора T14.