Изобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам, и может быть использовано в системах приема, обработки и передачи цифровых и аналоговых данных, в которых необходима гальваническая изоляция приемника и передатчика данных.

В системах с гальванической изоляцией важными параметрами являются: напряжение изоляции, уровень стойкости к быстро меняющимся магнитным и электрическим полям окружения. Известны несколько типов гальванической развязки, которые применяются в интегральных микросхемах, среди них:

- трансформаторная,

- конденсаторная,

- оптоэлектронная,

- магниторезистивная.

Следует отметить, что наибольшее распространение получили трансформаторная и конденсаторная развязки, что обусловлено их технологичностью при интеграции в стандартные процессы изготовления интегральных микросхем. В интегральных микросхемах с трансформаторной развязкой достигается высокий уровень стойкости к магнитным полям, но они всегда уступают микросхемам с конденсаторной развязкой, что обусловлено конструкцией конденсаторов, в которой нет чувствительных к магнитным полям элементов. Уровень стойкости к быстро меняющимся электрическим полям зависит от конструктивных особенностей всего тракта прима и передачи гальванически развязанного сигнала. В частности, в системах с конденсаторной изоляцией применяется дифференциальная система приема и передачи сигнала, для чего в приемнике и передатчике используются пары изолирующих конденсаторов. При быстром изменении разности напряжений на изолированных частях интегральной микросхемы происходит перезарядка емкостей изолирующих конденсаторов, что вызывает появление токов в цепях приемника и передатчика, которые могут вызвать нарушение их режима работы и, как следствие, сбой в работе устройства. Положительный эффект от использования пар конденсаторов заключатся в том, что сигнал между изолированными частями приемника и передатчика передается в виде разницы напряжений на парных конденсаторах, на которую токи, возникающие при быстром изменения разности напряжений на изолированных частях интегральной микросхемы, не оказывают столь существенное влияние в сравнении с одиночными изолирующими конденсаторами. Каждый изолирующий конденсатор выполняется с использованием металлических слоев интегральной микросхемы, количество которых влияет на такие параметры, как напряжение изоляции, проходная емкость и емкость обкладок конденсатора относительно общей подложки. Напряжение изоляции возрастает при увеличении количества металлических слоев, а проходная емкость уменьшается. При этом, чем выше расположен уровень металлического слоя, используемого в качестве нижней обкладки изолирующего конденсатора, тем ниже напряжение изоляции. Емкость нижней обкладки относительно общей подложки также зависит от того, какой уровень металлического слоя в ней использован. Чем выше этот уровень, тем емкость меньше, что определяется количеством и толщиной низ лежащих диэлектрических слоев. Емкость верхней обкладки, обычно выполняемой в самом верхнем уровне металла, также зависит от количества используемых металлических слоев и уменьшается с увеличением их количества.

В материале (Capacitive Isolation: A Fundamental Building Block in Future AC/DC Power Conversion, by Zhihong Yu, AC/DC & Lighting Product Marketing Manager, Monolithic Power Systems) [2] описывается интегральная схема с возможностью развязки по напряжению, которая содержит два гальванически изолированных кристалла, содержащих функциональные схемы, расположенные в подложках указанных кристаллов, а также интегрированные схемы емкостной развязки функциональных схем, причем схема емкостной развязки выполнена в проводящих слоях кристаллов. Схемы емкостной развязки содержат как минимум по два конденсатора на каждом кристалле и имеют верхнюю и нижнюю обкладки, выполненные в проводящих слоях соответствующих кристаллов. Функциональные схемы электрически связаны с нижними обкладками конденсаторов, а верхние обкладки используются для соединения изолированных кристаллов друг с другом, создавая емкостную связь между кристаллами. Сигналы между функциональными схемами передаются через изолирующие конденсаторы, которые соединяются последовательно, что обуславливает напряжение изоляции равное сумме двух изолирующих напряжений. На одном из кристаллов, называемом передатчике, присутствует схема формирования передаваемого дифференциального сигнала, а на втором кристалле, называемом приемнике, содержится схема приема и усиления дифференциального сигнала. Форма и частота передаваемого сигнала определяется величиной проходной емкости изолирующих конденсаторов и может быть близкой к синусоидальной, с частотой сотни мегагерц. При этом на амплитуду принимаемого сигнала существенное влияния оказывают не только проходные емкости изолирующих конденсаторов, но и паразитные емкости обкладок конденсаторов. Существенное влияние оказывает паразитная емкость нижней обкладки, уменьшение которой позволяет увеличить сигнал на входе приемника, тем самым повысить надежность приема, а также увеличить уровень стойкости к воздействию сигнала синфазной помехи.

Наиболее близким к заявленному изобретению является известное из уровня техники устройство конденсаторной изоляции, представленного в патенте [1]. Это устройство выбрано в качестве прототипа предложенного устройства.

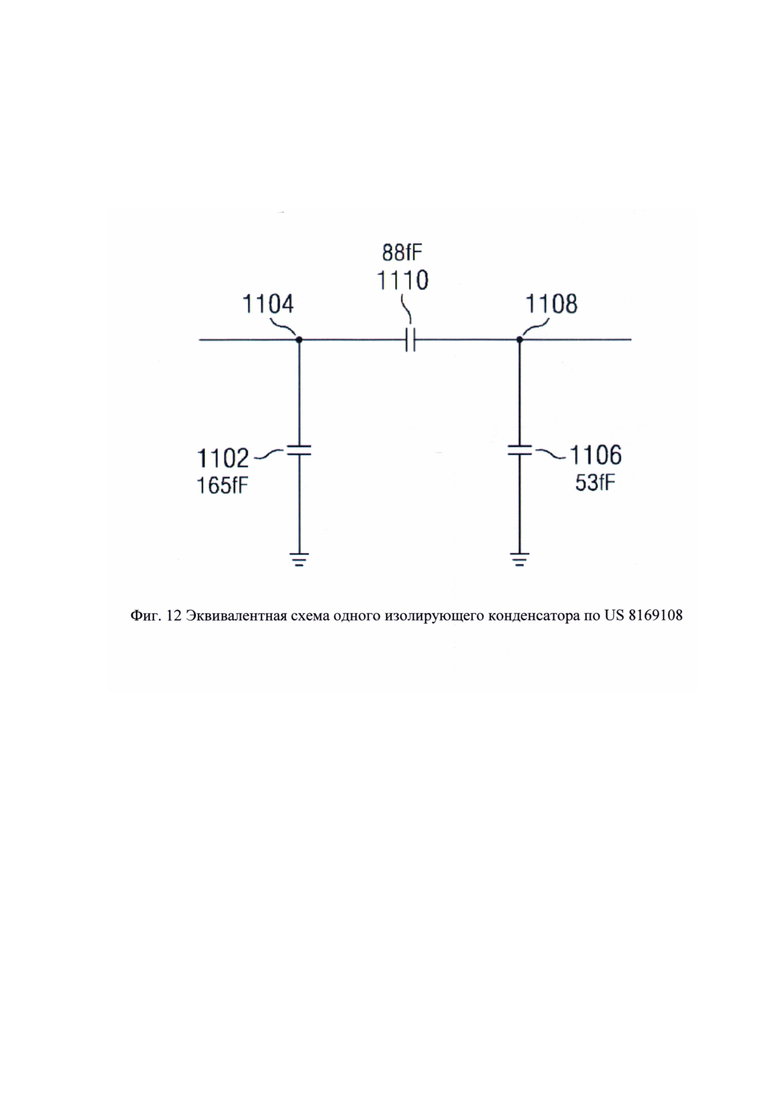

К недостаткам указанного изобретения следует отнести конструкцию изолирующих конденсаторов, в которой проходная емкость оказывается меньше паразитной емкости нижней обкладки относительно подложки. В прототипе, на фиг. 12, их значения указаны как 88фФ и 165фФ соответственно. Это приводит к уменьшению амплитуды полезного сигнала на входе приемника и к снижению уровня стойкости к синфазной помехе.

Задачей настоящего изобретения является создание устройства конденсаторного изолятора с более высоким напряжением изоляции и меньшей величиной емкости нижней обкладки изолирующих конденсаторов.

Технический результат заключается в уменьшении емкости нижней обкладки изолирующего конденсатора за счет применения изолирующей области в подложке микросхемы, расположенной под нижней обкладкой изолирующего конденсатора, что позволяет использовать первый проводящий слой в качестве нижней обкладки изолирующего конденсатора без существенного снижения амплитуды дифференциального сигнала на входе приемника.

Для достижения вышеуказанного технического результата устройство конденсаторной изоляции, содержащее первую область интегральной микросхемы, включающую функциональные схемы, схемы управления конденсаторной изоляцией, расположенные в подложке интегральной схемы, содержащие изолирующие конденсаторы, выполненные с использованием проводящих слоев этой интегральной микросхемы, а также вторую область интегральной микросхемы, включающую функциональные схемы, схемы управления конденсаторной изоляцией, содержащие изолирующие конденсаторы, выполненные с использованием проводящих слоев этой интегральной микросхемы, при этом схема емкостной изоляции первой области интегральной схемы включает первый изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном с функциональными схемами, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к первому выходу, а также второй изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном с функциональными схемами, а также вторую обкладку, расположенную на втором проводящем слое и подключенную ко второму выходу; схема емкостной изоляции второй области интегральной схемы включает третий изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном с функциональными схемами, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к третьему выходу, а также четвертый изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном с функциональными схемами, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к четвертому выходу, при этом, с помощью устройства коммутации, первый выход электрически соединен с третьим выходом, а второй выход соединен с четвертым выходом.

Существует вариант, в котором изолированные области интегральных микросхем содержат шесть проводящих слоев, при этом нижняя обкладка изолирующих конденсаторов выполнена в первом проводящем слое, верхняя обкладка выполнена в шестом проводящем слое, а каждый изолирующий конденсатор содержит область изоляции нижней обкладки конденсатора, расположенную в подложке микросхемы.

Указанный технический результат достигается посредством того, что в устройстве конденсаторного изолятора дополнительно используется изолирующие области, расположенные в подложках интегральных микросхем, непосредственно под нижними обкладками изолирующих конденсаторов, а область изоляции нижней обкладки конденсатора выполнена в виде сетки вертикальных диэлектрических слоев.

Сущность изобретения поясняется чертежами, где:

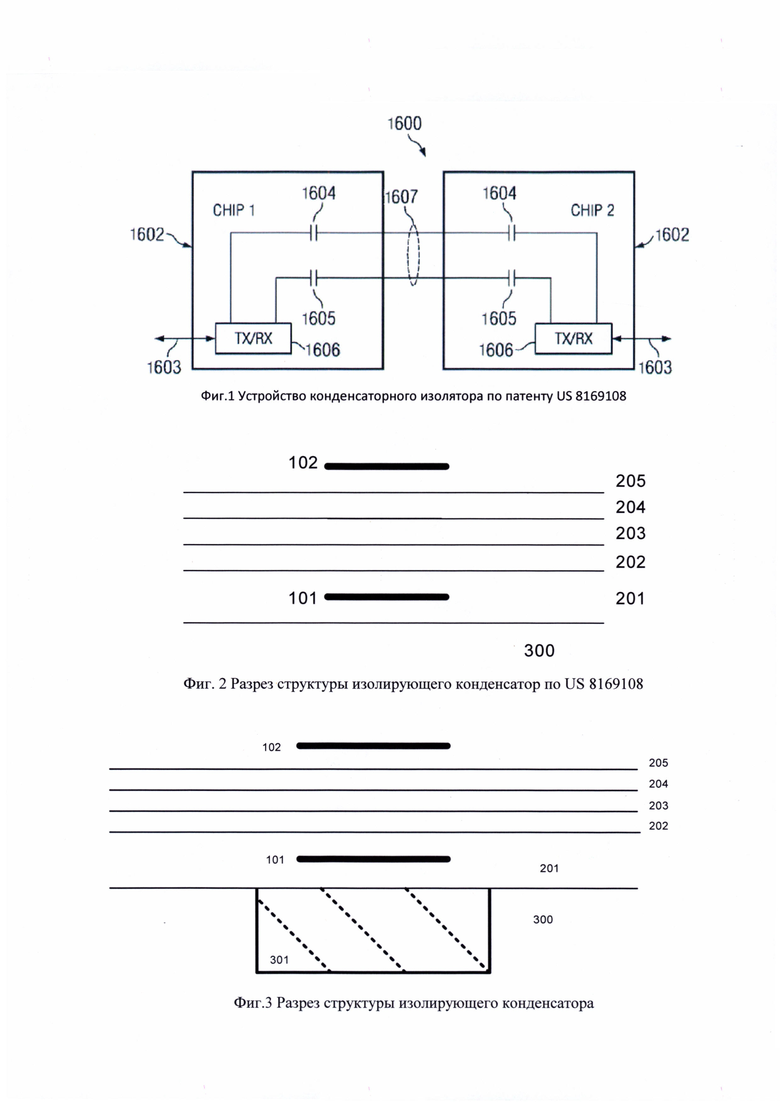

- на Фиг. 1 изображено устройство конденсаторного изолятора по патенту (1), где

1602 - первая и вторая области интегральных микросхем,

1603 - входы и выходы данных приемника и передатчика,

1604 - первые изолирующие конденсаторы,

1605 - вторые изолирующие конденсаторы,

1606 - функциональные схемы приемников и передатчиков,

1607 - устройство соединения конденсаторов изолированных микросхем.

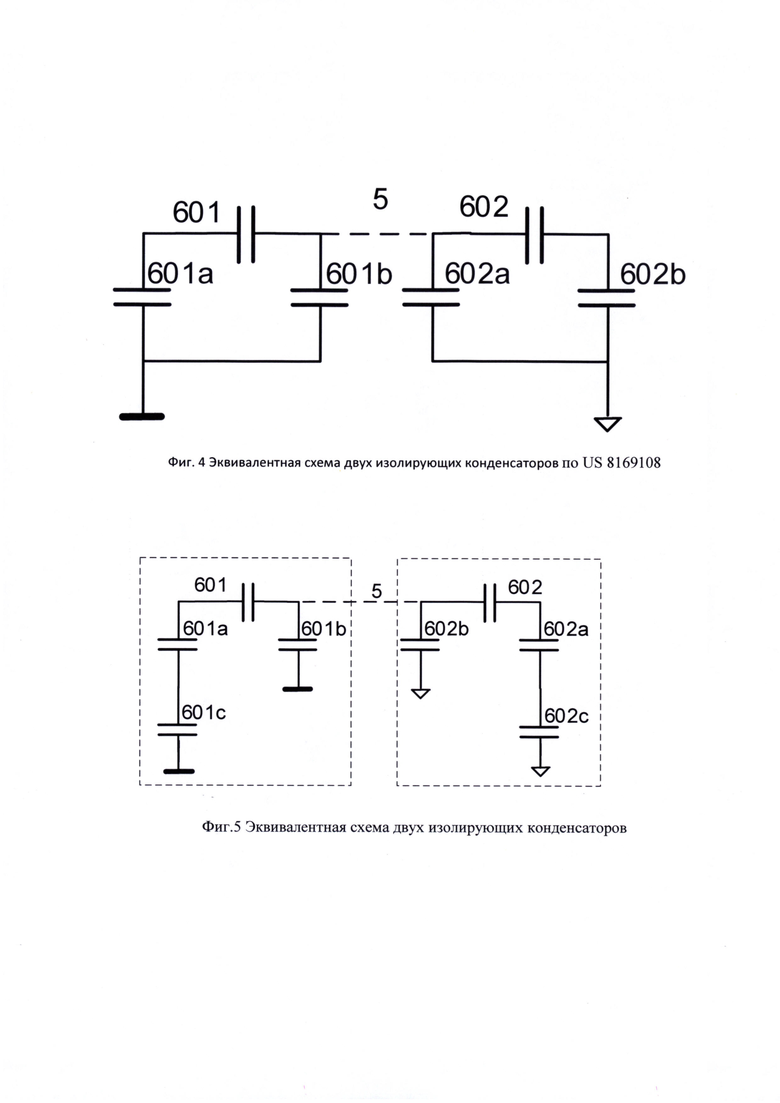

- на Фиг. 2 изображен разрез структуры изолирующего конденсатора по (1), где

300 - подложка кристалла,

101 - проводящая область нижней обкладки конденсатора,

102 - проводящая область верхней обкладки конденсатора,

201-206 - изолирующие области проводящих слоев микросхемы.

- на Фиг. 3 изображен разрез структуры изолирующего конденсатора по данному изобретению, где

300 - подложка кристалла,

301 - изолирующая область,

101 - проводящая область нижней обкладки конденсатора,

102 - проводящая область верхней обкладки конденсатора,

201-206 - изолирующие области проводящих слоев микросхемы.

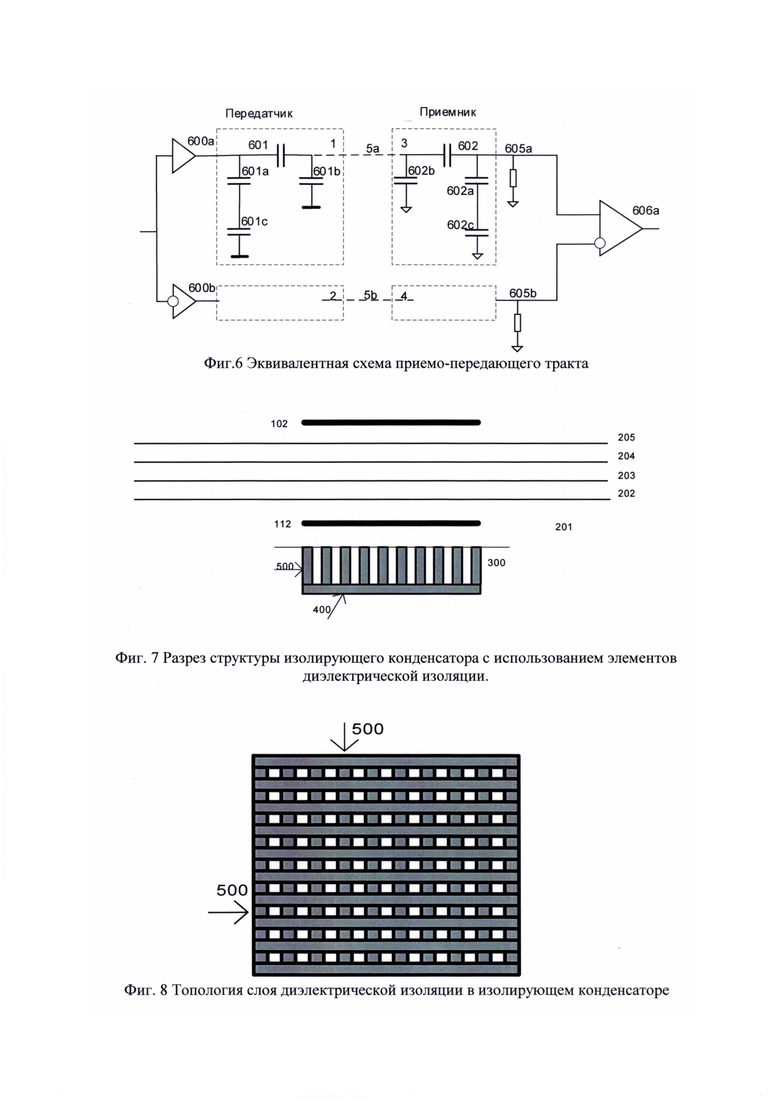

- на Фиг. 4 изображена эквивалентная схема двух изолирующих конденсаторов по патенту (1) где

601 - проходная емкость изолирующего конденсатора первой микросхемы,

601а - емкость нижней обкладки на подложку микросхемы,

601b - емкость верхней обкладки на подложку микросхемы,

602 - проходная емкость изолирующего конденсатора второй микросхемы,

602а - емкость нижней обкладки на подложку микросхемы,

602b - емкость верхней обкладки на подложку микросхемы,

5 - соединение верхних обкладок изолирующих конденсаторов.

- на Фиг. 5 изображена эквивалентная схема двух изолирующих конденсаторов по данному изобретению, где

601 - проходная емкость изолирующего конденсатора первой микросхемы,

601а - емкость нижней обкладки на изолирующую область микросхемы,

601b - емкость верхней обкладки на обкладки на изолирующую область микросхемы,

601с - емкость изолирующей области микросхемы на подложку,

602 - проходная емкость изолирующего конденсатора первой микросхемы,

602а - емкость нижней обкладки на изолирующую область микросхемы,

602b - емкость верхней обкладки на обкладки на изолирующую область микросхемы,

602с - емкость изолирующей области микросхемы на подложку,

5 - соединение верхних обкладок изолирующих конденсаторов.

- на Фиг. 6 изображена эквивалентная схема приемо-передающего тракта по данному изобретению, где

600а,b - драйверы передатчика первой микросхемы,

1-4 - изолирующие конденсаторы микросхем передатчика и приемника,

605а,b - эквивалентные входные сопротивления приемника,

606а - емкость изолирующей области микросхемы на подложку,

5а,b - соединение верхних обкладок изолирующих конденсаторов.

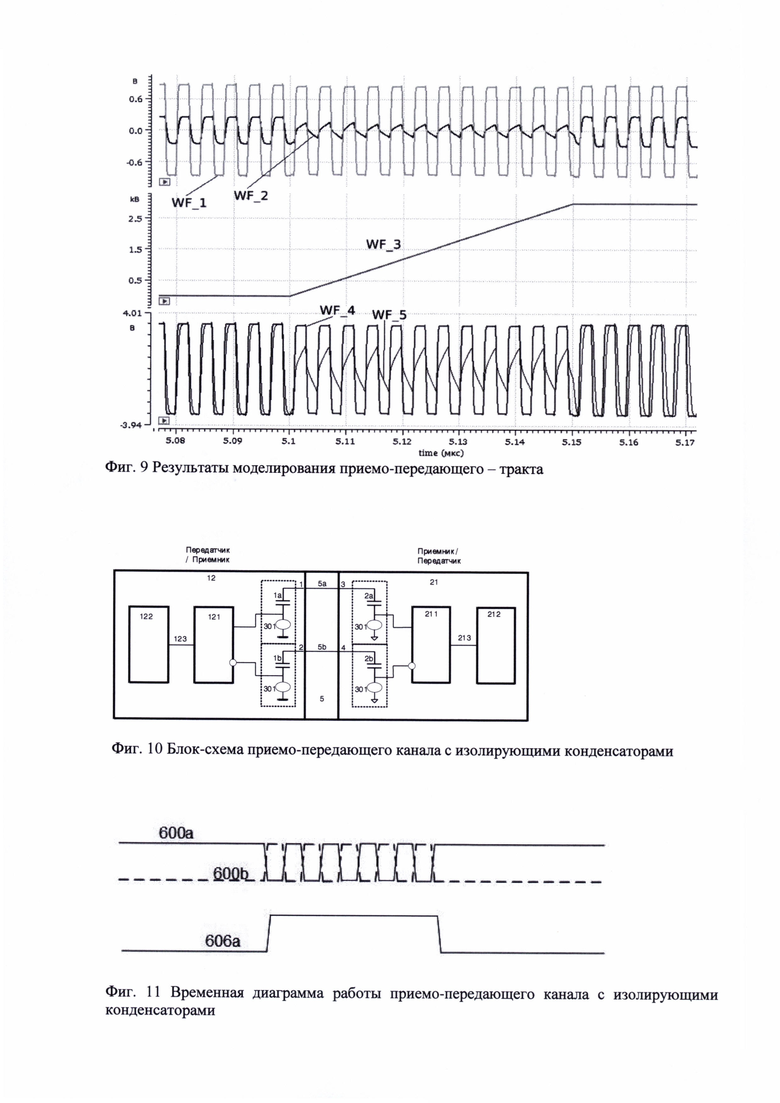

- на Фиг. 7 приведен разрез структуры изолирующего конденсатора по данному изобретению с использованием элементов диэлектрической изоляции, где

300 - подложка кристалла,

400 - горизонтальная изолирующая область,

500 - вертикальные изолирующие области,

101 - проводящая область нижней обкладки конденсатора,

102 - проводящая область верхней обкладки конденсатора,

201-206 - изолирующие области проводящих слоев микросхемы.

- на Фиг. 8 приведена топология слоя диэлектрической изоляции в изолирующем конденсаторе по данному изобретению, где

вертикальные изолирующие области 500 выполнены в виде сетки.

- на Фиг. 9 приведены результаты моделирования приемо-передающего тракта, где

WF_1 - дифференциальный сигнал на входе приемника при наличии изолирующей области под нижней обкладкой конденсатора,

WF_2 - дифференциальный сигнал на входе приемника при отсутствии изолирующей области под нижней обкладкой конденсатора,

WF_3 - дифференциальный сигнал синфазной помехи,

WF_4 - дифференциальный сигнал на выходе передатчика при наличии изолирующей области,

WF_5 - дифференциальный сигнал на выходе передатчика при отсутствии изолирующей области.

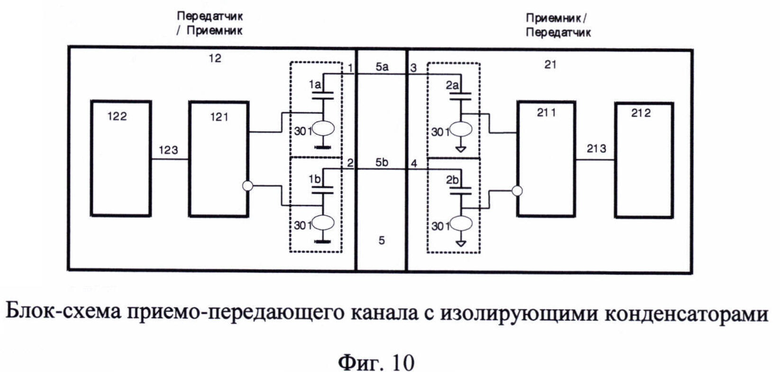

- на Фиг. 10 изображена блок-схема приемо-передающего канала с изолирующими конденсаторами по данному изобретению, где

12 и 21 - изолированные кристаллы микросхем,

122 и 212 - функциональные схемы,

121 и 211 - приемники и передатчики,

1а,b - изолирующие конденсаторы первого кристалла,

2а,b - изолирующие конденсаторы второго кристалла,

5 - устройство коммутации,

5а,b - соединение верхних обкладок изолирующих конденсаторов.

- на Фиг. 11 приведена временная диаграмма работы приемопередающего канала с изолирующими конденсаторами по данному изобретению, где

700а,b - сигналы на выходах драйверов передатчика,

701 - сигнал, восстановленный на выходе приемника.

- на Фиг. 12 приведена эквивалентная схема одного изолирующего конденсатора по US 8169108, где

1110 - изолирующий конденсатор,

1102 - паразитный конденсатор нижней обкладки,

1104 - нижняя обкладка,

1106 - паразитный конденсатор верхней обкладки,

1108 - верхняя обкладка.

Изобретение осуществляется следующим образом.

Устройство конденсаторной изоляции содержит (фиг. 10) первую область интегральной микросхемы 12, включающую функциональные схемы 122, схемы управления конденсаторной изоляцией 121, расположенные в подложке интегральной схемы, а также изолирующие конденсаторы 1a, 1b, выполненные с использованием проводящих слоев этой интегральной микросхемы, а также вторую область интегральной микросхемы 21, включающую функциональные схемы 212, схемы управления конденсаторной изоляцией 211, а также изолирующие конденсаторы 2а, 2b, выполненные с использованием проводящих слоев этой интегральной микросхемы, при этом схема емкостной изоляции первой области интегральной микросхемы включает первый изолирующий конденсатор 1а, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией 121, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к первому выходу 1, а также второй изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией 121, а также вторую обкладку, расположенную на втором проводящем слое и подключенную ко второму выходу 2, схема емкостной изоляции второй области интегральной микросхемы включает третий изолирующий конденсатор 2а, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией 211, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к третьему выходу 3, а также четвертый изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией 211, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к четвертому выходу 4, при этом, с помощью устройства коммутации 5, первый выход электрически соединен с третьим выходом, второй выход соединен с четвертым выходом, а каждый изолирующий конденсатор содержит область 301, которая расположена в подложке микросхемы, под нижней обкладкой конденсатора.

В частном случае выполнения изобретения изолированные области интегральных микросхем содержат шесть проводящих слоев, при этом нижняя обкладка изолирующих конденсаторов выполнена в первом проводящем слое, а верхняя обкладка выполнена в шестом проводящем слое, а область 301 (Фиг. 3) выполнена в виде сетки вертикальных диэлектрических слоев (фиг. 8).

Условные сечения изолирующих конденсаторов приведены на фиг. 2 и 3, на которых 101 и 102 - нижняя и верхняя обкладки изолирующих конденсаторов, 201-205 - изолирующие слои диэлектрика, 300 - подложка микросхемы, 301 - изолированная область. Использование изолированных областей 301, расположенных в подложках интегральных микросхем непосредственно под нижними обкладками изолирующих конденсаторов, позволяет уменьшить емкость нижних обкладок изолирующих конденсаторов относительно подложки микросхемы. При этом достигаются два положительных эффекта: во-первых, возрастает амплитуда дифференциального сигнала, поступающего на входы приемника и, во-вторых, снижается эффект воздействия синфазной помехи. На фиг. 4 и 5 представлены эквивалентные схемы двух связанных электрически изолирующих конденсаторов, поясняющие эффект дополнительной изолирующей области. Уменьшение емкостей нижних обкладок изолирующих конденсаторов происходит за счет емкостей дополнительных изолирующих областей 601с, 602с, включенных последовательно с емкостями нижних обкладок 601а, 602а. На фиг. 6 представлена эквивалентная схема одного канала приемо-передающего тракта, который содержит драйверы 600а, 600b, изолирующие конденсаторы 1-4, эквивалентные входные сопротивления приемника 605а, 605b и дифференциальный приемник 606а. На фиг. 9 представлены результаты моделирования процесса передачи дифференциального выходного сигнала WF_4 через изолирующие конденсаторы на вход приемника: WF_2 при отсутствии изолирующей области и WF_1 при ее наличии. На интервале времени 5.08 мкс - 5.1 мкс амплитуды сигналов отличаются более чем в 2 раза. На интервале времени 5.1 мкс - 5.15 мкс синфазный сигнал WF_3 изменяется с 0 В до 3 кВ, что соответствует скорости изменения 60 кВ/мкс. При этом сигнал WF_2 значительно уменьшается по амплитуде и изменяет свою форму, а сигнал WF_1 лишь слабо уменьшается по амплитуде при сохранении формы. Такое поведение сигналов на входе приемника связано с тем, что перезарядка емкости нижней обкладки изолирующих конденсаторов приводит к увеличению выходного тока драйверов и, как следствие, к увеличению падения напряжения на его выходных транзисторах, что способствует как уменьшению выходного напряжения, так и изменению формы выходного сигнала WF_4, WF_5.

Была разработана, изготовлена и исследована интегральная микросхема цифрового приемо-передатчика, содержащего четыре цифровых реверсивных канала на основе КМОП технологии с проектной нормой 0,18 мкм и полной диэлектрической изоляцией.

Конструкция изолирующего конденсатора включала первый и шестой уровни металлов в качестве обкладок изолирующих конденсаторов и сетку из вертикальных диэлектрических слоев в качестве изолирующего слоя, расположенного под нижней обкладкой конденсаторов. Размеры конденсаторов составляли 103 мкм х 103 мкм. Драйверы передатчика выполнены на основе КМОП транзисторов с рабочим напряжением 5 В и размерами W=72 мкм, L=0,5 мкм и W=32 мкм, L=0,5 мкм, соответственно р- и п-канальные транзисторы. Приемники выполнены на основе 3-х каскадов дифференциальных усилителей с емкостной развязкой, а также схем детектора и компаратора уровней усиленных сигналов. Формы передаваемых и принимаемых сигналов приведены на фиг. 11, где 600а, 600b - сигналы на выходах драйвера, а 606а - сигнал на выходе компаратора уровней. Уровню логического нуля соответствуют временные интервалы, на которых отсутствуют импульсы, а уровню логической единицы - временные интервалы, заполненные импульсами. Измерения показали, что напряжение изоляции превышает 5 кВ, а уровень стойкости к воздействию быстро меняющихся электрических полей превышает скорость изменения 20 кВ/мкс.

Литература

1. Патент США 8,169,108.

2. Capacitive Isolation: A Fundamental Building Block in Future AC/DC Power Conversion, by Zhihong Yu, AC/DC & Lighting Product Marketing Manager, Monolithic Power Systems.

| название | год | авторы | номер документа |

|---|---|---|---|

| Проекционно-ёмкостная сенсорная панель и способ её изготовления | 2016 |

|

RU2695493C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ НАКОПИТЕЛЬНОГО КОНДЕНСАТОРА ЭЛЕМЕНТА ПАМЯТИ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2110870C1 |

| НАКОПИТЕЛЬНЫЙ КОНДЕНСАТОР ЭЛЕМЕНТА ПАМЯТИ ИНТЕГРАЛЬНЫХ СХЕМ | 1991 |

|

RU2030813C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КОНДЕНСАТОРА ИНТЕГРАЛЬНОЙ СХЕМЫ | 1990 |

|

SU1817606A1 |

| АНТЕННА С ПЕРЕМЕННОЙ ЕМКОСТЬЮ ДЛЯ ПОДКЛЮЧЕНИЯ | 2001 |

|

RU2258282C2 |

| КОМБИНИРОВАННЫЙ СУХОЙ ЭЛЕКТРОННЫЙ ТРАНСФОРМАТОР С ОРГАНИЧЕСКОЙ ИЗОЛЯЦИЕЙ ДЛЯ ВЫВОДА ОПТИЧЕСКИХ СИГНАЛОВ | 2005 |

|

RU2353994C2 |

| СИСТЕМЫ И СПОСОБЫ ДЛЯ ПЕРЕДАЧИ ДАННЫХ ПОСРЕДСТВОМ БЕСКОНТАКТНОГО ЦИЛИНДРИЧЕСКОГО ИНТЕРФЕЙСА | 2019 |

|

RU2780225C2 |

| СТРУКТУРА СОЕДИНЕНИЙ ЭЛЕМЕНТОВ ВЫСОКОЧАСТОТНЫХ МИКРОСХЕМ (ВАРИАНТЫ) | 1994 |

|

RU2158992C2 |

| УЗЕЛ ОФТАЛЬМОЛОГИЧЕСКОЙ ЛИНЗЫ СО ВСТРОЕННОЙ КОНСТРУКЦИЕЙ АНТЕННЫ | 2013 |

|

RU2621483C2 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

Изобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам, и может быть использовано в системах приема, обработки и передачи цифровых и аналоговых данных, в которых необходима гальваническая изоляция приемника и передатчика данных. Техническим результатом изобретения является уменьшение емкости нижней обкладки изолирующего конденсатора за счет применения изолирующей области в подложке микросхемы, расположенной под нижней обкладкой изолирующего конденсатора, что позволяет использовать первый уровень разводки в качестве нижней обкладки изолирующего конденсатора без существенного снижения амплитуды дифференциального сигнала на входе приемника. Устройство конденсаторной изоляции содержит первую и вторую области интегральных микросхем 12 и 21, включающие функциональные схемы 122, 212, схемы управления конденсаторной изоляцией 121, 211, расположенные в подложках интегральных микросхем, изолирующие конденсаторы 1a, 1b, 2а, 2b, выполненные с использованием проводящих слоев этих микросхем. Изолирующие конденсаторы содержат первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией, а также вторую обкладку, расположенную на втором проводящем слое, и подключены к выходам 1, 2, 3, 4. С помощью устройства коммутации 5 первый выход электрически соединен с третьим выходом, второй выход соединен с четвертым выходом, а каждый изолирующий конденсатор содержит область 301, расположенную в подложках микросхем, под нижними обкладками конденсаторов. 1 з.п. ф-лы, 12 ил.

1. Устройство конденсаторной изоляции, содержащее первую область интегральной микросхемы, включающую функциональные схемы, схемы управления конденсаторной изоляцией, а также изолирующие конденсаторы, расположенные в подложке интегральной схемы, выполненные с использованием проводящих слоев этой интегральной микросхемы, а также вторую область интегральной микросхемы, включающую функциональные схемы, схемы управления конденсаторной изоляцией, а также изолирующие конденсаторы, выполненные в подложке интегральной схемы, с использованием проводящих слоев этой интегральной микросхемы, при этом изолирующие конденсаторы первой области интегральной микросхемы включают первый изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к первому выходу, а также второй изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией, а также вторую обкладку, расположенную на втором проводящем слое и подключенную ко второму выходу, изолирующие конденсаторы второй области интегральной микросхемы включают третий изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к третьему выходу, а также четвертый изолирующий конденсатор, содержащий первую обкладку, расположенную на первом проводящем слое, соединенном со схемами управления конденсаторной изоляцией, а также вторую обкладку, расположенную на втором проводящем слое и подключенную к четвертому выходу, при этом с помощью устройства коммутации первый выход электрически соединен с третьим выходом, а второй выход соединен с четвертым выходом, а каждый изолирующий конденсатор содержит область изоляции нижней обкладки конденсатора, расположенную в подложке микросхемы.

2. Устройство по п. 1, отличающееся тем, что изолированные области интегральных микросхем содержат шесть проводящих слоев, при этом нижняя обкладка изолирующих конденсаторов выполнена в первом проводящем слое, верхняя обкладка выполнена в шестом проводящем слое, а область изоляции нижней обкладки конденсатора выполнена в виде сетки вертикальных диэлектрических слоев.

| US 8169108 B2, 01.05.2012 | |||

| ZHIHONG YU Capacitive Isolation: A Fundamental Building Block in Future AC/DC Power Conversion, https://web.archive.org/web/20220627115742/https://www.monolithicpower.com/en/capacitive-isolation-article; дата обращения: 30.01.2023 | |||

| Многоканальный радиочастотный модуль с частотным разнесением приема и передачи | 2016 |

|

RU2631224C1 |

| СИСТЕМЫ НАСТРАИВАЕМЫХ АНТЕНН | 2011 |

|

RU2499354C2 |

| Коловратный насос с вращающимися направляющим диском и цилиндрами, могущий служить двигателем | 1927 |

|

SU6177A1 |

| EP | |||

Авторы

Даты

2023-02-28—Публикация

2022-07-15—Подача