Изобретение относится к электронной технике, а более конкретно к технологии изготовления интегральных схем и может быть использовано при изготовлении МДП ИС.

Целью изобретения является повышение выхода годных интегральных схем за счет увеличения емкости конденсатора, упрощения способа изготовления и повышения пробивных напряжений изолирующего диэлектрического слоя.

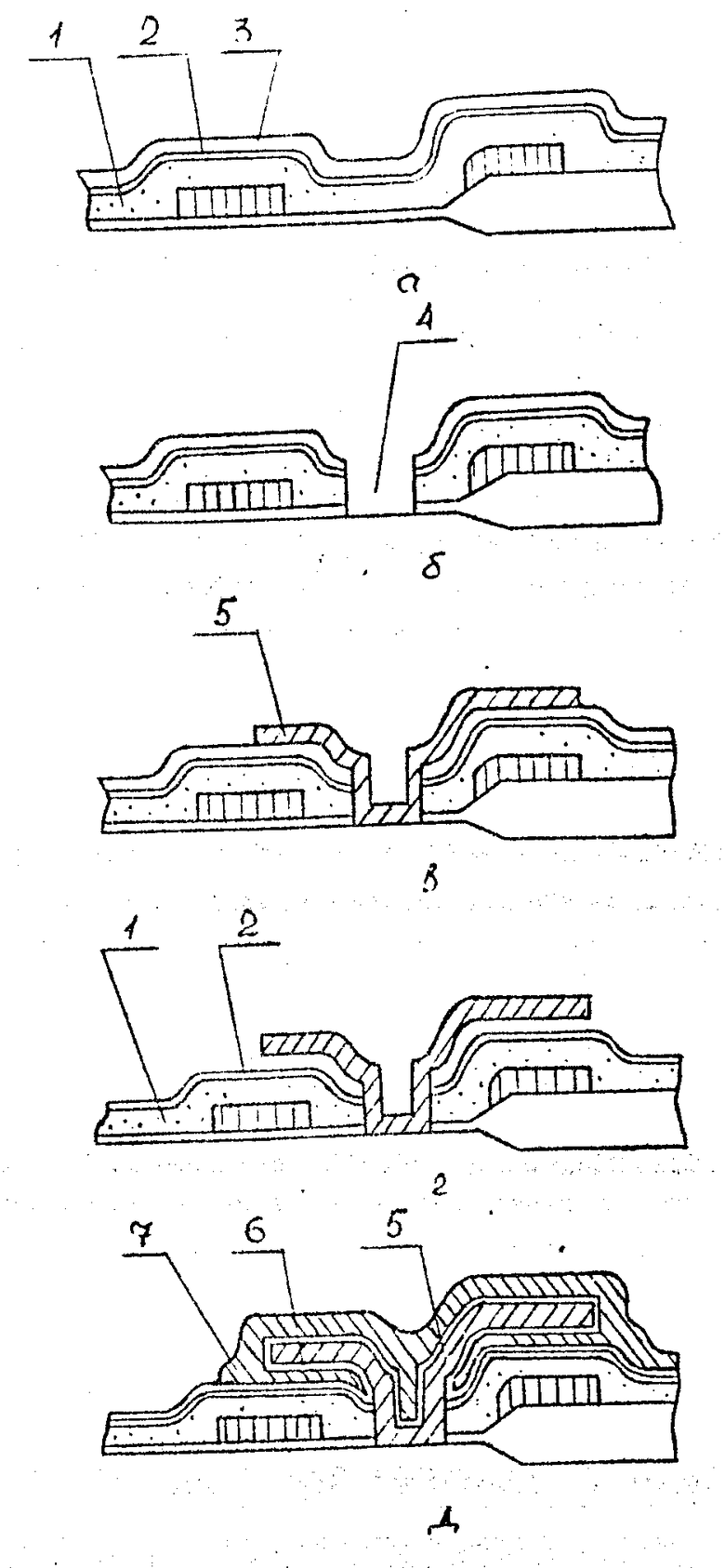

На чертеже изображены основные технологические этапы формирования конденсатора интегральной схемы (на фиг.1а сечение интегральной схемы после формирования комбинированного диэлектрического слоя, состоящего, например, из трех диэлектрических пленок 1, 2, 3, отличающихся свойствами реакционной способности и устойчивости к реагентам при удалении слоев; на 1б показано сечение после создания контактного окна 4 в диэлектрическом слое; на 1в - после нанесения слоя проводящего материала с последующим формированием с помощью фотолитографии и плазмохимического травления первой обкладки конденсатора 5; на 1г сечение после удаления диэлектрической пленки 3, при этом диэлектрическая пленка 2 устойчива к реагенту химической реакции травления диэлектрической пленки 3; на 1д сечение после формирования конденсаторного диэлектрика 6 и второй обкладки конденсатора 7).

Увеличение емкости конденсатора ячейки делает интегральную схему некритичной к разбросу из-за технологических процессов величины емкости, что повышает выход годных интегральных схем, а за счет снижения величины Cв/Cs повышается выходной сигнал и надежность в работе схемы, здесь Cв емкость разрядной шины в ДОЗУ, Cs емкость конденсатора ячейки памяти. Кроме того, увеличение емкости конденсатора ячейки памяти повышает время хранения информации ячейкой памяти, согласно выражению

τ=Cs•U/1,

где U напряжение между обкладками;

I ток утечки, что также повышает надежность работы интегральной схемы.

Способ изготовления конденсатора ячейки памяти обладает большей простотой по сравнению с прототипом, что обусловлено, прежде всего, устранением высокоселективной операции плазмохимического травления при формировании первой обкладки конденсатора. Так как в известном решении первая обкладка конденсатора лежит непосредственно на диэлектрическом слое, изолирующем конденсатор от полупроводниковой подложки и сформированных элементов интегральной схемы, то необходимо применение высокоселективного процесса плазмохимического травления поликремния. А вследствие конечности значения селективности и наличия значительного рельефа сформированных элементов, что вызывает необходимость перетрава, происходит частичное удаление диэлектрического слоя, что ухудшает его изолирующие свойства, сказывающиеся на снижении пробивных напряжений и, в конечном итоге, на снижении выхода годных.

В заявляемом техническом решении диэлектрический слой, предназначенный для изоляции конденсатора от сформированных элементов, сохраняется полностью, подтравы (уменьшение толщины) исключаются. Это обусловлено тем, что первая обкладка конденсатора наносится на комбинированный диэлектрический слой, верхняя диэлектрическая пленка которого впоследствии удаляется реагентами, к которым устойчивы другие диэлектрические пленки комбинированного диэлектрического слоя. Тем самым, получающийся затрав в верхнюю диэлектрическую пленку не страшен, так как она затем полностью удаляется, и одновременно сохраняются нижележащие диэлектрические пленки, которые обеспечивают изоляцию. Таким образом, заявляемое техническое решение упрощает способ изготовления конденсатора за счет исключения высокоселективных операций и позволяет обеспечить высокие пробивные напряжения изолирующего диэлектрического слоя, что в свою очередь обеспечивает повышение выхода годных.

Формирование комбинированного диэлектрического слоя проводится исходя из следующих требований:

нижняя часть слоя необходима для изоляции конденсатора от сформированных элементов на полупроводниковой подложке, при этом, чтобы обеспечить надежную изоляцию применяют среднетемпературный или высокотемпературный окисел, получаемый осаждением из газовой фазы;

верхняя часть слоя необходима для получения специальной конфигурации первой обкладки, поэтому эта часть слоя должна легко удаляться в травителях, для этого могут использоваться более рыхлые пленки по сравнению с остальными частями слоя, например, пленки фосфорно-силикатного стекла, скорость травления которых в травителях состава HF:H2O в 3-5 раз выше скорости травления среднетемпературного окисла;

средняя часть слоя может использоваться, если нижняя часть слоя все-таки несколько подтравливается в травителях при удалении верхней части, что будет ухудшать изолирующие свойства, поэтому средняя часть слоя будет служить в качестве стоп-слоя, предотвращающего подтравливание нижней части слоя, для этого используется пленка нитрида кремния, которая устойчива к травителям типа HF:H2O.

Таким образом, исходя из совокупности функциональных свойств каждой части диэлектрического слоя может быть сформирован комбинированный диэлектрический слой. Признак формирования комбинированного диэлектрического слоя, сходный с признаком заявляемого решения, известен в ряде технических решений. Однако сравнение свойств заявляемого и известных решений, обусловленные наличием в них указанных признаков, показало, что в заявляемом решении этот признак имеет новые функциональные свойства специальное формирование первой обкладки конденсатора с помощью комбинированного диэлектрического слоя. Часть диэлектрических пленок слоя имеют функции межуровневой изоляции, а верхние диэлектрические пленки имеют промежуточные функции для специальной конфигурации первой обкладки конденсатора, что и достигается после их удаления. Это и определяет основные свойства и функции комбинированного диэлектрического слоя, что в известных решениях не было обнаружено.

Кроме того, последовательность признаков изготовления конденсатора - формирование диэлектрического слоя с последующим удалением после создания первой обкладки конденсатора части диэлектрических пленок слоя также не обнаружен среди известных технических решений. Заявляемый способ проиллюстрируем на следующем примере.

На полупроводниковой подложке со сформированными активными и пассивными элементами СБИС ДОЗУ емкостью 256 Кбит после формирования шин затворов из поликристаллического кремния наносили комбинированный диэлектрический слой последовательным нанесением диэлектрических пленок: среднетемпературного окисла толщиной 0,3 мкм, пленки Si3N4 толщиной 200  и пленки фосфорно-силикатного стекла (ФСС) толщиной 0,15 мкм, которые отличаются свойствами реакционной способности и устойчивости к реагентам при удалении слоев, а именно, к травителю состава HF:H20 с соотношением 1:10, в котором удаляется пленка ФСС со скоростью 1,9-2,0 мкм/мин, а пленка Si3N4 устойчива к этому травителю. После формирования комбинированного диэлектрического слоя с помощью фотолитографии и плазмохимического травления создавали контактирующее окно, затем наносили пленку поликремния толщиной 0,2 мкм и формировали первую обкладку конденсатора. Причем при плазмохимическом травлении пленки поликремния значительно увеличивали время перетрава, что позволяло уменьшить процент закороток между элементами в слое первой обкладки при сохранении высоких изолирующих свойств диэлектрика. После формирования первой обкладки конденсатора проводили травление верхней диэлектрической пленки ФСС комбинированного диэлектрического слоя в травителе HF:H2O с соотношением 1:10 3 минуты, в результате чего пленка удалялась полностью под обкладкой, а диэлектрические пленки среднетемпературного окисла и Si3N4 сохраняли свои исходные толщины. Затем наносили пленку конденсаторного диэлектрика из Ni3N4 толщиной 180-200

и пленки фосфорно-силикатного стекла (ФСС) толщиной 0,15 мкм, которые отличаются свойствами реакционной способности и устойчивости к реагентам при удалении слоев, а именно, к травителю состава HF:H20 с соотношением 1:10, в котором удаляется пленка ФСС со скоростью 1,9-2,0 мкм/мин, а пленка Si3N4 устойчива к этому травителю. После формирования комбинированного диэлектрического слоя с помощью фотолитографии и плазмохимического травления создавали контактирующее окно, затем наносили пленку поликремния толщиной 0,2 мкм и формировали первую обкладку конденсатора. Причем при плазмохимическом травлении пленки поликремния значительно увеличивали время перетрава, что позволяло уменьшить процент закороток между элементами в слое первой обкладки при сохранении высоких изолирующих свойств диэлектрика. После формирования первой обкладки конденсатора проводили травление верхней диэлектрической пленки ФСС комбинированного диэлектрического слоя в травителе HF:H2O с соотношением 1:10 3 минуты, в результате чего пленка удалялась полностью под обкладкой, а диэлектрические пленки среднетемпературного окисла и Si3N4 сохраняли свои исходные толщины. Затем наносили пленку конденсаторного диэлектрика из Ni3N4 толщиной 180-200  и пленку поликремния, легированного в процессе роста фосфором, толщиной 0,2 мкм, после чего формировали с помощью фотолитографии и плазмохимического травления второй обкладки конденсатора.

и пленку поликремния, легированного в процессе роста фосфором, толщиной 0,2 мкм, после чего формировали с помощью фотолитографии и плазмохимического травления второй обкладки конденсатора.

В результате этого емкость конденсатора ячейки памяти увеличилась в 1,81 раза по сравнению с прототипом, процент закороток между адресными шинами и обкладкой первой конденсатора составил нулевую величину, процент закороток между элементами в слое первой обкладки уменьшился в 10 раз, а в целом выход годных интегральных схем увеличился в 1,32 раза. Время хранения заряда повысилось в 1,7-1,8 раза.

Был опробован также способ изготовления конденсатора интегральной схемы, когда комбинированный диэлектрический слой формировался последовательным нанесением среднетемпературного окисла, Si3N4, среднетемпературного окисла толщиной 500  и ФСС толщиной 0,1 мкм. Последовательность изготовления была аналогичной, как в предыдущем примере. Результаты этого способа были на том же уровне, что и в первом случае.

и ФСС толщиной 0,1 мкм. Последовательность изготовления была аналогичной, как в предыдущем примере. Результаты этого способа были на том же уровне, что и в первом случае.

Таким образом, заявляемое решение явно позволяет повысить выход годных интегральных схем за счет увеличения емкости конденсаторов, повышения изолирующих свойств диэлектрического слоя и упрощения способа изготовления.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1840163A1 |

| Способ изготовления тонкопленочного конденсатора электронной техники | 2022 |

|

RU2799811C1 |

| Способ изготовления компактного тренч-конденсатора | 2024 |

|

RU2825218C1 |

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1985 |

|

SU1371445A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1981 |

|

SU952051A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ НАКОПИТЕЛЬНОГО КОНДЕНСАТОРА ЭЛЕМЕНТА ПАМЯТИ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2110870C1 |

| Способ изготовления чувствительных элементов газовых датчиков | 2017 |

|

RU2650793C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108640C1 |

Использование: в электронной технике, в частности к технологии изготовления интегральных схем. Сущность изобретения: на полупроводниковую подложку со сформированными элементами наносят изолирующий диэлектрический слой (С) и одну или несколько пленок из диэлектрических материалов, травящихся избирательно. Затем формируют контактное окно и нижнюю обкладку конденсатора (К), после чего одну или несколько диэлектрических пленок удаляют. На поверхность нижней обкладки К наносят С диэлектрика и формируют верхнюю обкладку К. Указанная последовательность операций позволяет повысить выход годных интегральных схем за счет увеличения емкости К и пробивного напряжения изолирующего диэлектрического С. 1 ил.

Способ изготовления конденсатора интегральной схемы, включающий нанесение изолирующего диэлектрического слоя на полупроводниковую подложку со сформированными элементами, создание в диэлектрическом слое контактного окна, нанесение первого проводящего слоя с последующим формированием нижней обкладки конденсатора, последовательное нанесение на ее поверхность слоя конденсаторного диэлектрика, второго проводящего слоя и последующее формирование верхней обкладки конденсатора, отличающийся тем, что, с целью повышения выхода годных интегральных схем за счет увеличения емкости конденсатора и пробивного напряжения изолирующего диэлектрического слоя, а также упрощения процесса изготовления конденсатора, перед созданием контактного окна на изолирующий диэлектрический слой наносят дополнительный слой диэлектрика, выполненный из одной или нескольких последовательно нанесенных пленок из диэлектрических материалов, травящихся избирательно, причем после формирования нижней обкладки одну или несколько пленок удаляют.

| Накано Т | |||

| и др | |||

| Динамическое ЗУ с произвольной выборной с многоярусной структурой ячеек памяти | |||

| Nikkei Microdevices, 1987, N 1, с | |||

| Аппарат для испытания прессованных хлебопекарных дрожжей | 1921 |

|

SU117A1 |

Авторы

Даты

1996-10-10—Публикация

1990-07-02—Подача