Изобретение относится к области вычислительных устройств и программных алгоритмов и может быть использовано в системах и устройствах обработки информации, построенной на основе нечеткой логики.

Известно устройство оптоэлектронного дефаззификатора, предназначенного для оптических систем обработки информации, полученной на основе непрерывной (нечеткой) логики [Патент РФ №2408052, G06E 3/00 (аналог)].

Признаком аналога совпадающими с существующим заявляемым устройством, является использование нечеткой логики в алгоритме расчета, и наличие этапа дефаззификации в его структуре.

Недостаток описанного устройства в невысокой скорости обработки данных, а также отсутствием аддитивности, из-за применения методов дефаззификации первого и последнего максимумов.

Известно устройство дефаззификации на основе метода отношения площадей [Патент РФ №2701841, G06E 3/00, G06N 7/02 (прототип)].

Признаком прототипа совпадающими с существующим заявляемым устройством, является использование применения дефаззификации в структуре алгоритма нечеткого вывода для получения результирующего значения.

Недостатки указанного прототипа: сложная структура устройства; невысокая скорость обработки 590 нс из-за большого числа итераций, что увеличивает время выполнения операций тем самым снижая быстродействие; отсутствие блоков генератора управляющего сигнала, операций фаззификации и нечеткой импликации, т.е. отсутствие всех блоков нечетко-логического вывода.

Техническая задачей изобретения является повышение вычислительной производительности процесса дефаззификации до 160 нс и упрощение структуры устройства.

Техническая задача решается за счет исключения операции нахождения ширины верхнего основания трапециевидной функции принадлежности, что позволяет обеспечить повышение вычислительной скорости процесса де фаззификации.

Техническим результатом быстродействующего устройства нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности (Модификация 1) является генерация и преобразование входных данных в единственное четкое значение на выходе нечетко-логической системы. В структуре устройства использован 5-слойный анализатор, позволяющий проводить параллельные расчет по входной информации о степенях принадлежности входных переменных, используемых в предпосылках нечеткого вывода.

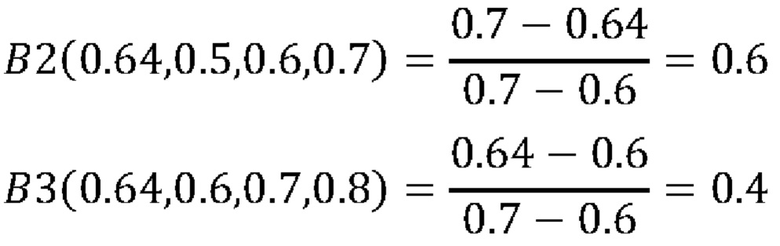

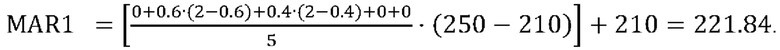

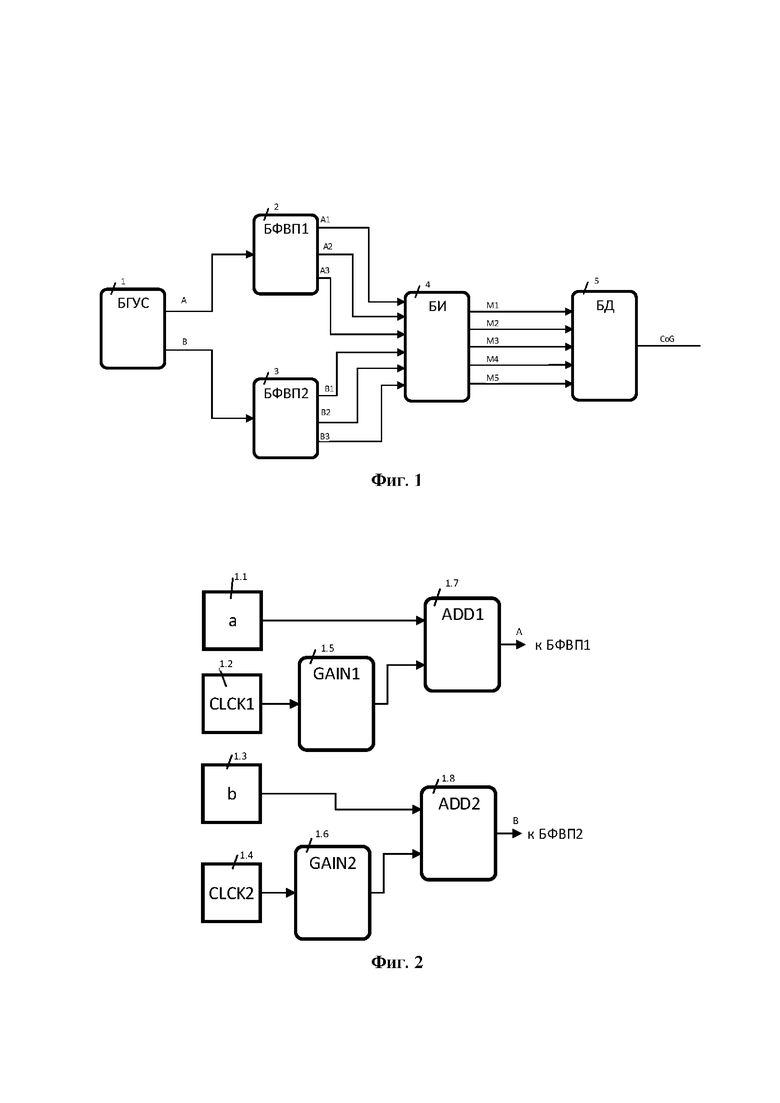

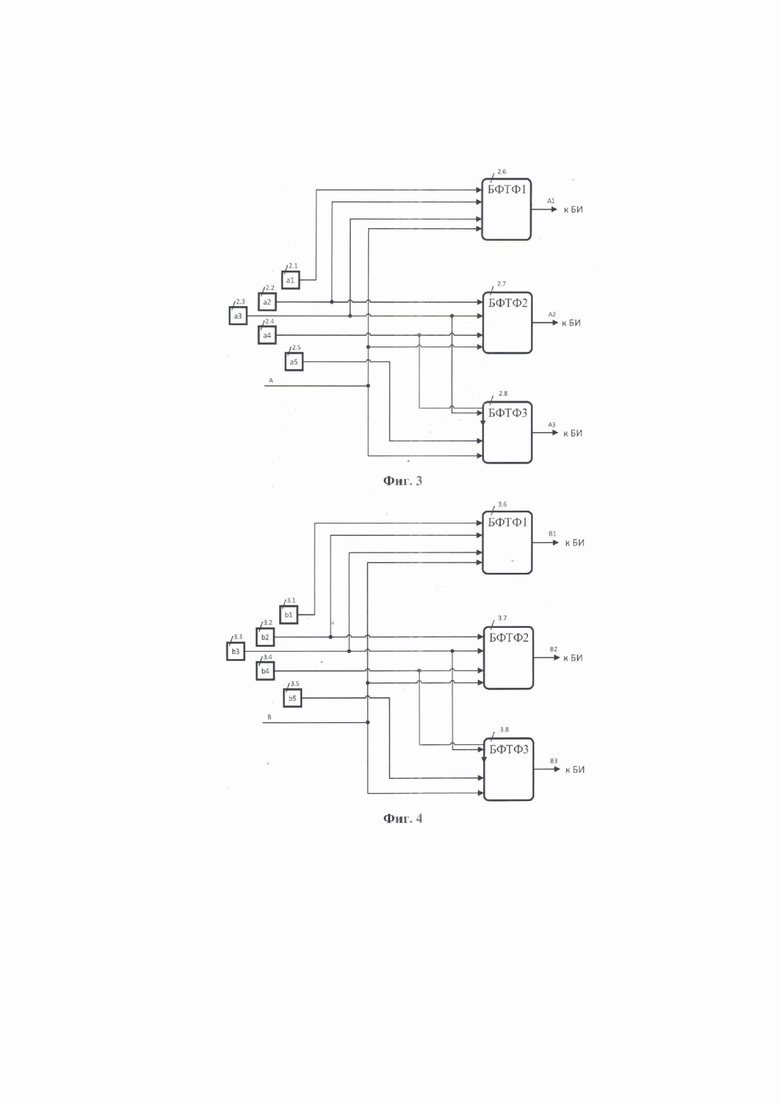

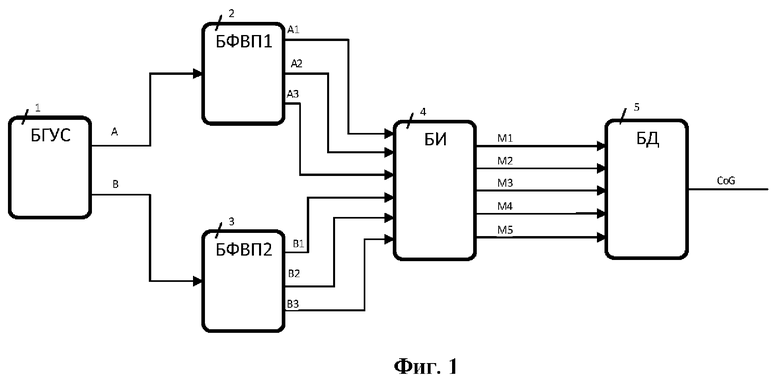

Изобретение поясняется чертежами: фиг. 1 - Быстродействующее устройство нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности (Модификация 1); фиг. 2 - Блок генератора управляющего сигнала (БГУС); фиг. 3 - Блок фаззификации первой входной переменной (БФВП1); фиг. 4 - Блок фаззификации второй входной переменной (БФВП2); фиг. 5 - Блок формирования треугольной функции (БФТФ); фиг. 6 - Блок импликации (БИ); фиг. 7 - Блок дефаззификации (БД); фиг. 8 - Треугольная функция принадлежности; фиг. 9 - Результаты моделирования в программе ISE Design v. 14.7, написанной на языке программирования VHDL.

Быстродействующее устройство нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности (Модификация 1) (фиг. 1) содержит блок генератора формирования управляющего сигнала БГУС 1, блок фаззификации первой входной переменной БФВП1 2, блок фаззификации второй входной переменной БФВП2 3, блок импликации БИ 4, быстродействующий дефаззификатор БД 5.

Блок генератора формирования управляющего сигнала БГУС 1 (фиг. 2) содержит блок входных переменных (управляющие сигналы, поступающие с разного рода датчиков) «а» 1.1 и «b» 1.3, счетчики CLCK 1.2, 1.4, усилители GAIN 1.5, 1.6, сумматоры ADD 1.7, 1.8.

Связи в БГУС 1 определяются следующим образом. Выход блока переменной «а» 1.1 соединен с первым входом сумматора ADD1 1.7. Выход счетчика CLCK1 1.2 соединен с входом усилителя GAIN1 1.5. Выход усилителя GAIN1 1.5 соединен со вторым входом сумматора ADD1 1.7. Выход блока переменной «b» 1.3 соединен с первым входом сумматора ADD2 1.8. Выход счетчика CLCK2 1.4 соединен с входом усилителя GAIN2 1.6. Выход усилителя GAIN2 1.6 соединен со вторым входом сумматора ADD2 1.8. Выходящие сигналы «А» и «В» блока из блоков ADD1 1.7 и ADD2 1.8, являются выходящими из БГУС 1 и соединены со входами БФВП1 2 и БФВП2 3 соответственно.

Блок фаззификации первой входной переменной БФВП1 2 (фиг. 3) содержит блоки переменных «a1» 2.1, «а2» 2.2, «а3» 2.3, «а4» 2.4, «а5» 2.5, блок формирования первой треугольной функции БФТФ1 2.6, блок формирования второй треугольной функции БФТФ2 2.7, блок формирования третей треугольной функции БФТФ3 2.8.

Связи в БФВП1 2 определяются следующим образом. Блок переменной «a1» 2.1 соединен с входом блока БФТФ1 2.6. Блок переменной «а2» 2.2 соединен с входами блоков БФТФ1 2.6 и БФТФ2 2.7. Блок переменной «а3» 2.3 соединен с входами блоков БФТФ1 2.6, БФТФ2 2.7 и БФТФ3 2.8. Блок переменной «а4» 2.4 соединен с входами блоков БФТФ2 2.7 и БФТФ3 2.8. Блок переменной «а5» 2.5 соединен с входом блока БФТФ3 2.8. Входной сигнал «А» соединен с входами блоков БФТФ1 2.6, БФТФ2 2.7, БФТФ3 2.8. Сигналы «А1», «А2», «A3» выходящие из БФТФ1 2.6, БФТФ2 2.7, БФТФ3 2.8 соответственно являются выходящими из БФВП1 2 и соединены с первыми 3 входами БИ 3.

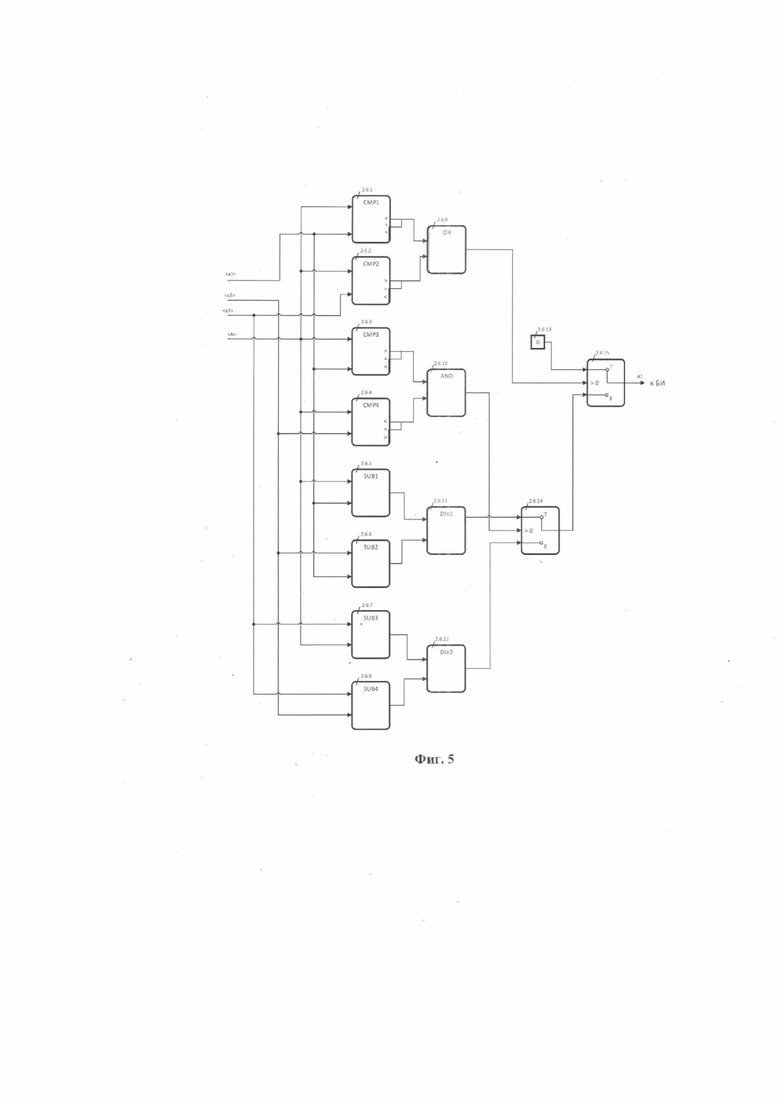

Блок формирования первой треугольной функции БФТФ1 2.6 (фиг. 5) содержит компараторы СМР 2.6.1÷2.6.4, вычитатели SUB 2.6.5÷2.6.8, блок OR 2.6.9, блок AND 2.6.10, делители DIV 2.6.11, 2.6.12, константу «0» 2.6.13, ключи SWITCH 2.6.14, 2.6.15.

Связи в БФТФ1 2.6 определяются следующим образом. Переменная «a1» соединена со вторым входом компаратора СМР1 2.6.1, вторым входом компаратора СМР3 2.6.3, вторым входом вычитателя SUB1 2.6.5 и вторым входом вычитателя SUB2 2.6.6. Переменная «а2» соединена со вторым входом компаратора СМР4 2.6.4, первым входом вычитателя SUB2 2.6.6 и вторым входом вычитателя SUB4 2.6.8. Переменная «а3» соединена со вторым входом компаратора СМР2 2.6.2, первым входом вычитателя SUB3 2.6.7 и первым входом вычитателя SUB4 2.6.8. Входной сигнал «А» соединен с первым входом компаратора СМР1 2.6.1, первым входом компаратора СМР2 2.6.2, первым входом компаратора СМР3 2.6.3, первым входом компаратора СМР4 2.6.4, первым входом вычитателя SUB1 2.6.5, вторым входом вычитателя SUB3 2.6.7. Выходные сигналы «<» и «=» компаратора СМР1 2.6.1 соединены между собой и подключены к первому входу блока OR 2.6.9. Выходные сигналы «>» и «=» компаратора СМР2 2.6.2 соединены между собой и подключены ко второму входу блока OR 2.6.9. Выходные сигналы «>» и «=» компаратора СМР3 2.6.3 соединены между собой и подключены к первому входу блока AND 2.6.10. Выходные сигналы «<» и «=» компаратора СМР4 2.6.4 соединены между собой и подключены к второму входу блока AND 2.6.10. Выходной сигнал вычитателя SUB1 2.6.5 соединен с первым входом делителя DIV1 2.6.11. Выходной сигнал вычитателя SUB2 2.6.6 соединен со вторым входом делителя DIV1 2.6.11. Выходной сигнал вычитателя SUB3 2.6.7 соединен с первым входом делителя DIV2 2.6.12. Выходной сигнал вычитателя SUB4 2.6.8 соединен со вторым входом делителя DIV2 2.6.12. Выходной сигнал блока OR 2.6.9 соединен со вторым входом (>0) ключа SWITCH2 2.6.15. Выходной сигнал блока AND 2.6.10 соединен со вторым входом (>0) ключа SWITCH2 2.6.14. Выходной сигнал делителя DIV1 2.6.11 соединен с первым входом (True) ключа SWITCH1 2.6.14. Выходной сигнал делителя DIV2 2.6.12 соединен с третьим входом (False) ключа SWITCH1 2.6.14. Выходной сигнал константы «0» 2.6.13 соединен с первым входом (True) ключа SWITCH2 2.6.15. Выходной сигнал ключа SWITCH1 2.6.14 соединен с третьим входом (False) ключа SWITCH2 2.6.15. Сигнал «А1» является выходящим сигналом блока БФТФ1 2.6, который выходит из ключа SWITCH2 2.6.15.

Блок формирования второй треугольной функции БФТФ2 2.7 содержит компараторы CMP 2.7.1÷2.7.4, вычитатели SUB 2.7.5÷2.7.8, блок OR 2.7.9, блок AND 2.7.10, делители DIV 2.7.11, 2.7.12, константу «0» 2.7.13, ключи SWITCH 2.7.14, 2.7.15.

Связи в БФТФ2 2.7 определяются аналогично блоку БФТФ1 2.6.

Блок формирования третьей треугольной функции БФТФ3 2.8 содержит компараторы CMP 2.8.1÷2.8.4, вычитатели SUB 2.8.5÷2.8.8, блок OR 2.8.9, блок AND 2.8.10, делители DIV 2.8.11, 2.8.12, константу «0» 2.8.13, ключи SWITCH 2.8.14, 2.8.15.

Связи в БФТФ3 2.8 определяются аналогично блоку БФТФ1 2.6.

Блок фаззификации второй входной переменной БФВП2 3 (фиг. 4) содержит блоки переменных «b1» 3.1, «b2» 3.2, «b3» 3.3, «b4» 3.4, «b5» 3.5, блок формирования первой треугольной функции БФТФ1 3.6, блок формирования второй треугольной функции БФТФ2 3.7, блок формирования третей треугольной функции БФТФ3 3.8.

Связи в БФВП2 3 определяются аналогично блоку БФВП1 2.

Блок формирования первой треугольной функции БФТФ1 3.6 содержит компараторы СМР 3.6.1÷3.6.4, вычитатели SUB 3.6.5÷3.6.8, блок OR 3.6.9, блок AND 3.6.10, делители DIV 3.6.11, 3.6.12, константу «0» 3.6.13, ключи SWITCH 3.6.14, 3.6.15.

вязи в БФТФ1 3.6 определяются аналогично блоку БФТФ1 2.6.

Блок формирования второй треугольной функции БФТФ2 3.7 содержит компараторы СМР 3.7.1÷3.7.4, вычитатели SUB 3.7.5÷3.7.8, блок OR 3.7.9, блок AND 3.7.10, делители DIV 3.7.11, 3.7.12, константу «0» 3.7.13, ключи SWITCH 3.7.14, 3.7.15.

Связи в БФТФ2 3.7 определяются аналогично блоку БФТФ1 2.6.

Блок формирования третьей треугольной функции БФТФ3 3.8 содержит компараторы СМР 3.8.1÷3.8.4, вычитатели SUB 3.8.5÷3.8.8, блок OR 3.8.9, блок AND 3.8.10, делители DIV 3.8.11, 3.8.12, константу «0» 3.8.13, ключи SWITCH 3.8.14, 3.8.15.

Связи в БФТФ3 3.8 определяются аналогично блоку БФТФ1 2.6.

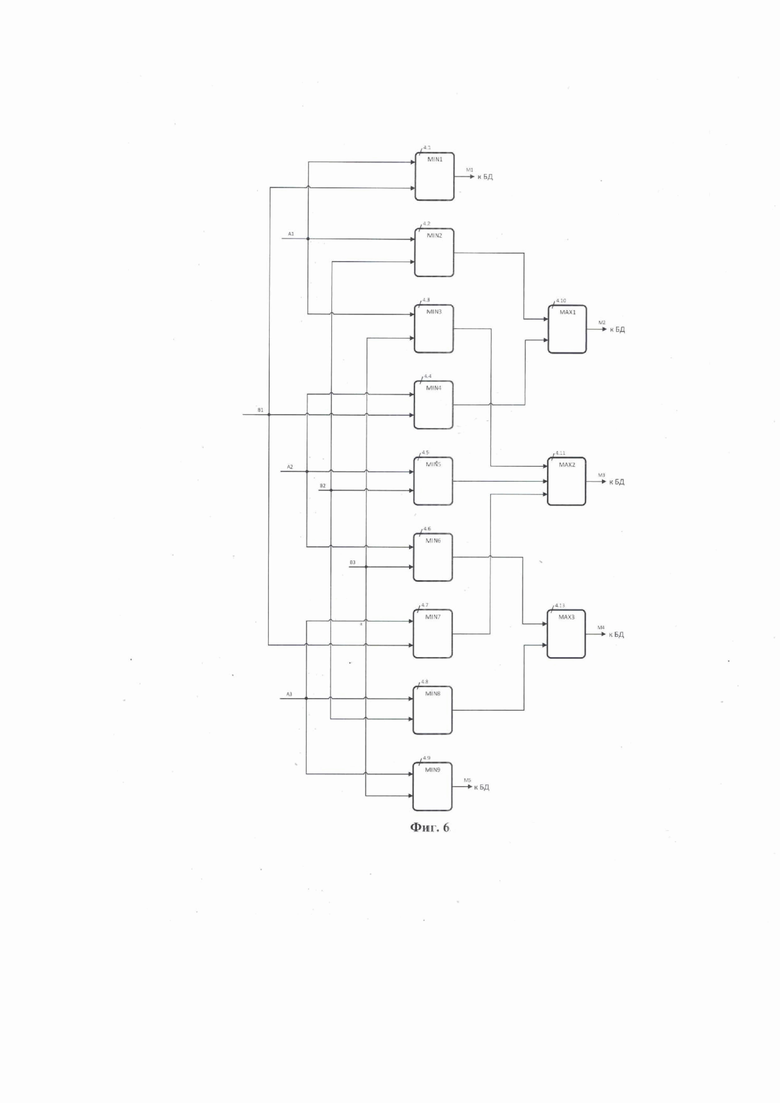

Блок импликации БИ 4 (фиг. 6) содержит блоки MIN 4.1÷4.9 и блоки МАХ 4.10÷4.12.

Связи в БИ 4 определяются следующим образом. Входной сигнал «А1» соединен с первым входом блока MIN1 4.1, с первым входом блока MIN2 4.2, с первым входом блока MIN3 4.3. Входной сигнал «А2» соединен с первым входом блока MIN4 4.4, с первым входом блока MIN5 4.5, с первым входом блока MIN6 4.6. Входной сигнал «A3» соединен с первым входом блока MIN7 4.7, с первым входом блока MIN8 4.8, с первым входом блока MIN9 4.9. Входной сигнал «В1» соединен со вторым входом блока MIN1 4.1, со вторым входом блока MIN4 4.4, со вторым входом блока MIN7 4.7. Входной сигнал «В2» соединен со вторым входом блока MIN2 4.2, со вторым входом блока MIN5 4.5, со вторым входом блока MIN8 4.8. Входной сигнал «В3» соединен со вторым входом блока MIN3 4.3, со вторым входом блока MIN6 4.6, со вторым входом блока MIN9 4.9. Выходной сигнал из блока MIN2 4.2 соединен с первым входом блока МАХ1 4.10. Выходной сигнал из блока MIN3 4.3 соединен с первым входом блока МАХ2 4.11. Выходной сигнал из блока MIN4 4.4 соединен со вторым входом блока МАХ1 4.10. Выходной сигнал из блока MIN5 4.5 соединен со вторым входом блока МАХ2 4.11. Выходной сигнал из блока MIN6 4.6 соединен с

первым входом блока МАХ3 4.12. Выходной сигнал из блока MIN7 4.7 соединен с третьим входом блока МАХ2 4.11. Выходной сигнал из блока MIN8 4.8 соединен со вторым входом блока МАХ3 4.12. Сигналы «М1», «М2», «М3», «М4», «М5» выходящие из блоков MIN1 4.1, МАХ1 4.10, МАХ2 4.11, МАХ3 4.12, MIN9 4.9 являются выходящими из блока БИ 4 и соединены со входами БД 5.

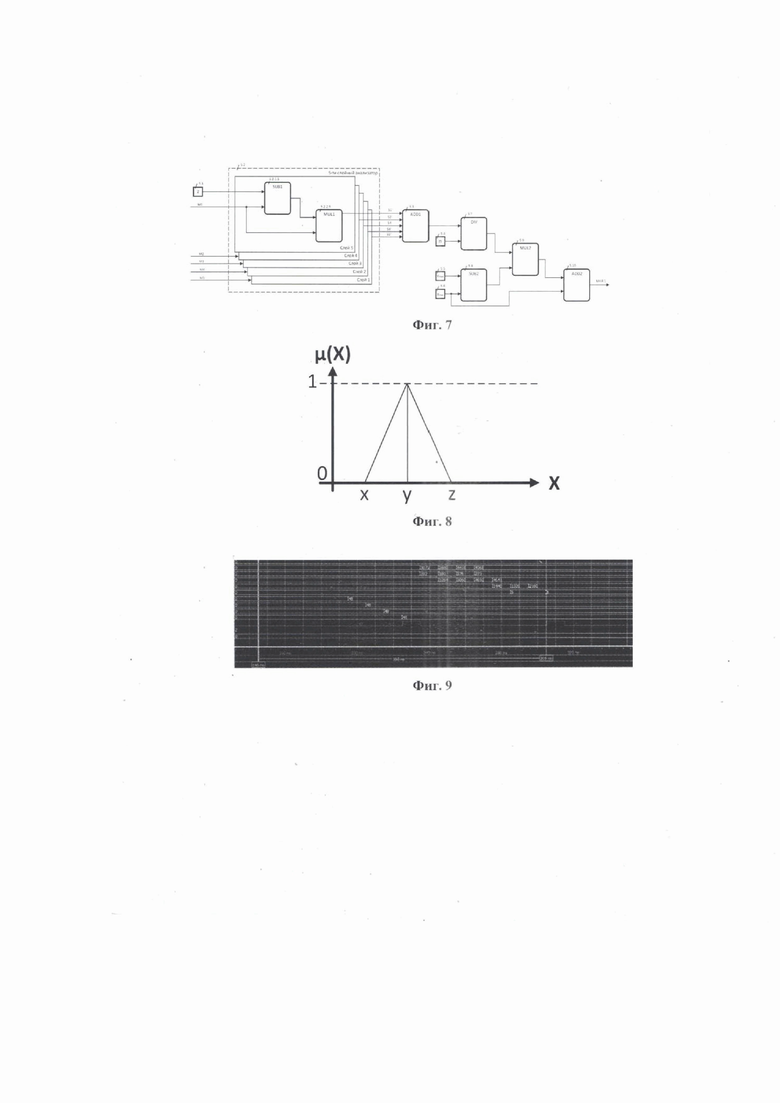

Блок быстродействующего дефаззификатора БД 5 (фиг. 7) содержит константу «2» 5.1, 5-ти слойный анализатор 5.2, состоящий из пяти вычитателей SUB1 5.2.1.1÷5.2.1.5, пяти блоков умножения MUL1 5.2.2.1÷5.2.2.5, сумматор ADD1 5.3, блок переменной «n» 5.4, блок переменной «Ymax» 5.5, блок переменной «Ymin» 5.6, делитель DIV 5.7, вычитатель SUB2 5.8, умножитель MUL2 5.9, сумматор ADD2 5.10.

Связи в БД 5 определяются следующим образом. Выходной сигнал константы «2» 5.1 соединен со входами вычитателей SUB1 5.2.1÷5.2.5. Входные сигналы «М1», «М2», «М3», «М4», «М5» соединены с входами вычитателей SUB1 5.2.1÷5.2.5 и со вторыми входами умножителей MUL1 5.3.1÷5.3.5. Выходной сигнал сумматора вычитателей SUB1 5.2.1÷5.2.5 соединен с первыми входоми умножителей MUL1 5.3.1÷5.3.5. Выходные сигналы «М1`», «M2`», «М3`», «M4`», «М5`» умножителей MUL1 5.3.1÷5.3.5 соединены с входами сумматора ADD1 5.4. Выходной сигнал сумматора ADD1 5.4 соединен с первым входом делителя DIV 5.8. Выходной сигнал блока переменной «n» 5.4 соединен со вторым входом делителя DIV 5.8. Выходной сигнал делителя DIV 5.8 соединен с первым входом умножителя MUL 5.10. Выходной сигнал константы «Ymax» 5.5 соединен с первым входом вычитателя SUB2 5.9. Выходной сигнал константы «Ymin» 5.6 соединен со вторым входом вычитателя SUB2 5.9 и первым входом сумматора ADD2 5.11. Выходной сигнал вычитателя SUB2 5.9 соединен со вторым входом умножителя MUL2 5.10. Выходной сигнал умножителя MUL 5.10 соединен со вторым входом сумматора ADD2 5.11. Из сумматора ADD2 5.8 выходит сигнал «MAR1». Выходной сигнал «MAR1» блока БД 5 является выходным сигналом быстродействующего устройства нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности. (Модификация 1).

Принцип работы быстродействующего устройства нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности (Модификация 1) состоит из четырех шагов. Сигналы двух переменных «А» и «В» генерируются в блоке 1 БГУС. Далее переменная «А» поступает в блок 2 БФВП1, а переменная «В» передается в блок 3 БФВП2. В блоке 2 БФВП1 генерируются первые три треугольные функции «А1», «В2», «A3», а в блоке 3 БФВП2 генерируются вторые три треугольные функции «В1», «В2», «В3». Каждая из треугольных функций принадлежности имеет вид аналогичный фиг. 8. Треугольные функции «А1», «В2», «A3», «В1», «В2», «В3» передаются в блок 4 БИ, где подвергаются импликации. В результате, на выходе из блока 4 БИ передаются 5 переменных «М1», «М2», «М3», «М4», «М5» в блок 5 БД. В блоке 5 БД происходит процесс дефаззификации, в ходе которого, получается результирующая переменная «MAR1». Выход результирующей переменной «MAR1» в быстродействующем устройстве нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности. Модификация 1 осуществляется за 4 шага:

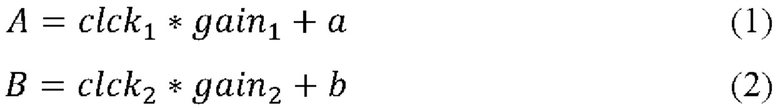

Шаг 1. Генерация переменных счетчиками:

где clck1 - сигнал с блока 1.2, gain1 - сигнал с блока 1.5, clck2 - сигнал с блока 1.4, gain2 - сигнал с блока 1.6, а - сигнал с блока 1.1, b - сигнал с блока 1.3 (сигналы «а», «b» - сигналы с реальных датчиков, полученных от систем управления) (фиг. 2).

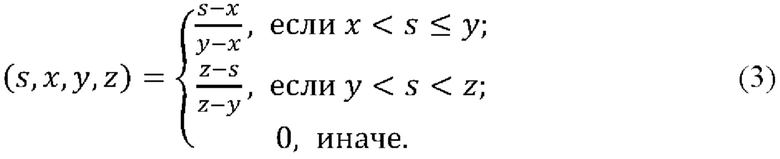

Шаг 2. Формирование треугольной функции принадлежности по формуле:

где s - входящий сигнал А или В поступающий из блока 1 (фиг. 1, фиг. 3, фиг. 4), х, у, z - сигналы значений, хранящиеся в блоках 2.1÷2.5 и 3.1÷3.5. Переменные х, у, z подбираются в зависимости от требуемого вида треугольной функции принадлежности, изображенной на фиг. 8. В результате этой операции на выходе блока БФВП1 формируются три выходных сигнала «А1», «А2» и «A3», а на выходе блока БФВП2 «В1», «В2», и «В3». Пример их расчета представлен ниже (шаг 2).

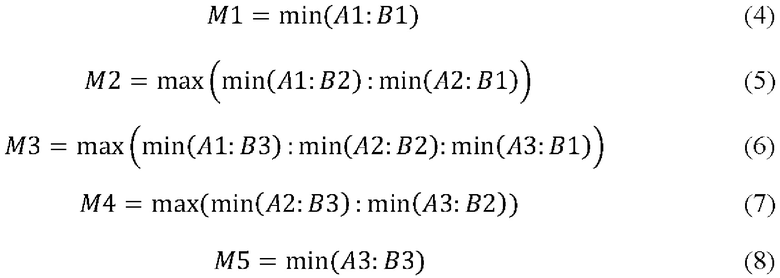

Шаг 3. Сигналы «А1», «А2», «A3», «В1», «В2», «В3» поступают с выходов блоков БФВП1, БФВП2 на входы блока БИ. Процесс импликации входящих переменных вычисляется по установленным нечетким правилам:

Выходными сигналами блока являются M1, М2, М3, М4, М5, причем переменная M1 вычисляется в блоке 4.1, М2 вычисляется в блоке 4.10, МЗ вычисляется в блоке 4.11, М4 вычисляется в блоке 4.12, М5 вычисляется в блоке 4.9.

Шаг 4. Процесс дефаззификации. Определение выходного значения после дефаззификации на основе метода отношения площадей функций принадлежности согласно формуле (9):

где Mi - значение сигнала М из блока 4, n - число нечетких функций принадлежности, Ymax - сигнал с блока 5.4, Ymin - сигнал с блока 5.5.

Для нахождения разницы Ymax и Ymin на входы блока вычитания SUB2 5.8 подаются входные сигналы Ymax и Ymin. Для расчета уравнения 12 на вход вычитателя SUB2 5.8 подаются десятиразрядные значения Ymin и Ymax. На вход умножителя MULT2 5.9 подается значение выхода вычитателя SUB2 5.10, определяющее величину области определения выходной функции принадлежности, и на второй вход умножителя MULT2 5.9 подается D, полученное на выходе делителя DIV 5.7. Выход умножителя MULT2 5.9 соединен с входом сумматора ADD2 5.10. На второй вход сумматора ADD2 5.10 подается значение Ymin. На выходе сумматора ADD2 5.10 рассчитывается выходное десятиразрядное значения после дефаззификации на основе метода отношения площадей функций принадлежности MAR1.

Пример численного моделирования работы Быстродействующее устройство нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности (Модификация 1).

Шаг 1. Рассчитывается управляющий сигнал с помощью формул (1) и (2). Пусть clck1, clck2=8, gain1=2, gain2=0.03, а=20, b=0.4. Тогда:

А=8*2+20=36;

B=8* 0.03+0.4=0.64

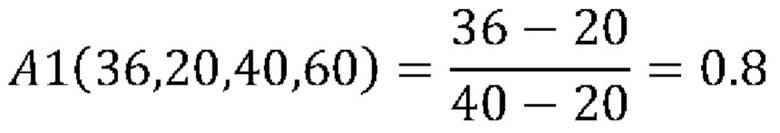

Шаг 2. Далее по формуле (3) считаются участки треугольных функции. С учетом, что а1=20, а2=40, а3=60, а4=80, а5=100, b1=0.4, b2=0.5, b3=0.6, b4=0.7, b5=0.8, А=36, В=0.64, тогда для обработки функций принадлежности производится вычисление:

Случаи μA2, μA3, μB1, μB2, μB3 считаем аналогично.

A2(36,40,60,80)=0

A3(36,60,80,100)=0

B1(0.64,0.4,0.5,0.6)=0

Шаг 3. Процесс импликации входящих переменных по установленным нечетким правилам по формулам (4), (5), (6), (7), (8):

M1=min(0.8:0)=0

М2=max(min(0.8:0.6):min(0: 0))=max(0.6:0)=0.6

М3=max(min(0.8:0.4):min(0:0.6):min(0:0))=max(0.4:0:0)=0.4

M4=max(min(0:0.4):min(0:0.6))=max(0:0)=0

M5=min(0:0.4)=0

Шаг 4. Определение выходного значения после дефаззификации на основе метода отношения площадей функций принадлежности по формуле (9). Пусть n=5, Ymax=250, Ymin=210.

Проведено моделирование в программе ISE Designer, написанной на языке программирования VHDL, показывающее быстродействие устройства дефаззификации на основе метода отношения площадей функций принадлежности составляет порядка 160 нс. (фиг. 9).

Таким образом быстродействующее устройство нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности (Модификация 1) позволяет определять единственное значение после дефаззификации и обеспечивает повышенное быстродействие за счет исключения операции нахождения ширины верхнего основания усеченных входных функций принадлежности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующее устройство нечетко-логического вывода на основе дефазификатора отношения площадей (Модификация 2) | 2022 |

|

RU2803406C1 |

| Быстродействующее устройство нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности c машинным обучением | 2024 |

|

RU2832427C1 |

| Быстродействующий дефаззификатор с использованием треугольных функций принадлежности | 2021 |

|

RU2759251C1 |

| Быстродействующий дефаззификатор с использованием треугольных функций принадлежности | 2020 |

|

RU2760632C1 |

| Устройство дефаззификации на основе метода отношения площадей | 2018 |

|

RU2701841C1 |

| ОПТОЭЛЕКТРОННЫЙ НЕЧЕТКИЙ ПРОЦЕССОР | 2010 |

|

RU2445672C1 |

| ОПТОЭЛЕКТРОННЫЙ НЕЧЕТКИЙ ПРОЦЕССОР | 2011 |

|

RU2446433C1 |

| ОПТОЭЛЕКТРОННЫЙ НЕЧЕТКИЙ ПРОЦЕССОР | 2011 |

|

RU2446436C1 |

| СПОСОБ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ И СЛЕДЯЩАЯ СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2296355C2 |

| Способ и устройство для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ | 2018 |

|

RU2709125C2 |

Изобретение относится к области вычислительных устройств и может быть использовано в устройствах обработки информации, построенных на основе нечеткой логики. Техническим результатом является повышение быстродействия устройства и генерация и преобразование входных данных в единственное четкое значение на выходе нечетко-логической системы. Устройство содержит блок генератора формирования управляющего сигнала БГУС, блок фаззификации первой входящей переменной БФВП1, блок фаззификации второй входящей переменной БФВП2, блок импликации БИ и быстродействующий дефаззификатор БД. 9 ил.

Быстродействующее устройство нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности, содержащее блок дефаззификации, отличающееся тем, что содержит блок генератора управляющего сигнала, выходы которого соединены со входами блока фаззификации первой входящей переменной и блока фаззификации второй входящей переменной, три выхода которых соединены с шестью входами блока импликации, пять выходов которого соединены с пятью входами блока дефаззификации, содержащего блок константы «2», 5-ти слойный анализатор, состоящий из пяти вычитателей SUB1 и пяти умножителей MUL1, сумматор ADD1, блок переменной «n», блок переменной «Ymax», блок переменной «Ymin», делитель DIV, вычитатель SUB2, умножитель MUL2, сумматор ADD2, при этом выход блока константы «2» соединен со входами вычитателей SUB1, выходы импликатора соединены с другими входами вычитателей SUB1 и со вторыми входами умножителей MUL1, выходы вычитателей SUB1 соединены с первыми входами умножителей MUL1, выходы умножителей MUL1 соединены с входами сумматора ADD1, выход сумматора ADD1 соединен с первым входом делителя DIV, выход блока переменной «n» соединен со вторым входом делителя DIV, выход которого соединен с первым входом умножителя MUL2, выход блока переменной «Ymax» соединен с первым входом вычитателя SUB2, выход блока переменной «Ymin» соединен со вторым входом вычитателя SUB2 и первым входом сумматора ADD2, выход вычитателя SUB2 соединен со вторым входом умножителя MUL2, выход которого соединен со вторым входом сумматора ADD2, выход которого является выходом блока дефаззификации и является выходом устройства.

| Устройство дефаззификации на основе метода отношения площадей | 2018 |

|

RU2701841C1 |

| ОПТОЭЛЕКТРОННЫЙ ДЕФАЗЗИФИКАТОР | 2009 |

|

RU2408052C1 |

| Быстродействующий дефаззификатор с использованием треугольных функций принадлежности | 2020 |

|

RU2760632C1 |

| Быстродействующий дефаззификатор с использованием треугольных функций принадлежности | 2021 |

|

RU2759251C1 |

| US 5751908 A, 12.05.1998 | |||

| US 5657427 A, 12.08.1997 | |||

| US 5852708 A, 22.12.1998. | |||

Авторы

Даты

2023-04-11—Публикация

2022-06-29—Подача