Устройство дефаззификации на основе метода отношения площадей

Изобретение относится к области вычислительных устройств и программных алгоритмов и может быть использовано в системах и устройствах обработки информации, построенной на основе нечеткой логики.

Техническая задачей изобретения является повышение вычислительной производительности процесса дефаззификации до 590 нс и обеспечение аддитивности нечеткой системы.

Техническая задача решается за счет внедрения в устройство 5-ти слойного анализатора и дополнительных логических элементов, которые реализуют новую модель дефаззификации на основе метода отношения площадей.

Техническим результатом устройства дефаззификации на основе метода отношения площадей является преобразование входных данные в единственное четкое значение на выходе системы. В структуре устройства использован 5-ти слойный анализатор, позволяющий проводить параллельные расчет по входной информации о степенях принадлежности входных переменных, используемых в предпосылках нечеткого вывода.

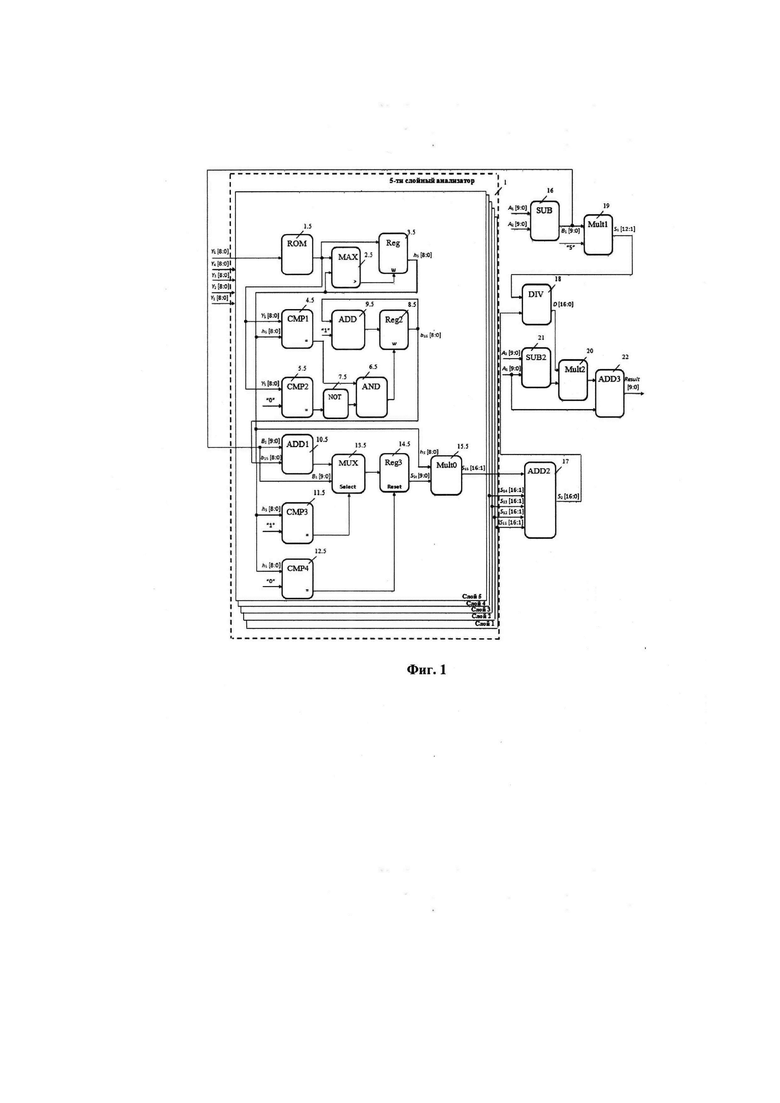

В устройство дефаззификации на основе метода отношения площадей введены блоки: 5-ти слойный анализатор, который содержит: пять блоков памяти ROM, пять блоков максимума MAX, пять блоков хранения Reg, пять блоков хранения Reg2, пять блоков записи Reg3, пять компараторов CMP1, пять компараторов CMP2, пять компараторов CMP3, пять компараторов CMP4, пять блоков логического умножения AND, пять блоков логического отрицания NOT, пять сумматоров ADD, пять сумматоров ADD1, пять мультиплексоров MUX и пять блоков умножения Mult0; вычитатель SUB, вычитатель SUB2, сумматор ADD2, сумматор ADD3, делитель DIV, умножитель Mult1 и умножитель Mult2.

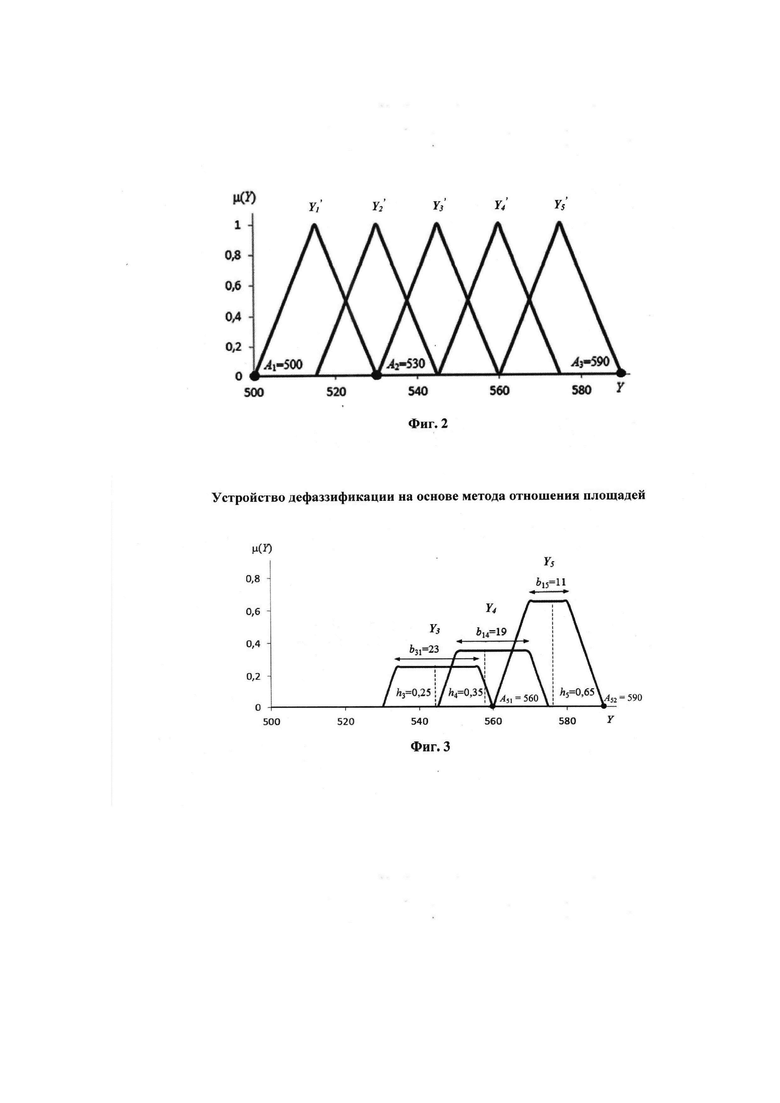

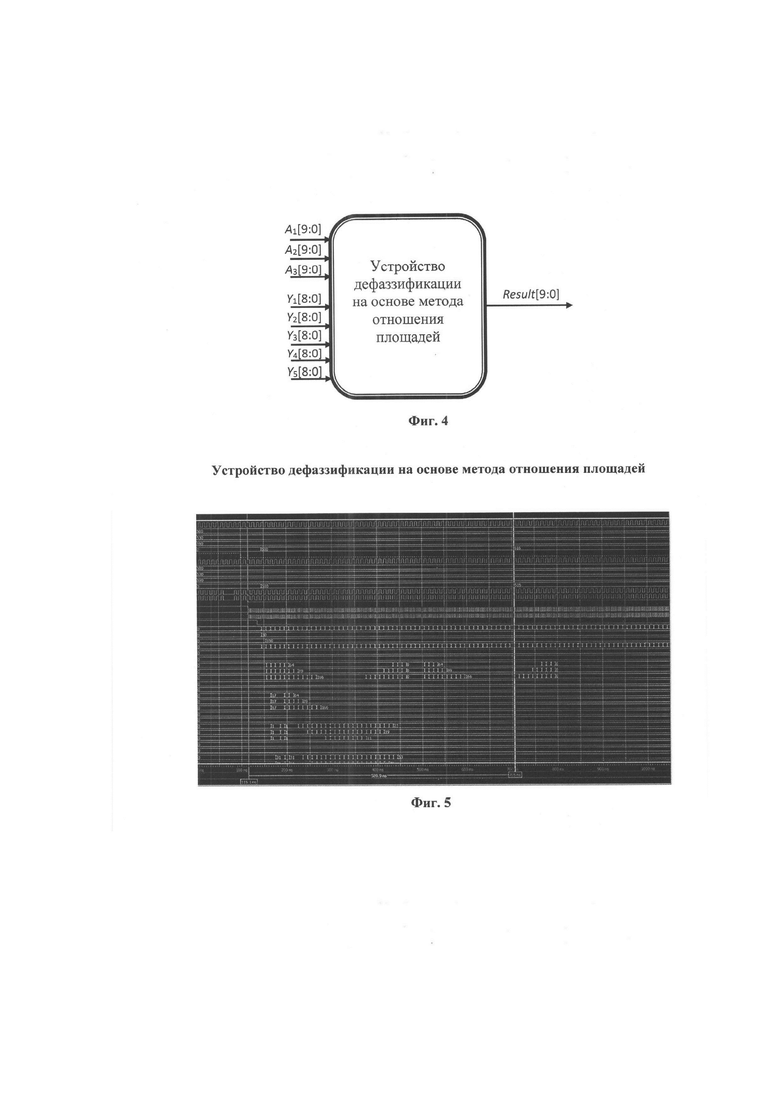

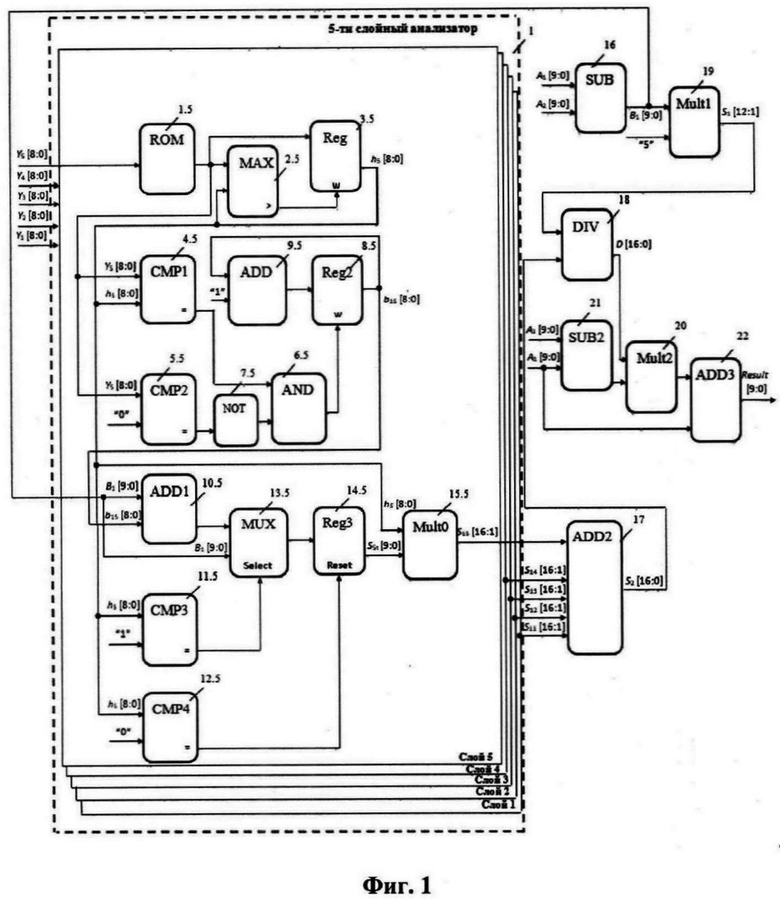

Сущность изобретения поясняется чертежами: фиг. 1 - Устройство дефаззификации на основе метода отношения площадей; фиг. 2 - Функции принадлежности выходной переменной; фиг.3 - Функции принадлежности выходной переменной после агрегации; фиг. 4 – Схема входных и выходных параметров устройства дефаззификации на основе метода отношения площадей; фиг. 5 – Результаты моделирования в программе ISE Design v.14.7, написанной на языке программирования VHDL.

Устройство дефаззификации на основе метода отношения площадей содержит 5-ти слойный анализатор 1, состоящий из пяти блоков памяти ROM 1.1÷1.5, пяти блоков максимума MAX 2.1÷2.5, пяти блоков хранения Reg 3.1÷3.5, пяти компараторов CMP1 4.1÷4.5, пяти компараторов CMP2 5.1÷5.5, пяти блоков логического умножения AND 6.1÷6.5, пяти блоков логического отрицания NOT 7.1÷7.5, пяти блоков хранения Reg2 8.1÷8.5, пяти сумматоров ADD 9.1÷9.5, пяти сумматоров ADD1 10.1÷10.5, пяти компараторов CMP3 11.1÷11.5, пяти компараторов CMP4 12.1÷12.5, пяти мультиплексоров MUX 13.1÷13.5, пяти блоков записи Reg3 14.1÷14.5 и пяти блоков умножения Mult0 15.1÷15.5, вычитатель SUB 16, сумматор ADD2 17, делитель DIV18 , умножитель Mult1 19, умножитель Mult2 20, вычитатель SUB2 21 и сумматор ADD3 22.

Связи в устройстве дефаззификации на основе метода отношения площадей между блоками определяются следующим образом. Входы блока памяти ROM 1.1÷1.5 5-слойного анализатора 1 соединены с входными сигналами Y1[8:0], Y2[8:0], Y3[8:0], Y4[8:0], Y5[8:0]. Выход блоков памяти ROM 1.1÷1.5 соединены с входами блоков максимума MAX 2.1÷2.5 и входами блоков хранения Reg 3.1÷3.5. Вторые входы блоков MAX 2.1÷2.5 соединены с выходами блоков хранения Reg 3.1÷3.5. Выходы блоков максимума MAX 2.1÷2.5 «>» соединены с входами записи «w» блоков хранения Reg 3.1÷3.5. Выходы блоков памяти ROM 1.1÷1.5 соединены с входами компараторов CMP1 4.1÷4.5 и CMP2 5.1÷5.5. При этом вторые входы компараторов CMP1 4.1÷4.5 соединены с выходами блоков хранения Reg 3.1÷3.5, а вторые входы компараторов CMP2 5.1÷5.5 соединены с логическим “0”. Выходы «=» компараторов CMP1 4.1÷4.5 соединены с входами блоков логического умножения AND 6.1÷6.5, а выходы «=» компараторов CMP2 5.1÷5.5 соединены с входами блоков логического отрицания NOT 7.1÷7.5, выходы которого соединены со вторым входом блоков логического умножения AND 6.1÷6.5. Выходы блоков логического умножения AND 6.1÷6.5 соединены со входами записи «w» блоков хранения Reg2 8.1÷8.5. Вторые входы блоков хранения Reg2 8.1÷8.5 соединены с выходами сумматоров ADD 9.1÷9.5. Первый вход сумматоров ADD 9.1÷9.5 соединен с выходами блоков хранения Reg2 8.1÷8.5, а второй соединен с логической “1”. Выходы блоков хранения Reg2 8.1÷8.5 также соединены с входами сумматоров ADD1 10.1÷10.5. Вторые входы сумматоров ADD1 10.1÷10.5 соединены с выходом вычитателя SUB 16, входы которого соединены с входными сигналами A1[9:0] и A2[9:0]. Выходы блоков хранения Reg 3.1÷3.5 также соединены с входами компараторов CMP3 11.1÷11.5 и CMP4 12.1÷12.5. Вторые входы компараторов CMP3 11.1÷1.5 соединены с логической “1”, а вторые входы компараторов CMP4 12.1÷12.5 соединены с логическим “0”. Выходы компараторов «=» CMP3 11.1÷11.5 соединены с входами «Select» мультиплексоров MUX 13.1÷13.5. При этом входы мультиплексоров MUX 13.1÷13.5 подключены к выходу вычитателя SUB 16 и сумматоров ADD1 10.1÷10.5. Выходы мультиплексоров MUX 13.1÷13.5 соединены с входами блоков записи Reg3 14.1÷14.5. Вторые входы «Reset» блоков записи Reg3 14.1÷14.5 соединены с выходами компараторов CMP4 12.1÷12.5. Выходы блоков записи Reg3 14.1÷14.5 соединены с входами блоков умножения Mult0 15.1÷15.5. Вторые входы блоков умножения Mult0 15.1÷15.5 соединены с выходами блоков хранения Reg 3.1÷3.5. Выходы блоков умножения Mult0 15.1÷15.5 соединены с входом сумматора ADD2 17. Выход сумматора ADD2 17 подключен к входу делителя DIV 18. Второй вход делителя DIV 18 соединен с выходом умножителя Mult1 19, один вход которого соединен с выходом вычитателя SUB 16, а второй соединен с константой “5”. Выход делителя DIV 18 соединен с входом умножителя Mult2 20. Второй вход умножителя Mult2 20 соединен с выходом вычитателя SUB2 21. Входы вычитателя SUB2 21 соединены с входными сигналами A1[9:0] и A3[9:0]. Выход умножителя Mult2 20 соединен с входом сумматора ADD3 22. Второй вход сумматора ADD3 22 соединен с входным сигналом A1[9:0]. Выход сумматора ADD3 22 является выходным сигналом устройства дефаззификации на основе метода отношения площадей.

Принцип работы устройства дефаззификации на основе метода отношения площадей состоит из 6 шагов. Входными данными (фиг. 4) в устройстве дефаззификации на основе метода отношения площадей является пять множеств Y1[8:0], Y2[8:0], Y3[8:0], Y4[8:0], Y5[8:0], c данными о степенях принадлежности α функций принадлежности выходной переменной после агрегации (фиг.3); A1[9:0] - точка начала нижнего основания первой выходной функции принадлежности и начальное значение области определения функций принадлежности выходной переменной; A2[9:0] – точка конца нижнего основания первой выходной функции принадлежности; A3[9:0] – конечное значение области определения функции принадлежности выходной переменной.

Y1[8:0], Y2[8:0], Y3[8:0], Y4[8:0], Y5[8:0] поступают в 5-ти слойный анализатор 1 (фиг. 1) для определения площади каждого усеченного терма следующим образом: девятиразрядное значение Y1[8:0] на вход блока памяти ROM 1.1 первого слоя; девятиразрядное значение Y2[8:0] на вход блока памяти ROM 1.2 второго слоя; девятиразрядное значение Y3[8:0] на вход блока памяти ROM 1.3 слоя три; девятиразрядное значение Y4[8:0] на вход памяти блока памяти ROM 1.4 четвертого слоя; девятиразрядное значение Y5[8:0] на вход блока памяти ROM 1.5 пятого слоя. Выполнение операций описано для пятого слоя. Операции, выполняемые в первом, втором, третьем и четвертом слоях, имеют ту же последовательность выполняемых действий.

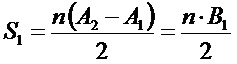

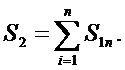

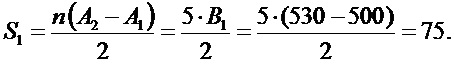

Шаг 1. Расчёт общей площади функций принадлежности выходной переменной S1 выполняется по формуле (1):

где n – число термов функции принадлежности выходной переменной (n = 5), B1 = A2 - A1 – длина основания первой функции принадлежности выходной переменной.

Для выполнения данной операции, на вход вычитателя SUB 16 подаются два десятиразрядных значения входных сигналов A1[9:0] и A2[9:0]. В результате на выходе вычитателя SUB 16 вычисляется десятиразрядное значение B1[9:0]. Полученное значение B1[9:0] с выхода вычитателя SUB 16 подается на первый вход умножителя Mult1 19. На второй вход умножителя Mult1 19 подается переменная n равная константе “5”. Операция деления на два на выходе умножителя Mult1 19 организована следующим образом. В частое записываются только самые старшие биты S1[12:1], а не все число S1[12:0], полученное после операции умножения в умножителе Mult1 19. В результате на выходе умножителя Mult1 19 рассчитывается общая площадь пяти функций принадлежности выходной переменной S1[12:1].

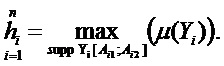

Шаг 2. Расчет высот треугольных функций принадлежности выходной переменной после агрегации выполняется по формуле (2):

где supp (супстремум) –множество данных в диапазоне значений, где степень принадлежности α отлично от нуля; Ai1 – начальное значение диапазона supp; Ai2 – конечное значение диапазона supp.

Выходная переменная в нечеткой системе задана 5-ю треугольными функциями принадлежности Y’i (фиг. 2). Функции принадлежности после агрегации Yi (фиг. 3) содержат данные о степенях принадлежности α в диапазоне [0;1], где i = 1…5.

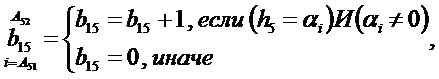

Тогда в пятом слое формула 2 имеет вид:

где A51 - начальное значение диапазона supp для пятой функции принадлежности, A52 - конечное значение диапазона supp для пятой функции принадлежности.

Для этого в устройстве дефаззификации на основе метода отношения площадей данные с выхода блока памяти ROM 1.5 передаются поэлементно в блок максимума MAX 2.5. В блоке MAX 2.5 выполняется сравнение полученного девятиразрядного значения из блока памяти ROM 1.5 с девятиразрядным значением из блока хранения Reg 3.5. Первое значение в блоке хранения Reg 3.5 равно “0”. В случае, если текущее значение из блока памяти ROM 1.5 больше значения из блока хранения Reg 3.5, то на выходе «>» блока максимума MAX 2.5 формируется значение логической “1”. Оно передается на вход «w» блока хранения Reg 3.5, и открывает его вход для записи значения с выхода блока памяти ROM 1.5 в блок хранения Reg 3.5. Хранимое значение в блоке хранения Reg 3.5 понимается как значение высоты h5[8:0]. После перебора всех элементов из блока памяти ROM 1.5 в блоке хранения Reg 3.5 храниться девятиразрядное значение высоты h5[8:0] пятой функции принадлежности.

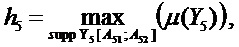

Шаг 3. Определение длины верхнего основания усеченных треугольных функций принадлежности выходной переменной после агрегации выполняется по формуле (3):

где n - номер функции принадлежности выходной переменной, An2 – конечное значение области определения n-ой функции принадлежности выходной переменной, An1 – начальное значение области определения n-ой функции принадлежности выходной переменной, αi – степень принадлежности функции принадлежности выходной переменной в точке i, при этом i находится в диапазоне [An1, An2].

Для пятого слоя формула 3 имеет вид:

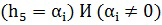

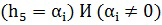

Для проверки условия  в устройстве дефаззификации на основе метода отношения площадей значение степени принадлежности αi из множества степеней принадлежности пятого терма Y5 из блока памяти ROM 1.5 передаются в компараторы CMP1 4.5 и CMP2 5.5. В компараторе CMP1 4.5 проверяется условие

в устройстве дефаззификации на основе метода отношения площадей значение степени принадлежности αi из множества степеней принадлежности пятого терма Y5 из блока памяти ROM 1.5 передаются в компараторы CMP1 4.5 и CMP2 5.5. В компараторе CMP1 4.5 проверяется условие  равенства между значением высоты h5[8:0], хранящееся в блоке хранения Reg 3.5, и текущим элементом αi на выходе блока памяти ROM 1.5. В компараторе CMP2 5.5 и в блоке отрицания NOT 7.5 выполняется проверка неравенства

равенства между значением высоты h5[8:0], хранящееся в блоке хранения Reg 3.5, и текущим элементом αi на выходе блока памяти ROM 1.5. В компараторе CMP2 5.5 и в блоке отрицания NOT 7.5 выполняется проверка неравенства  выходного значения αi блока памяти ROM 1.5 нулю. В случае истинности условия

выходного значения αi блока памяти ROM 1.5 нулю. В случае истинности условия  на выходе «=» компаратора CMP1 4.5 формируется значение логической “1”, которое передается на первый вход блока логического умножения AND 6.5. В случае выполнения условия

на выходе «=» компаратора CMP1 4.5 формируется значение логической “1”, которое передается на первый вход блока логического умножения AND 6.5. В случае выполнения условия  на выходе «=» компаратора CMP2 5.5 формируется значение логического “0”, которое передается в блок отрицания NOT 7.5, на выходе которого формируется значение логической “1”. Оно подается на второй вход блока логического умножения AND 6.5. В блоке логического умножения AND 6.5 выполняется проверка истинности двух условий. Когда условие в компараторе CMP1 4.5 истина и на выходе в блоке отрицания NOT 7.5 истина, то на выходе блока логического умножения AND 6.5 формируется значение логической “1”, передаваемое на вход «w» блока хранения Reg2 8.5. При этом, в сумматор ADD 9.5 подается на первый вход девятиразрядное значение b15[8:0] из блока хранения Reg2 8.5 и складывается в сумматоре ADD 9.5 с единицей. После увеличения значения b15[8:0] на единицу, оно из сумматора ADD 9.5 передается для записи в блок хранения Reg2 8.5.

на выходе «=» компаратора CMP2 5.5 формируется значение логического “0”, которое передается в блок отрицания NOT 7.5, на выходе которого формируется значение логической “1”. Оно подается на второй вход блока логического умножения AND 6.5. В блоке логического умножения AND 6.5 выполняется проверка истинности двух условий. Когда условие в компараторе CMP1 4.5 истина и на выходе в блоке отрицания NOT 7.5 истина, то на выходе блока логического умножения AND 6.5 формируется значение логической “1”, передаваемое на вход «w» блока хранения Reg2 8.5. При этом, в сумматор ADD 9.5 подается на первый вход девятиразрядное значение b15[8:0] из блока хранения Reg2 8.5 и складывается в сумматоре ADD 9.5 с единицей. После увеличения значения b15[8:0] на единицу, оно из сумматора ADD 9.5 передается для записи в блок хранения Reg2 8.5.

В случае неисполнения одного из условий  , из формулы 3, увеличения значения b15[8:0] на единицу на i-ой итерации в блок хранения Reg2 8.5 не производится. В начале выполнения третьего шага в блоке хранения Reg2 8.5 записано значение ноль.

, из формулы 3, увеличения значения b15[8:0] на единицу на i-ой итерации в блок хранения Reg2 8.5 не производится. В начале выполнения третьего шага в блоке хранения Reg2 8.5 записано значение ноль.

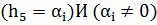

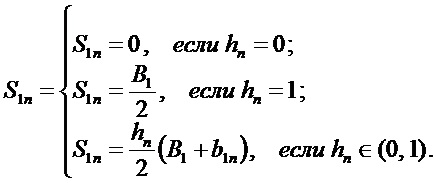

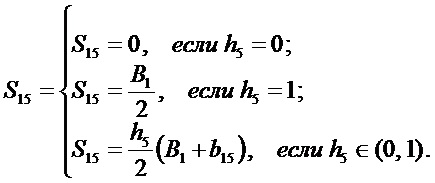

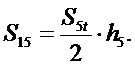

Шаг 4. Определение общей площади усеченных треугольных функций принадлежности выходной переменной проводиться по формулам (4) и (5):

где S1n – площадь n-ой функции принадлежности выходной переменной, S2 – общая площади усеченных функций принадлежности выходной переменной.

Для пятого слоя формула 4 имеет вид:

Формула (4a) в устройстве дефаззификации на основе метода отношения площадей сводится к формуле (4b):

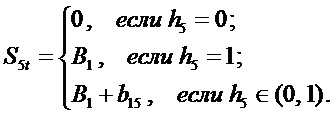

При этом значение S5t зависит от выполнения одного из условий формулы 4а и рассчитывается по формуле 4c:

Для получения площади пятой функции принадлежности выходной переменной S15[16:1] необходимо расcчитать по формуле (4c) значение S5t[9:0] и проверить выполнение трех условий формул (4a) и (4c). Для проверки условия h5=0, значение h5[8:0] из блока хранения Reg 3.5 подается на вход компаратора CMP4 12.5 для сравнения с логическим “0”. В случае выполнения условия, на выходе «=» компаратора CMP4 12.5 формируется значение логической “1”, которое подается на вход «Reset» блока записи Reg3 14.5. В этом случае, в блоке записи Reg3 14.5 сбрасывается записанное значение в ноль и на выходе блоке записи Reg3 14.5 формируется десятиразрядное значение S5t[9:0] равное нулю. Затем нулевое значение S5t[9:0] передается на вход блока умножения Mult0 15.5.

Для проверки второго условия из формул (4a) и (4c) h5=1 значение h5[8:0] из блока хранения Reg 3.5 подается на вход компаратора CMP3 11.5 для сравнения с логической “1”. В случае истинности этого условия, на выходе «=» компаратора CMP3 11.5 формируется значение логической “1”, которое подается в мультиплексор MUX 13.5 на вход «Select». В этом случае в мультиплексор MUX 13.5 будет записано значение B1[9:0], полученное с выхода вычитателя SUB 16. С выхода мультиплексора MUX 13.5 на входе блока записи Reg3 14.5 будет передано значение B1[9:0]. В этом случае, на выходе блоке записи Reg3 14.5 формируется десятиразрядное значение S5t[9:0] равное B1[9:0]. Затем с выхода блока записи Reg3 14.5 значение S5t[9:0] передается на вход блока умножения Mult0 15.5.

В случае невыполнения первых двух условий из формул (4a) и (4c) [(h5=1) и (h5=0)] c компаратора CMP3 11.5 на вход «Select» мультиплексора MUX 13.5 передается значение логического “0”. В этом случае в мультиплексор MUX 13.5 будет записана сумма значений B1[9:0] и b15[8:0], рассчитанная на выходе сумматора ADD1 10.5. С выхода мультиплексора MUX 13.5 сумма значений B1[9:0] и b15[8:0] передается на вход блока записи Reg3 14.5. В этом случае, на выходе блока записи Reg3 14.5 формируется десятиразрядное значение S5t[9:0] равное сумме B1[9:0] и b15[8:0]. Затем с выхода блока записи Reg3 14.5 значение S5t[9:0] передается на вход блока умножения Mult0 15.5.

В блоке умножения Mult0 15.5 выполняется операция умножения значений h5[8:0] и S5t[9:0]. Операция деления на два на выходе блока умножения Mult0 15.5 организована следующим образом. В частое записываются только самые старшие биты S15 [16:1], а не все число S2[16:0] полученное после операции умножения в блоке умножения Mult0 15.5. Значение S15 [16:1] будет подано на вход сумматора ADD2 17.

После выполнения расчета площади функций принадлежности выходной переменной S11[16:1], S12[16:1], S13[16:1], S14[16:1] в оставшихся четырех слоях 5-ти слойного анализатора 1 аналогичным образом, они поступают в сумматор ADD2 17, на выходе которого формируется семнадцатиразрядное значение общей площади усеченных термов функции принадлежности выходной переменной S2[16:0], рассчитанное по формуле 5.

Шаг 5. Расчет отношения площадей S2 и S1 выполняется по формуле (6):

Для этого в устройстве дефаззификации на основе метода отношения площадей с выхода сумматора ADD2 17 полученное значение общей площади усеченных термов функции принадлежности выходной переменной S2[16:0] подается на вход делителя DIV 18, в котором производиться операция деления на значение выхода умножителя Mult1 19, в котором рассчитано значение S1[12:1]. В результате на выходе делителя DIV 18 вычисляется семнадцатиразрядная величина D[16:0].

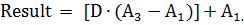

Шаг 6. Определение выходного значения после дефаззификации на основе метода отношения площадей согласно формуле (7):

Для расчета уравнения 7 на вход вычитателя SUB2 21 подаются десятиразрядные значения A1[9:0] и A3[9:0]. На вход умножителя Mult2 20 подается значение выхода вычитателя SUB2 21, определяющее величину области определения выходной функции принадлежности, и на второй вход умножителя Mult2 20 подается D[16:0], полученное на выходе делителя DIV 18. Выход умножителя Mult2 20 соединен с входом сумматора ADD3 22. На второй вход сумматора ADD3 22 подается значение A1. На выходе сумматора ADD3 22 рассчитывается выходное десятиразрядное значения после дефаззификации на основе метода отношения площадей Result [9:0].

Пример численного моделирования работы устройства дефаззификации на основе метода отношения площадей.

Шаг 1. Рассчитывается общая площадь функций принадлежности выходной переменной. Пусть А3 = 590, А2 = 530 и A1 = 500 (фиг.2), B1 = 30, количество функций принадлежности выходной переменной n = 5. Тогда по формуле (1) S1 равно:

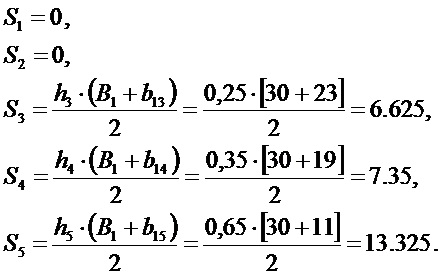

Шаг 2. Высоты треугольных усеченных функций принадлежности (фиг. 3) рассчитываются согласно формуле (2):

h1 = 0, h2 = 0, h3 = 0,25, h4 = 0.35, h5 = 0.65.

Шаг 3. Длина верхних оснований усеченных функций принадлежности выходной переменной (фиг. 3) рассчитывается согласно формуле (3):

b11 = 0, b12 = 0, b13 = 23, b14 = 19, b15 = 11.

Например, при расчете b15 условие  выполнилось 11 раз, поэтому b15 = 11.

выполнилось 11 раз, поэтому b15 = 11.

Шаг 4. Площадь усеченных функций принадлежности рассчитывается по формуле (4):

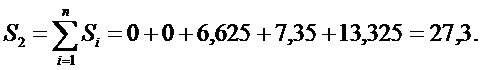

Общая суммарная площадь усеченных функций принадлежности выходной переменной определяется по формуле (5):

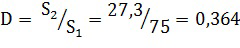

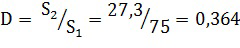

Шаг 5. Отношение общей площади усеченной функции принадлежности к общей площади выходной функции принадлежности рассчитывается согласно формуле (6):

.

.

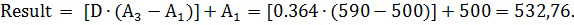

Шаг 6. Выходное значения после дефаззификации на основе метода отношения площадей рассчитывается по формуле (7):

Метод отношения площадей основан на нахождении отношения площади, получаемой после усечения функций принадлежности выходной переменной к первоначальной.

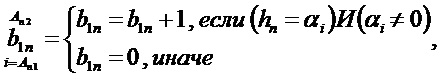

Проведено моделирование в программе ISE Designer, написанной на языке программирования VHDL, показывающее быстродействие устройства дефаззификации на основе метода отношения площадей порядка 590 нс. (фиг. 5).

Таким образом устройство дефаззификации на основании метода отношения площадей позволяет определять единственное значение после дефаззификации и обеспечивает быстродействие до 590 нс.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий дефаззификатор с использованием треугольных функций принадлежности | 2021 |

|

RU2759251C1 |

| Быстродействующий дефаззификатор с использованием треугольных функций принадлежности | 2020 |

|

RU2760632C1 |

| Быстродействующее устройство нечетко-логического вывода на основе дефаззификатора отношения площадей функций принадлежности c машинным обучением | 2024 |

|

RU2832427C1 |

| Быстродействующее устройство нечетко-логического вывода на основе дефаззификатора отношения площадей (Модификация 1) | 2022 |

|

RU2794059C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ МЕЖДУ СОСЕДНИМИ КАДРАМИ И ОЦЕНКИ ДВИЖЕНИЯ ИЗОБРАЖЕНИЙ | 1993 |

|

RU2117412C1 |

| Быстродействующее устройство нечетко-логического вывода на основе дефазификатора отношения площадей (Модификация 2) | 2022 |

|

RU2803406C1 |

| Способ и устройство для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ | 2018 |

|

RU2709125C2 |

| МНОГОКАНАЛЬНЫЙ ИМПУЛЬСНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ | 2024 |

|

RU2838912C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ОШИБОК В КАНАЛЕ | 2001 |

|

RU2192038C1 |

| ДИСКРЕТНАЯ СИСТЕМА ОЦЕНИВАНИЯ | 2007 |

|

RU2398258C2 |

Изобретение относится к области вычислительных устройств и программных алгоритмов и может быть использовано в системах и устройствах обработки информации, построенной на основе нечеткой логики. Технический результат заключается в преобразовании входных данных в единственное четкое значение на выходе системы и достигается за счет внедрения 5-слойного анализатора, позволяющего проводить параллельные расчет по входной информации о степенях принадлежности входных переменных, используемых в предпосылках нечеткого вывода. В устройство дефаззификации на основе метода отношения площадей введены блоки: 5-слойный анализатор, который содержит: пять блоков памяти ROM, пять блоков максимума MAX, пять блоков хранения Reg, пять блоков хранения Reg2, пять блоков записи Reg3, пять компараторов CMP1, пять компараторов CMP2, пять компараторов CMP3, пять компараторов CMP4, пять блоков логического умножения AND, пять блоков логического отрицания NOT, пять сумматоров ADD, пять сумматоров ADD1, пять мультиплексоров MUX и пять блоков умножения Mult0; вычитатель SUB, вычитатель SUB2, сумматор ADD2, сумматор ADD3, делитель DIV, умножитель Mult1 и умножитель Mult2. 5 ил.

Устройство дефаззификации на основе метода отношения площадей, предназначенное для расчёта выходного значения после дефаззификации на основе метода отношения площадей, содержащее 5-слойный анализатор, состоящий из пяти блоков памяти ROM, пяти блоков максимума MAX, пяти блоков хранения Reg, пяти компараторов CMP1, пяти компараторов CMP2, пяти блоков логического умножения AND, пяти блоков логического отрицания NOT, пяти блоков хранения Reg2, пяти сумматоров ADD, пяти сумматоров ADD1, пяти компараторов CMP3, пяти компараторов CMP4, пяти мультиплексоров MUX, пяти блоков записи Reg3, пяти блоков умножения Mult0; и вычитатель SUB, сумматор ADD2, делитель DIV, умножитель Mult1, умножитель Mult2, вычитатель SUB2 и сумматор ADD3, на котором формируется выходное значение после дефаззификации на основе метода отношения площадей, вход которого соединен с входным сигналом A1 и выходом умножителя Mult2, первый вход которого подключены к выходам вычитателя SUB2, вход которого соединен с входными сигналами A1 и A3, и второй вход умножителя Mult2 соединен с выходом делителя DIV, один вход которого соединен с выходом умножителя Mult1, входы которого соединены с константой “5” и выходом вычитателя SUB, входы которого соединены с входными сигналами A1 и A2, и второй вход делителя DIV соединен с выходом сумматора ADD2, входы которого соединены с выходами блоков умножения Mult0 5-слойного анализатора, при этом входы блоков Mult0 соединены с выходами блоков записи Reg3, входы «Reset» которых соединены с выходами «=» компараторов CMP4, входы которых соединены с константой “0” и выходами блоков хранения Reg, и вторые входы блока записи Reg3 соединены с выходами мультиплексоров MUX, входы «Select» которых соединены с выходами «=» компараторов CMP3, входы которых соединены с константой “1” и выходами блоков хранения Reg, и входы мультиплексоров MUX соединены с выходом вычитателя SUB и выходом сумматоров ADD1, входы которых соединены с выходом вычитателя SUB и выходами блоков хранения Reg2, входы которых соединены с выходами сумматоров ADD, входы которых соединены с константой “1”, и выходами хранения Reg2, и входы «w» блоков хранения Reg2 соединены с выходами блоков логического умножения AND, входы которых соединены с выходами блоков отрицания NOT, входы которых соединены с выходами «=» компараторов CMP2, входы которых соединены с константой “0” и выходами блоков памяти ROM, и вторые входы блоков логического умножения AND соединены с выходами «=» компараторов CMP1, входы которых соединены с выходами блоков хранения Reg и выходами блоков памяти ROM, а вторые входы блоков умножения Mult0 соединены с выходами блоков хранения Reg, входы которых соединены с выходами блоков памяти ROM, и выходами «>» блоков максимума MAX, входы которых соединены с выходом блоков хранения Reg и выходами блоков памяти ROM, входы которых являются входами 5-слойного анализатора и соединены с входными сигналами Y1, Y2, Y3, Y4, Y5.

| ОПТОЭЛЕКТРОННЫЙ ДЕФАЗЗИФИКАТОР | 2009 |

|

RU2408052C1 |

| ОПТОЭЛЕКТРОННЫЙ ДЕФАЗЗИФИКАТОР | 2010 |

|

RU2439652C1 |

| ОПТОЭЛЕКТРОННЫЙ ДЕФАЗЗИФИКАТОР | 2010 |

|

RU2439651C1 |

| ОПТОЭЛЕКТРОННЫЙ ДЕФАЗЗИФИКАТОР | 2010 |

|

RU2446432C1 |

| ОПТОЭЛЕКТРОННЫЙ ДЕФАЗЗИФИКАТОР | 2010 |

|

RU2446435C1 |

| US 5524174 A1, 04.06.1996. | |||

Авторы

Даты

2019-10-01—Публикация

2018-12-13—Подача