Изобретение относится к области высокоскоростной обработки изделий на оборудовании с ЧПУ, в частности к системам компенсации температурных деформаций за счет использования нечеткого контроллера для управления термоэлементом.

Известно энергосберегающее устройство охлаждения режущего инструмента [Патент РФ №2591931, кл. B23B 27/10, 2013 (аналог)].

Недостатком данного устройства является то, что не указана реализация принципа обработки информации на логических элементах в нечетком контроллере, что увеличивает время обработки информации от датчиков.

Известно устройство охлаждения режущего инструмента [Патент РФ №2470757, кл. B23Q 11/10, 2011 (прототип)].

Недостатком устройства является то, что при охлаждении резца используется управляемый генератор тока, причем регулирование тока возможно только в ручном режиме, что увеличивает время на его перенастройку.

Известен способ охлаждения режущего инструмента для повышения точности при обработке деталей на оборудовании с ЧПУ [Патент РФ №2486992, кл. B23B 1/00, B23Q 11/14, 2011 (аналог)].

Недостатком представленного способа является то, что в нем не указана аппаратная реализация алгоритма на логических элементах, следовательно, он реализован программно, данные обрабатываются последовательно - это уменьшает быстродействие устройства.

Известен способ охлаждения резца [Патент РФ №2586189, кл. B23Q11/14, B23B 27/10, 2014 (прототип)].

Недостатком данного способа является то, что в нем не представлена аппаратная реализация алгоритма, а это уменьшает быстродействие устройства.

Технической задачей изобретения является улучшение качества обработки изделий на оборудовании с ЧПУ, увеличение периода стойкости режущего инструмента за счет компенсации температурных деформаций и использования нечеткого контроллера для управления термоэлементом.

Поставленная задача решается тем, что в известное устройство, включающее в себя резец, термоэлемент, исполнительные механизмы, компьютер введены аналого-цифровые преобразователи, цифро-аналоговый преобразователь, резистор, полевой транзистор, блоки питания, датчик температуры, датчик напряжения, программатор, блок разности, нечеткий

контроллер, содержащий; блок ввода информации, блок определения степенней истинности, блок ввода выходной переменной, блок усечения термов выходной переменной, блок объединения усеченных термов выходной переменной, блок дефаззификации.

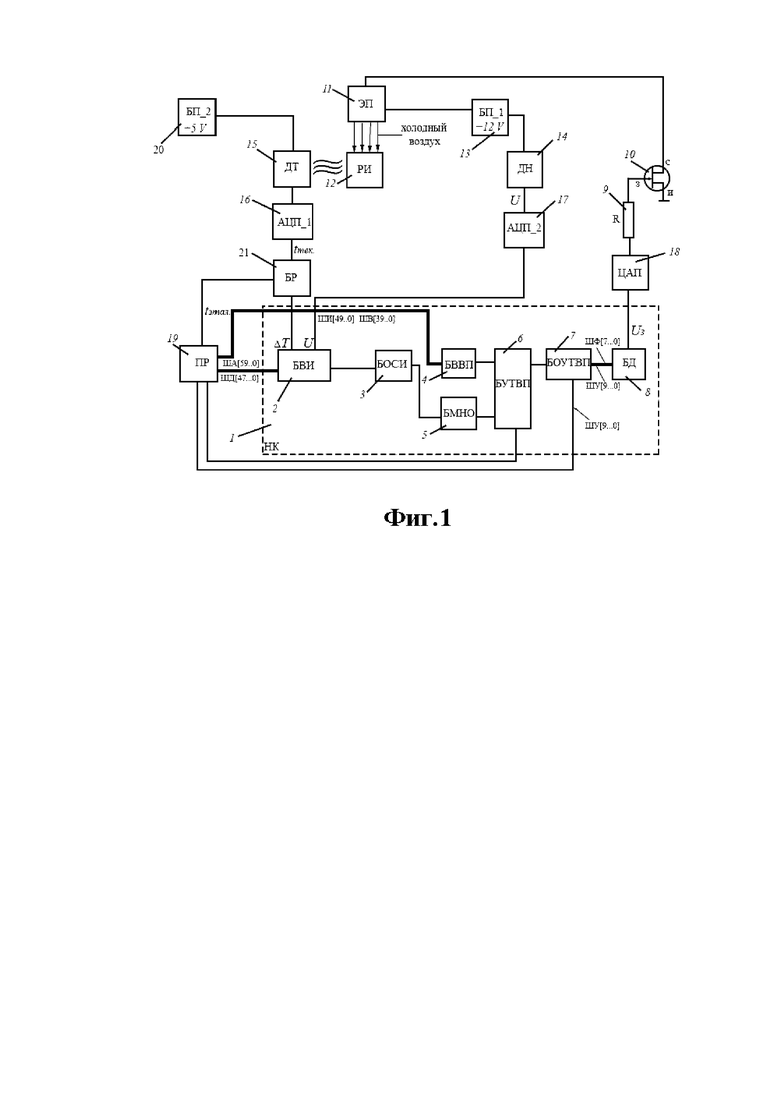

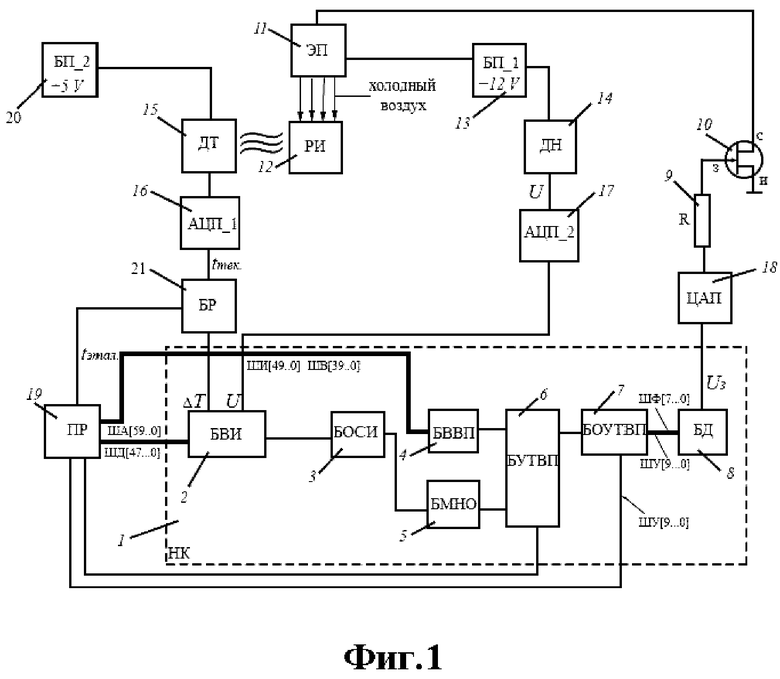

Сущность устройства для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ поясняется чертежами, где

на Фиг.1 приведена схема устройства для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ,

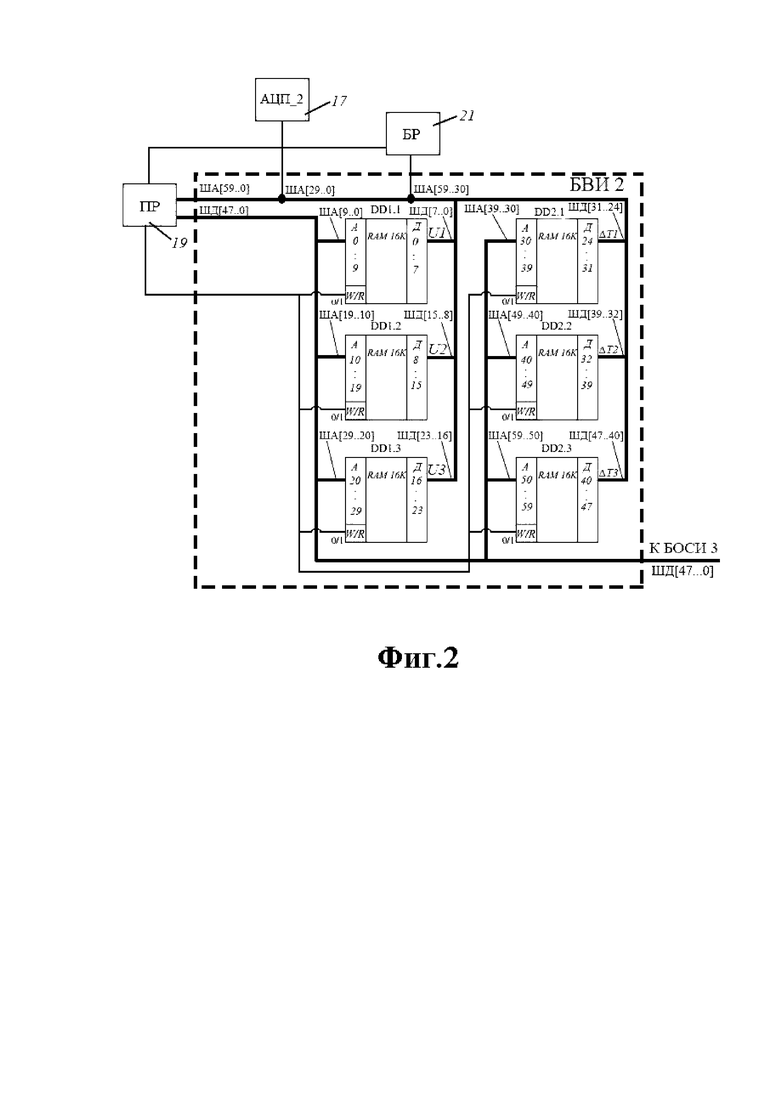

на Фиг.2 представлен блок ввода информации,

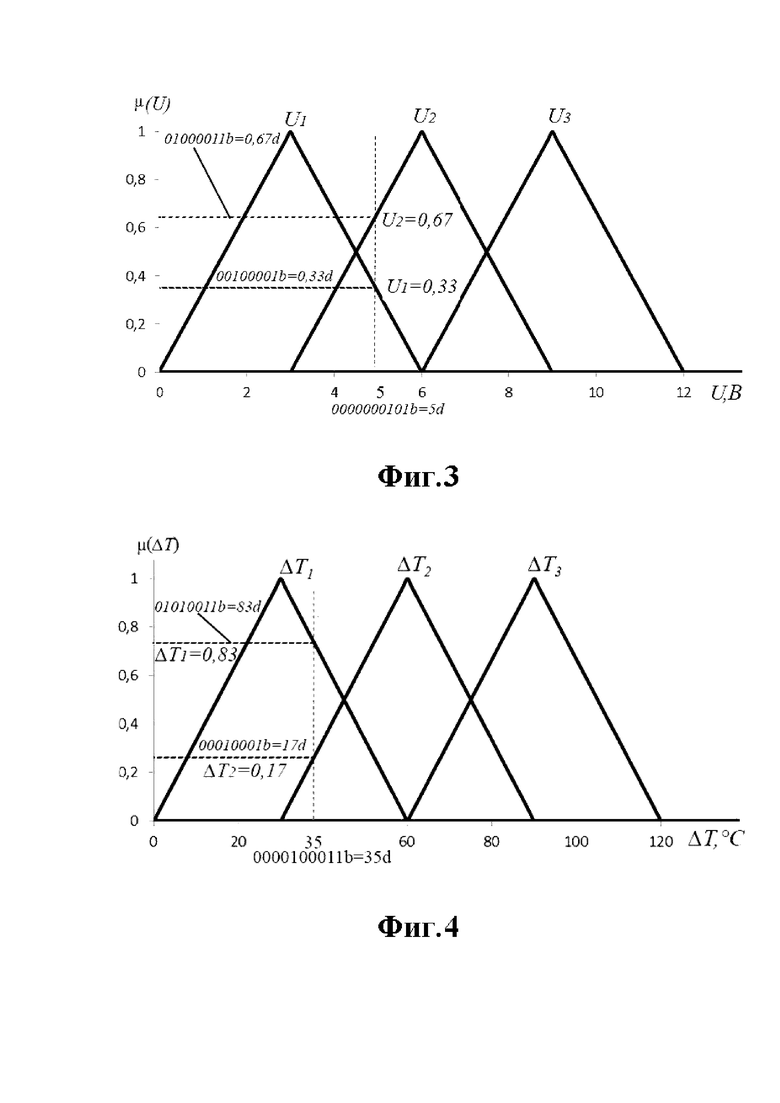

на Фиг.3 представлены треугольные функции принадлежности для первой входной переменной - напряжение на элементе Пельтье,

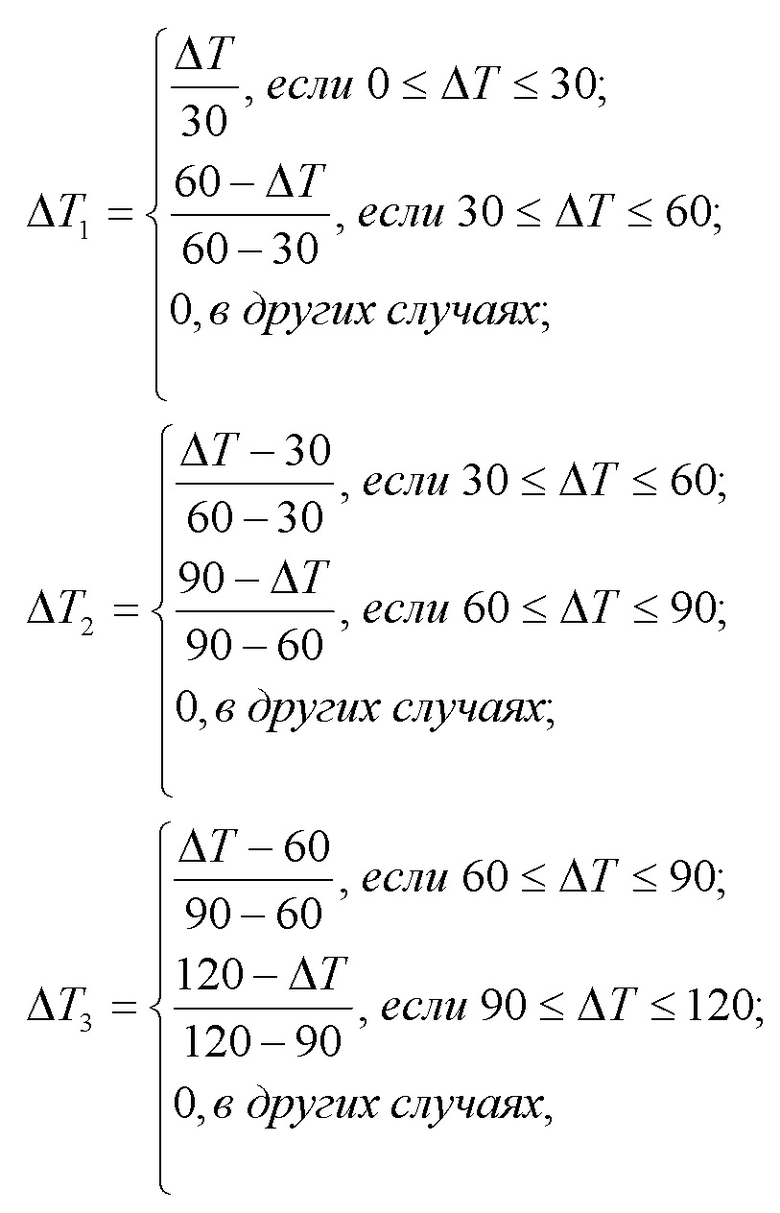

на Фиг.4 представлены треугольные функции принадлежности для второй входной переменной – разность температур в зоне резания на выходе блока разности,

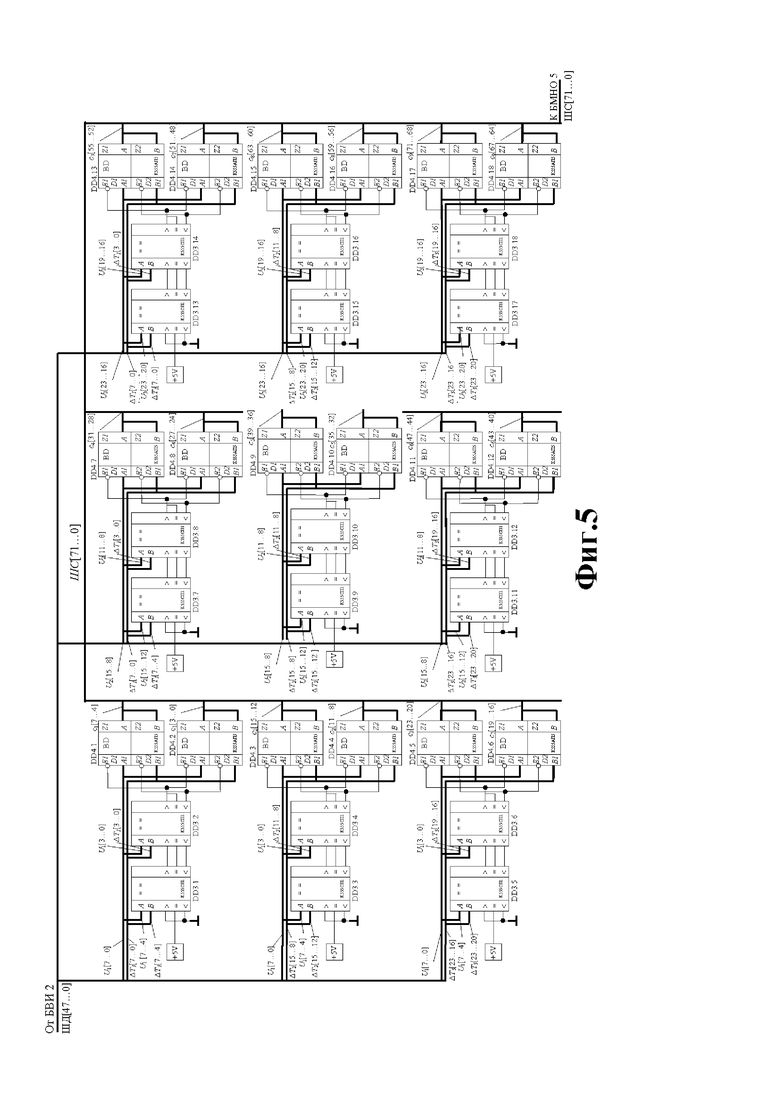

На Фиг.5 представлен блок определения степеней истинности;

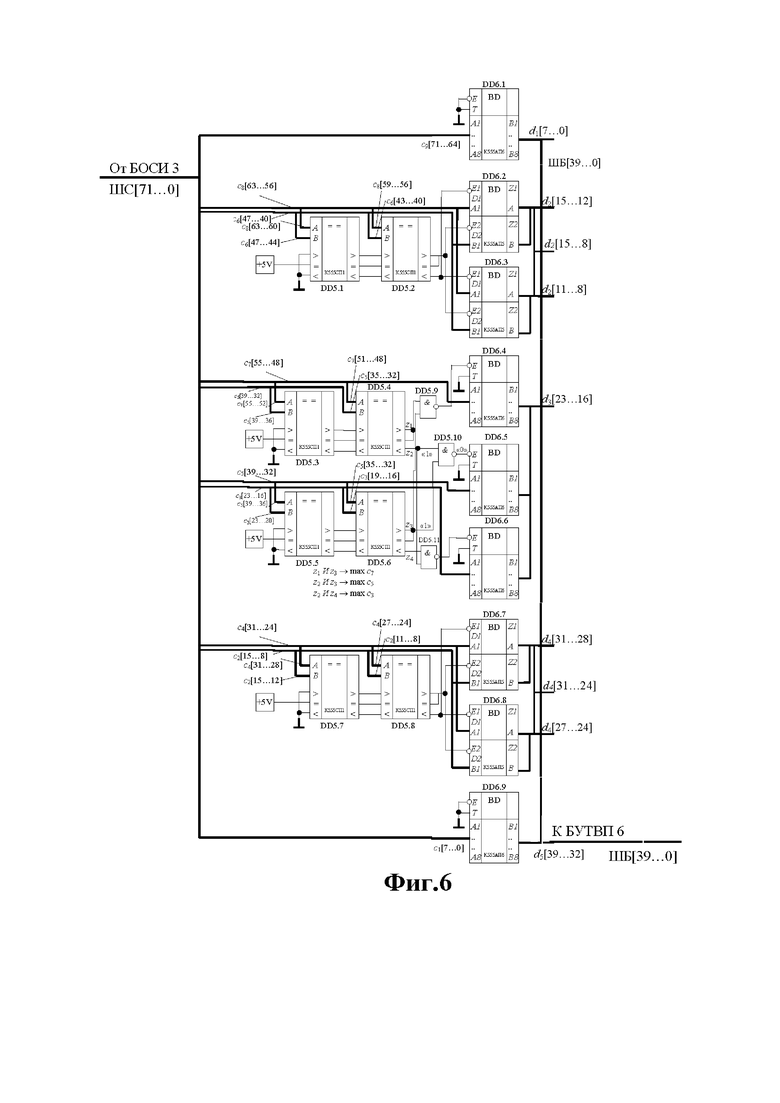

на Фиг.6 представлен блок матрицы нечетких отношений,

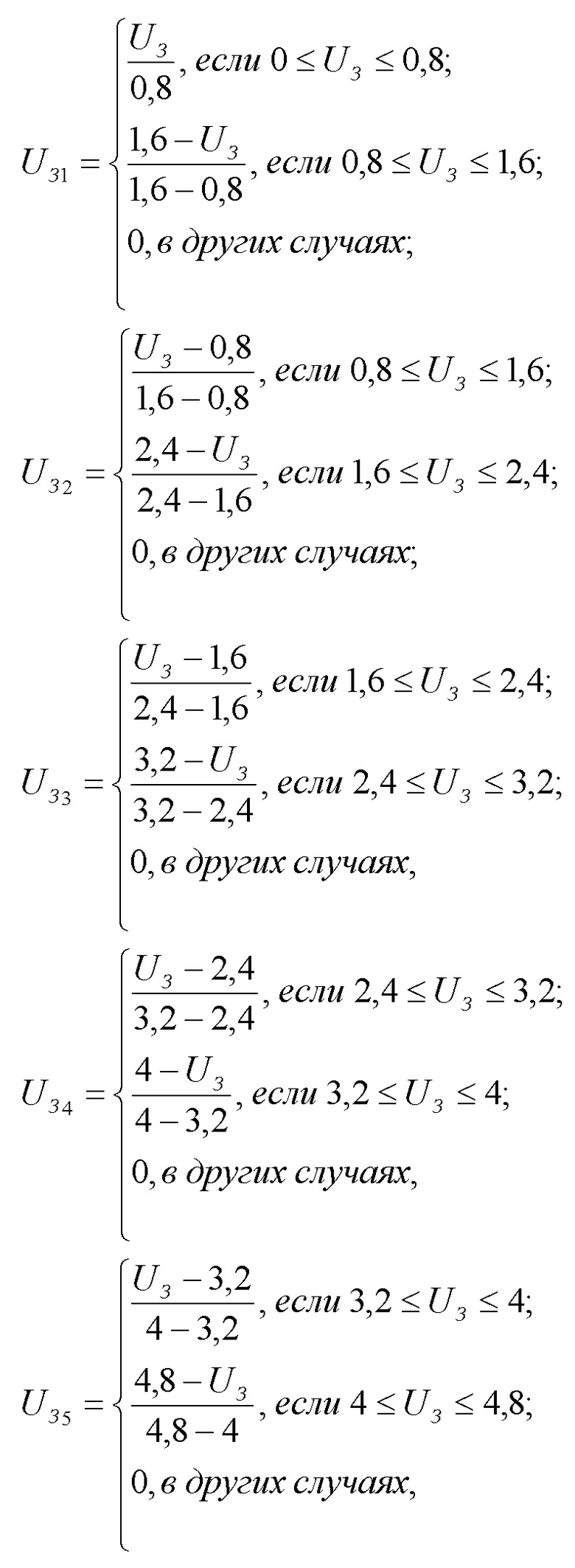

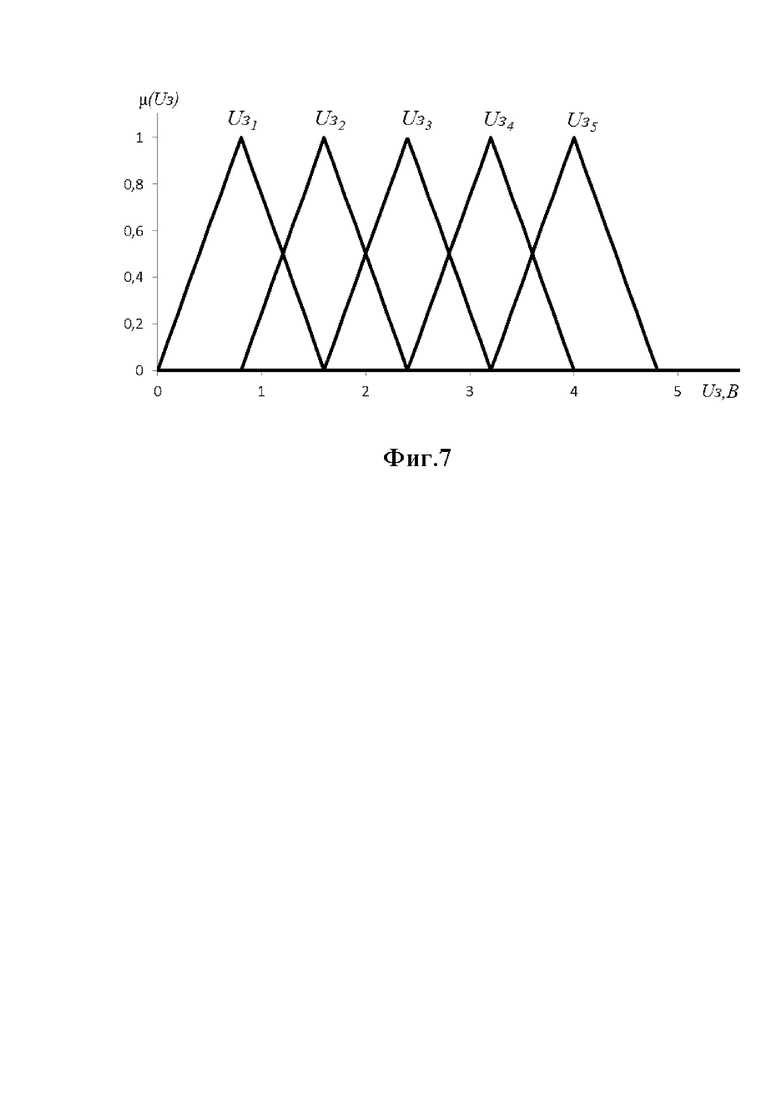

на Фиг.7 представлены треугольные функции принадлежности для выходной переменной – выходное напряжение, подаваемое на затвор полевого транзистора,

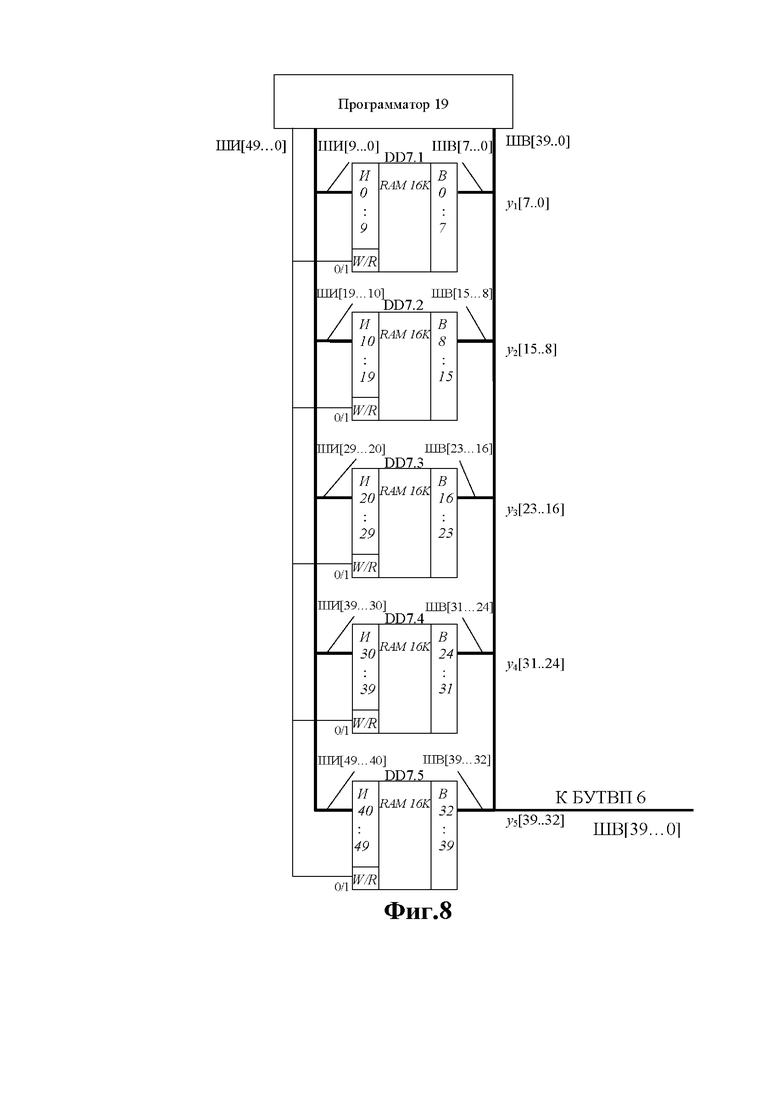

на Фиг.8 представлен блок ввода выходной переменной,

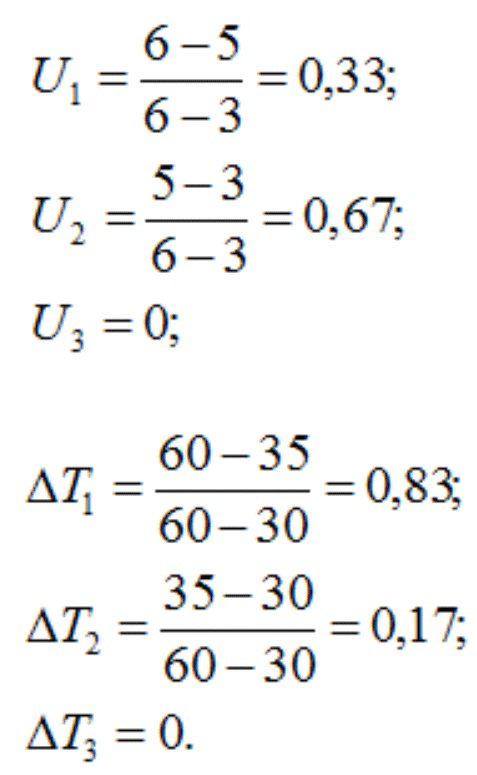

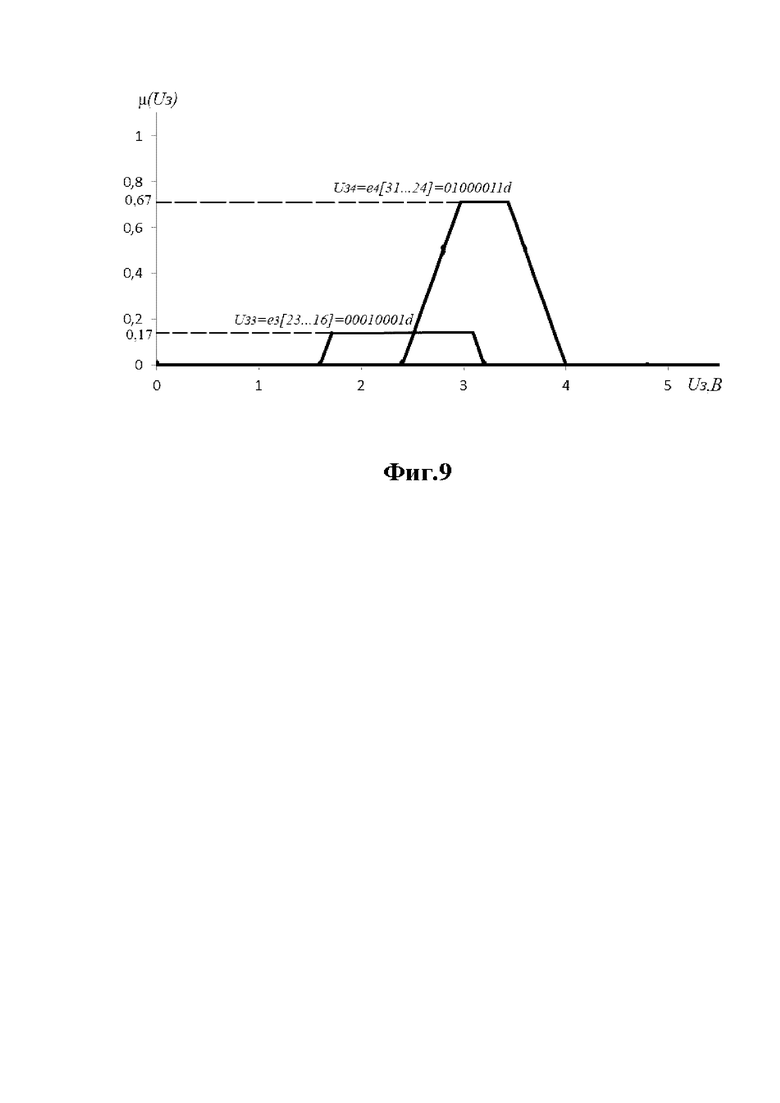

на Фиг.9 представлен графический результат этапа усечения термов выходных функций принадлежности,

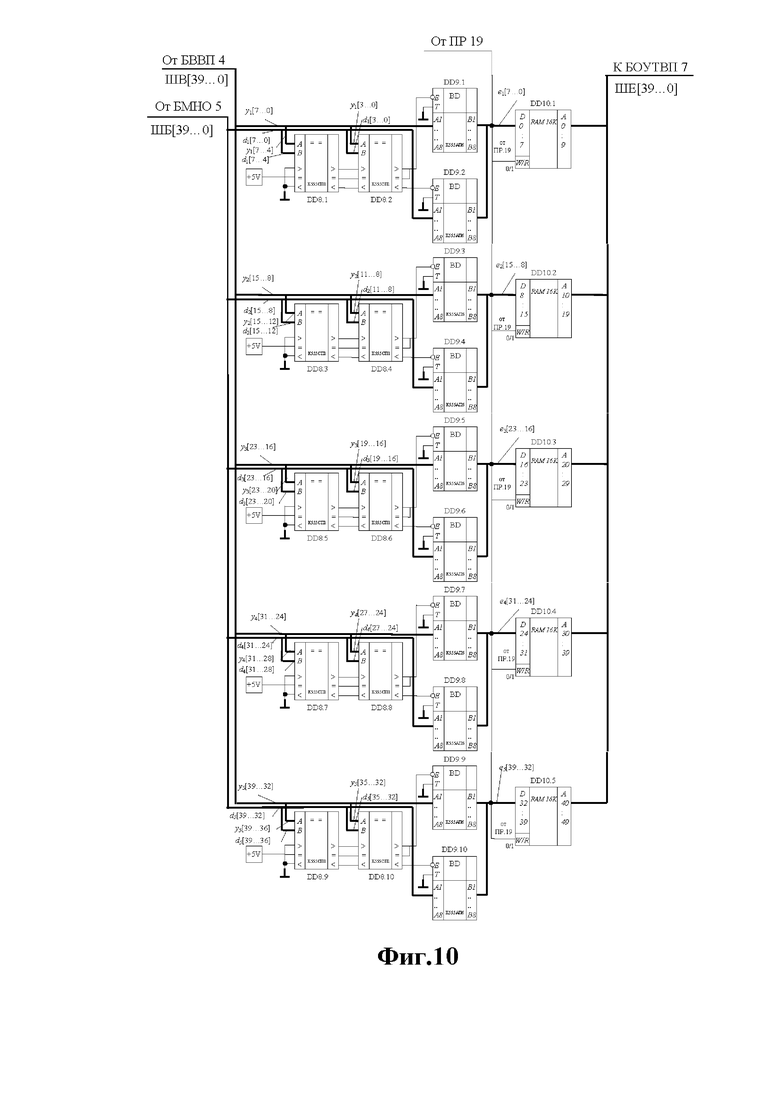

на Фиг.10 представлен блок усечения термов выходной переменной,

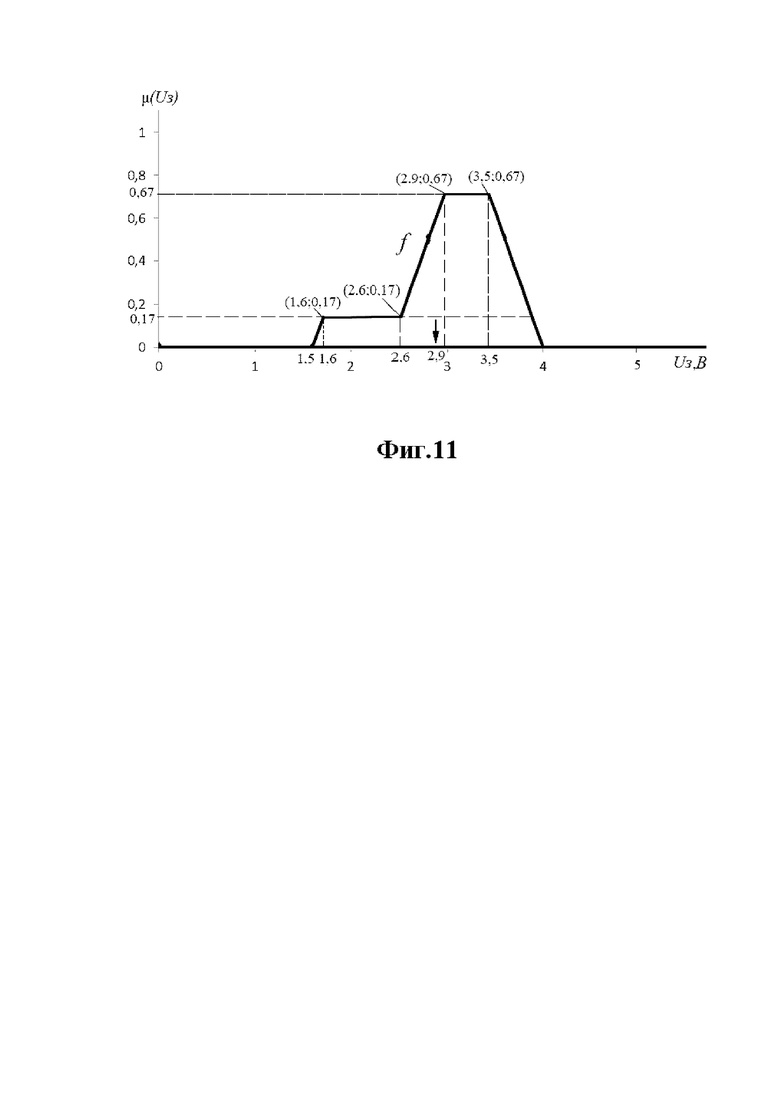

на Фиг.11 представлен графический результат этапа объединения усеченных термов выходной функции принадлежности в один массив данных,

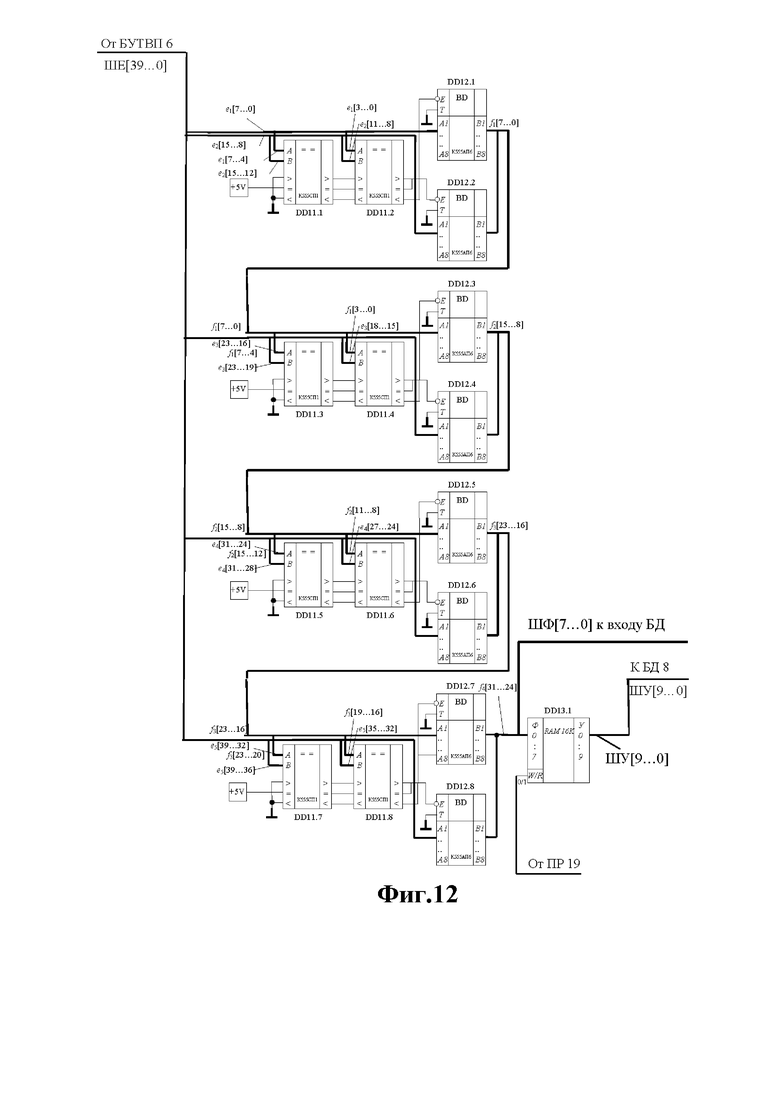

на Фиг.12 представлен блок объединения усеченных термов выходной функции принадлежности,

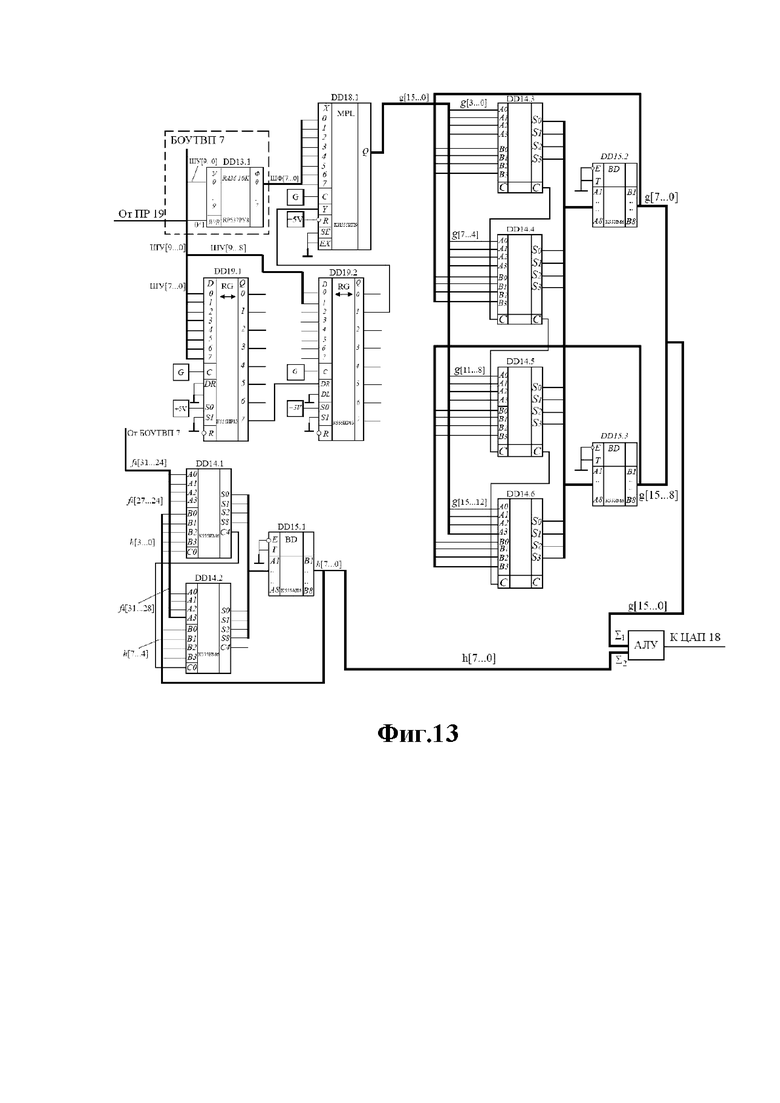

на Фиг.13 представлен блок дефаззификации.

Устройство для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ содержит нечеткий контроллер (НК) 1, блок ввода информации (БВИ) 2, блок определения степеней истинности (БОСИ) 3, блок ввода выходной переменной (БВВП) 4, блок матрицы нечетких отношений (БМНО) 5, блок усечения термов выходной переменной (БУТВП) 6, блок объединения усеченных термов выходной переменной (БОУТВП) 7, блок дефаззификации (БД) 8, резистор 9, полевой транзистор 10, элемент Пельтье 11, режущий инструмент 12, блок питания 12V (БП_1) 13, датчик напряжения 14, датчик температуры 15, аналого-цифровой преобразователь (АЦП_1) 16, аналого-цифровой преобразователь (АЦП_2) 17, цифро-аналоговый преобразователь (ЦАП) 18, программатор 19, блок питания 5V (БП_2) 20, блок разности 21.

Связи в устройстве для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ расположены следующим образом: выход БП_2 20 соединен с входом датчика температуры 15, при этом датчик температуры установлен в зоне резания, первый выход БП_1 13 соединен с одним выводом элемента Пельтье 11. Второй выход БП_1 13 соединен с входом датчика напряжения 14, выход датчика напряжения 14 соединен с входом АЦП_2 17, выход АЦП_2 17 соединен с первым входом БВИ 2. Выход датчика температуры 15 соединен с входом АЦП_1 16, выход АЦП_1 16 соединен с первым входом блока разности 21, второй вход блока разности 21 соединен с первым выходом программатора 19, выход блока разности 21 соединен со вторым входом БВИ 2. Вход программатора 19 соединен с компьютером (в заявке не указа), первый выход программатора 19 подключен к третьему входу БВИ 2, второй выход программатора 19 подключен к входу БВВП 4, третий выход программатора 19 соединен с БУТВП 6, четвертый выход программатора 19 соединен с БОУТВП 7. Выход БВИ 2 соединен с входом БОСИ 3, выход БОСИ 3 соединен с входом БМНО 5, выход БМНО 5 соединен с первым входом БУТВП 6, второй вход БУТВП 6 соединен с выходом БВВП 4, выход БУТВП 6 соединен с входом БОУТВП 7, выход БОУТВП 7 соединен с БД 8, выход БД 8 соединен с входом ЦАП 18, выход ЦАП 18 соединен с одним выводом резистора 9, другой вывод резистора 9 соединен с затвором полевого транзистора 10, исток полевого транзистора 10 соединен с землей, сток полевого транзистора 10 соединен с другим выводом элемента Пельтье 11. Холодная сторона элемента Пельтье 11 направлена на режущий инструмент 12.

Устройство для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ работает следующим образом. В процессе обработки изделий происходит нагрев режущего инструмента 12, возникают температурные деформации, которые необходимо компенсировать, так как это приводит к уменьшению периода стойкости режущего инструмента 12. Температура режущего инструмента 12 от датчика температуры 15 поступает в блок разности 21. В блоке разности 21 рассчитывается разность температур ΔT между эталонным tэтал. и текущем значении температуры tтек.: ΔT= tэтал.- tтек, которую необходимо минимизировать ΔT→min. Для этого НК 1 рассчитывает напряжение Uз, которое передается на затвор полевого транзистора 10. Полевой транзистор 10 изменяет величину тока стока и передает ее на элемент Пельтье 11, который в свою очередь изменяет интенсивность охлаждения режущего инструмента 12. Изначально на элементе Пельтье 11 установлено напряжение 12 V. В процессе работы способа в нечетком контроллере 1 перерасчитывается и изменяется напряжение, которое передается на резистор 9. Это вызывает изменение тока стока полевого транзистора 10, следовательно изменяется напряжение на элементе Пельтье 11, которое контролирует датчик напряжения 14.

Расчет величины напряжения Uз в НК 1 осуществляется следующим образом. Величина напряжения на элементе Пельтье 11 поступает в НК 1 в БВИ 2 от датчика напряжения 14, посредством АЦП_2 17. Разность температур - ΔT поступает так же в БВИ 2 от блока разности 21. Перед обработкой изделий на оборудовании с ЧПУ в БВИ 2 и БВВП 4 с помощью программатора 19 записываются входные и выходная функции принадлежности. Для этого программатор 19 устанавливает контакты W/R элементов DD1.1, DD1.2, DD1.3, DD2.1, DD2.2, DD2.3 в состояние логического нуля (Фиг.2).

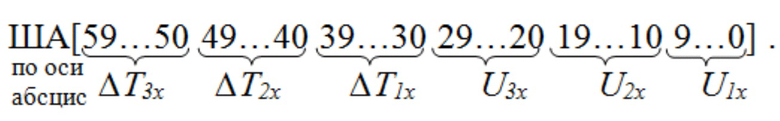

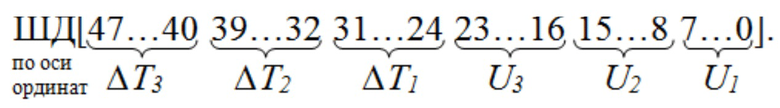

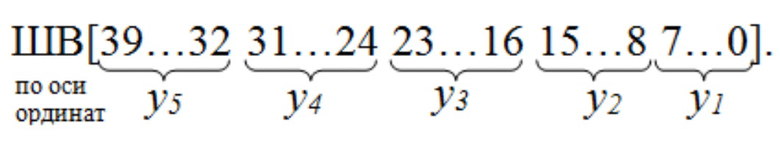

Далее в БВИ 2, в блоки DD1.1, DD1.2, DD1.3, DD2.1, DD2.2, DD2.3 поступают сигналы по шине адреса ША[59..0] и по шине данных ШД[47..0]. Фактически сигналы на ША[59..0] соответствуют значениям по оси абсцисс входных переменных U и ΔT, а значения на ШД[47:0] соответствуют значениям этих переменных по оси ординат. Шина адреса ША[59…0] состоит из 60 разрядов формат которой имеет вид:

Шина данных ШД[47…0] состоит из 48 разрядов, формат которой имеет вид:

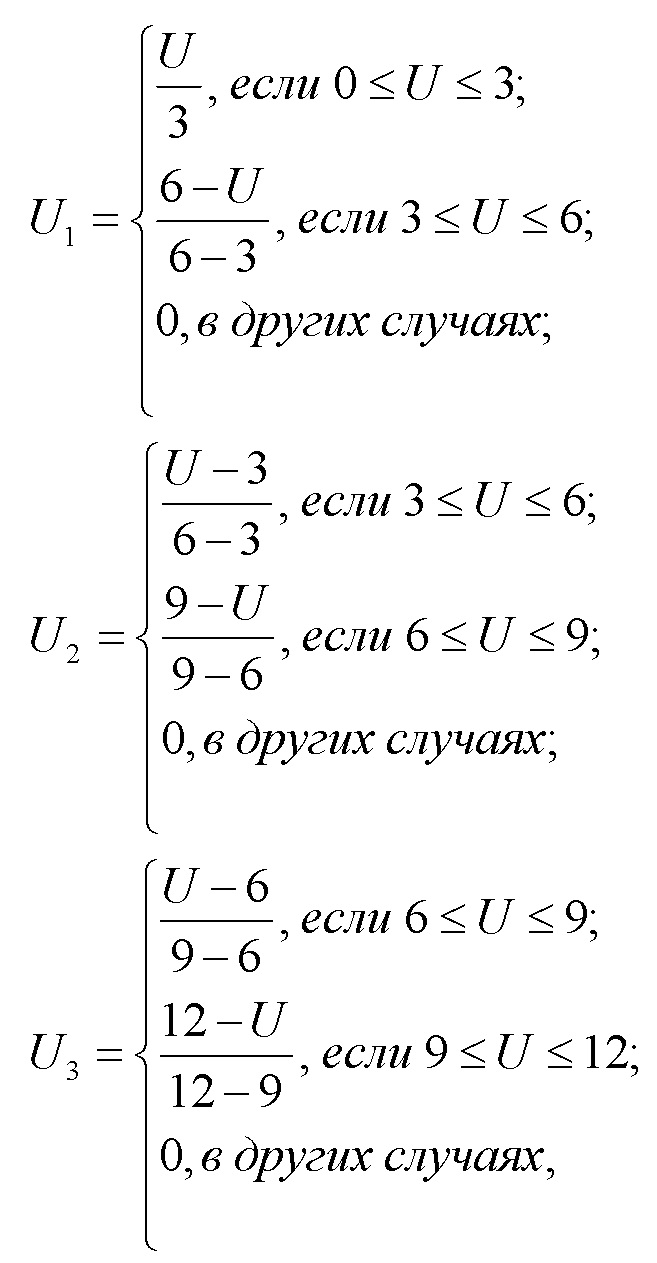

В блок DD1.1 поступает сигнал по шине адреса ША[9...0] и шине данных ШД[7...0] для хранения функции принадлежности U1 первой входной переменной (Фиг.3). В блок DD1.2 поступают сигналы по шине адреса ША[19...10] и шине данных ШД[15...8] для хранения функции принадлежности U2 первой входной переменной. В блок DD1.3 поступают сигналы по шине адреса ША[29...20] и шине данных ШД[23...16] для хранения функции принадлежности U3 первой входной переменной. В блок DD2.1 поступают сигналы по шине адреса ША[39...30] и шине данных ШД[31...24] для хранения функции принадлежности ΔT1 второй входной переменной (Фиг.4). В блок DD2.2 поступают сигналы по шине адреса ША[49...40] и шине данных ШД[32...29] для хранения функции принадлежности ΔT2 второй входной переменной. В блок DD2.3 поступают сигналы по шине адреса ША[59..50] и шине данных ШД[47...40] для хранения функции принадлежности ΔT3 второй входной переменной. В качестве элементов DD1.1, DD1.2, DD1.3, DD2.1, DD2.2, DD2.3 могут использоваться схемы оперативно-запоминающих устройств (ОЗУ) RAM16K, например схема КР537РУ8.

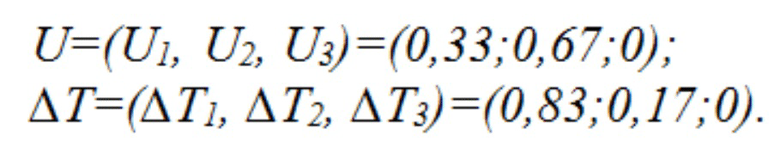

Следует учитывать, что данные вводимые по ШД[47...0] являются целыми и находятся в диапазоне [0…255], чтобы они соответствовали значениям оси ординат из диапазона [0…1] их необходимо разделить на 100.

Например, напряжению равному 5В, соответствует сигнал, поступающий на ША[9...0]=0000000101b(5d) (Фиг.3). Для первой функции принадлежности U1 первой входной переменной U сигнал на ШД[7..0] вычисляется в программаторе 19 по формуле: (6-5)/(6-3)=1/3=0,33, затем умножается на 100 и передается по ШД[7...0]=00100001b(33d) в блок DD1.1, где и хранится. Для второй функции принадлежности U2 первой входной переменной U напряжению равному 5В соответствует сигнал, поступающий на ША[19...10]=0000000101b(5d) (Фиг.3). Сигнал на ШД[15..8] вычисляется в программаторе 19 по формуле: (5-3)/(6-3)=2/3=0,67, затем умножается на 100 и передается по ШД[15...8]=01000011b(67d) в блок DD1.2, где и хранится.

Для третей функции принадлежности U3 первой входной переменной U напряжению равному 5В соответствует сигнал, поступающий на ША[29...20]=0000000000b(5d) (Фиг.3). Сигнал на ШД[23...16] вычисляется в программаторе 19 по формуле: (9-5)/(9-6)=4/3=1,3, причем если полученный сигнал больше единицы, то по ШД[23...16] в блок DD1.3 записывается и хранится 0.

Разности температур равной 35 C0 соответствует сигнал, поступающий на ША[39…30]=0000100011b(35d) (Фиг.4). Сигнал на ШД[31...24] вычисляется в блоке разности 21 по формуле: (60-35)/(60-30)=5/6=0,83, затем умножается на 100 и передается по ШД[31...24]=01010011b(83d) в блок DD2.1, где и хранится. Для второй функции принадлежности ΔT2 второй входной переменной ΔT разности температур равной 35 C0 соответствует сигнал, поступающий на ША[49...40]=0000100011b(35d) (Фиг.4). Сигнал на ШД[39...32] вычисляется в блоке разности 21 по формуле: (35-30)/(60-30)=1/6=0,17, затем умножается на 100 и передается по ШД[39...32]=00010001b(17d) в блок DD2.2, где и хранится. Для третей функции принадлежности ΔT3 второй входной переменной ΔT разности температур равной 35 C0 соответствует сигнал, поступающий на ША[59...50]=0000000000b(35d) (Фиг.4). Сигнал на ШД[39...32] вычисляется в блоке разности 21 по формуле: (90-35)/(90-60)=11/6=1,8, причем, если полученный сигнал больше единицы, то по ШД[39...32] в блок DD2.3 записывается и хранится 0.

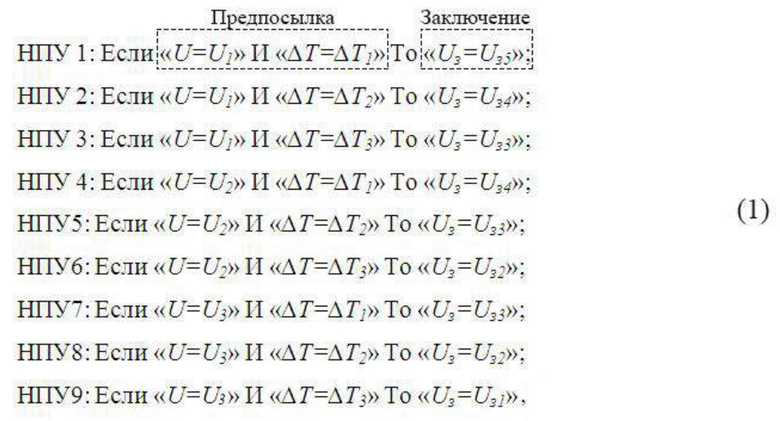

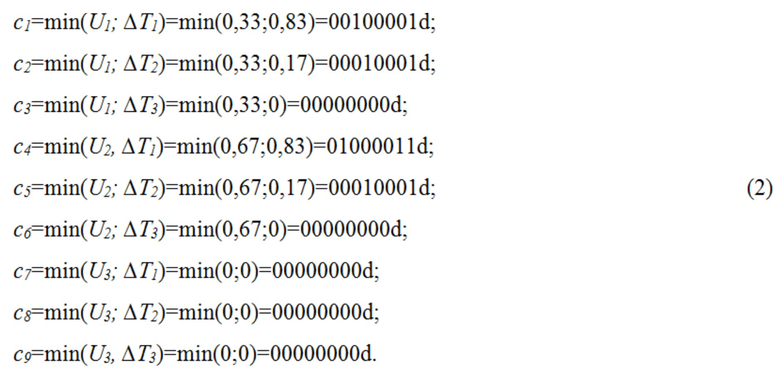

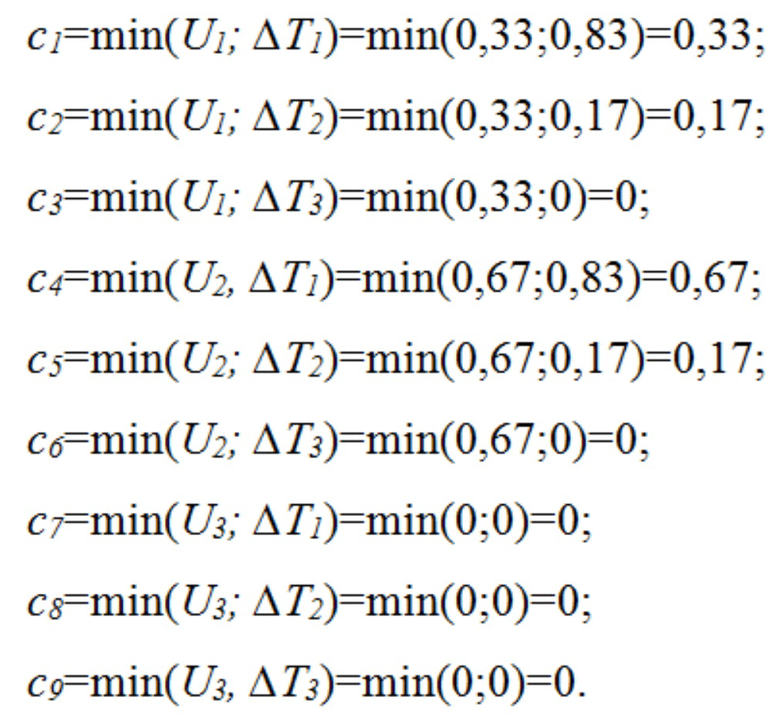

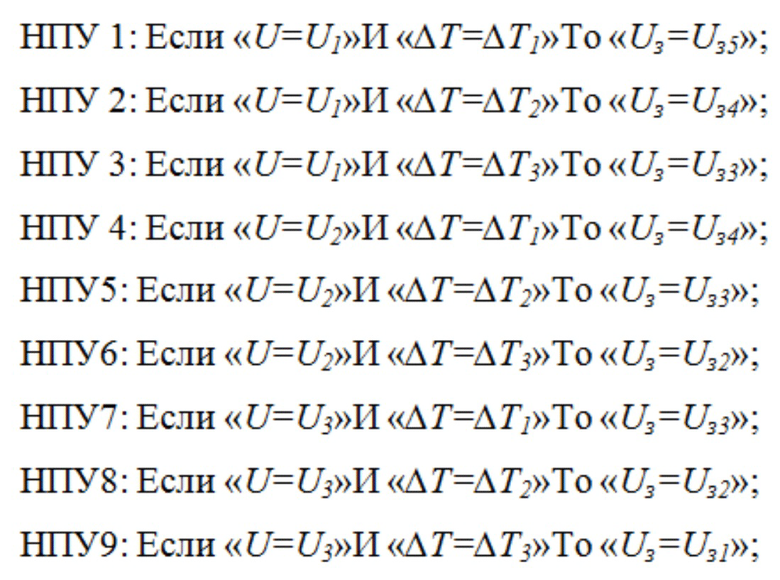

Для расчета 9 предпосылок нечетких правил управления (НПУ):

где U1…3 – численные значения входного напряжения на элементе Пельтье;

ΔT1…3 – численные значения входной разности температур в зоне резания на

выходе блока разности;

UЗ1…З5 – численные значения выходного напряжения, подаваемого на затвор

полевого транзистора;

программатор 19 устанавливает контакты W/R блоков DD1.1, DD1.2, DD1.3, DD2.1, DD2.2, DD2.3 в состояние логической единицы. После этого в БВИ 2 поступают данные от датчика напряжения 14 (U) и блока разности 21 (ΔT). Если U =5В и ΔT=35 , тогда на выходе блока БВИ 2 формируются следующие сигналы: U1=0,33; U2=0,67; U3=0; ΔT1=0,83; ΔT2=0,17; ΔT3=0, которые по шине данных ШД[47…0] передаются в БОСИ 3 (Фиг. 5).

Для расчета предпосылки НПУ1 (Если «U=U1» И «ΔT=ΔT1») в БОСИ 3 8-ми разрядные сигналы U1 и ΔT1 разбиваются по 4 разряда. Для этого в блок DD3.1 на входы А[3...0] и B[3...0] передаются старшие разряда сигнала U1[7...4] и ΔT1[7...4], соответственно. А на входы блока DD3.2 А[3...0] и B[3...0] передаются младшие разряда сигнала U1[3…0] и ΔT1[3…0], соответственно. Логическая операции «И» реализуется как операция нахождения минимума.

В зависимости от результата операции сравнения в компараторах DD3.1 и DD3.2 на выходе компаратора DD3.2 будет проходить тот сигнал U1 или ΔT1, значение которого минимально min(U1;ΔT1)=min(0,33;0,83). В случае если сигнал U1 окажется меньше ΔT1, то на выходе «<» блока DD3.2 будет сигнал логической единицы, который заблокирует инверсные входы E2 блоков DD4.1, DD4.2. Таким образом, в блок DD4.1 на выходы Z2 не будут поступать старшие разряды сигнала ΔT1[7...4] и на выходы Z2 блока DD4.2 младшие разряды сигнала ΔT1[3…0]. Тогда блок DD4.1 пропустит старшие разряды сигнала U1[7…4], а блок DD4.2 пропустит младшие разряды сигнала U1[3…0]. При этом на выходе шины ШС[71…0] формируется 8-ми разрядный сигнал c1[7…0], реализующий операцию взятия минимума min(U1, ΔT1)=(0,33;0,83)=00100001. В качестве компараторов DD4.1, DD4.2, DD4.3, DD4.4, DD4.5, DD4.6, DD4.7, DD4.8, DD4.9, DD4.10, DD4.11, DD4.12, DD4.13, DD4.13, DD4.14, DD4.15, DD4.16, DD4.17, DD4.18 могут использоваться цифровые схемы К555АП5, а в качестве блоков DD3.1, DD3.2, DD3.3, DD3.4, DD3.5, DD3.6, DD3.7, DD3.8, DD3.9, DD3.10, DD3.11, DD3.12, DD3.13, DD3.14, DD3.15. DD3.16, DD3.17, DD3.18 могут

использоваться логические элементы K555CП1.

Для расчета предпосылки НПУ 1 в блок DD3.1 поступают старшие разряды сигнала U1[7...4]=0010 и ΔT1[7…4]=0101, а в блок DD3.2 младшие разряды сигнала U1[3...0]=0001 и ΔT1[3…0]=0011. Для расчета предпосылки НПУ 2 в блок DD3.3 поступают старшие разряды сигнала U1[7...4]=0010 и ΔT2[15…12]=0001, а в блок DD3.4 младшие разряды сигнала U1[3...0]=0001 и ΔT2[11…8]=0001. Для расчета предпосылки НПУ3 в блок DD3.5 поступают

старшие разряды сигнала U1[7...4]=0010 и ΔT3[23…20]=0000, а в блок DD3.6 младшие разряды сигнала U1[3...0]=0001 и ΔT3[19…16]=0000. Для расчета предпосылки НПУ 4 в блок DD3.7 поступают старшие разряды сигнала U2[15...12]=0100 и ΔT1[7…4]=0101, а в блок DD3.8 младшие разряды сигнала U2[11...8]=0011 и ΔT1[3…0]=0011. Для расчета предпосылки НПУ 5 в блок DD3.9 поступают старшие разряды сигнала U2[15...12]=0100 и

ΔT2[15…12]=0001, а в блок DD3.10 младшие разряды сигнала U2[11...8]=0011 и ΔT2[11…8]=0001. Для расчета предпосылки НПУ 6 в блок DD3.11 поступают старшие разряды сигнала U2[15...12]=0100 и ΔT3[23…20]=0000, а в блок DD3.12 младшие разряды сигнала U2[11...8]=0011 и ΔT3[19…16]=0000.

Для расчета предпосылки НПУ 7 в блок DD3.13 поступают старшие разряды сигнала U3[23...20]=0000 и ΔT1[7…4]=0101, а в блок DD3.14 младшие разряды сигнала U3[19...16]=0000 и ΔT1[3…0]=0011. Для расчета предпосылки НПУ 8 в блок DD3.15 поступают старшие разряды сигнала U3[23...20]=0000 и ΔT2[11…8]=0001, а в блок DD3.16 младшие разряды сигнала U3[19...16]=0000 и ΔT2[11…8]=0001. Для расчета предпосылки НПУ в блок DD3.17 поступают старшие разряды сигнала U3[23...20]=0000 и ΔT3[23…20]=0000, а в блок DD3.18 младшие разряды сигнала U3[19...16]=0000 и ΔT3[19…16]=0000.

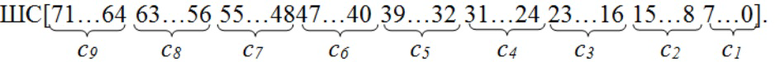

Шина ШС[71…0] подключена к входу БМНО 5 и состоит из 72 разрядов формат которой имеет вид:

При реализации операции взятия минимума с учетом предпосылок девяти нечетких правил управления на выходе шины ШС[71…0] БОСИ 3 формируются следующие сигналы:

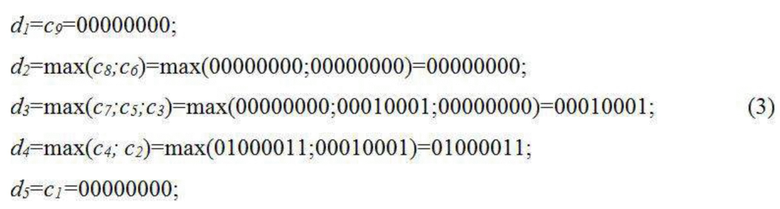

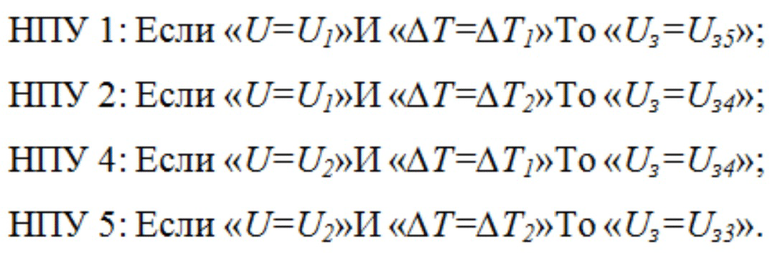

По шине ШС[71…0] сигнал от БОСИ 3 поступает на вход БМНО 5, в котором осуществляется формирование уровней отсечения для термов выходной переменной.

В БМНО 5 выполняются следующие операции нахождения максимумов:

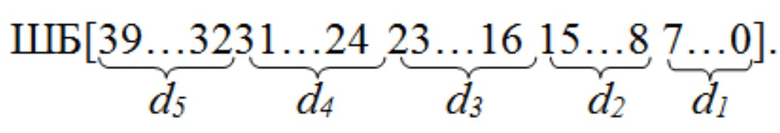

На выходе БМНО 5 формируется сигнал ШБ[39…0] формат которого имеет вид:

БМНО 5 работает следующим образом. В соответствие с формулой (3) сигнал d1=c1 хранится в блоке DD6.1, сигнал d5=c9 хранится в блоке DD6.9 (Фиг.6).

Для реализации операции взятия максимума d2=max(c8, c6) используются блоки DD5.1 и DD5.2 и блоки DD6.2 и DD6.3. Причем в DD6.2 хранятся старшие разряды сигнала d2[15…12], а DD6.2 хранятся младшие разряды сигнал d2[11…8].

В блок DD5.1 поступают для сравнения старшие разряды сигналов с8[63…60] и с6[47…44], а в блок DD5.2 поступают для сравнения младшие разряды сигналов с8[59…56] и с6[43…40]. В зависимости от результата операции сравнения на 8-ми разрядный сигнал d2[15…8] будет проходить тот сигнал c8[63…56] или c6[47…40], значение которого максимально. В случае если сигнал с6=00000000 равен сигналу с8=00000000, так как выход блока DD5.2 «=» соединен с выходом «>», то сигнал логической единицы заблокирует инверсные входы E2 блоков DD6.2 и DD6.3. Таким образом, не будет пропускаться на выходы Z2 схемы DD6.2 старшие разряды сигнала с6[63…60]=0000 и на выходы Z2 схемы DD6.3 младшие разряды сигнала с6[59…56]=0000. Тогда блок DD6.2 пропустит старшие разряды сигнала с8[47…44]=0000, а блоков DD6.3 пропустит младшие разряды сигнала с8[43…40]=0000. При этом на выходе шины данных d2[15…8]=00000000 формируется 8-ми разрядный сигнал, реализующий операцию взятия максимума d2=max(c8, c6)=00000000.

Для реализации операции взятия максимума d3=max(c7, c5, c3) используются блоки DD5.3, DD5.4, DD5.5, DD5.6, DD5.9, DD5.10, DD5.11, DD6.4, DD6.5, DD6.6. На вход блока DD5.3 поступают старшие разряды сигналов c7[55…52]=0000 и c [39…32]=0001. На вход блока DD5.4 поступают младшие разряды сигналов c7[51…48]=0000 и c5[35…32]=0001. На вход блока DD5.5 поступают старшие разряды сигналов c5[39…36]=0001 и c3[23…20]=0000. На вход блока DD5.6 поступают младшие разряды сигналов c5[35…32]=0001 и c3[19…16]=0000.

В зависимости от результата операции сравнения на 8-ми разрядный сигнал d3[23…16] будет проходить тот сигнал c7=00000000, c5=00010001 или c3=00000000, значение которого максимально. В случае если сигнал с5=00010001 окажется больше с7=00000000 и с3=00000000, то на выходе Z2 «<» блока DD5.4 и выходе Z3 «>» блока DD5.6 будет сигнал логической единицы, что сформирует на выходе блока DD5.10 сигнал логического нуля, который откроет инверсный вход блока DD6.5 Е и позволит записать в него сигнал c5[39…32]=00010001, который и будет являться выходным 8-ми разрядным сигналом d3[23…16]=00010001. Блоки DD5.9, DD5.10, DD5.11 настроены таким образом, если на выходе Z1 блока DD5.4 и выходе Z3 блока DD5.6 будут сигналы логической единицы, то на выходе d3[23…16] будет максимальный сигнал с7[55…48], который будет равняться сигналу d3[23…16]. Если на выходе Z2 блока DD5.4 и выходе Z4 блока DD5.6 будут сигналы логической единицы, то блок DD5.11 активирует блок DD6.6 и в него будет записан максимальный сигнал с3[23…16]. В данном случае операция взятия максимума имеет вид: d3=max(c7;с5;с3); d3=17b=0010001d.

Общее правило для работы блоков DD5.3, DD5.4, DD5.5, DD5.6:

Для реализации операции взятия максимума d4=max(c4, c2) используются блоки DD5.7 и DD5.8, блоки DD6.7 и DD6.8. Причем в DD6.7 хранятся старшие разряды сигнал d4[31…28]=0100, а DD6.8 хранятся младшие разряды сигнал d4[27…24]=0011.

В зависимости от результата операции сравнения на 8-ми разрядный сигнал d4[31…24] будет проходить тот сигнал c4=01000011 или c2=00010001, значение которого максимально. В случае если сигнал с4=01000011 окажется больше с2=00010001, то на выходе «>» блока DD5.8 будет сигнал логической единицы, который заблокирует инверсные входы E2 блоков DD6.7 и DD6.8. Таким образом, не будут пропускаться на выходы Z2 блока DD6.7 старшие разряды сигнала с2[15…12] и на выходе Z2 блока DD6.8 младшие разряды сигнала с2[11…8]. Тогда блок DD6.7 пропустит старшие разряды сигнала с4[31…28], а блок DD6.8 пропустит младшие разряды сигнала с4[27…24]. При этом на выходе шины данных d4[31…24] формируется 8-ми разрядный сигнал, реализующий операцию взятия максимума d4=max(c4, c2); d4=67b=1000011d. В качестве блоков DD6.1, DD6.2, DD6.3, DD6.7, DD6.8, DD6.9 могут использоваться цифровые логические элементы К555АП5, в качестве блоков DD6.4, DD6.5, DD6.6 могут использоваться цифровые логические элементы K555АП6, в качестве блоков DD5.1, DD5.2, DD5.3, DD5.4, DD5.5, DD5.6, DD5.7, DD5.8, используются цифровые схемы компараторов K555СП1. В качестве блоков DD5.9, DD5.10, DD5.11 используются логические элементы 2И-НЕ, выполненных на логических схемах К555ЛА3.

БВВП 4 хранит выходную функцию принадлежности – напряжение на затворе полевого транзистора 10 UЗ (Фиг.7). Запись функций принадлежности осуществляется аналогично записи информации в блок БВИ 2. Программатор 19 устанавливает контакты W/R блоков DD7.1, DD7.2, DD7.3, DD7.4, DD7.5 в состояние логического нуля (Фиг.8).

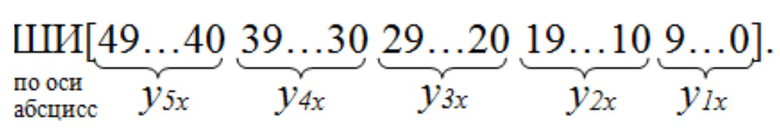

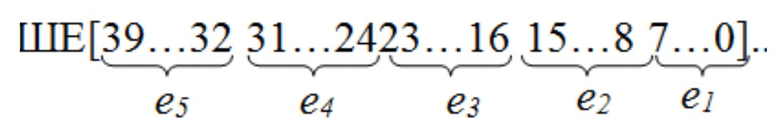

Далее в БВВП 4, в блоки DD7.1, DD7.2, DD7.3, DD7.4, DD7.5 поступают сигналы по шине адреса ШИ[49…0] и по шине данных ШВ[39…0]. Фактически сигналы на ШИ[43…0] соответствуют значениям по оси абсцисс выходной переменной UЗ, а значения на ШВ[39…0] соответствуют значениям выходной переменной UЗ по оси ординат. Формат шины адреса ШИ[49…0] имеет вид:

Шина данных ШВ[39…0] состоит из:

В блок DD7.1 поступает сигнал по шине адреса ШИ[9…0] и шине данных ШВ[7…0] для хранения функций принадлежности UЗ1 выходной переменной y1[7…0]. В блок DD7.2 поступает сигнал по ШИ[19…10] и шине данных ШВ[15…8] для хранения функций принадлежности UЗ2 выходной переменной y2[15…8]. В блок DD7.3 поступает сигнал по ШИ[29…20] и шине данных ШВ[23…16] для хранения функций принадлежности UЗ3 выходной переменной y3[23…16]. В блок DD7.4 поступает сигнал по ШИ[39…30] и шине данных ШВ[31…24] для хранения функций принадлежности UЗ4 выходной переменной y4[31…24]. В блок DD7.5 поступает сигнал по ШИ[49…40] и шине данных ШВ[39…32] для хранения функций принадлежности UЗ5 выходной переменной y5[39…32]. Логические

элементы DD7.1, DD7.2, DD7.3, DD7.4, DD7.5 представляют собой ОЗУ(RAM16K), выполненные на логических схемах КР537РУ8.

Следует учитывать, что данные вводимые по ШВ[39…0] являются целыми и находятся в диапазоне от [0…255], чтобы они соответствовали значениям оси ординат из диапазона [0…1] их необходимо разделить на 100.

Для передачи информации из БВВП 4 в БУТВП 6 программатор 19 устанавливает контакты W/R логических элементов DD7.1, DD7.2, DD7.3, DD7.4, DD7.5 в состояние логической единицы.

От БВВП 4 и БМНО 5 поступают сигналы в БУТВП 6 в котором осуществляется усечение термов выходной функции принадлежности. На выходе БУТВП 6 формируется сигнал ШЕ[39…0] формат которого имеет вид:

Графически результат выполнения данной операции (Uз4=01000011d,

Uз3=00010001d) представлен на Фиг.9.

Логические элементы DD8.1, DD8.2, DD8.3, DD8.4, DD8.5, DD8.6, DD8.7, DD8.9, DD8.10 выполнены на компараторах К555СП1. Буферные схемы DD9.1, DD9.2, DD9.3, DD9.4, DD9.5, DD9.6, DD9.7, DD9.8, DD9.10 выполнены на элементах К555АП6. Блоки ОЗУ DD10.1, DD10.2, DD10.3, DD10.4, DD10.5 выполнены на ОЗУ (RAM16K) КР537РУ8.

Связки компараторов выбирают минимальный сигнал и пропускают его в буфер данных. При сравнении сигналов y1[7…0]<d1[7…0] на вход компаратора DD8.1 подаются старшие разряды сигналов y1[7…4] и d1[7…4], а на компаратор DD8.2 подаются младшие разряды сигналов y1[3…0] и d1[3…0]. Если y1[7…0]<d1[7…0] то на выходе компаратора DD8.2 «<» будет сигнал логической единицы, который заблокирует инверсный вход E буферной схемы DD9.2. При этом на выходе компаратора DD8.2 «>», будет сигнал логического нуля, который откроет буферную схему DD9.1 для записи в нее минимального сигнала y1[7…0]. Запись в блок DD10.1 осуществляется после установки контакта W/R программатором 19 в состояние логического нуля. Остальные связки компараторов DD8.3, DD8.4, DD8.5, DD8.6, DD8.7, DD8.8, DD8.9, DD8.10, буферных схем DD9.3, DD9.4, DD9.5, DD9.6, DD9.7, DD9.8, DD9.9, DD9.10 и ОЗУ DD10.2, DD10.3, DD10.4, DD10.5 работают аналогично рассмотренному примеру. При этом в блоке DD10.1 хранится сигнал е1[7…0] соответствующий первой усеченной выходной функции принадлежности UЗ1. В блоке DD10.2 хранится сигнал е2[15…8] соответствующий второй усеченной выходной функции принадлежности UЗ2. В блоке DD10.3 хранится сигнал е3[23…16] соответствующий третьей усеченной выходной функции принадлежности UЗ3. В блоке DD10.4 хранится сигнал е4[31…24] соответствующий четвертой усеченной выходной функции принадлежности UЗ4. В блоке DD10.5 хранится сигнал е5[39…32] соответствующий пятой усеченной выходной функции принадлежности UЗ5 (Фиг.10). Логические элементы DD8.1, DD8.2, DD8.3, DD8.4, DD8.5, DD8.6, DD8.7, DD8.8, DD8.9, DD8.10 выполнены на компараторах К555СП1. Буферные схемы DD9.1, DD9.2, DD9.3, DD9.4, DD9.5, DD9.6, DD9.7, DD9.8, DD9.9, DD9.10 выполнены на элементах К555АП6. Блоки ОЗУ DD10.1, DD10.2, DD10.3, DD10.4, DD10.5 выполнены на ОЗУ (RAM16K) КР537РУ8.

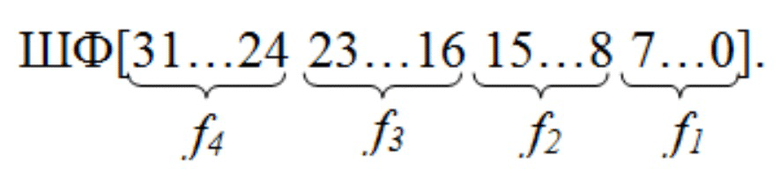

От БУТВП 6 по шине данных ШЕ[39…0] в БОУТВП 7 поступает сигнал, в котором осуществляется объединение усеченных термов выходной функции принадлежности в один массив данных. Графически результат выполнения данной операции приведен на Фиг.11. На выходе БОУТВП 7 формируется сигнал ШФ[31…0], формат которого имеет вид:

Для записи информации в БОУТВП 7 вход W/R устанавливается в состояние логической единицы с помощью программатора 19. Для передачи сигналов от блоков ОЗУ DD10.1, DD10.2, DD10.3, DD10.4, DD10.5 программатор 19 устанавливает контакт W/R в состояние логического нуля.

Связки компараторов DD11.1, DD11.2, DD11.3, DD11.4, DD14.5, DD11.6, DD11.7, DD11.8 выбирают максимальный сигнал из усеченных функций принадлежности, хранимых в блоках ОЗУ DD10.1, DD10.2, DD10.3, DD10.4, DD10.5 ШЕ[39…0] и пропускают его в буфер данных, построенных на схемах DD12.1, DD12.2, DD12.3, DD12.4, DD12.5, DD12.6, DD12.7, DD12.8.

Принцип работы БОУТВП 7 следующий. На вход компаратора DD11.1 подаются старшие разряды сигналов e1[7…4] и e2[15…12], а на компаратор DD11.2 подаются младшие разряды сигналов e1[3…0] и e2[11…8]. Если e1[7…0]<e2[15…8] то на выходе компаратора DD11.2 «<» будет сигнал логической единицы, который заблокирует инверсный вход E блока DD12.1. При этом на выходе компаратора DD11.2 «>», будет сигнал логического нуля, который откроет инверсный вход E блока DD12.2 для записи в него максимального сигнала e2[15…8]. Выходы буферных схем DD12.1 и DD12.2 соединены между собой и на общем выходе f1[7…0] будет максимальное значение из двух сигналов e1[7…0] и e2[15…8], то есть f1[7…0]=max(e1; e2). Выходы буферных схем DD12.3 и DD12.4 соединены между собой и на общем выходе f2[15…8] будет максимальное значение из двух сигналов f1[7…0] и e3[23…16], то есть f2[15…8]=max(f1; e3). Выход буферных схем DD12.5 и DD12.6 соединены между собой и на общем выходе f3[23…16] будет максимальное значение из двух сигналов f2[15…8] и e4[31…24], то есть f3[23…16]=max(f2; e4). Выход буферных схем DD12.7 и DD12.8 соединены между собой и на общем выходе f4[31…24] будет максимальное значение из двух сигналов f3[23…16] и e5[39…32], то есть f4[31…24]=max(f3; e5).

Программатор 19 устанавливает контакт W/R в состояние логического нуля, после чего в блок DD13.1 поступает максимальный сигнал из f4=max(e1, e2,e3,e4,e5). После того, как с ШФ[31…0] поступит первый сигнал в блок DD13.1 запишется первый максимальный сигнал f4[31…24]. Прошивка остальных ячеек ОЗУ, осуществляется аналогичным образом. Логические элементы DD11.1, DD11.2, DD11.3, DD11.4, DD11.5, DD11.6, DD11.7, DD11.8 выполнены на компараторах К555СП1. Буферные схемы DD12.1, DD12.2, DD12.3, DD12.4, DD12.5, DD12.6, DD12.7, DD12.8 выполнены на элементах К555АП6. Блок ОЗУ DD13.1 выполнены на ОЗУ (RAM16K) КР537РУ8.

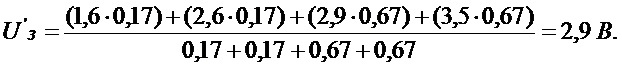

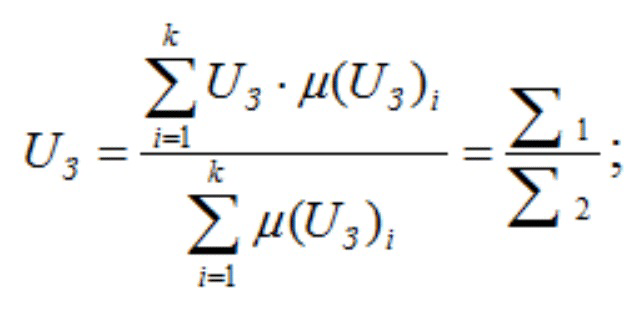

От БОУТВП 7 по шине данных ШФ[7…0] и шине адреса ШУ[9…0] поступает сигнал в БД 8 в блоки DD18.1 и DD19.1с помощью программатора 19, который устанавливает контакт W/R в состояние логической единицы. В БД 8 формируются дефаззифицированные значения выходной переменной на основе формулы (5) (Фиг.13)

где μ(UЗ)i – новые значения выходной величины напряжения, подаваемого на затвор полевого транзистора в виде новых термов функций принадлежности,

i=1...k, k - количество термов выходной переменной (k=5).

Процесс определения суммы Σ1 необходимо разделить на две операции. Первоначально перемножить два операнда между собой, а затем получившиеся результаты на каждой итерации сложить. Для выполнения операции перемножения операндов yl и μʹ(yl) используется умножитель DD18.1, выполненный на основе логической схемы К555ИП9.

В режиме умножения на входе R схемы DD18.1 должен действовать сигнал логической единицы R=1. На входы схемы умножителя DD18.1 Х[7…0] подается параллельный код сигнала, записанного в блок DD13.1. В то время как на информационный вход Y умножителя DD18.1 передается последовательный код адреса соответствующего номеру ячейки ШФ[7…0], в которой хранятся данные, передаваемые ШУ[9…0] на входы X[7…0] умножителя DD18.1. Вход умножителя DD18.1 С подключен к генератору импульсов G. Входы SE и EX заземлены. Параллельный код адреса ШУ[9…0] преобразуется в последовательный с помощью двух сдвиговых регистров DD19.1, DD19.2, которые работают в режиме сдвиг вправо. Для этого сигнал S0=1 и подключен к источнику питания +5V, а сигнал S1=0 заземлен. Регистровые схемы выполнены на цифровых схемах К555ИР13. Сигнал ШУ[9…0] 10-ти разрядный, поэтому на первую схему DD19.2 подаются старшие разряды шины адреса ШУ[9…8], а на вторую схему DD19.1 подаются младшие разряды сигнала ШУ[7…0]. Чтобы информация не была потеряна при наращивании сдвиговых регистров 7 выход схемы DD19.1 подключен к входу DR второго сдвигового регистра DD19.2. Последовательный код сигнала с ШУ[9…0] снимается с выхода 1 второй схемы DD19.2 и передается на информационный вход умножителя Y схемы DD18.1. Такое подключение логических элементов позволит осуществлять операцию умножения двух операндов. После реализации операции умножения полученные произведения g[15…0] передается на входы сумматоров DD14.3, DD14.4, DD14.5, DD14.6, DD14. Далее полученное произведение будет суммироваться. Сумматоры DD14.3, DD14.4, DD14.5, DD14.6 работают по принципу накапливающего сумматора. Результатом выполнения накапливающей суммы будет Σ1, которая предается на вход арифметико-логического устройства (АЛУ) (Фиг.13).

Для определения второй суммы Σ2 (Фиг.13) необходимо последовательно сложить все данные записанные в буферную схему DD13.1. Для этого программатор 19 устанавливает контакт W/R , блока DD13.1 в состояние логической единицы. На сумматор DD14.1 передаются младшие разряды сигнала f4[27…24] и сигнала суммы h[3…0] полученный на i-ой итерации, а на сумматор DD14.2 передаются старшие разряды сигнала f4[31…28] и сигнала суммы h[7…4] полученные на i-ой итерации. В качестве сумматоров DD14.1, DD14.2 используются цифровые схемы К555ИМ6. Результат суммирования, полученный на i-той операции, хранится в буферной схеме ОЗУ DD15.1. На выходе блока DD15.1 формируется сигнал h[7…0], который является вторым суммарным значением Σ2 и передается на вход АЛУ.

После определения двух суммарных значений Σ1, Σ2 в АЛУ, которое представляет собой цифровую схему арифметического делителя выполняется процедура деления первой суммы на вторую Σ1 и Σ2. Результат деления является выходным значением, полученным в ходе реализации нечетко-логического вывода и передается от БД 8 в ЦАП 18.

Способ управления охлаждением режущего инструмента при обработке

изделий на оборудовании с ЧПУ заключается в следующем.

Первым шагом способа является формирование входных переменных и

выходной переменной, которые рассчитываются в программаторе 19 и хранятся в БВИ 2 и БВВП 4 по формулам (6), (7), (8)

где U - первая входная переменная напряжение на элементе Пелтье 11, четкие значения напряжения находятся в диапазоне от 0 до 12 В,

где ΔT - вторая входная переменная разность температур в зоне резания на выходе блока разности 21, четкие значения разности температур находятся в диапазоне от 0 до 120 C,

где Uз – выходная переменная напряжение, передаваемое на затвор полевого транзистора 10, четкие значения напряжения находятся в диапазоне от 0 до 4,8 В.

Вторым шагом способа является фаззификация, при которой в зависимости от текущего значения напряжения на элементе Пельтье 10 U и разности температур в зоне резания на выходе блока разности 21 ΔT в зависимости от формулы (2) формируется фаззифицированный вектор значений для каждого терма функции принадлежности U и ΔT по формуле:

Третьим шагом способа является агрегации, при которой c помощью операции нечеткой логики «И» по формуле (3) выбирается минимальное значение из термов входных переменных и по формуле (2) находится вектор C(c1, c2, c3, c4, c5, c6, c7, c8, c9), который из БОСИ 3 по ШС[71…0] передается в БМНО 5.

Четвертым шагом способа является композиция, при которой по формуле (3) вычисляются новые значения d1, d2, d3, d4, d5 выходной величины напряжения, подаваемого на затвор полевого транзистора 10 в виде новых термов функций принадлежности, которые в свою очередь из БМНО 5 по ШБ[39…0] передаются в БУТВП 6.

Пятым шагом способа осуществляется усечение термов выходной переменной. С помощью операции нечеткой конъюнкции min (d1;y1), min (d2;y2), min (d3;y3), min (d4;y4), min (d5;y5) реализуется этап усечения термов функций принадлежности и формируется нечеткий вектор функции принадлежности e. Для его расчета в БУТВП 6 из БМНО 5 по ШБ[39…0] поступают новые значения d1, d2, d3, d4, d5, а из БВВП 4 по ШВ[39…0] передаются значения выходной функции принадлежности y1, y2, y3, y4, y5.

Графически результат усечения термов выходной переменой представлен на Фиг. 9.

Шестым шагом способа является аккумуляция, с помощью которой производится логическое объединение новых термов функции принадлежности e, и формирование нечеткого вектора функции принадлежности f, который из БОУТВП 7 по ШФ[7…0] и ШУ[9…0] передаются в БД 8. Графически результат объединения усеченных термов выходной переменной представлен на Фиг.11.

Седьмым шагом способа является дефаззификация, при котором нечеткий вектор функции принадлежностей f преобразуется в единственное четкое значение с помощью метода центра тяжести по формуле (5).

Рассмотрим пример расчета в нечетком контроллере 1 напряжения, передаваемого на затвор полевого транзистора 10. Пусть напряжение на элементе Пельтье 11 U=5В, а разность температур в зоне резания на выходе блока разности 21 ΔT=35◦C. Напряжение на затворе полевого транзистора 10 U3 с помощью представленного способа будет находиться следующим образом.

Шаг 1. На первом этапе в программаторе 19 рассчитываются значения степеней истинности функций принадлежности для входных и выходной переменной по формулам (6), (7), (8). Данные записываются в БВИ 2 и БВВП 4 (Фиг. 3, 4, 7).

Шаг 2. Фаззификация осуществляется в БВИ 2. В случае когда U=5 В и ΔT=35◦C, то вектор фаззификации значений для каждого терма входной функции принадлежности U и ΔT=35◦C определяется :

Тогда

Термы, имеющие нулевой результат, в дальнейших расчетах использоваться не будут.

Шаг 3. На этапе агрегации находится вектор C по формуле (2):

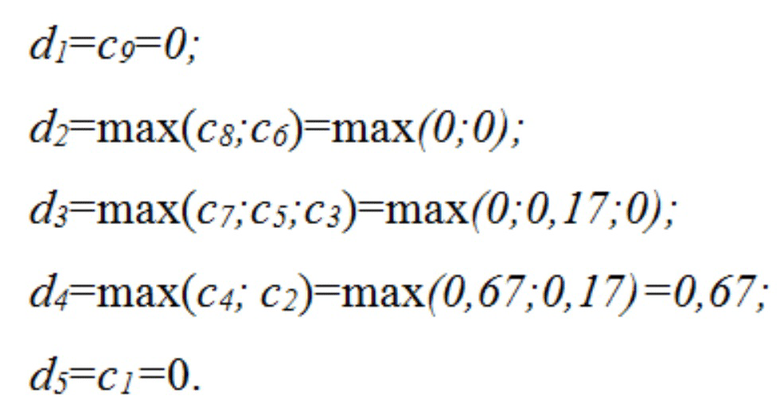

Шаг 4. На этапе композиции отбираются нечеткие правила, которые имеют пересечение. Это нечеткие правила с номерами 1, 2, 4, 5:

По формуле (3) нечеткой композиции определяется:

Шаг 5. На пятом этапе происходит усечение термов и формируется нечеткий вектор функций принадлежности е. Результат показан на Фиг.9.

Шаг 6. На шестом этапе осуществляется объединение усеченных термов выходной переменной. Графически данный результат представлен на Фиг.11.

Шаг 7. На этапе дефаззификации согласно формуле (5) вектор функции принадлежности f преобразуется в единственное четкое значение (Фиг.11). С целью упрощения вычислительной процедуры для расчета следует ограничиться четырьмя точками, для более точного вычисления количество точек нужно увеличить.

С помощью предложенного способа и реализующего его устройства в нечетком контроллере 1 осуществляется расчет нового значения напряжения, которое от нечеткого контроллера 1 передается на затвор полевого транзистора 10. В зависимости от рассчитанного напряжения изменяется ток стока полевого транзистора 10. Полевой транзистор 10 изменяет интенсивность охлаждения элемента Пельтье 11, это приводит к компенсации температурных деформаций, что в свою очередь увеличивает период стойкости режущего инструмента 12.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство и способ управления температурой в зоне резания | 2017 |

|

RU2676114C1 |

| Способ и устройство управления термоэлементом | 2020 |

|

RU2752492C1 |

| Быстродействующий дефаззификатор с использованием треугольных функций принадлежности | 2021 |

|

RU2759251C1 |

| Быстродействующий дефаззификатор с использованием треугольных функций принадлежности | 2020 |

|

RU2760632C1 |

| Способ и устройство мобильного робота для прохождения замкнутых контуров и лабиринтов | 2017 |

|

RU2670826C9 |

| Устройство преобразования напряжения для нечеткой системы управления охлаждением изделий | 2018 |

|

RU2712684C2 |

| Устройство дефаззификации на основе метода отношения площадей | 2018 |

|

RU2701841C1 |

| СПОСОБ РЕЗЕРВИРОВАНИЯ СИСТЕМ С ИСПОЛЬЗОВАНИЕМ МЕТОДОВ НЕЧЕТКОЙ ЛОГИКИ | 2014 |

|

RU2565417C1 |

| Регулятор с размытой логикой | 1988 |

|

SU1587466A1 |

| ОПТИЧЕСКИЙ ФАЗЗИФИКАТОР | 2010 |

|

RU2446431C1 |

Изобретение относится к области металлообработки и может быть использовано для управления охлаждением режущего инструмента при обработке изделий на оборудовании с ЧПУ. Способ включает перерасчет посредством нечеткого контроллера напряжения, подаваемого на затвор полевого транзистора для управления термоэлементом Пельтье при обработке изделия. На входы нечеткого контроллера подают напряжение на элементе Пельтье, полученное от датчика напряжения, и разность температуры на выходе блока разности и температуры в зоне резания, полученную от датчика температуры. При несовпадении измеренных значений напряжения и температуры с заданными регулируют интенсивность охлаждения режущего инструмента путем увеличения или уменьшения напряжения, подаваемого на затвор полевого транзистора с определением его величины при помощи девяти нечетких правил управления. Использование изобретения позволяет повысить точность управления охлаждением режущего инструмента и увеличить период его стойкости. 2 н.п. ф-лы, 13 ил.

1. Способ управления охлаждением режущего инструмента при обработке изделия на оборудовании с ЧПУ, включающий перерасчет напряжения, подаваемого на затвор полевого транзистора, подключенного к термоэлементу Пельтье, путем подачи на вход нечеткого контроллера двух входных переменных в виде напряжения на термоэлементе Пельтье, полученного от датчика напряжения и разности температур на выходе блока разности и в зоне резания, полученной от датчика температуры, при этом при несовпадении измеренных значений напряжения и температуры с заданными регулируют интенсивность охлаждения режущего инструмента путем увеличения или уменьшения напряжения UЗ, подаваемого на затвор полевого транзистора с определением его величины при помощи девяти нечетких правил управления (НПУ):

где U - входная переменная - напряжение на термоэлементе Пельтье;

ΔT - вторая входная переменная - разность температур в зоне резания на выходе блока разности,

по формуле

где U1…3 - численные значения входного напряжения на термоэлементе Пельтье;

ΔT1…3 - численные значения входной разности температур в зоне резания на выходе блока разности;

UЗ1…З5 - численные значения выходного напряжения, подаваемого на затвор полевого транзистора;

μ(UЗ)i - новые значения выходной величины напряжения, подаваемого на затвор полевого транзистора в виде новых термов функций принадлежности,

где i=1...k, k - количество термов выходной переменной (k=5).

2. Устройство для управления охлаждением режущего инструмента при обработке изделия на оборудовании с ЧПУ, содержащее термоэлемент Пельтье, резистор и компьютер, отличающееся тем, что оно снабжено аналого-цифровыми преобразователями, цифроаналоговым преобразователем, полевым транзистором, блоком питания, датчиком температуры, расположенным в зоне резания, датчиком напряжения, программатором, блоком разности, нечетким контроллером для перерасчета значения напряжения, подаваемого на затвор полевого транзистора в зависимости от нечетких правил управления, причем нечеткий контроллер включает в себя блок ввода информации, блок определения степеней истинности, блок ввода выходной переменной, блок усечения термов выходной переменной, блок объединения усеченных термов выходной переменной, блок дефаззификации, при этом выход датчика напряжения соединен с входом второго аналого-цифрового преобразователя, выход второго аналого-цифрового преобразователя соединен с первым входом блока ввода информации, выход датчика температуры соединен с входом первого аналого-цифрового преобразователя, выход аналого-цифрового преобразователя соединен с первым входом блока разности, а второй вход блока разности соединен с первым выходом программатора, причем выход блока разности соединен со вторым входом блока ввода информации, первый выход программатора подключен к третьему входу блока ввода информации, второй выход программатора подключен к входу блока ввода выходной переменной, третий выход программатора соединен с блоком усечения термов выходной переменной, четвертый выход программатора соединен с блоком объединения усеченных термов выходной переменной, а выход блока ввода информации соединен с входом блока определения степеней истинности, при этом выход блока определения степеней истинности соединен с входом блока матрицы нечетких отношений, выход которого соединен с первым входом блока усечения термов выходной переменной, второй вход блока усечения термов выходной переменной соединен с выходом блока ввода выходной переменой, а выход блока усечения термов выходной переменной соединен с входом блока объединения усеченных термов выходной переменной, причем выход блока объединения усеченных термов выходной переменной соединен с входом блока дефаззификации, выход которого соединен с входом цифроаналогового преобразователя, выход цифроаналогового преобразователя соединен с одним из выводов резистора, а его другой вывод соединен с затвором полевого транзистора, при этом исток полевого транзистора заземлен, сток полевого транзистора соединен с одним из выводов термоэлемента Пельтье, другой вывод которого соединен с блоком питания.

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ОХЛАЖДЕНИЕМ РЕЗЦА | 2014 |

|

RU2586189C2 |

| УСТРОЙСТВО ОХЛАЖДЕНИЯ РЕЖУЩЕГО ИНСТРУМЕНТА | 2011 |

|

RU2470757C2 |

| СПОСОБ И УСТРОЙСТВО ОХЛАЖДЕНИЯ РЕЖУЩЕГО ИНСТРУМЕНТА ДЛЯ ПОВЫШЕНИЯ ТОЧНОСТИ ПРИ ОБРАБОТКЕ ДЕТАЛЕЙ НА ОБОРУДОВАНИИ С ЧПУ | 2011 |

|

RU2486992C2 |

| УСТРОЙСТВО ВЫСОКОТОЧНОЙ ОБРАБОТКИ ДЕТАЛЕЙ НА ОБОРУДОВАНИИ ЧПУ | 2005 |

|

RU2280540C1 |

| JP 2003266209 A, 24.09.2003 | |||

| CN 101797704 A, 11.08.2010. | |||

Авторы

Даты

2019-12-16—Публикация

2018-05-10—Подача