ОБЛАСТЬ ТЕХНИКИ

[0001] Раскрытые варианты осуществления относятся в целом к нейронным сетям и, в частности, к системам и способам для аппаратной реализации нейронных сетей.

УРОВЕНЬ ТЕХНИКИ

[0002] Обычное аппаратное обеспечение не успевает за инновациями в нейронных сетях и растущей популярностью приложений на основе машинного обучения. Сложность нейронных сетей продолжает опережать вычислительные мощности CPU и GPU, поскольку улучшения цифровых микропроцессоров стабилизируются. Нейроморфные процессоры, основанные на пиковых нейронных сетях, такие как Loihi и True North, ограничены их приложениями. Применительно к GPU-подобным архитектурам, мощность и скорость таких архитектур ограничиваются скоростью передачи данных. Передача данных может потреблять вплоть до 80% мощности чипа и может существенно повлиять на скорость вычислений. Граничные приложения требуют низкого энергопотребления, но в настоящий момент отсутствуют известные высокопроизводительные аппаратные варианты осуществления, которые потребляют меньше 50 милливатт энергии.

[0003] Архитектуры на основе мемристоров, которые используют технологию кроссбара, остаются непрактичными для изготовления рекуррентных нейронных сетей и нейронных сетей с прямой связью. Например, кроссбары на основе мемристоров обладают некоторым количеством недостатков, включая высокое время ожидания и утечку токов во время работы, которые делают их непрактичными. Также присутствуют проблемы надежности при изготовлении кроссбаров на основе мемристоров, в частности, когда нейронные сети имеют как отрицательные, так и положительные весовые коэффициенты. Применительно к большим нейронным сетям со множеством нейронов, при больших размерах, кроссбары на основе мемристоров не могут быть использованы для одновременного распространения разных сигналов, что в свою очередь усложняет суммирование сигналов, когда нейроны представлены посредством операционных усилителей. Кроме того, аналоговые интегральные микросхемы на основе мемристоров обладают некоторым количеством ограничений, такими как небольшое количество резистивных состояний, проблема первого цикла при формировании мемристоров, сложность с формированием канала при обучении мемристоров, непредсказуемая зависимость от размеров мемристоров, медленная работа мемристоров и дрейф состояния сопротивления.

[0004] Дополнительно, процесс обучения, который требуется для нейронных сетей, представляет уникальные проблемы для аппаратной реализации нейронных сетей. Обученная нейронная сеть используется для конкретных задач логического вывода, таких как классификация. Как только нейронная сеть обучена, изготавливается аппаратный эквивалент. При переобучении нейронной сети, процесс изготовления аппаратного обеспечения повторяется, приводя к росту затрат. Несмотря на то, что существуют некоторые реконфигурируемые аппаратные решения, такое аппаратное обеспечение не может быть легко произведено серийно, и стоит много больше (например, стоит в 5 раз больше) аппаратного обеспечения, которое не является реконфигурируемым. Кроме того, граничные среды, такие как приложения умного дома, не требуют перепрограммирования как такового. Например, 85% всех приложений нейронных сетей не требуется какого-либо переобучения во время работы, так что обучение на-чипе не такое уж и используемое. Кроме того, граничные приложения включают в себя шумные среды, что может привести к тому, что перепрограммируемое аппаратное обеспечение станет ненадежным.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0005] Соответственно, существует потребность в способах, схемах и/или интерфейсах, которые решают по меньшей мере некоторые из недостатков, идентифицированных выше. Аналоговые схемы, которые моделируют обученные нейронные сети и изготавливаются в соответствии с методиками, описанными в данном документе, могут обеспечивать преимущества улучшенной производительности из расчета на ватт, могут быть полезны при реализации аппаратных решений в граничных средах, и могут поддерживать многообразие приложений, таких как навигация дронов и автономные автомобили. Преимущества в затратах, которые предоставляются предложенными способами изготовления и/или аналоговыми сетевыми архитектурами, еще более выражены при использовании больших нейронных сетей. Также аналоговые аппаратные варианты осуществления нейронных сетей обеспечивают улучшенный параллелизм и нейроморфизм. Более того, нейроморфные аналоговые компоненты нечувствительны к шуму и температурным изменениям в сравнении с цифровыми аналогами.

[0006] Чипы, изготовленные в соответствии с методиками, описанными в данном документе, обеспечивают улучшения на порядок в сравнении с обычными системами по размеру, мощности и производительности, и являются идеальными для граничных сред, включая для целей переобучения. Такие аналоговые нейроморфные чипы могут быть использованы для реализации граничных вычислительных приложений или в средах Интернет-Вещей (IoT). Благодаря аналоговому аппаратному обеспечению, первоначальная обработка (например, формирование дескрипторов для распознавания изображений), которая может потреблять около 80-90% энергии, может быть перемещена в чип, тем самым уменьшая потребление энергии и нагрузку на сеть, что может открыть новые рынки для приложений.

[0007] Различные граничные приложения могут получать выгоду от использования такого аналогового аппаратного обеспечения. Например, применительно к видеообработке, методики, описанные в данном документе, могут быть использованы, чтобы включать непосредственное соединение с датчиком CMOS без цифрового интерфейса. Различные другие приложения видеообработки включают в себя распознавание дорожных знаков для автомобилей, фактическую глубину на основе камеры и/или одновременную локализацию и отображение для роботов, управление доступом в помещение без соединения с сервером и постоянные решения для обеспечения безопасности и здравоохранения. Такие чипы могут быть использованы для обработки данных с радаров и лидаров, и для низкоуровневого слияния данных. Такие методики могут быть использованы для реализации функций управления батареями для больших батарейных блоков, обработки звука/голоса без соединения с центрами обработки данных, распознавания голоса в мобильных устройствах, речевых инструкций пробуждения для IoT датчиков, переводчиков, которые переводят с одного языка на другой, больших массивов датчиков в IoT с низкой интенсивностью сигнала и/или конфигурируемого управления процессом с сотнями датчиков.

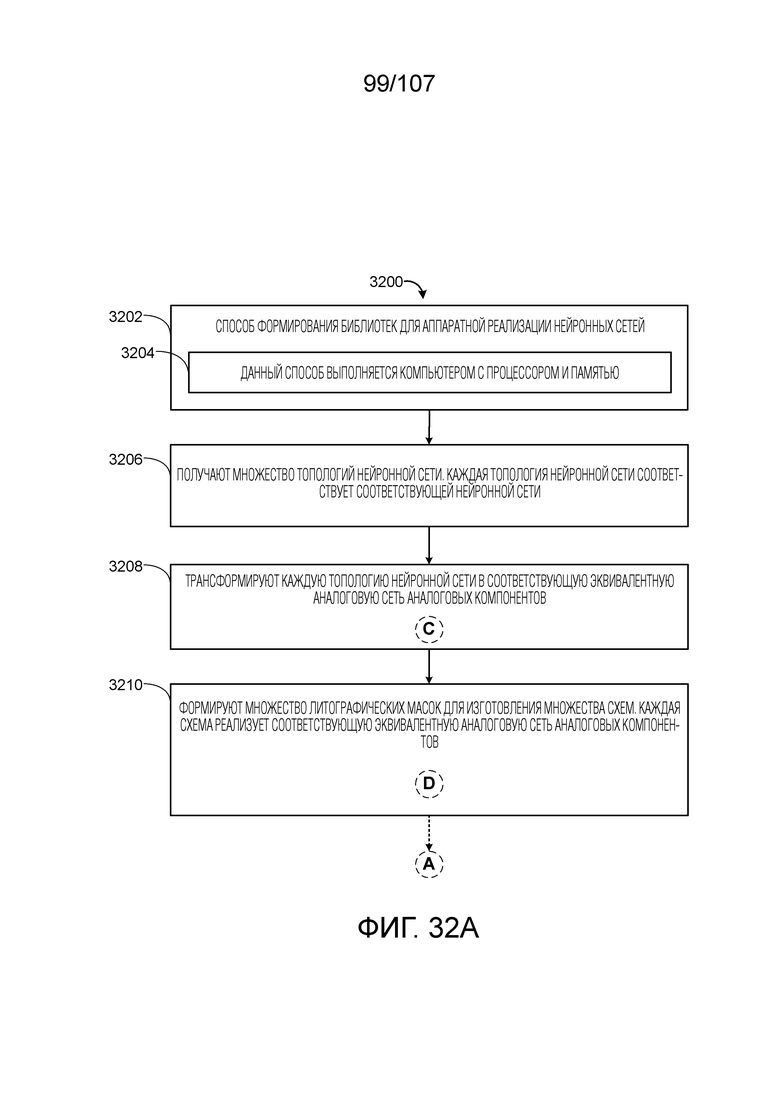

[0008] Нейроморфные аналоговые чипы могут быть произведены серийно после стандартных моделирований/обучения нейронных сетей на основе программного обеспечения, в соответствии с некоторыми вариантами осуществления. Клиентские нейронные сети могут быть легко перенесены, независимо от структуры нейронной сети, с помощью специализированной конструкции и производства чипа. Более того, библиотека готовых решений на-чипе (сетевые эмуляторы) предоставляются в соответствии с некоторыми вариантами осуществления. Таким решениям требуется только обучение, одно изменение литографической маски, вслед за чем чипы могут быть произведены серийно. Например, при производстве чипа, требуется изменение только части литографических масок.

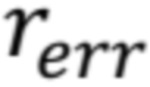

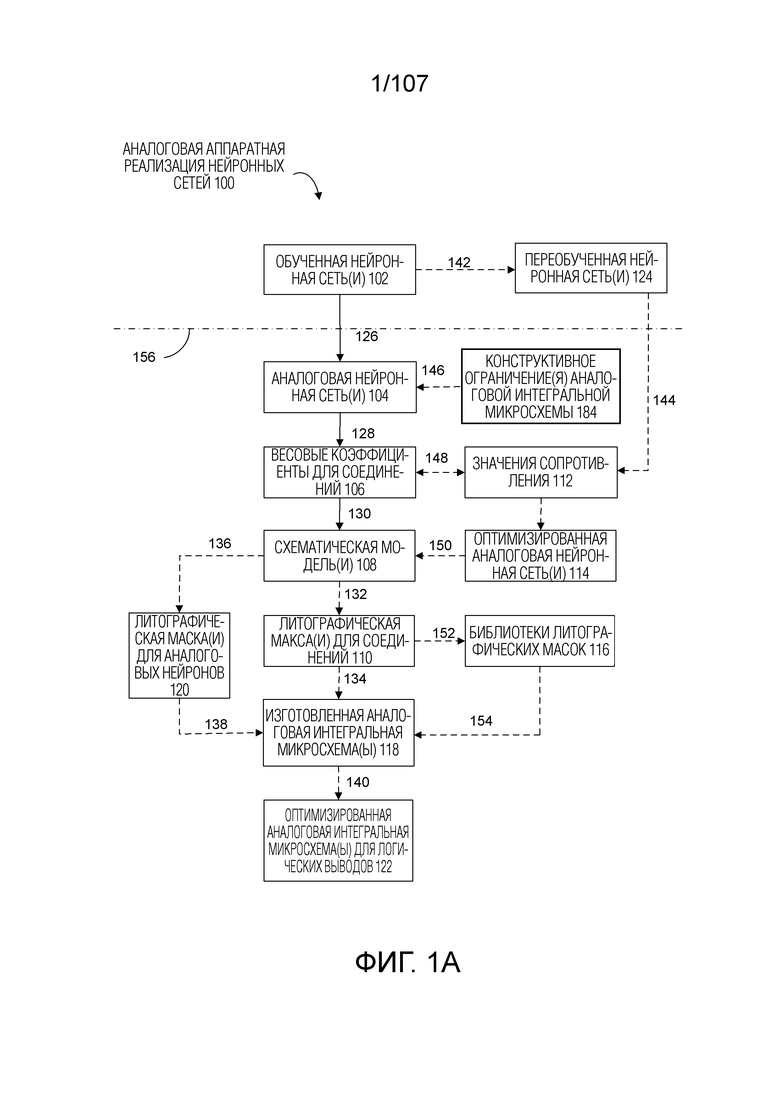

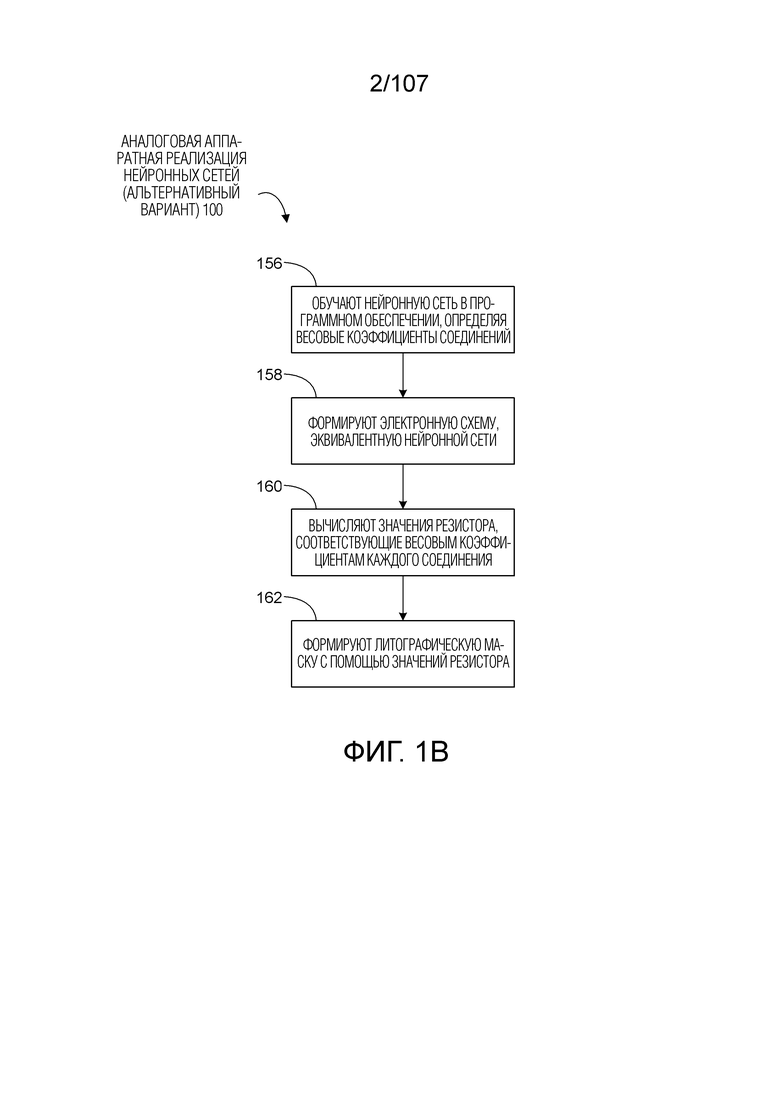

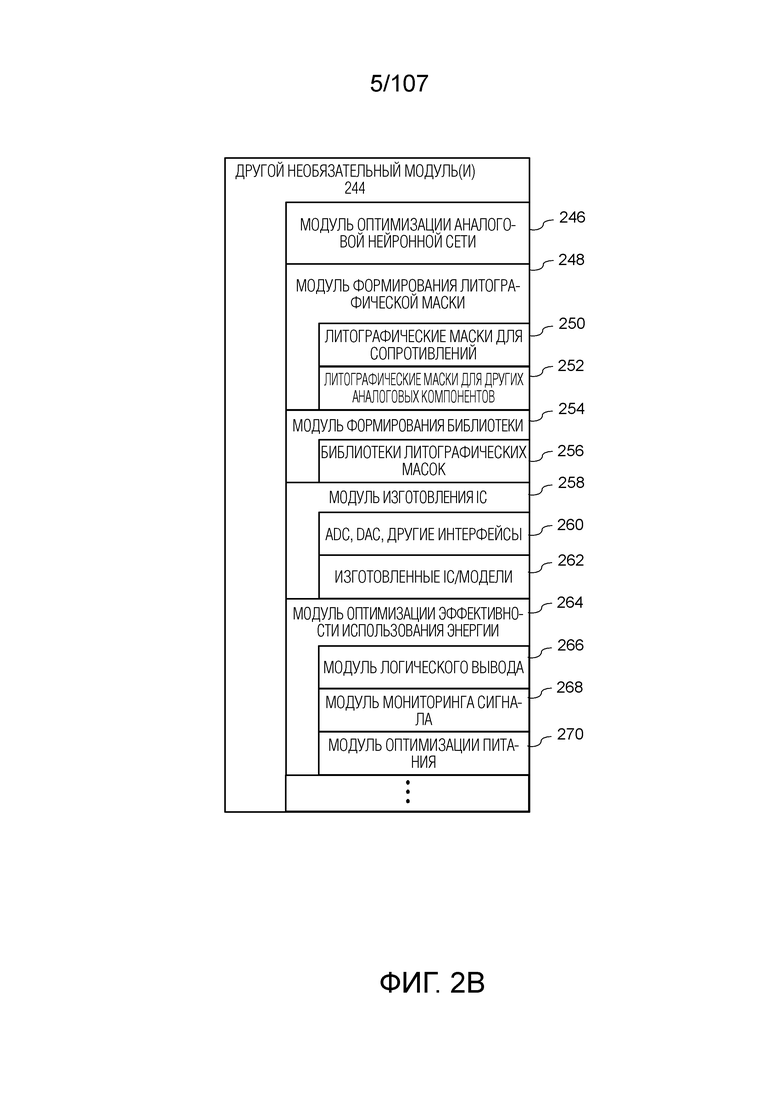

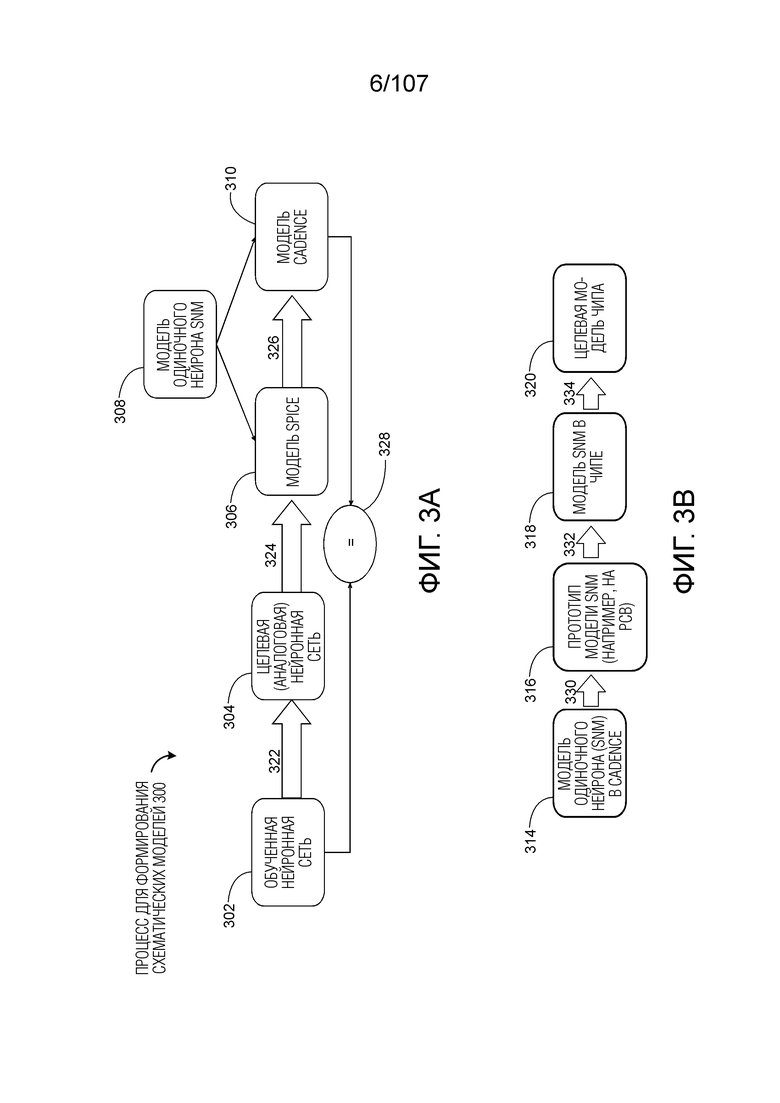

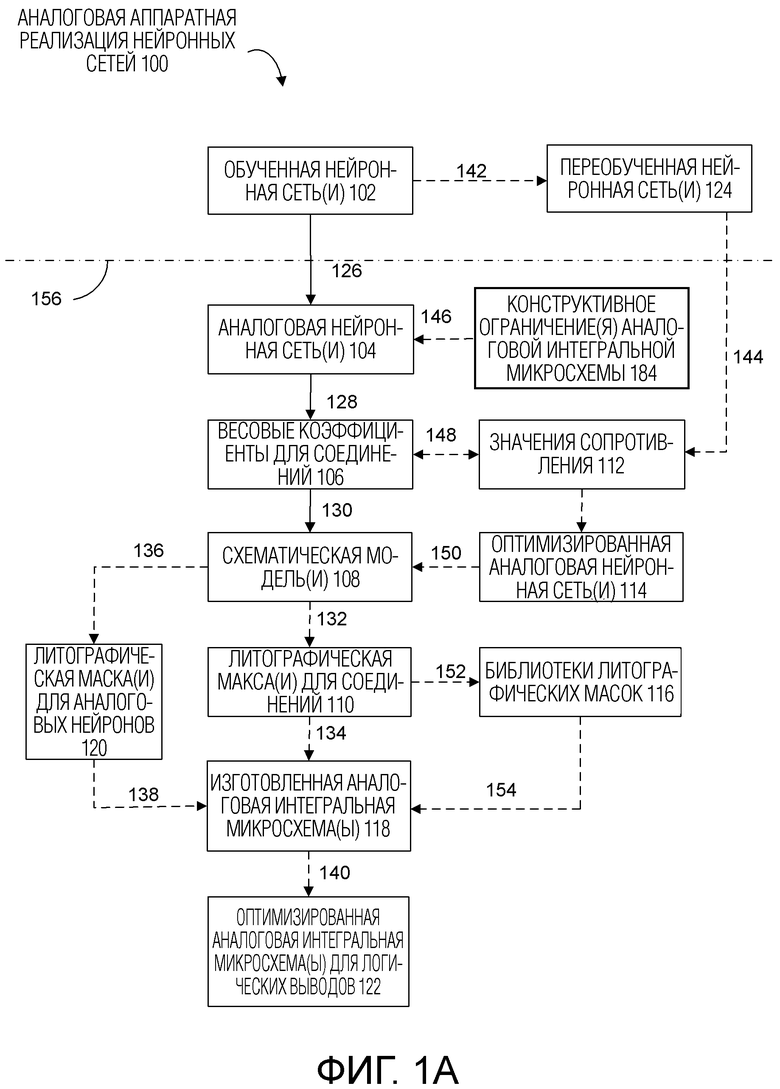

[0009] Методики, описанные в данном документе, могут быть использованы для конструкции и/или изготовления аналоговой нейроморфной интегральной микросхемы, которая является математически эквивалентной обученной нейронной сети (либо нейронной сети с прямой связью, либо рекуррентной нейронной сети). В соответствии с некоторыми вариантами осуществления, процесс начинается с обученной нейронной сети, которая сначала преобразуется в трансформированную сеть, состоящую из стандартных элементов. Работа трансформированной сети моделируется с использованием программного обеспечения с помощью известных моделей, представляющих собой стандартные элементы. Программное моделирование используется для определения отдельных значений сопротивления для каждого из резисторов в трансформированной сети. Литографические маски компонуются на основе расстановки стандартных элементов в трансформированной сети. Каждый из стандартных элементов компонуется в максах с использованием существующей библиотеки схем, соответствующих стандартным элементам, чтобы упростить и ускорить процесс. В некоторых вариантах осуществления, резисторы компонуются в одной или нескольких масках отдельно от масок, включающих в себя другие элементы (например, операционные усилители) в трансформированной сети. Таким образом, если нейронная сеть переобучается, то требуется обновление только масок, содержащих резисторы, или другие типы элементов с фиксированным сопротивлением, представляющие собой новые весовые коэффициенты в переобученной нейронной сети, что упрощает и ускоряет процесс. Литографические маски затем отправляются на фабрику для изготовления аналоговой нейроморфной интегральной микросхемы.

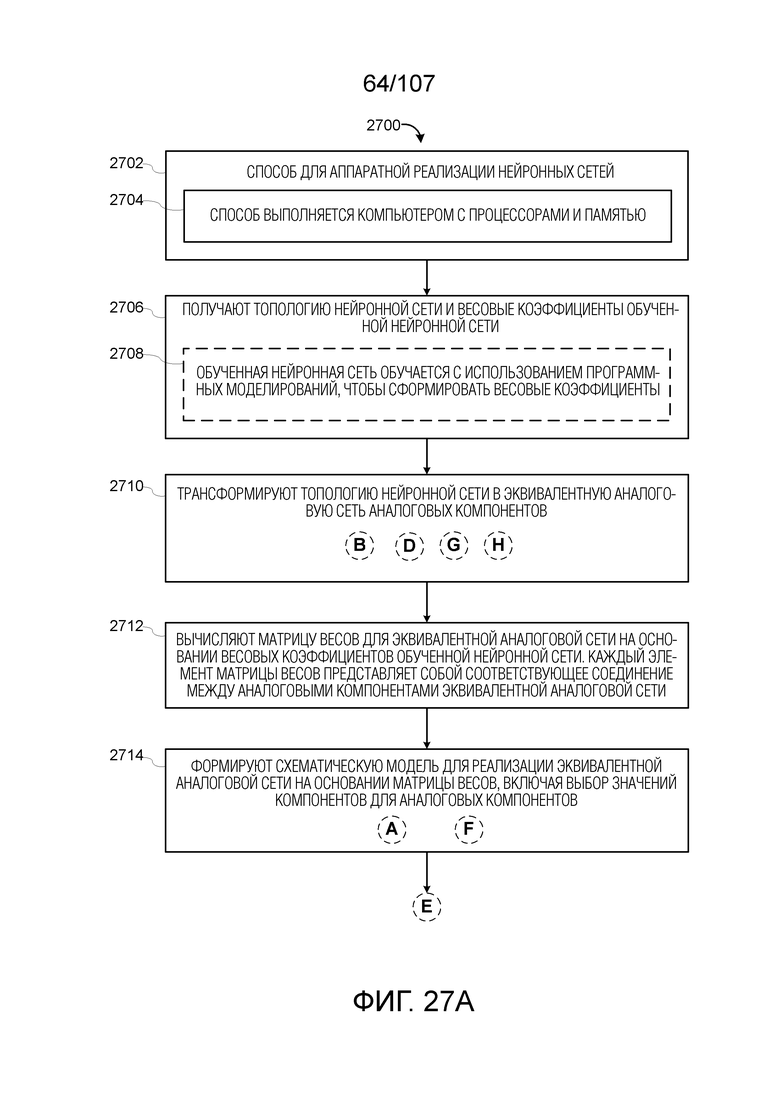

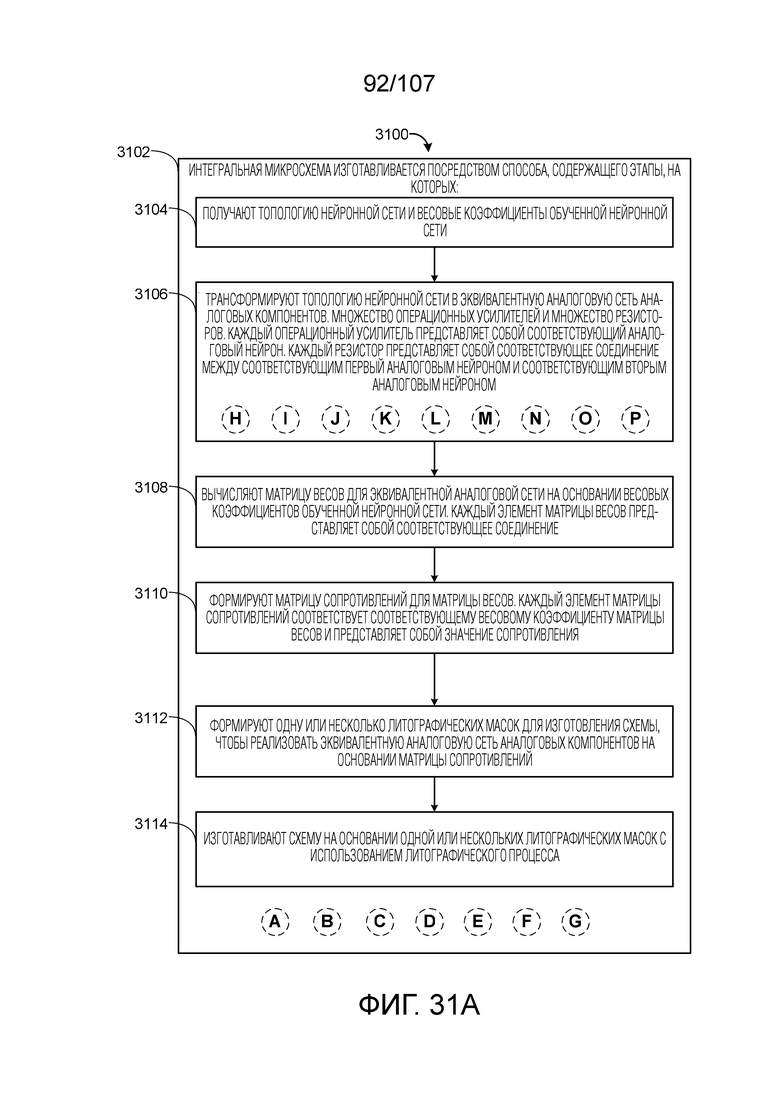

[0010] В одном аспекте, предоставляется способ для аппаратной реализации нейронных сетей, в соответствии с некоторыми вариантами осуществления. Способ включает в себя этап, на котором получают топологию нейронной сети и весовые коэффициенты обученной нейронной сети. Способ также включает в себя этап, на котором трансформируют топологию нейронной сети в эквивалентную аналоговую сеть аналоговых компонентов. Способ также включает в себя этап, на котором вычисляют матрицу весов для эквивалентной аналоговой сети на основе весовых коэффициентов обученной нейронной сети. Каждый элемент матрицы весов представляет собой соответствующее соединение между аналоговыми компонентами эквивалентной аналоговой сети. Способ также включает в себя этап, на котором формируют схематическую модель для реализации эквивалентной аналоговой сети на основе матрицы весов, включая выбор значений компонентов для аналоговых компонентов.

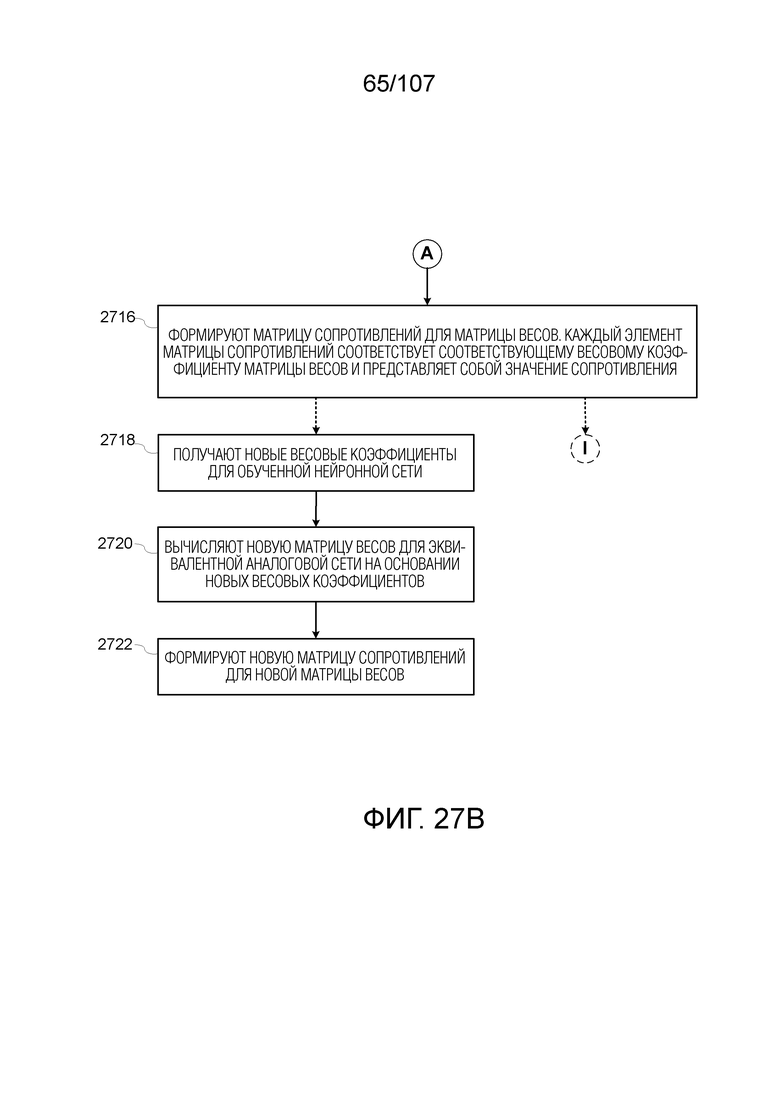

[0011] В некоторых вариантах осуществления, этап, на котором формируют схематическую модель, включает в себя этап, на котором формируют матрицу сопротивлений для матрицы весов. Каждый элемент матрицы сопротивлений соответствует соответствующему весовому коэффициенту матрицы весов и представляет собой значение сопротивления.

[0012] В некоторых вариантах осуществления, способ дополнительно включает в себя этапы, на которых: получают новые весовые коэффициенты для обученной нейронной сети, вычисляют новую матрицу весов для эквивалентной аналоговой сети на основе новых весовых коэффициентов, и формируют новую матрицу сопротивлений для новой матрицы весов.

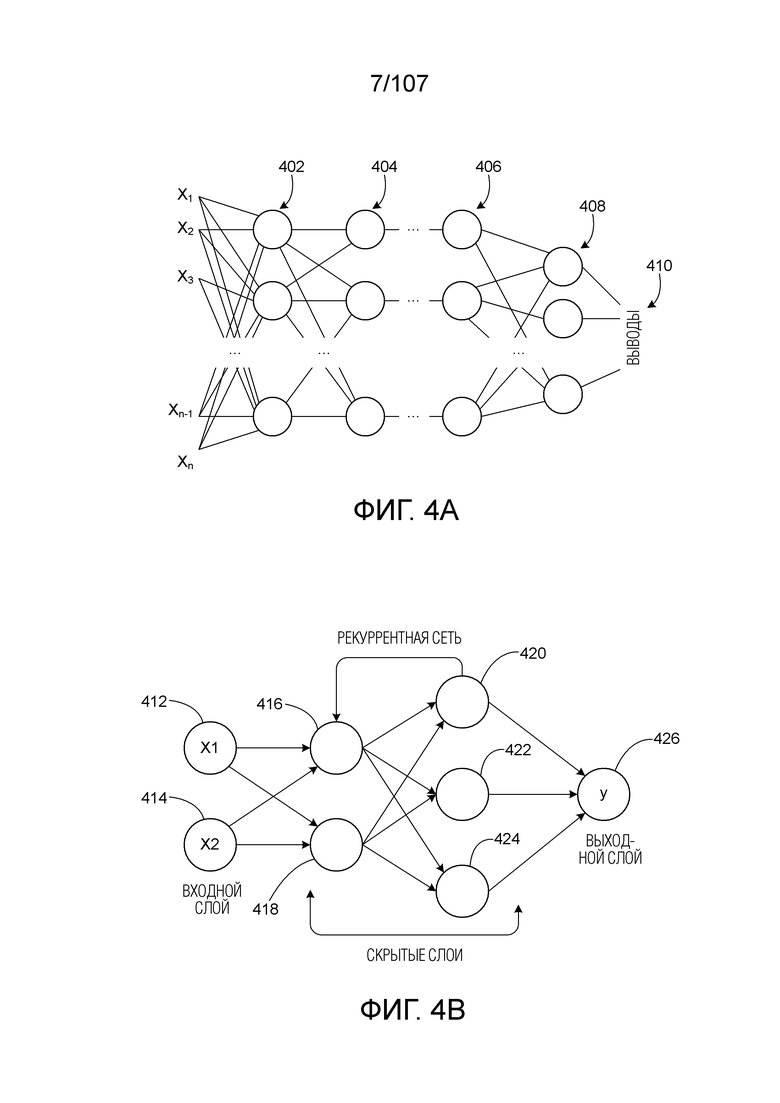

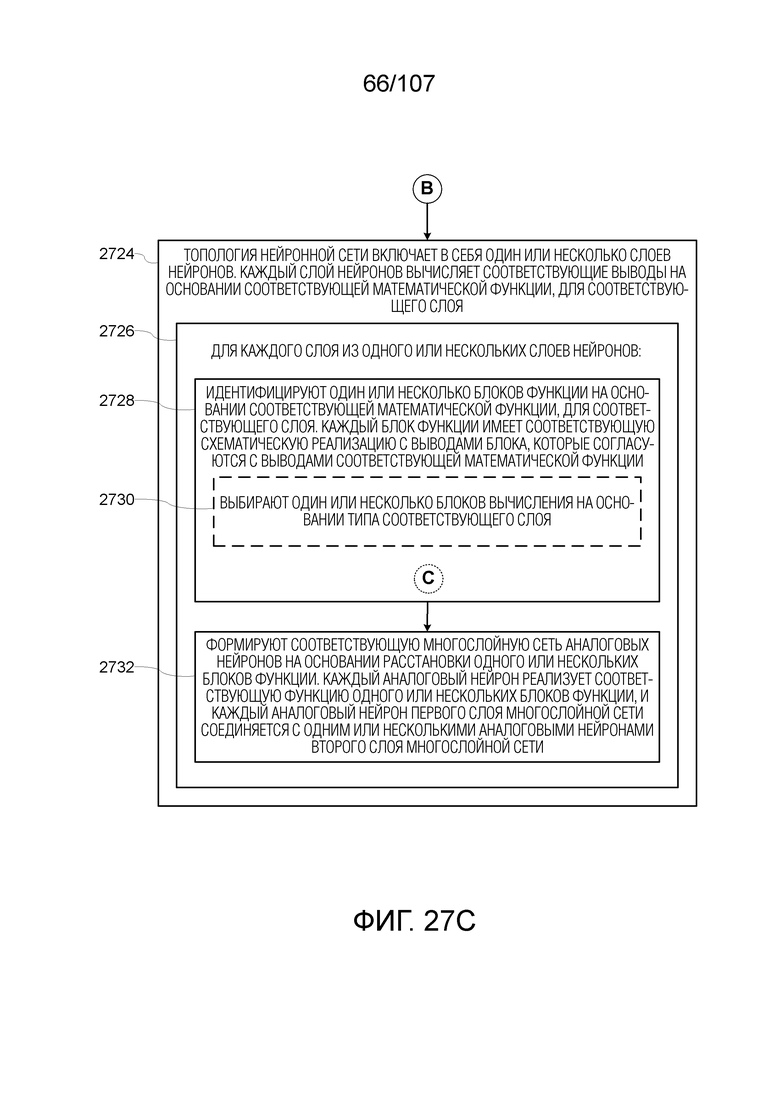

[0013] В некоторых вариантах осуществления, топология нейронной сети включает в себя один или несколько слоев нейронов, причем слой нейронов вычисляет соответствующие выводы на основе соответствующей математической функции, и этап, на котором трансформируют топологию нейронной сети в эквивалентную аналоговую сеть аналоговых компонентов, включает в себя этапы, на которых: для каждого слоя из одного или нескольких слоев нейронов: (i) идентифицируют один или несколько блоков функции на основе соответствующей математической функции, для соответствующего слоя. Каждый блок функции имеет соответствующую схематическую реализацию с выводами блока, которые согласуются с выводами соответствующей математической функции; и (ii) формируют соответствующую многослойную сеть аналоговых нейронов на основе расстановки одного или нескольких блоков функции. Каждый аналоговый нейрон реализует соответствующую функцию одного или нескольких блоков функции, и каждый аналоговый нейрон первого слоя многослойной сети соединяется с одним или несколькими аналоговыми нейронами второго слоя многослойной сети.

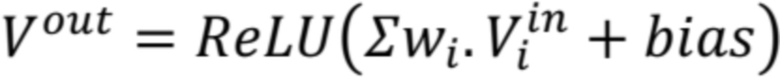

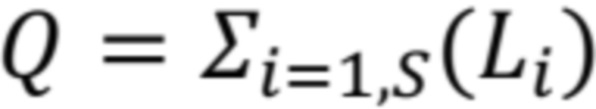

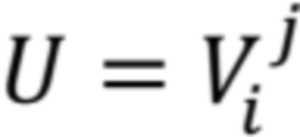

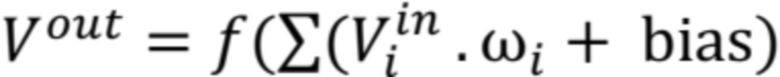

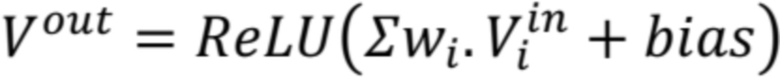

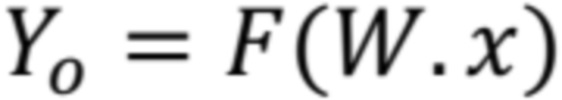

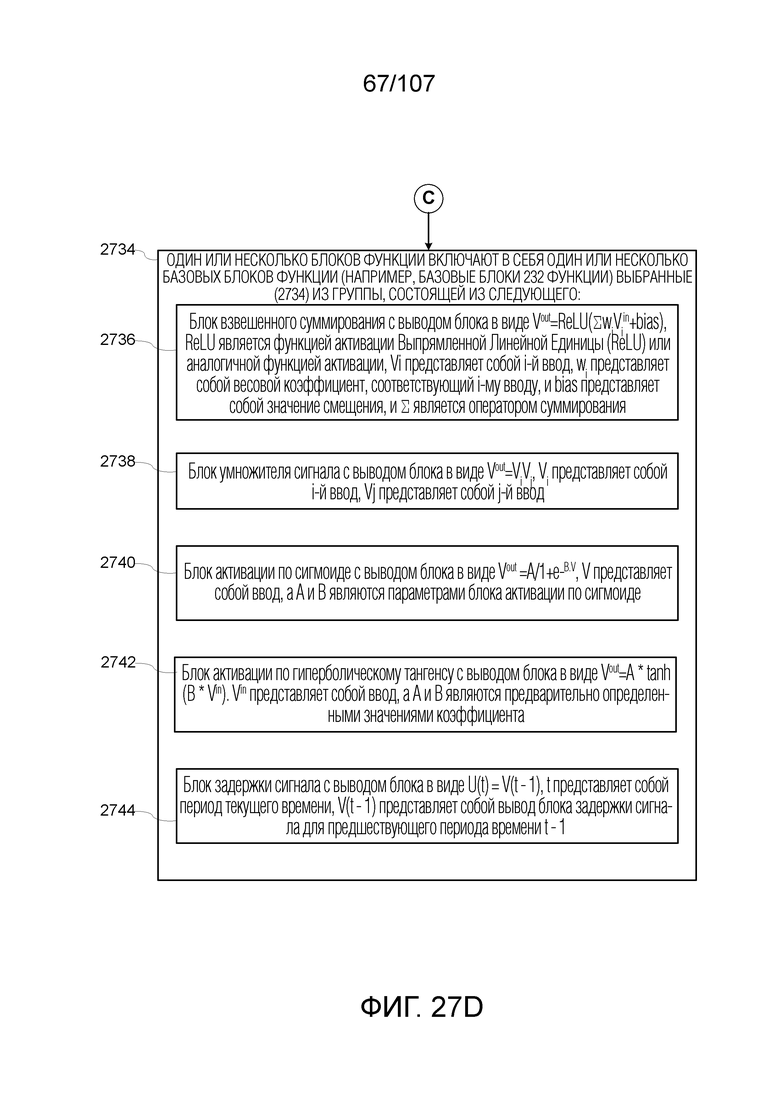

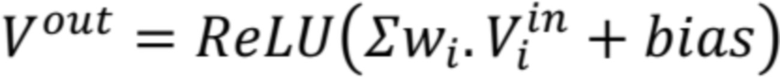

[0014] В некоторых вариантах осуществления, один или несколько блоков функции включают в себя один или несколько базовых блоков функции, выбранных из группы, состоящей из следующего: (i) блок взвешенного суммирования с выводом блока в виде  .

.  является функцией активации Выпрямленной Линейной Единицы (ReLU) или аналогичной функцией активации,

является функцией активации Выпрямленной Линейной Единицы (ReLU) или аналогичной функцией активации,  представляет собой i-й ввод,

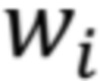

представляет собой i-й ввод,  представляет собой весовой коэффициент, соответствующий i-му вводу, и

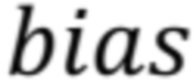

представляет собой весовой коэффициент, соответствующий i-му вводу, и  представляет собой значение смещения, и

представляет собой значение смещения, и  является оператором суммирования; (ii) блок умножителя сигнала с выводом блока в виде

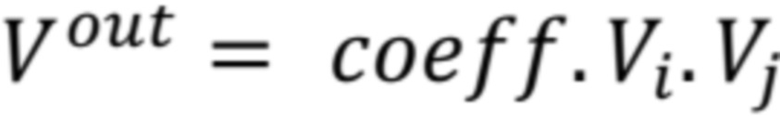

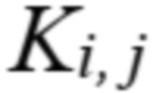

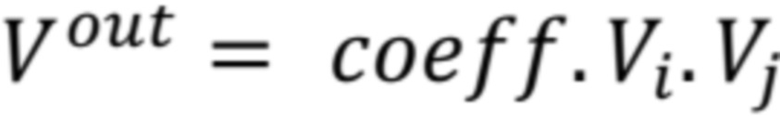

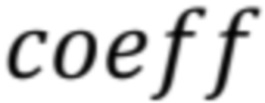

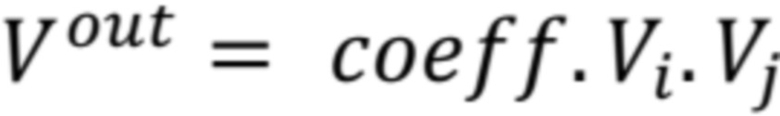

является оператором суммирования; (ii) блок умножителя сигнала с выводом блока в виде  .

.  представляет собой i-й ввод,

представляет собой i-й ввод,  представляет собой j-й ввод, а

представляет собой j-й ввод, а  является предварительно определенным коэффициентом; (iii) блок активации по сигмоиде с выводом блока в виде

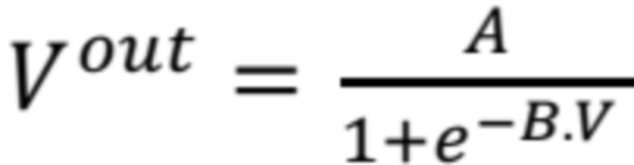

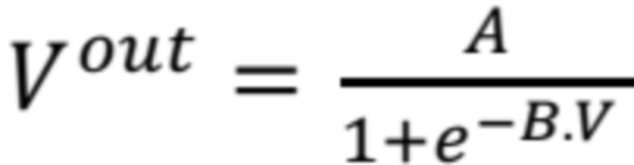

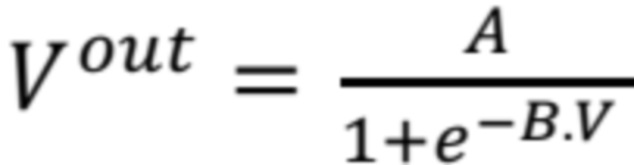

является предварительно определенным коэффициентом; (iii) блок активации по сигмоиде с выводом блока в виде  .

.  представляет собой ввод, а A и B являются предварительно определенными значениями коэффициента блока активации по сигмоиде; (iv) блок активации по гиперболическому тангенсу с выводом блока в виде

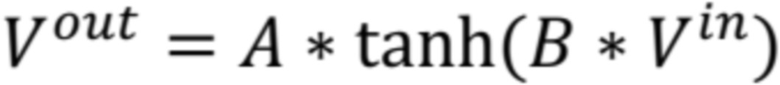

представляет собой ввод, а A и B являются предварительно определенными значениями коэффициента блока активации по сигмоиде; (iv) блок активации по гиперболическому тангенсу с выводом блока в виде  .

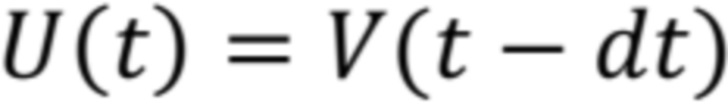

.  представляет собой ввод, а A и B являются предварительно определенными значениями коэффициента; и (v) блок задержки сигнала с выводом блока в виде

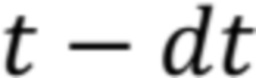

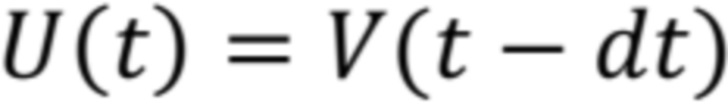

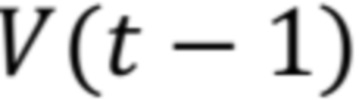

представляет собой ввод, а A и B являются предварительно определенными значениями коэффициента; и (v) блок задержки сигнала с выводом блока в виде  .

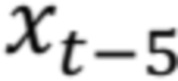

.  представляет собой период текущего времени,

представляет собой период текущего времени,  представляет собой вывод блока задержки сигнала для предшествующего периода времени

представляет собой вывод блока задержки сигнала для предшествующего периода времени  , а

, а  является значением задержки.

является значением задержки.

[0015] В некоторых вариантах осуществления этап, на котором идентифицируют один или несколько блоков функции, включает в себя этап, на котором выбирают один или несколько блоков функции на основе типа соответствующего слоя.

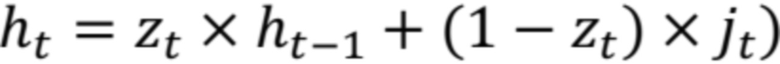

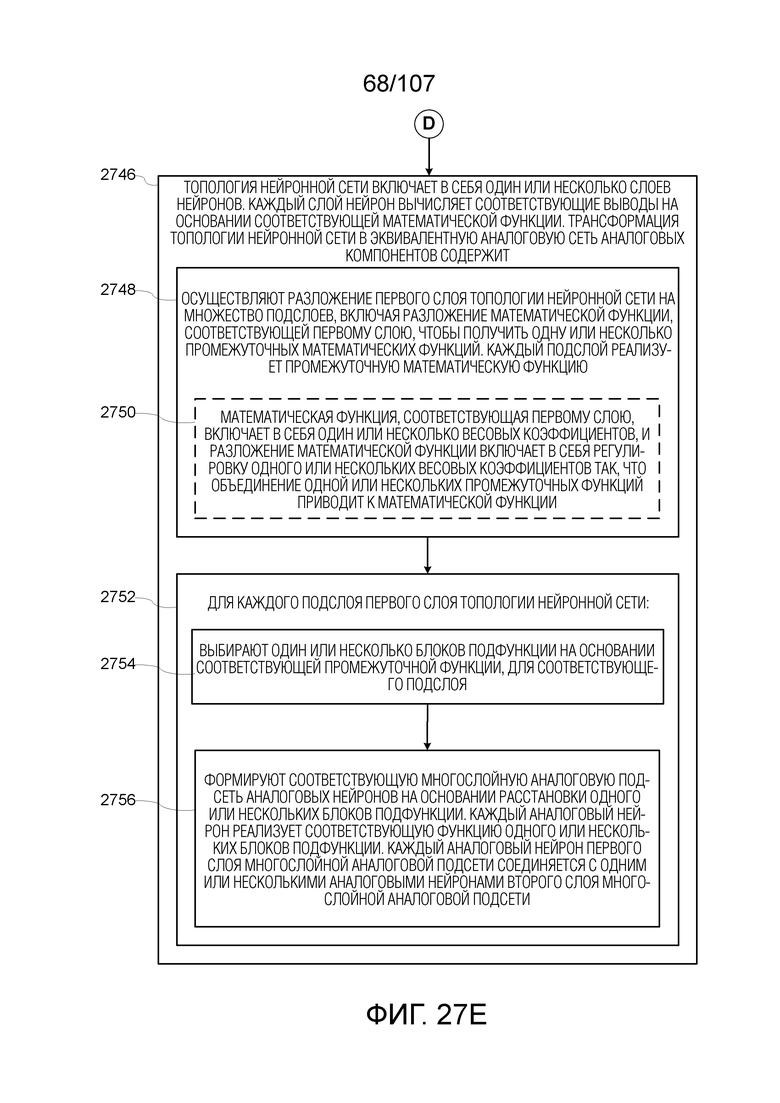

[0016] В некоторых вариантах осуществления, топология нейронной сети включает в себя один или несколько слоев нейронов, причем каждый слой нейронов вычисляет соответствующие выводы на основе соответствующей математической функции, и этап, на котором трансформируют топологию нейронной сети в эквивалентную аналоговую сеть аналоговых компонентов, включает в себя этапы, на которых: (i) осуществляют разложение первого слоя топологии нейронной сети на множество подслоев, включая разложение математической функции, соответствующей первому слою, чтобы получить одну или несколько промежуточных математических функций. Каждый подслой реализует промежуточную математическую функцию; и (ii) для каждого подслоя первого слоя топологии нейронной сети: (a) выбирают один или несколько блоков подфункции на основе соответствующей промежуточной математической функции, для соответствующего подслоя; и (b) формируют соответствующую многослойную аналоговую подсеть аналоговых нейронов на основе расстановки одного или нескольких блоков подфункции. Каждый аналоговый нейрон реализует соответствующую функцию одного или нескольких блоков подфункции, и каждый аналоговый нейрон первого слоя многослойной аналоговой подсети соединяется с одним или несколькими аналоговыми нейронами второго слоя многослойной аналоговой подсети.

[0017] В некоторых вариантах осуществления, математическая функция, соответствующая первому слою, включает в себя один или несколько весовых коэффициентов, и этап, на котором осуществляют разложение математической функции, включает в себя этап, на котором регулируют один или несколько весовых коэффициентов так, что объединение одной или нескольких промежуточных функций приводит к математической функции.

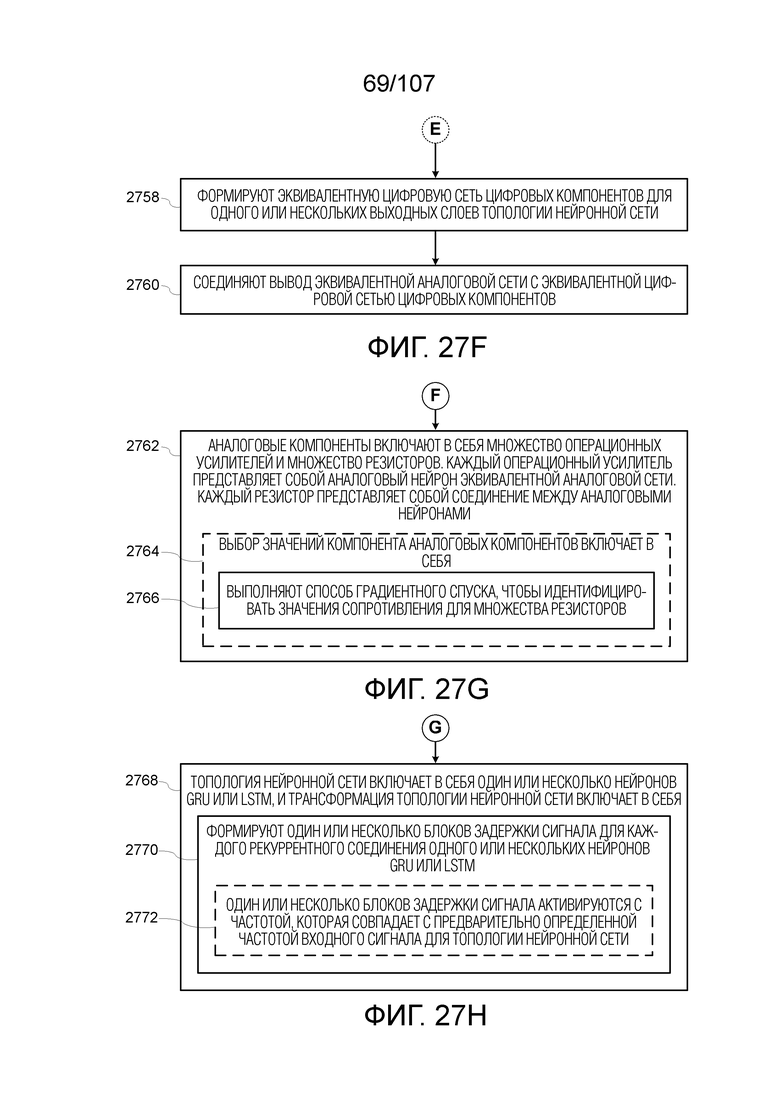

[0018] В некоторых вариантах осуществления, способ дополнительно включает в себя этапы, на которых: (i) формируют эквивалентную цифровую сеть цифровых компонентов для одного или нескольких выходных слоев топологии нейронной сети; и (ii) соединяют вывод одного или нескольких слоев эквивалентной аналоговой сети с эквивалентной цифровой сетью цифровых компонентов.

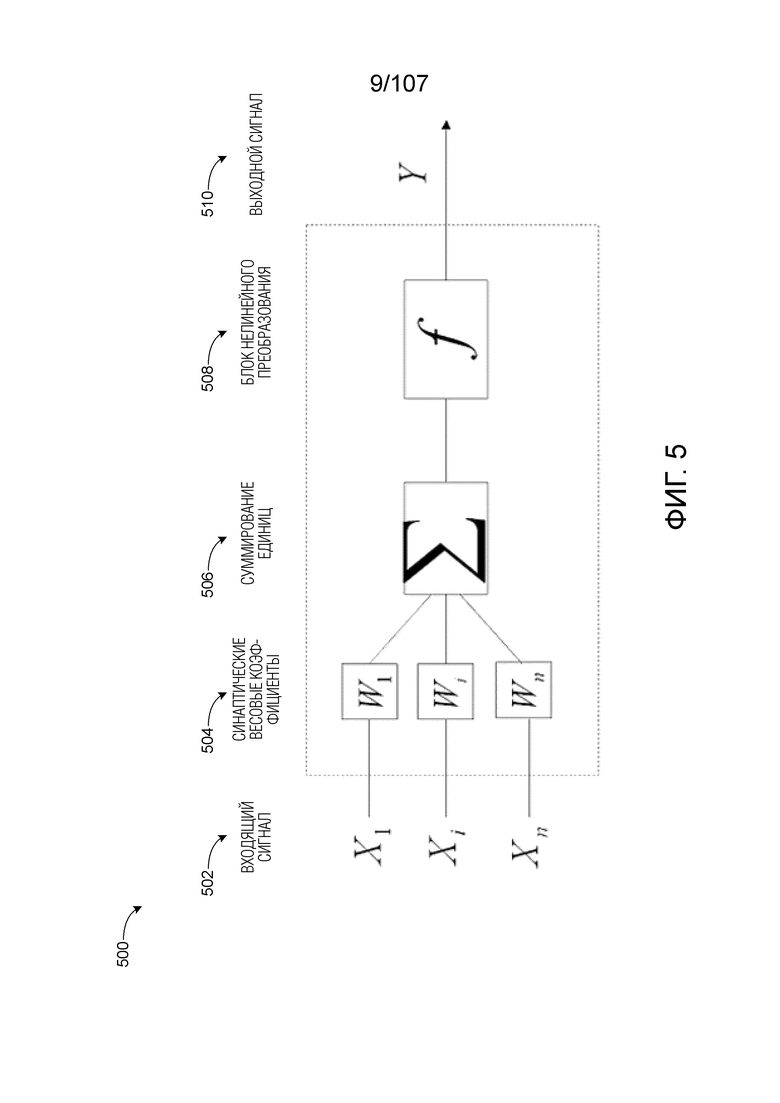

[0019] В некоторых вариантах осуществления, аналоговые компоненты включают в себя множество операционных усилителей и множество резисторов, причем каждый операционный усилитель представляет собой аналоговый нейрон эквивалентной аналоговой сети, а каждый резистор представляет собой соединение между аналоговыми нейронами.

[0020] В некоторых вариантах осуществления, этап, на котором выбирают значения компонента аналоговых компонентов, включает в себя этап, на котором выполняют способ градиентного спуска, чтобы идентифицировать возможные значения сопротивления для множества резисторов.

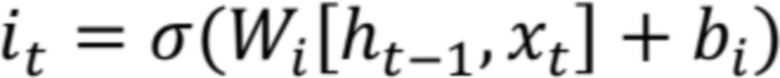

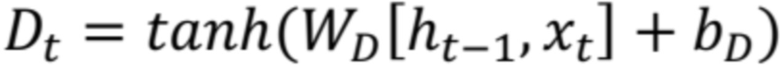

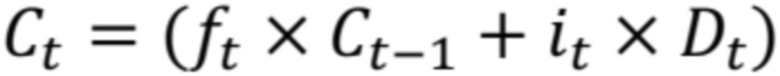

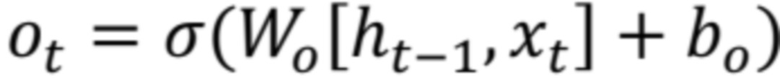

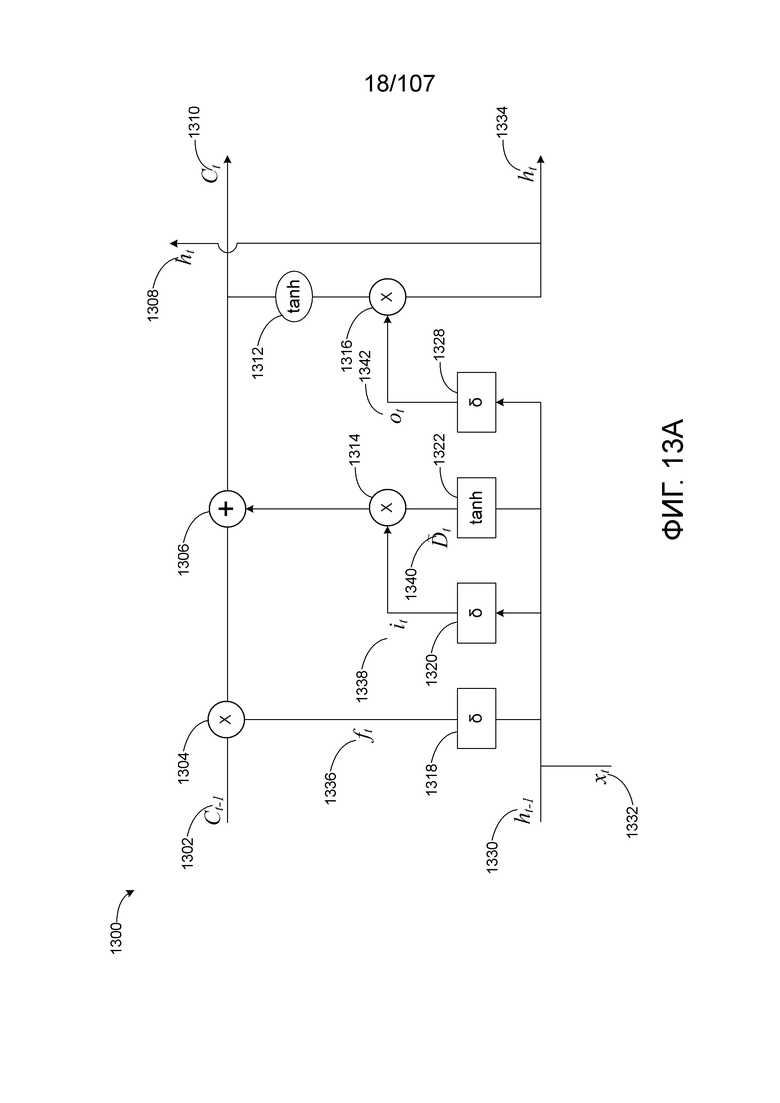

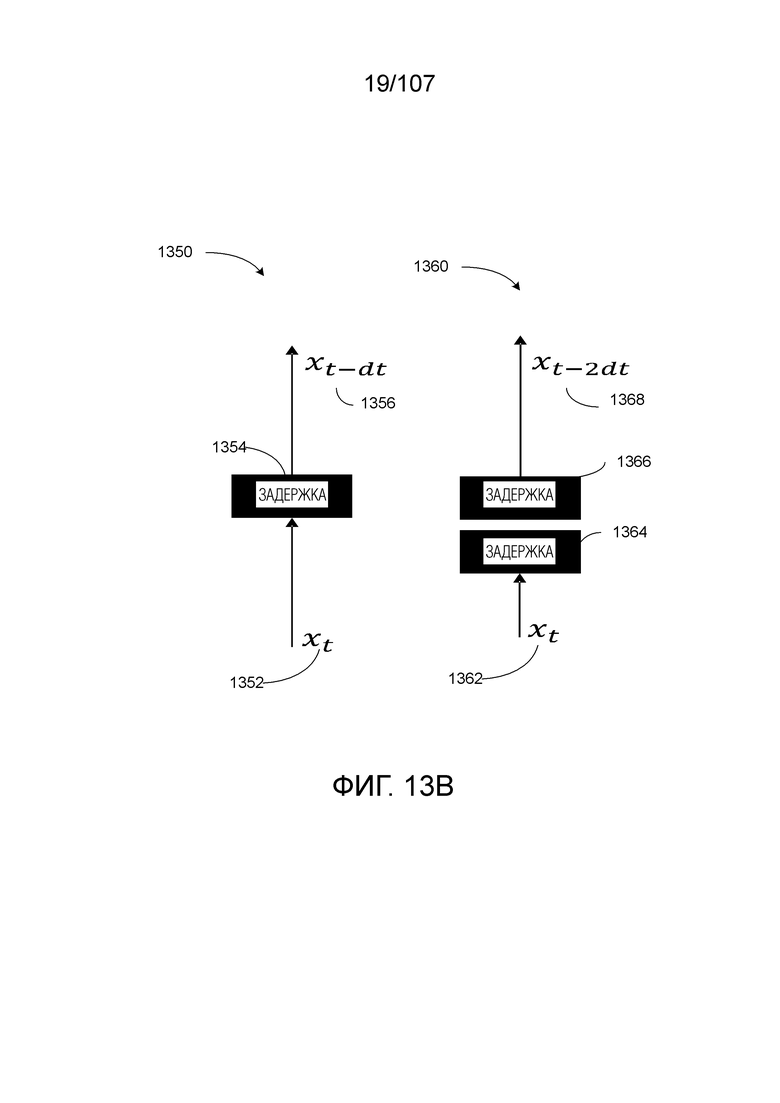

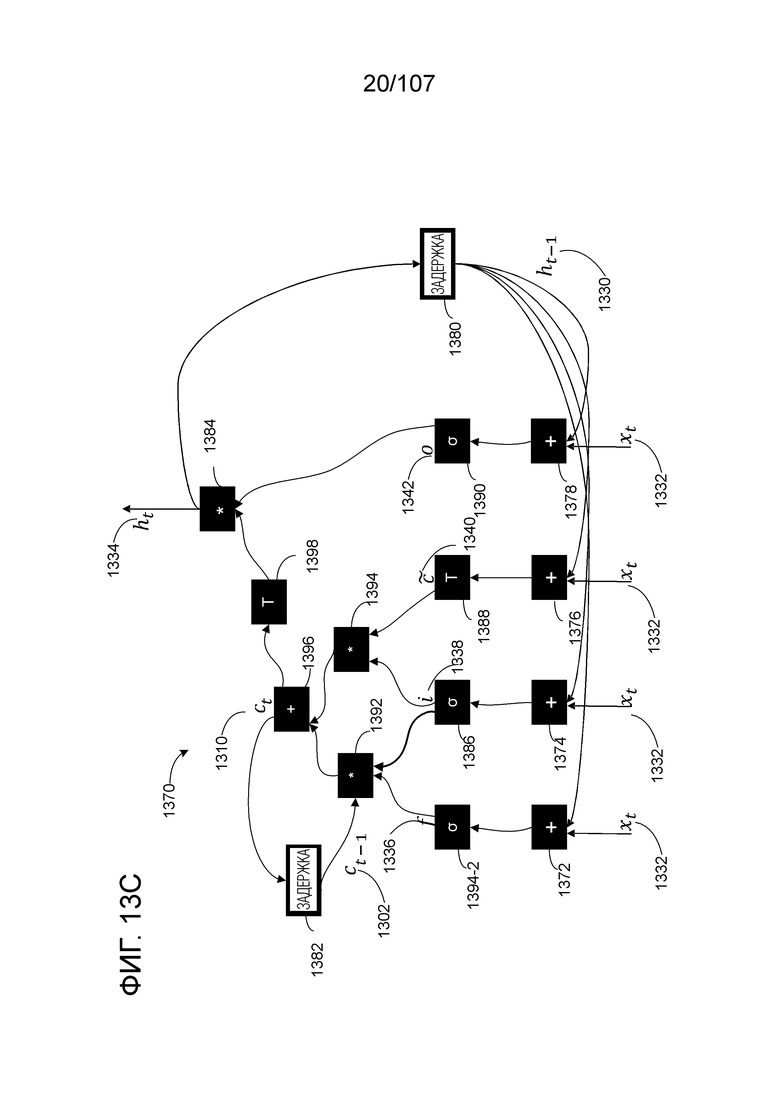

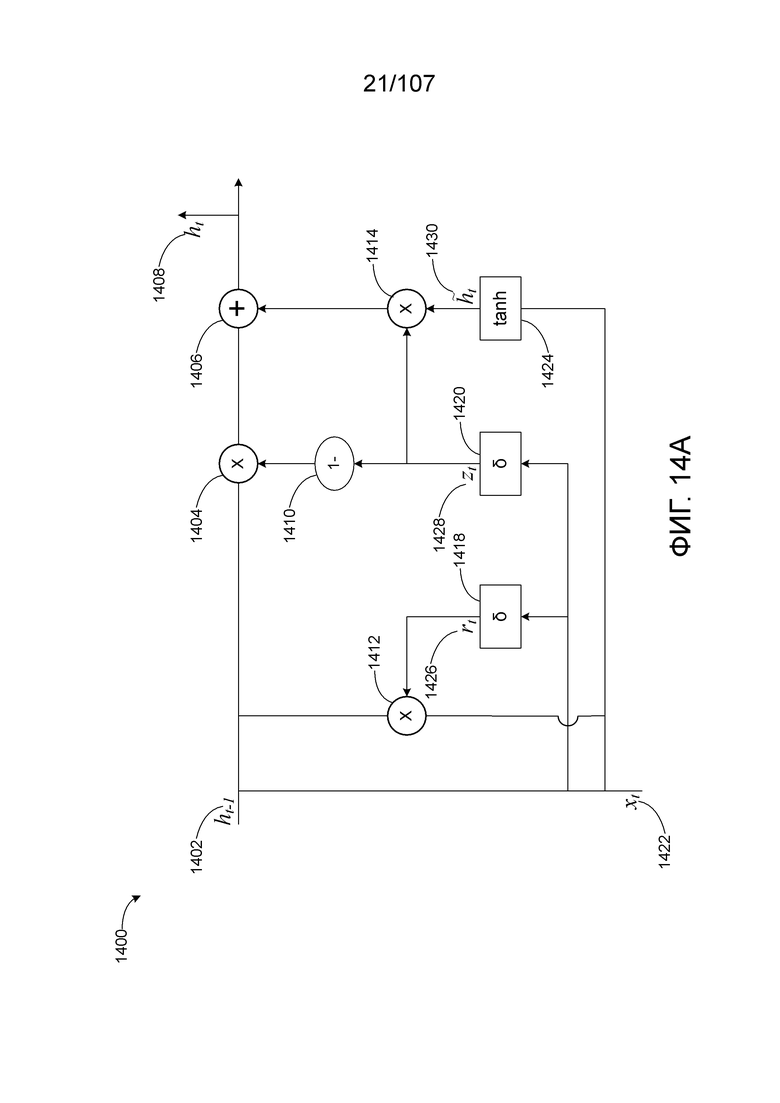

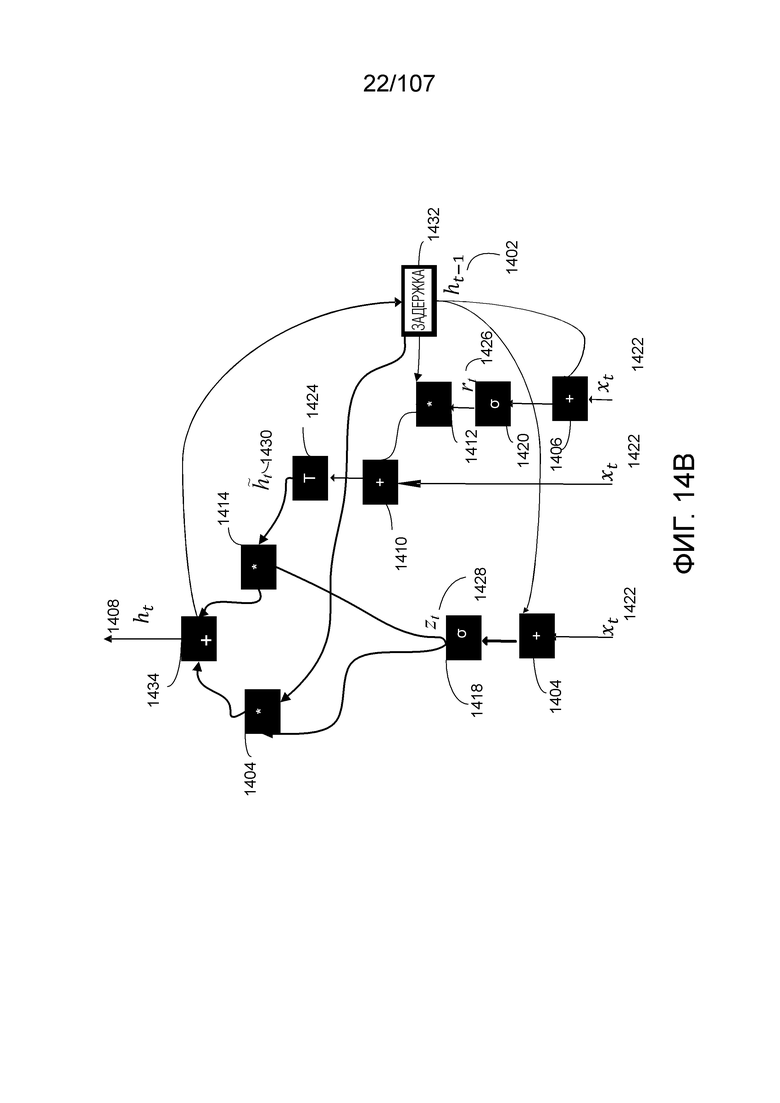

[0021] В некоторых вариантах осуществления, топология нейронной сети включает в себя один или несколько нейронов GRU или LSTM, и этап, на котором трансформируют топологию нейронной сети, включает в себя этап, на котором формируют один или несколько блоков задержки сигнала для каждого рекуррентного соединения одного или нескольких нейронов GRU или LSTM.

[0022] В некоторых вариантах осуществления, один или несколько блоков задержки сигнала активируются с частотой, которая совпадает с предварительно определенной частотой входного сигнала для топологии нейронной сети.

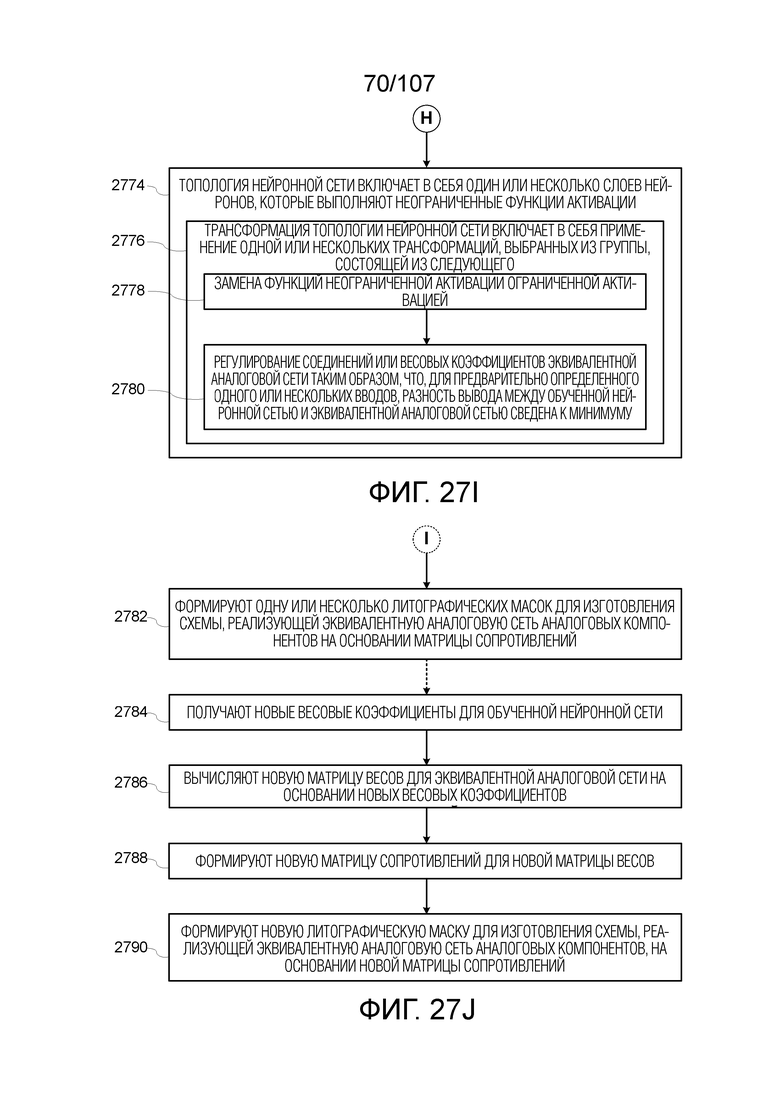

[0023] В некоторых вариантах осуществления, топология нейронной сети включает в себя один или несколько слоев нейронов, которые выполняют функции неограниченной активации, и этап, на котором трансформируют топологию нейронной сети, включает в себя этап, на котором применяют одну или несколько трансформаций, выбранных из группы, состоящей из следующего: (i) замена функций неограниченной активации ограниченной активацией; и (ii) регулирование соединений или весовых коэффициентов эквивалентной аналоговой сети таким образом, что, для предварительно определенного одного или нескольких вводов, разность вывода между обученной нейронной сетью и эквивалентной аналоговой сетью сведена к минимуму.

[0024] В некоторых вариантах осуществления, способ дополнительно включает в себя этап, на котором формируют одну или несколько литографических масок для изготовления схемы, реализующей эквивалентную аналоговую сеть аналоговых компонентов на основе матрицы сопротивлений.

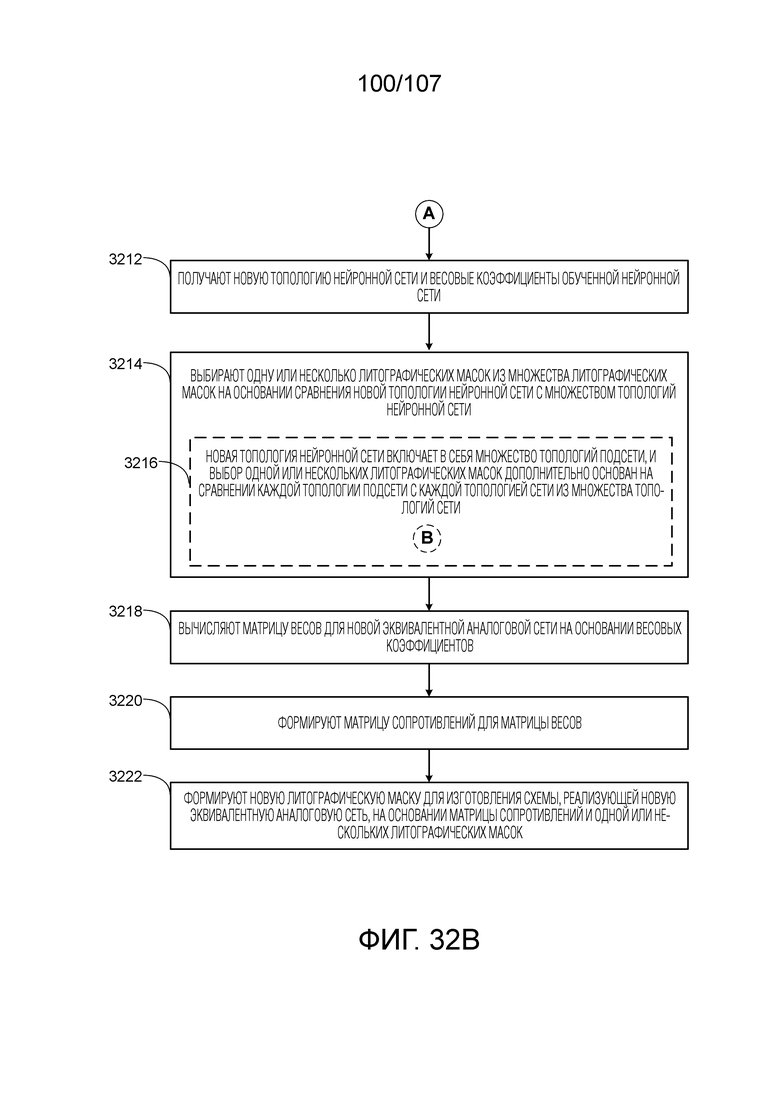

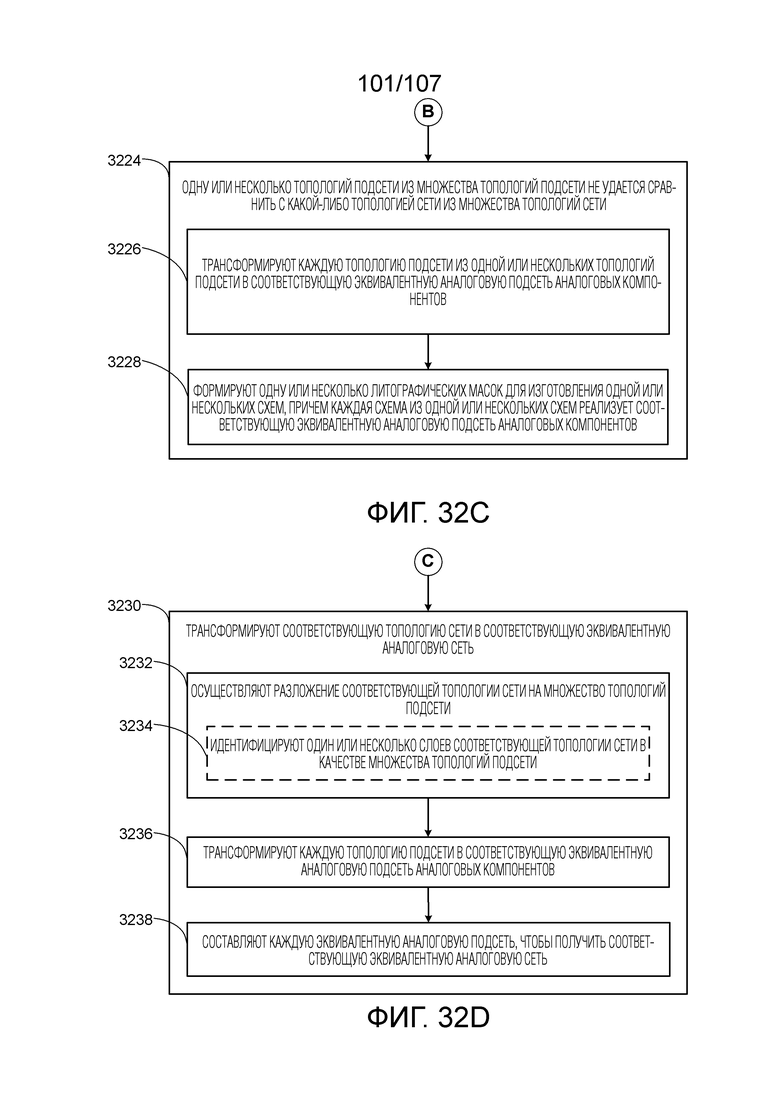

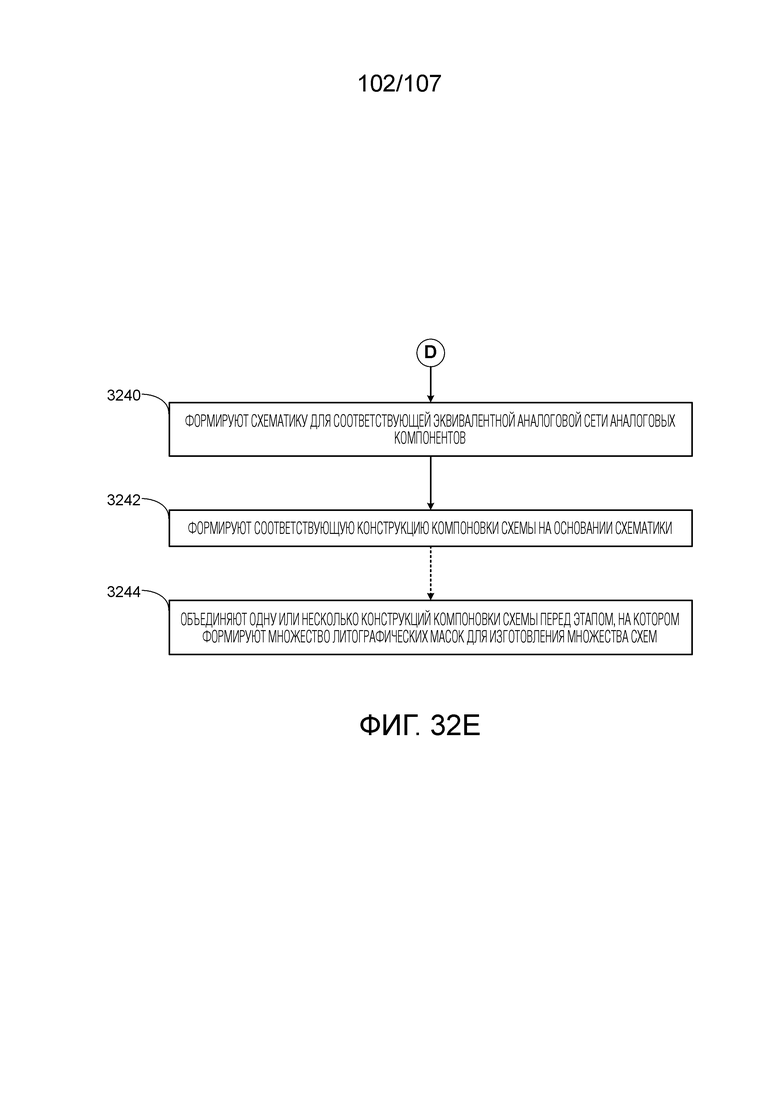

[0025] В некоторых вариантах осуществления, способ дополнительно включает в себя этапы, на которых: (i) получают новые весовые коэффициенты для обученной нейронной сети; (ii) вычисляют новую матрицу весов для эквивалентной аналоговой сети на основе новых весовых коэффициентов; (iii) формируют новую матрицу сопротивлений для новой матрицы весов; и (iv) формируют новую литографическую маску для изготовления схемы, реализующей эквивалентную аналоговую сеть аналоговых компонентов, на основе новой матрицы сопротивлений.

[0026] В некоторых вариантах осуществления, обученная нейронная сеть обучается с использованием программных моделирований, чтобы сформировать весовые коэффициенты.

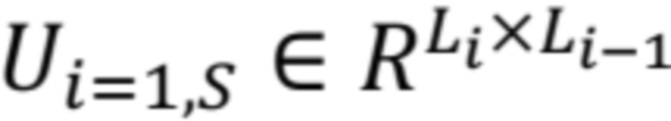

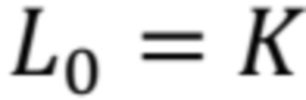

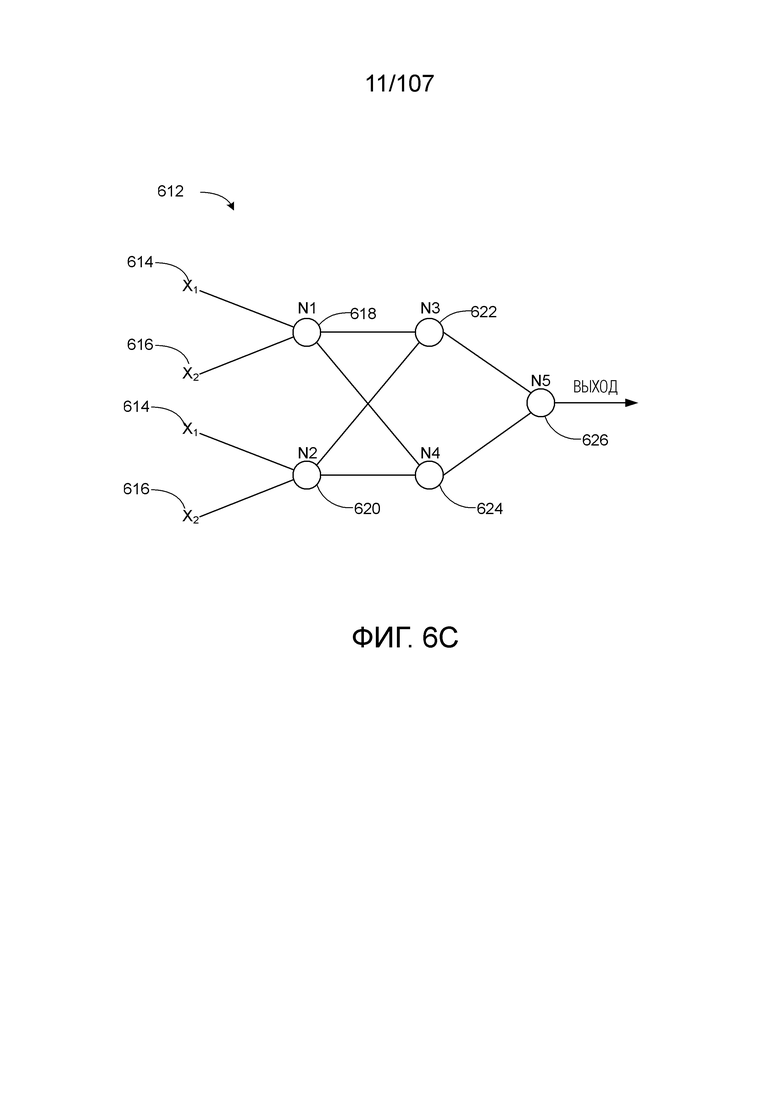

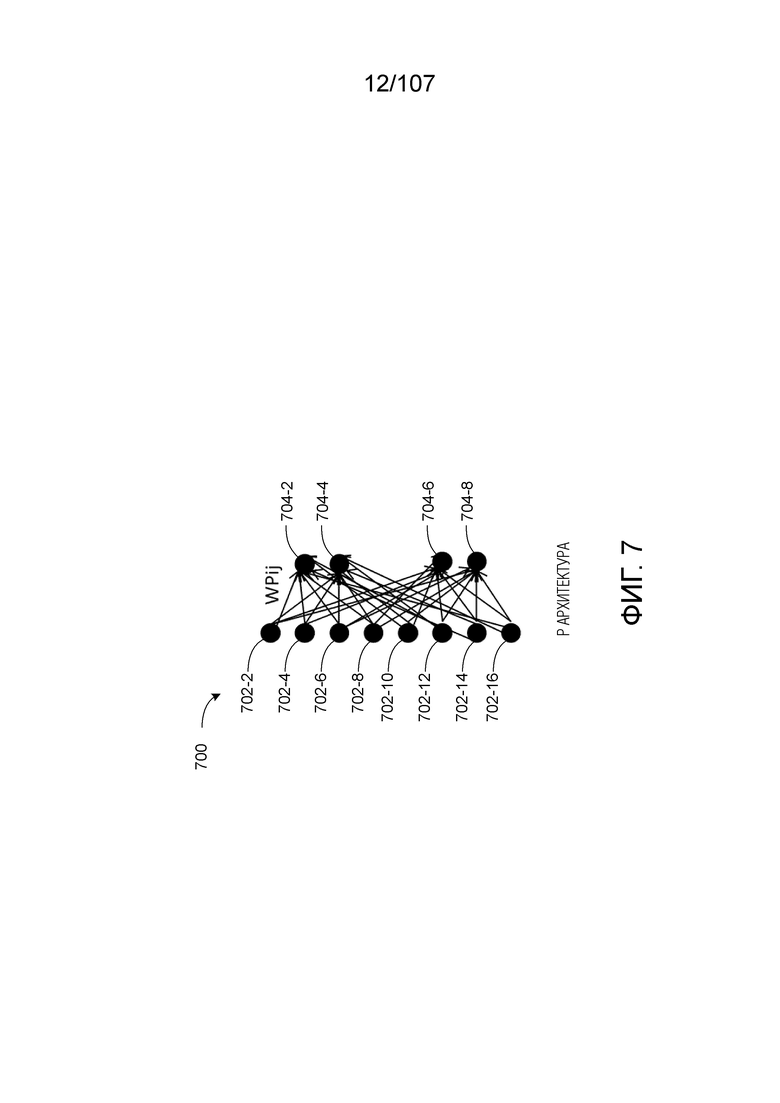

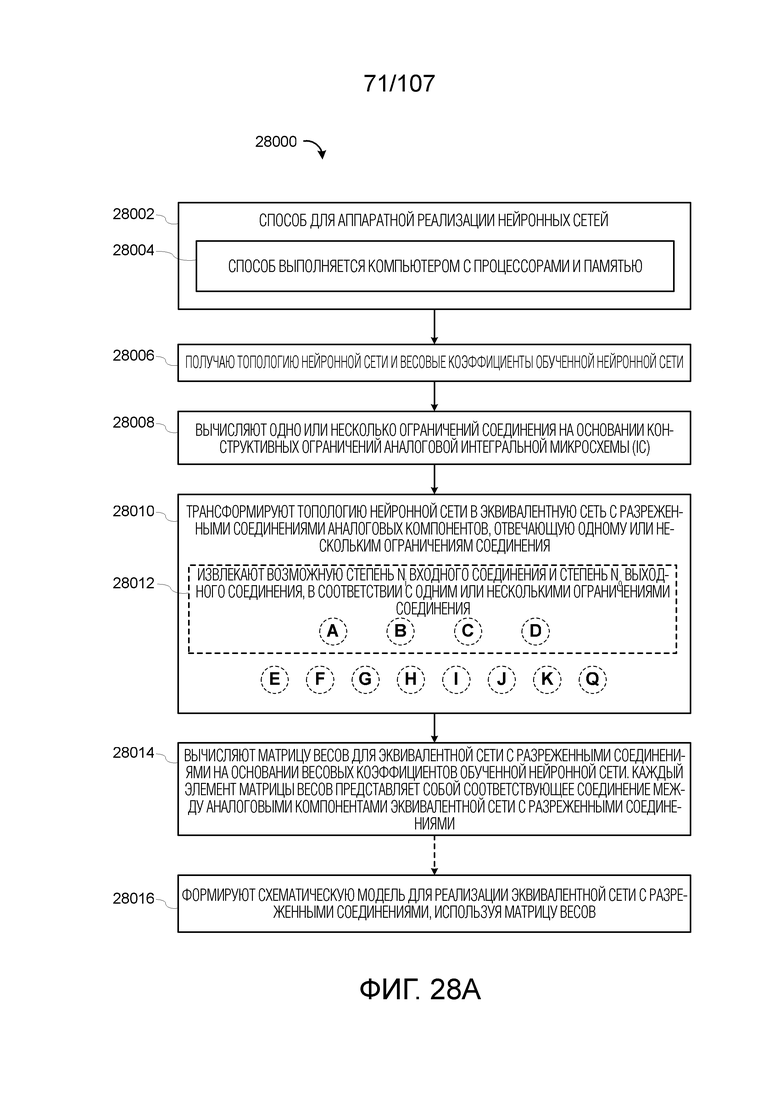

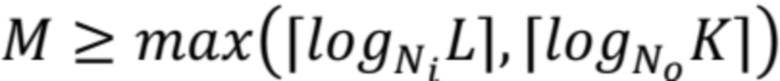

[0027] В другом аспекте, предоставляется способ для аппаратной реализации нейронных сетей, в соответствии с некоторыми вариантами осуществления. Способ включает в себя этап, на котором получают топологию нейронной сети и весовые коэффициенты обученной нейронной сети. Способ также включает в себя этап, на котором вычисляют одно или несколько ограничений соединения на основе конструктивных ограничений аналоговой интегральной микросхемы (IC). Способ также включает в себя этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, отвечающую одному или нескольким ограничениям соединения. Способ также включает в себя этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями на основе весовых коэффициентов обученной нейронной сети. Каждый элемент матрицы весов представляет собой соответствующее соединение между аналоговыми компонентами эквивалентной сети с разреженными соединениями.

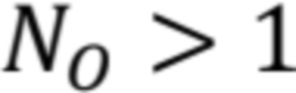

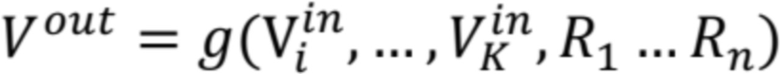

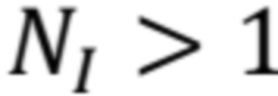

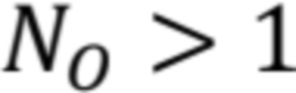

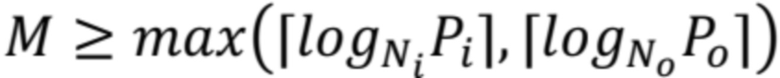

[0028] В некоторых вариантах осуществления, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором извлекают возможную степень  входного соединения и степень

входного соединения и степень  выходного соединения, в соответствии с одним или несколькими ограничениями соединения.

выходного соединения, в соответствии с одним или несколькими ограничениями соединения.

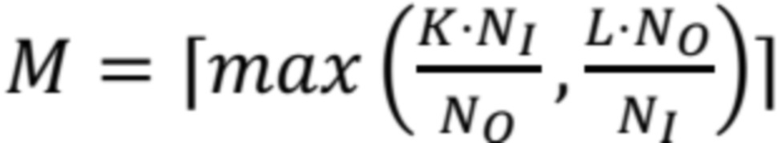

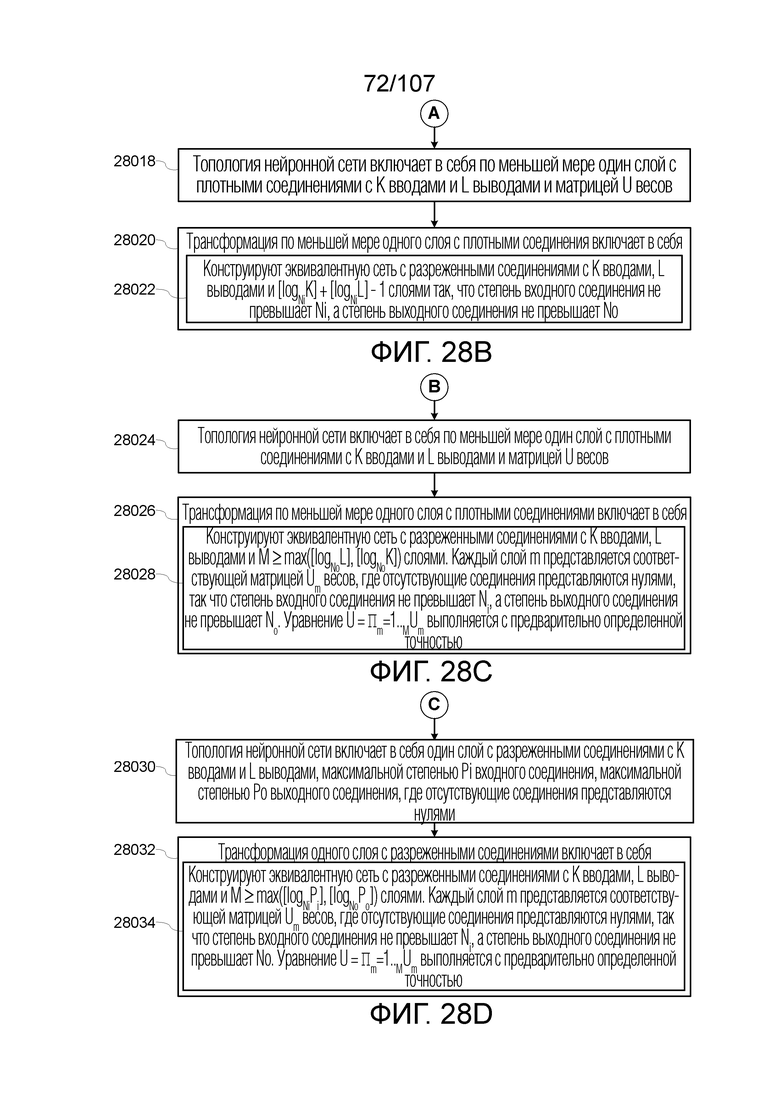

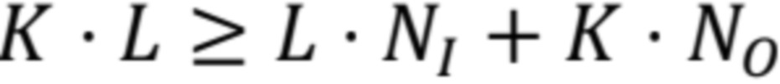

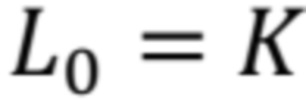

[0029] В некоторых вариантах осуществления, топология нейронной сети включает в себя по меньшей мере один слой с плотными соединениями с  вводами и

вводами и  выводами и матрицей

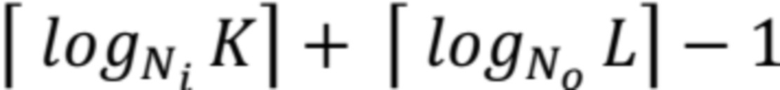

выводами и матрицей  весов. В таких случаях, этап, на котором трансформируют по меньшей мере один слой с плотными соединениями, включает в себя этап, на котором конструируют эквивалентную сеть с разреженными соединениями с

весов. В таких случаях, этап, на котором трансформируют по меньшей мере один слой с плотными соединениями, включает в себя этап, на котором конструируют эквивалентную сеть с разреженными соединениями с  вводами,

вводами,  выводами и

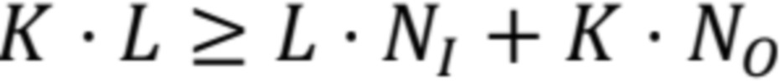

выводами и  слоями так, что степень входного соединения не превышает

слоями так, что степень входного соединения не превышает  , а степень выходного соединения не превышает

, а степень выходного соединения не превышает  .

.

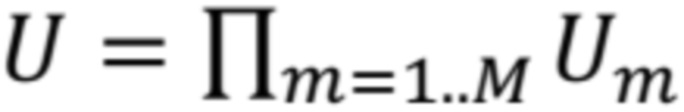

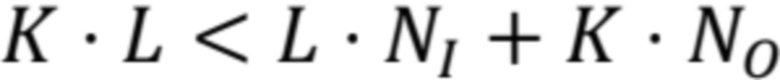

[0030] В некоторых вариантах осуществления, топология нейронной сети включает в себя по меньшей мере один слой с плотными соединениями с  вводами и

вводами и  выводами и матрицей

выводами и матрицей  весов. В таких случаях, этап, на котором трансформируют по меньшей мере один слой с плотными соединениями, включает в себя этап, на котором конструируют эквивалентную сеть с разреженными соединениями с

весов. В таких случаях, этап, на котором трансформируют по меньшей мере один слой с плотными соединениями, включает в себя этап, на котором конструируют эквивалентную сеть с разреженными соединениями с  вводами,

вводами,  выводами и

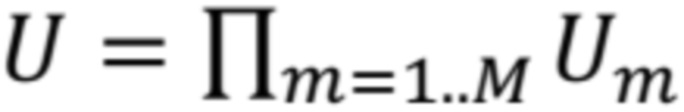

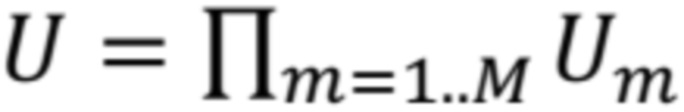

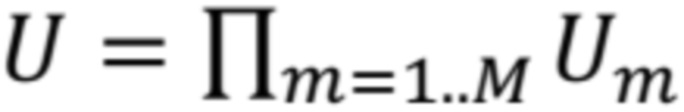

выводами и  слоями. Каждый слой

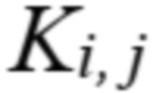

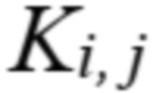

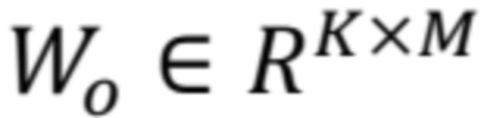

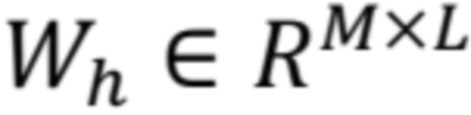

слоями. Каждый слой  представляется соответствующей матрицей

представляется соответствующей матрицей  весов, где отсутствующие соединения представляются нулями, так что степень входного соединения не превышает

весов, где отсутствующие соединения представляются нулями, так что степень входного соединения не превышает  , а степень выходного соединения не превышает

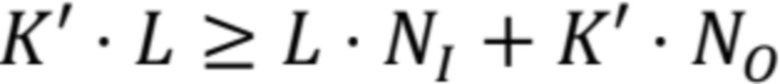

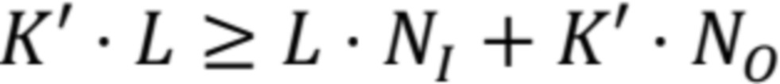

, а степень выходного соединения не превышает  . Уравнение

. Уравнение  выполняется с предварительно определенной точностью.

выполняется с предварительно определенной точностью.

[0031] В некоторых вариантах осуществления, топология нейронной сети включает в себя один слой с разреженными соединениями с  вводами и

вводами и  выводами, максимальной степенью

выводами, максимальной степенью  входного соединения, максимальной степенью

входного соединения, максимальной степенью  выходного соединения и матрицей

выходного соединения и матрицей  весов, где отсутствующие соединения представляются нулями. В таких случаях, этап, на котором трансформируют один слой с разреженными соединениями, включает в себя этап, на котором конструируют эквивалентную сеть с разреженными соединениями с

весов, где отсутствующие соединения представляются нулями. В таких случаях, этап, на котором трансформируют один слой с разреженными соединениями, включает в себя этап, на котором конструируют эквивалентную сеть с разреженными соединениями с  вводами,

вводами,  выводами,

выводами,  слоями, причем каждый слой

слоями, причем каждый слой  представляется соответствующей матрицей

представляется соответствующей матрицей  весов, где отсутствующие соединения представляются нулями, так что степень входного соединения не превышает

весов, где отсутствующие соединения представляются нулями, так что степень входного соединения не превышает  , а степень выходного соединения не превышает

, а степень выходного соединения не превышает  . Уравнение

. Уравнение  выполняется с предварительно определенной точностью.

выполняется с предварительно определенной точностью.

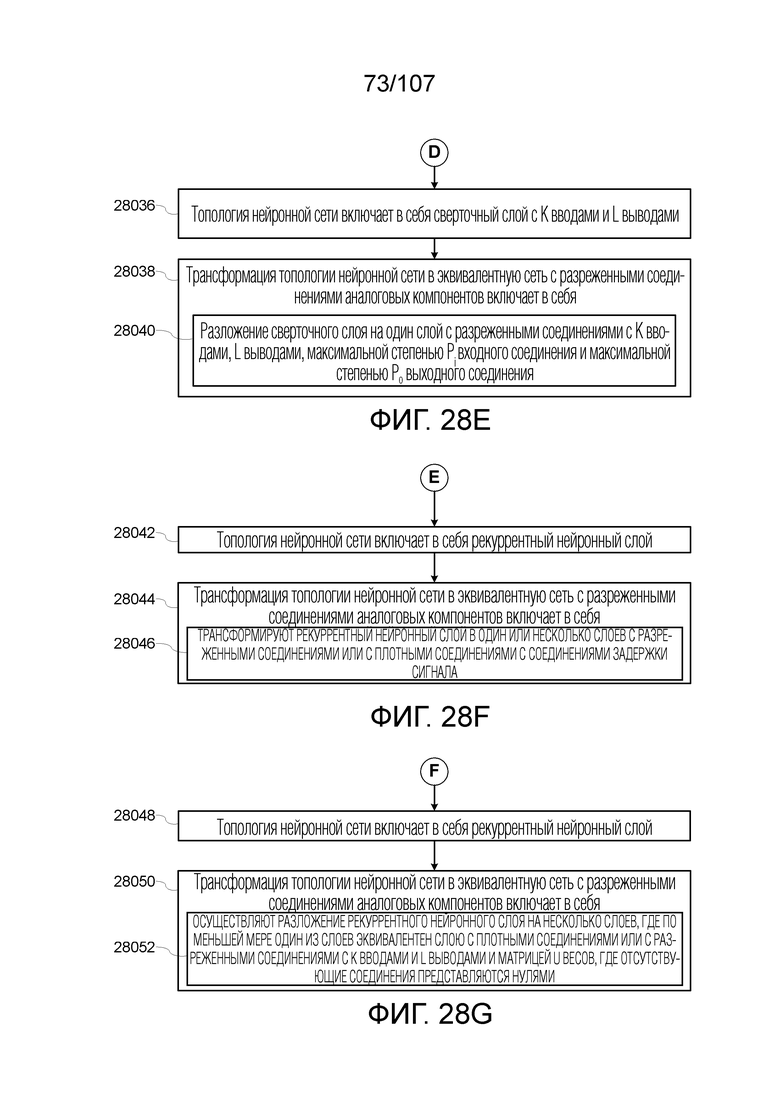

[0032] В некоторых вариантах осуществления, топология нейронной сети включает в себя сверточный слой с  вводами и

вводами и  выводами. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором осуществляют разложение сверточного слоя на один слой с разреженными соединениями с

выводами. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором осуществляют разложение сверточного слоя на один слой с разреженными соединениями с  вводами и

вводами и  выводами, максимальной степенью

выводами, максимальной степенью  входного соединения и максимальной степенью

входного соединения и максимальной степенью  выходного соединения.

выходного соединения.  и

и  .

.

[0033] В некоторых вариантах осуществления, этап, на котором формируют схематическую модель для реализации эквивалентной сети с разреженными соединениями, использует матрицу весов.

[0034] В некоторых вариантах осуществления, топология нейронной сети включает в себя рекуррентный нейронный слой. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором трансформируют рекуррентный нейронный слой в один или несколько слоев с разреженными соединениями или с плотными соединениями с соединениями задержки сигнала.

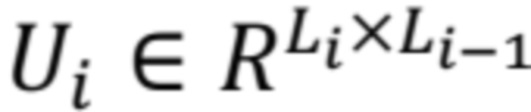

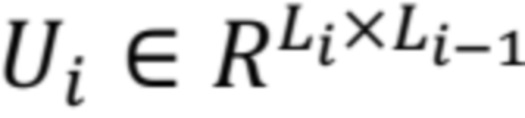

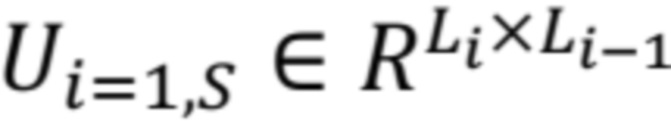

[0035] В некоторых вариантах осуществления, топология нейронной сети включает в себя рекуррентный нейронный слой. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором осуществляют разложение рекуррентного нейронного слоя на несколько слоев, где по меньшей мере один из слоев эквивалентен слою с плотными соединениями или с разреженными соединениями с  вводами и

вводами и  выводами и матрицей

выводами и матрицей  весов, где отсутствующие соединения представляются нулями.

весов, где отсутствующие соединения представляются нулями.

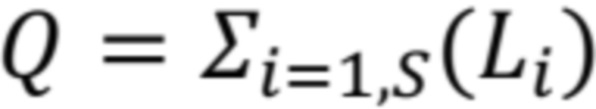

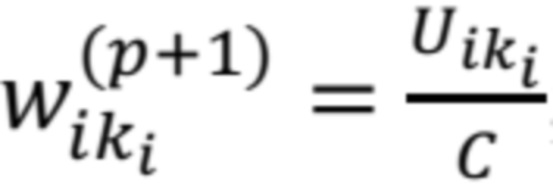

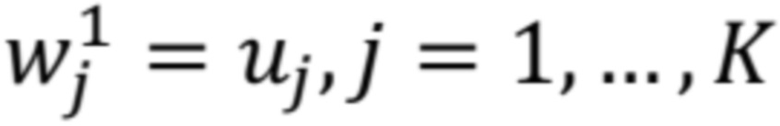

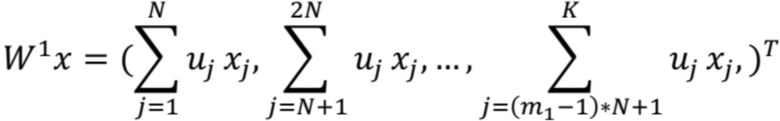

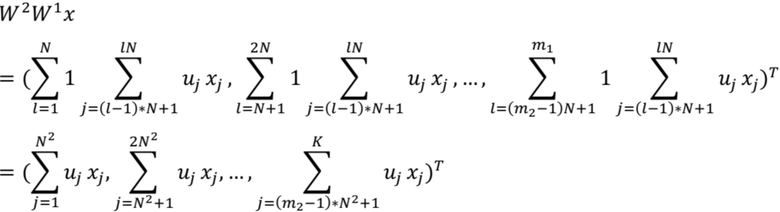

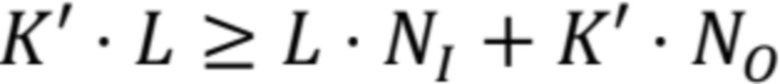

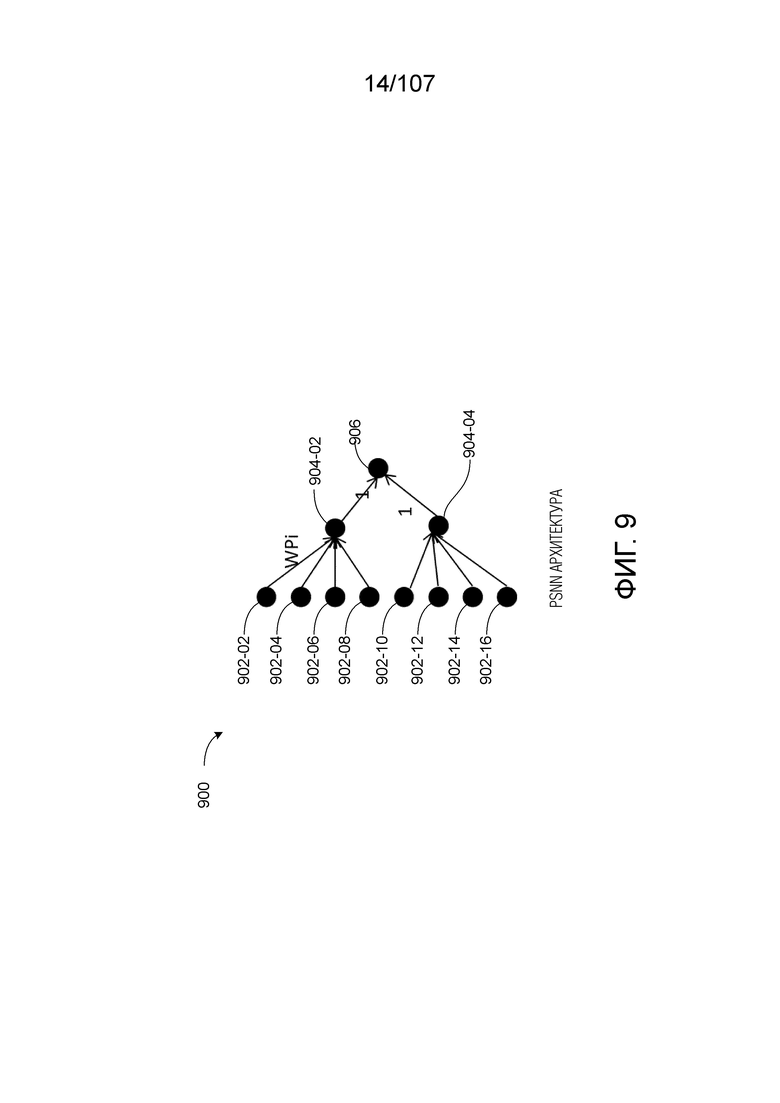

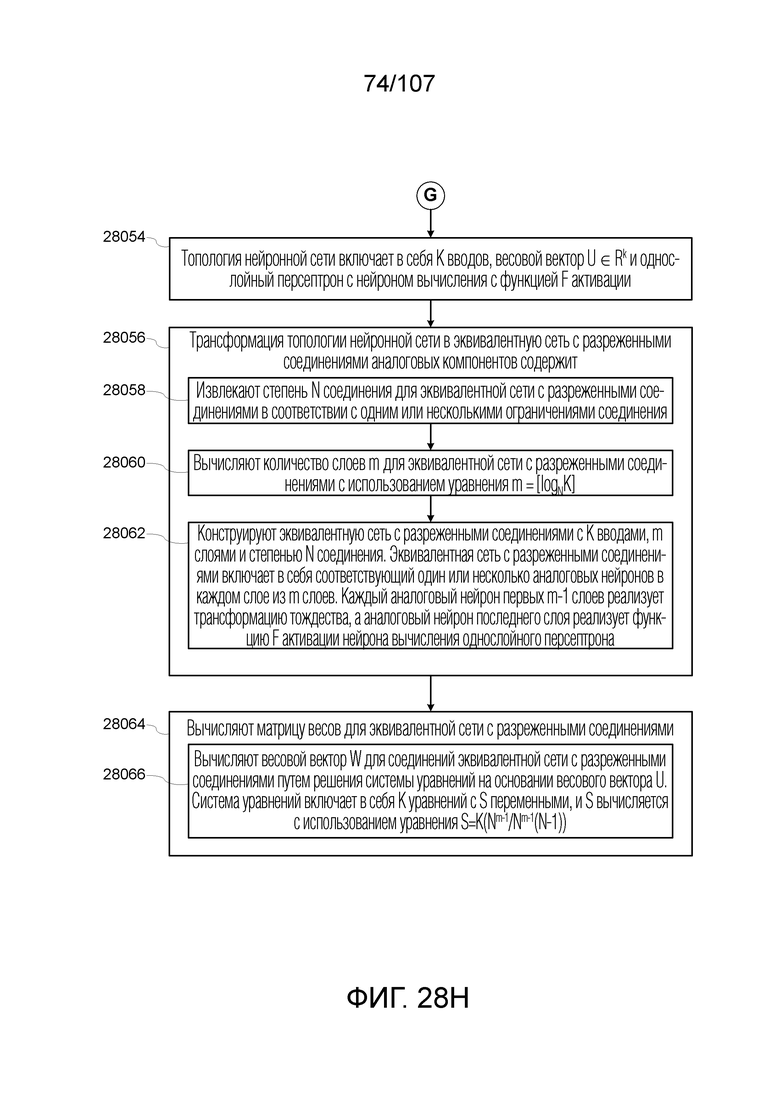

[0036] В некоторых вариантах осуществления, топология нейронной сети включает в себя  вводов, весовой вектор

вводов, весовой вектор  и однослойный персептрон с нейроном вычисления с функцией

и однослойный персептрон с нейроном вычисления с функцией  активации. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: (i) извлекают степень

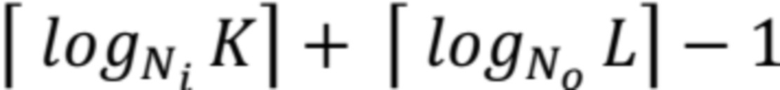

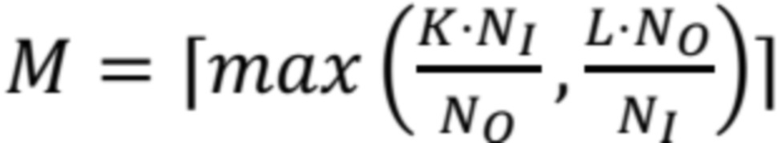

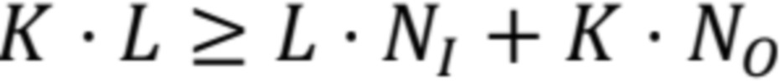

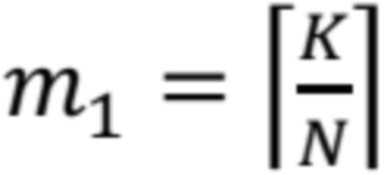

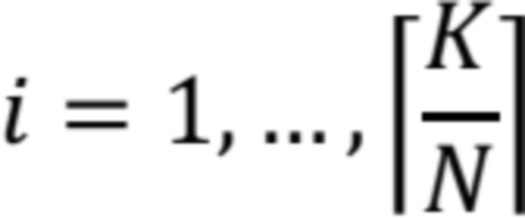

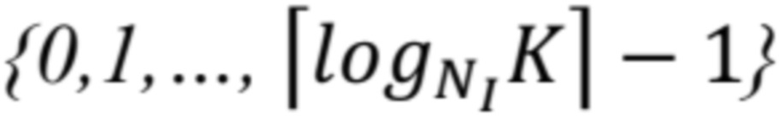

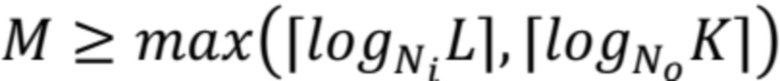

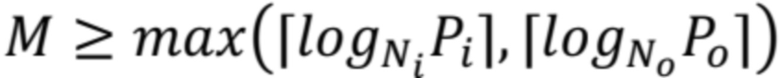

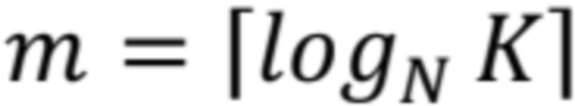

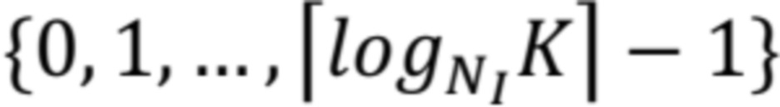

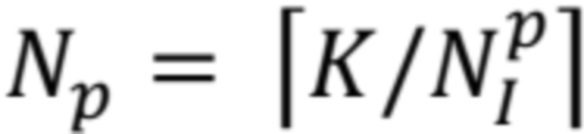

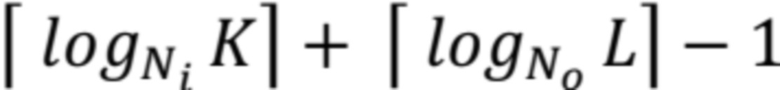

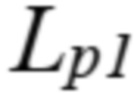

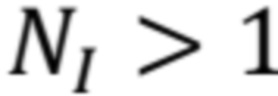

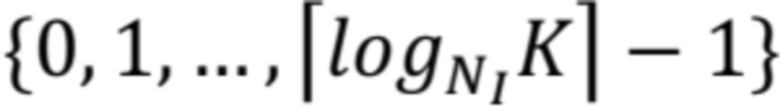

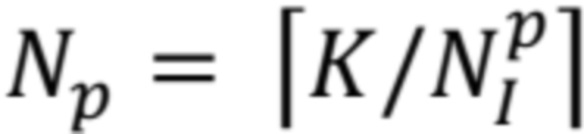

активации. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: (i) извлекают степень  соединения для эквивалентной сети с разреженными соединениями в соответствии с одним или несколькими ограничениями соединения; (ii) вычисляют количество слоев

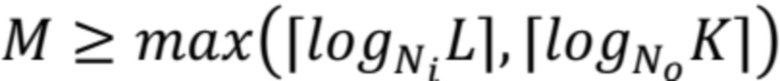

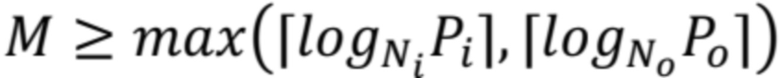

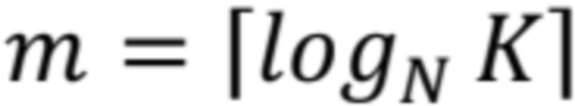

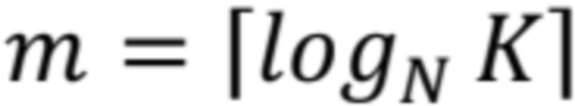

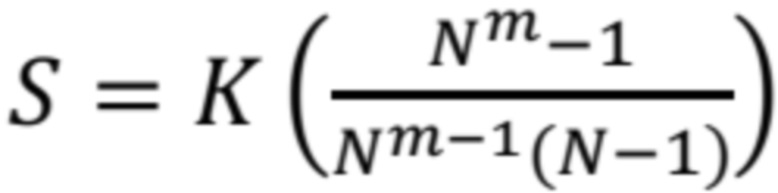

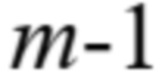

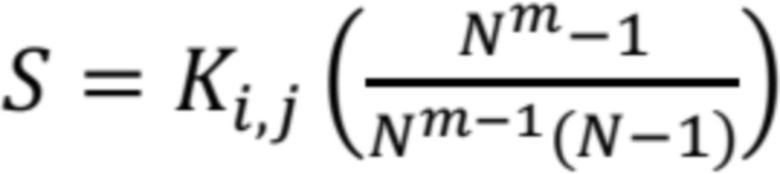

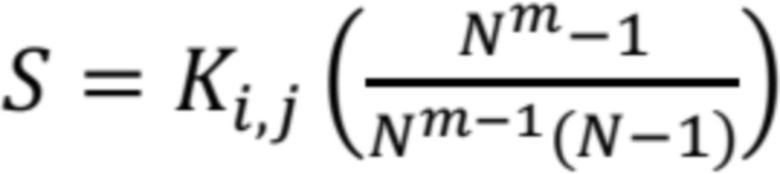

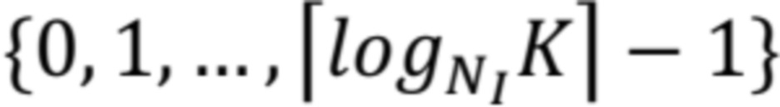

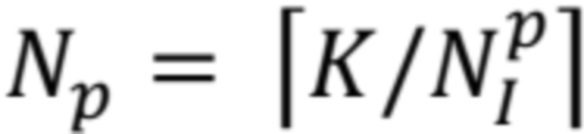

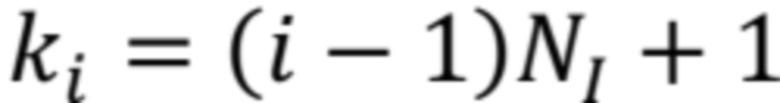

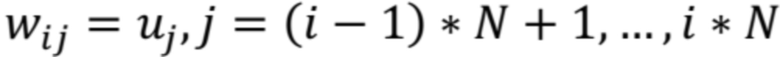

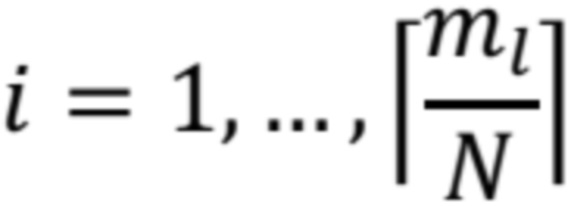

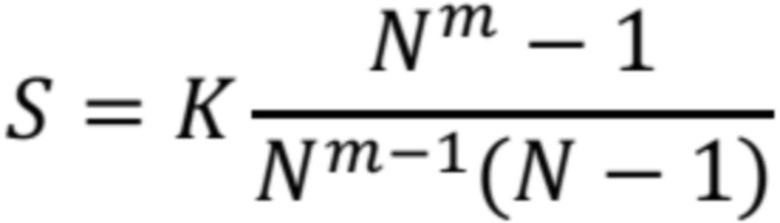

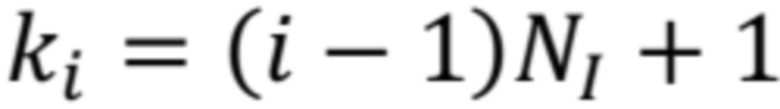

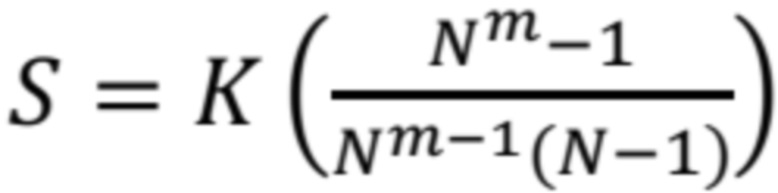

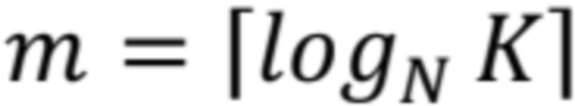

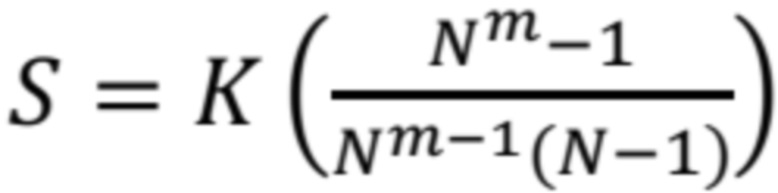

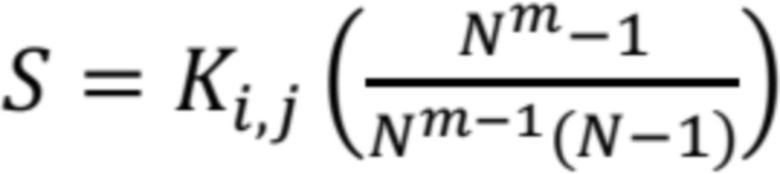

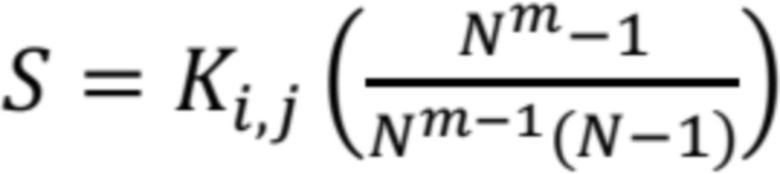

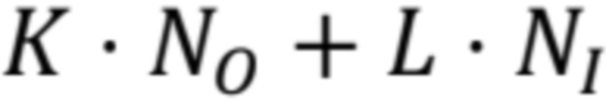

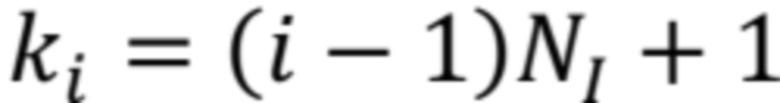

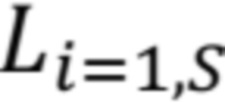

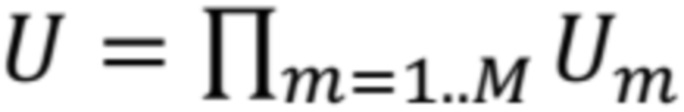

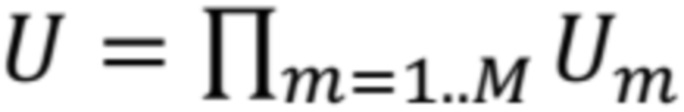

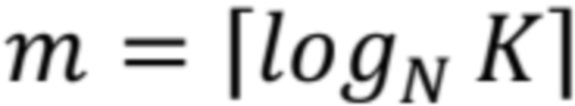

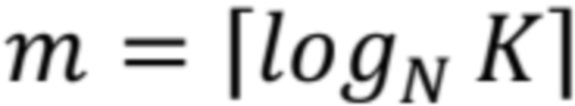

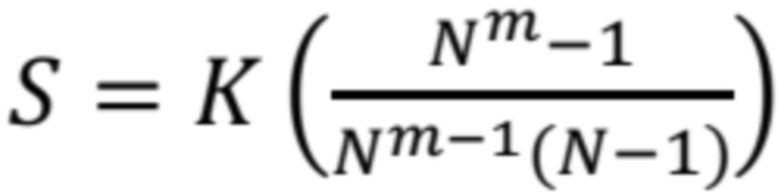

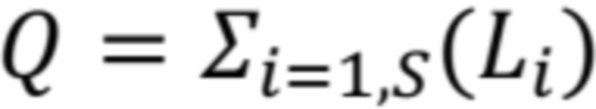

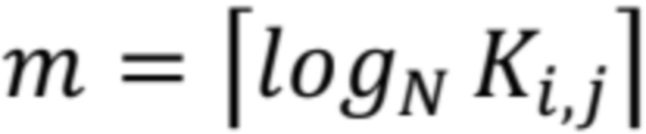

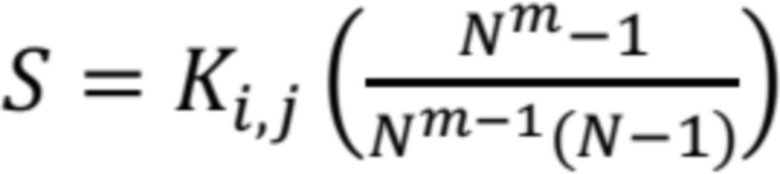

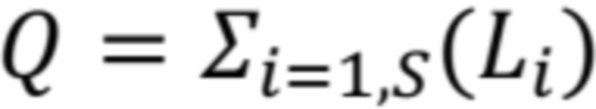

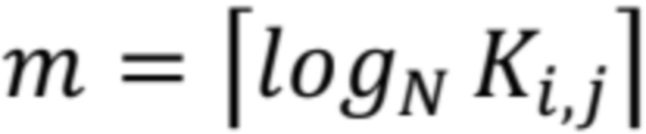

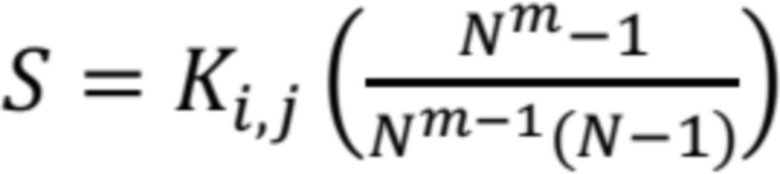

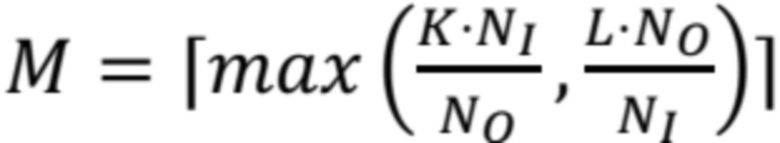

соединения для эквивалентной сети с разреженными соединениями в соответствии с одним или несколькими ограничениями соединения; (ii) вычисляют количество слоев  для эквивалентной сети с разреженными соединениями с использованием уравнения

для эквивалентной сети с разреженными соединениями с использованием уравнения  ; и (iii) конструируют эквивалентную сеть с разреженными соединениями с

; и (iii) конструируют эквивалентную сеть с разреженными соединениями с  вводами,

вводами,  слоями и степенью

слоями и степенью  соединения. Эквивалентная сеть с разреженными соединениями включает в себя соответствующий один или несколько аналоговых нейронов в каждом слое из

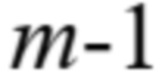

соединения. Эквивалентная сеть с разреженными соединениями включает в себя соответствующий один или несколько аналоговых нейронов в каждом слое из  слоев, причем каждый аналоговый нейрон первых

слоев, причем каждый аналоговый нейрон первых  слоев реализует тождественную трансформацию, а аналоговый нейрон последнего слоя реализует функцию

слоев реализует тождественную трансформацию, а аналоговый нейрон последнего слоя реализует функцию  активации нейрона вычисления однослойного персептрона. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этап, на котором вычисляют весовой вектор

активации нейрона вычисления однослойного персептрона. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этап, на котором вычисляют весовой вектор  для соединений эквивалентной сети с разреженными соединениями путем решения системы уравнений на основе весового вектора

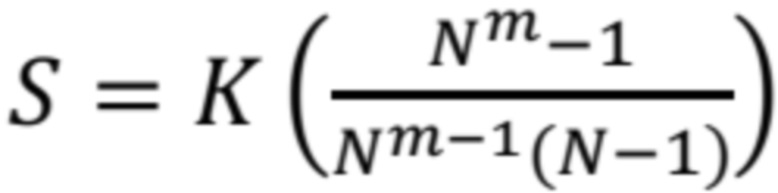

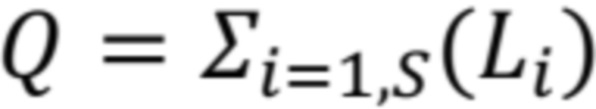

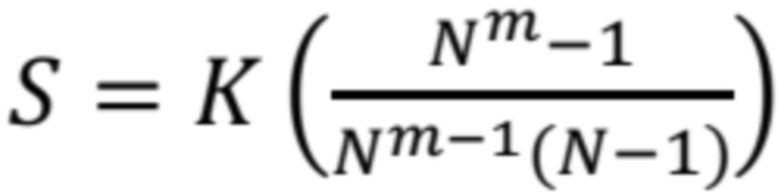

для соединений эквивалентной сети с разреженными соединениями путем решения системы уравнений на основе весового вектора  . Система уравнений включает в себя

. Система уравнений включает в себя  уравнений с

уравнений с  переменными, и

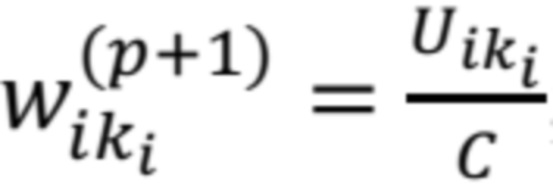

переменными, и  вычисляется с использованием уравнения

вычисляется с использованием уравнения  .

.

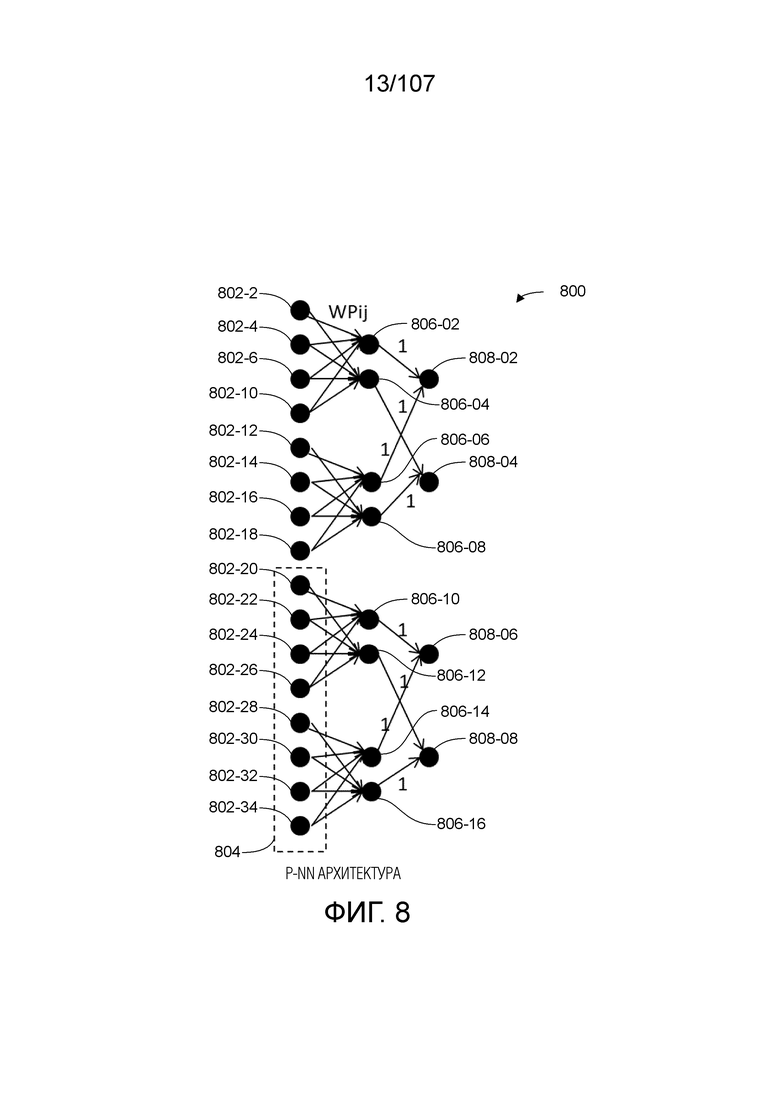

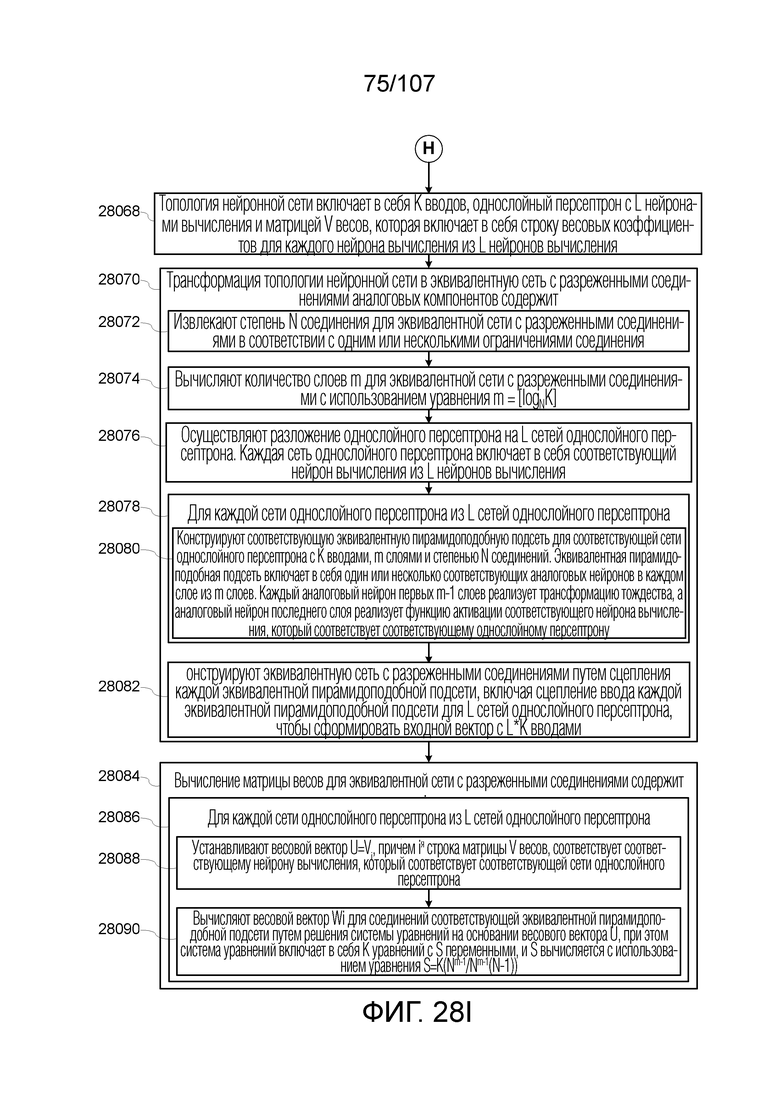

[0037] В некоторых вариантах осуществления, топология нейронной сети включает в себя  вводов, однослойный персептрон с

вводов, однослойный персептрон с  нейронами вычисления и матрицей

нейронами вычисления и матрицей  весов, которая включает в себя строку весовых коэффициентов для каждого нейрона вычисления из

весов, которая включает в себя строку весовых коэффициентов для каждого нейрона вычисления из  нейронов вычисления. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: (i) извлекают степень

нейронов вычисления. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: (i) извлекают степень  соединения для эквивалентной сети с разреженными соединениями в соответствии с одним или несколькими ограничениями соединения; (ii) вычисляют количество слоев

соединения для эквивалентной сети с разреженными соединениями в соответствии с одним или несколькими ограничениями соединения; (ii) вычисляют количество слоев  для эквивалентной сети с разреженными соединениями с использованием уравнения

для эквивалентной сети с разреженными соединениями с использованием уравнения  ; (iii) осуществляют разложение однослойного персептрона на

; (iii) осуществляют разложение однослойного персептрона на  сетей однослойного персептрона. Каждая сеть однослойного персептрона включает в себя соответствующий нейрон вычисления из

сетей однослойного персептрона. Каждая сеть однослойного персептрона включает в себя соответствующий нейрон вычисления из  нейронов вычисления; (iv) для каждой сети однослойного персептрона из

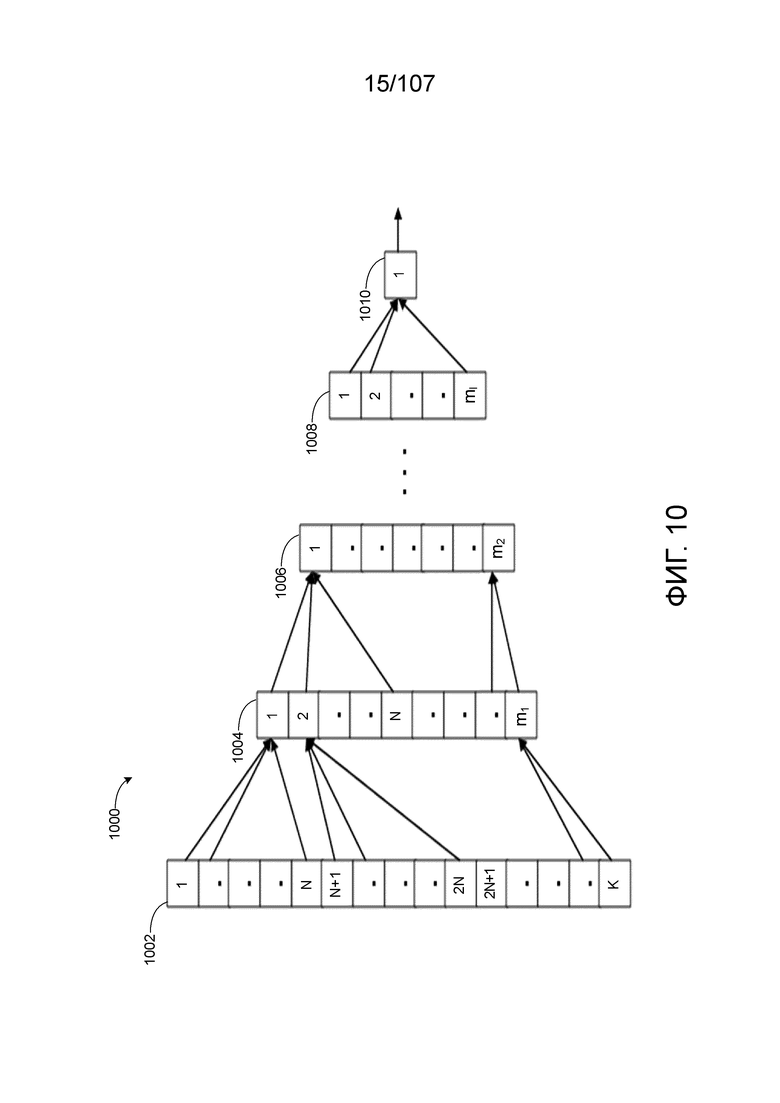

нейронов вычисления; (iv) для каждой сети однослойного персептрона из  сетей однослойного персептрона: (a) конструируют соответствующую эквивалентную пирамидоподобную подсеть для соответствующей сети однослойного персептрона с

сетей однослойного персептрона: (a) конструируют соответствующую эквивалентную пирамидоподобную подсеть для соответствующей сети однослойного персептрона с  вводами,

вводами,  слоями и степенью

слоями и степенью  соединений. Эквивалентная пирамидоподобная подсеть включает в себя один или несколько соответствующих аналоговых нейронов в каждом слое из

соединений. Эквивалентная пирамидоподобная подсеть включает в себя один или несколько соответствующих аналоговых нейронов в каждом слое из  слоев, причем каждый аналоговый нейрон первых

слоев, причем каждый аналоговый нейрон первых  слоев реализует тождественную трансформацию, а аналоговый нейрон последнего слоя реализует функцию активации соответствующего нейрона вычисления, который соответствует соответствующему однослойному персептрону; и (b) конструируют эквивалентную сеть с разреженными соединениями путем сцепления каждой эквивалентной пирамидоподобной подсети, включая сцепление ввода каждой эквивалентной пирамидоподобной подсети для

слоев реализует тождественную трансформацию, а аналоговый нейрон последнего слоя реализует функцию активации соответствующего нейрона вычисления, который соответствует соответствующему однослойному персептрону; и (b) конструируют эквивалентную сеть с разреженными соединениями путем сцепления каждой эквивалентной пирамидоподобной подсети, включая сцепление ввода каждой эквивалентной пирамидоподобной подсети для  сетей однослойного персептрона, чтобы сформировать входной вектор с

сетей однослойного персептрона, чтобы сформировать входной вектор с  вводами. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этапы на которых, для каждой сети однослойного персептрона из

вводами. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этапы на которых, для каждой сети однослойного персептрона из  сетей однослойного персептрона: (i) устанавливают весовой вектор

сетей однослойного персептрона: (i) устанавливают весовой вектор  , причем iя строка матрицы

, причем iя строка матрицы  весов, соответствует соответствующему нейрону вычисления, который соответствует соответствующей сети однослойного персептрона; и (ii) вычисляют весовой вектор

весов, соответствует соответствующему нейрону вычисления, который соответствует соответствующей сети однослойного персептрона; и (ii) вычисляют весовой вектор  для соединений соответствующей эквивалентной пирамидоподобной подсети путем решения системы уравнений на основе весового вектора

для соединений соответствующей эквивалентной пирамидоподобной подсети путем решения системы уравнений на основе весового вектора  . Система уравнений включает в себя

. Система уравнений включает в себя  уравнений с

уравнений с  переменными, и

переменными, и  вычисляется с использованием уравнения

вычисляется с использованием уравнения  .

.

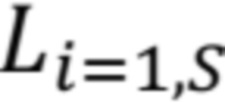

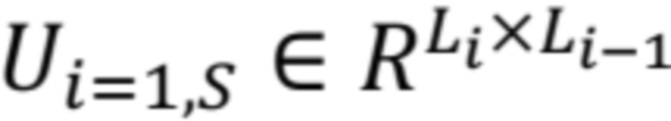

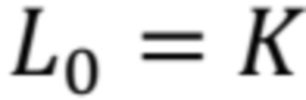

[0038] В некоторых вариантах осуществления, топология нейронной сети включает в себя  вводов, многослойный персептрон с

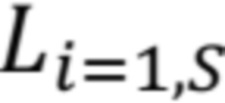

вводов, многослойный персептрон с  слоями, причем каждый слой

слоями, причем каждый слой  из

из  слоев включает в себя соответствующий набор из

слоев включает в себя соответствующий набор из  нейронов вычисления и соответствующих матриц

нейронов вычисления и соответствующих матриц  весов, которые включают в себя строку весовых коэффициентов для каждого нейрона вычисления из

весов, которые включают в себя строку весовых коэффициентов для каждого нейрона вычисления из  нейронов вычисления. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: (i) извлекают степень

нейронов вычисления. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: (i) извлекают степень  соединения для эквивалентной сети с разреженными соединениями в соответствии с одним или несколькими ограничениями соединения; (ii) осуществляют разложение многослойного персептрона на

соединения для эквивалентной сети с разреженными соединениями в соответствии с одним или несколькими ограничениями соединения; (ii) осуществляют разложение многослойного персептрона на  сетей однослойного персептрона. Каждая сеть однослойного персептрона включает в себя соответствующий нейрон вычисления из

сетей однослойного персептрона. Каждая сеть однослойного персептрона включает в себя соответствующий нейрон вычисления из  нейронов вычисления. Этап, на котором осуществляют разложение многослойного персептрона, включает в себя этап, на котором дублируют один или несколько вводов из

нейронов вычисления. Этап, на котором осуществляют разложение многослойного персептрона, включает в себя этап, на котором дублируют один или несколько вводов из  вводов, которые совместно используются

вводов, которые совместно используются  нейронами вычисления; (iii) для каждой сети однослойного персептрона из

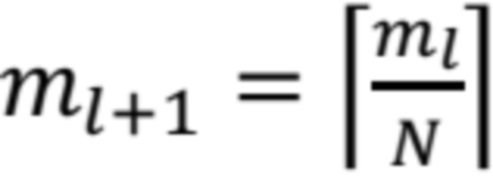

нейронами вычисления; (iii) для каждой сети однослойного персептрона из  сетей однослойного персептрона: (a) вычисляют количество слоев

сетей однослойного персептрона: (a) вычисляют количество слоев  для соответствующей эквивалентной пирамидоподобной подсети с использованием уравнения

для соответствующей эквивалентной пирамидоподобной подсети с использованием уравнения  .

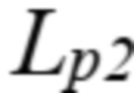

.  является количеством вводов для соответствующего нейрона вычисления в многослойном персептроне; и (b) конструируют соответствующую эквивалентную пирамидоподобную подсеть для соответствующей сети однослойного персептрона с

является количеством вводов для соответствующего нейрона вычисления в многослойном персептроне; и (b) конструируют соответствующую эквивалентную пирамидоподобную подсеть для соответствующей сети однослойного персептрона с  вводами,

вводами,  слоями и степенью

слоями и степенью  соединения. Эквивалентная пирамидоподобная подсеть включает в себя один или несколько соответствующих аналоговых нейронов в каждом слое из

соединения. Эквивалентная пирамидоподобная подсеть включает в себя один или несколько соответствующих аналоговых нейронов в каждом слое из  слоев, причем каждый аналоговый нейрон первых

слоев, причем каждый аналоговый нейрон первых  слоев реализует тождественную трансформацию, а аналоговый нейрон последнего слоя реализует функцию активации соответствующего нейрона вычисления, который соответствует соответствующей сети однослойного персептрона; и (iv) конструируют эквивалентную сеть с разреженными соединениями путем сцепления каждой эквивалентной пирамидоподобной подсети, включая сцепление ввода каждой эквивалентной пирамидоподобной подсети для

слоев реализует тождественную трансформацию, а аналоговый нейрон последнего слоя реализует функцию активации соответствующего нейрона вычисления, который соответствует соответствующей сети однослойного персептрона; и (iv) конструируют эквивалентную сеть с разреженными соединениями путем сцепления каждой эквивалентной пирамидоподобной подсети, включая сцепление ввода каждой эквивалентной пирамидоподобной подсети для  сетей однослойного персептрона, чтобы сформировать входной вектор с

сетей однослойного персептрона, чтобы сформировать входной вектор с  вводами. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этапы, на которых: для каждой сети однослойного персептрона из

вводами. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этапы, на которых: для каждой сети однослойного персептрона из  сетей однослойного персептрона: (i) устанавливают весовой вектор

сетей однослойного персептрона: (i) устанавливают весовой вектор  , причем iя строка матрицы

, причем iя строка матрицы  весов, соответствует соответствующему нейрону вычисления, который соответствует соответствующей сети однослойного персептрона, где

весов, соответствует соответствующему нейрону вычисления, который соответствует соответствующей сети однослойного персептрона, где  является соответствующим слоем соответствующего нейрона вычисления в многослойном персептроне; и (ii) вычисляют весовой вектор

является соответствующим слоем соответствующего нейрона вычисления в многослойном персептроне; и (ii) вычисляют весовой вектор  для соединений соответствующей эквивалентной пирамидоподобной подсети путем решения системы уравнений на основе весового вектора

для соединений соответствующей эквивалентной пирамидоподобной подсети путем решения системы уравнений на основе весового вектора  . Система уравнений включает в себя

. Система уравнений включает в себя  уравнений с

уравнений с  переменными, и

переменными, и  вычисляется с использованием уравнения

вычисляется с использованием уравнения  .

.

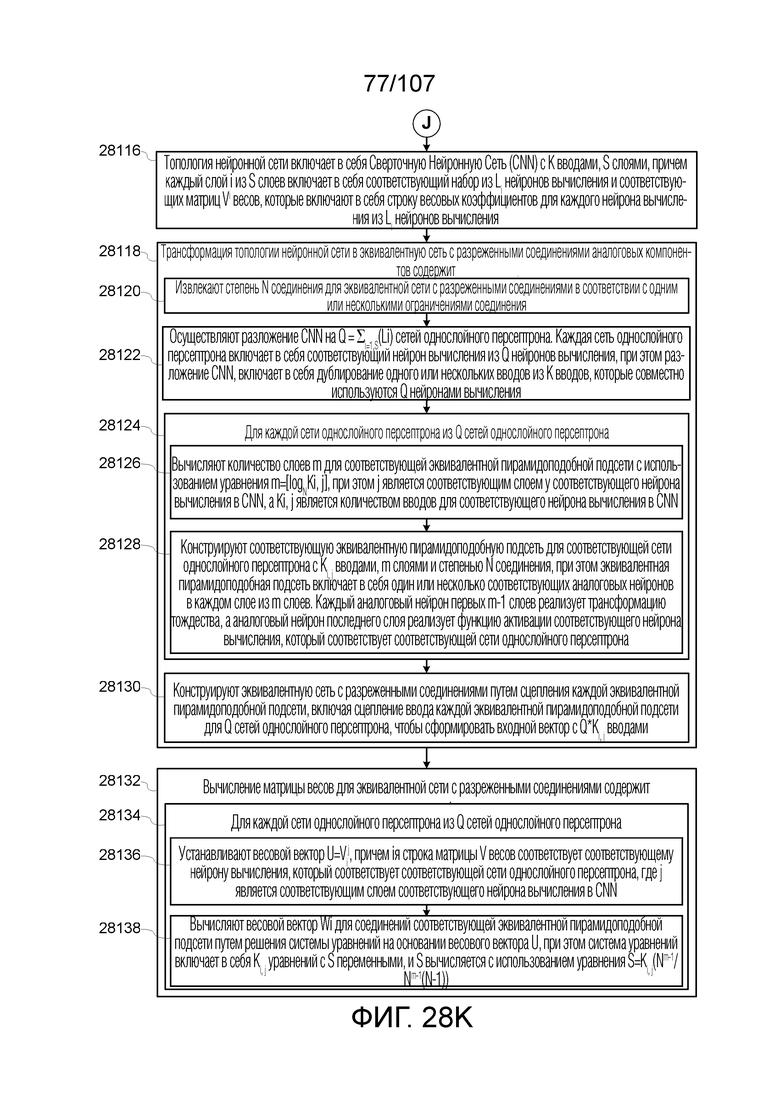

[0039] В некоторых вариантах осуществления, топология нейронной сети включает в себя Сверточную Нейронную Сеть (CNN) с  вводами,

вводами,  слоями, причем каждый слой

слоями, причем каждый слой  из

из  слоев включает в себя соответствующий набор из

слоев включает в себя соответствующий набор из  нейронов вычисления и соответствующих матриц

нейронов вычисления и соответствующих матриц  весов, которые включают в себя строку весовых коэффициентов для каждого нейрона вычисления из

весов, которые включают в себя строку весовых коэффициентов для каждого нейрона вычисления из  нейронов вычисления. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: (i) извлекают степень

нейронов вычисления. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: (i) извлекают степень  соединения для эквивалентной сети с разреженными соединениями в соответствии с одним или несколькими ограничениями соединения; (ii) осуществляют разложение CNN на

соединения для эквивалентной сети с разреженными соединениями в соответствии с одним или несколькими ограничениями соединения; (ii) осуществляют разложение CNN на  сетей однослойного персептрона. Каждая сеть однослойного персептрона включает в себя соответствующий нейрон вычисления из

сетей однослойного персептрона. Каждая сеть однослойного персептрона включает в себя соответствующий нейрон вычисления из  нейронов вычисления. Этап, на котором осуществляют разложение CNN, включает в себя этап, на котором дублируют один или несколько вводов из

нейронов вычисления. Этап, на котором осуществляют разложение CNN, включает в себя этап, на котором дублируют один или несколько вводов из  вводов, которые совместно используются

вводов, которые совместно используются  нейронами вычисления; (iii) для каждой сети однослойного персептрона из

нейронами вычисления; (iii) для каждой сети однослойного персептрона из  сетей однослойного персептрона: (a) вычисляют количество слоев

сетей однослойного персептрона: (a) вычисляют количество слоев  для соответствующей эквивалентной пирамидоподобной подсети с использованием уравнения

для соответствующей эквивалентной пирамидоподобной подсети с использованием уравнения  .

.  является соответствующим слоем у соответствующего нейрона вычисления в CNN, а

является соответствующим слоем у соответствующего нейрона вычисления в CNN, а  является количеством вводов для соответствующего нейрона вычисления в CNN; и (b) конструируют соответствующую эквивалентную пирамидоподобную подсеть для соответствующей сети однослойного персептрона с

является количеством вводов для соответствующего нейрона вычисления в CNN; и (b) конструируют соответствующую эквивалентную пирамидоподобную подсеть для соответствующей сети однослойного персептрона с  вводами,

вводами,  слоями и степенью

слоями и степенью  соединения. Эквивалентная пирамидоподобная подсеть включает в себя один или несколько соответствующих аналоговых нейронов в каждом слое из

соединения. Эквивалентная пирамидоподобная подсеть включает в себя один или несколько соответствующих аналоговых нейронов в каждом слое из  слоев, причем каждый аналоговый нейрон первых

слоев, причем каждый аналоговый нейрон первых  слоев реализует тождественную трансформацию, а аналоговый нейрон последнего слоя реализует функцию активации соответствующего нейрона вычисления, который соответствует соответствующей сети однослойного персептрона; и (iv) конструируют эквивалентную сеть с разреженными соединениями путем сцепления каждой эквивалентной пирамидоподобной подсети, включая сцепление ввода каждой эквивалентной пирамидоподобной подсети для

слоев реализует тождественную трансформацию, а аналоговый нейрон последнего слоя реализует функцию активации соответствующего нейрона вычисления, который соответствует соответствующей сети однослойного персептрона; и (iv) конструируют эквивалентную сеть с разреженными соединениями путем сцепления каждой эквивалентной пирамидоподобной подсети, включая сцепление ввода каждой эквивалентной пирамидоподобной подсети для  сетей однослойного персептрона, чтобы сформировать входной вектор с

сетей однослойного персептрона, чтобы сформировать входной вектор с  вводами. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этапы, на которых, для каждой сети однослойного персептрона из

вводами. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этапы, на которых, для каждой сети однослойного персептрона из  сетей однослойного персептрона: (i) устанавливают весовой вектор

сетей однослойного персептрона: (i) устанавливают весовой вектор  , причем iя строка матрицы

, причем iя строка матрицы  весов соответствует соответствующему нейрону вычисления, который соответствует соответствующей сети однослойного персептрона, где

весов соответствует соответствующему нейрону вычисления, который соответствует соответствующей сети однослойного персептрона, где  является соответствующим слоем соответствующего нейрона вычисления в CNN; и (ii) вычисляют весовой вектор

является соответствующим слоем соответствующего нейрона вычисления в CNN; и (ii) вычисляют весовой вектор  для соединений соответствующей эквивалентной пирамидоподобной подсети путем решения системы уравнений на основе весового вектора

для соединений соответствующей эквивалентной пирамидоподобной подсети путем решения системы уравнений на основе весового вектора  . Система уравнений включает в себя

. Система уравнений включает в себя  уравнений с

уравнений с  переменными, и

переменными, и  вычисляется с использованием уравнения

вычисляется с использованием уравнения  .

.

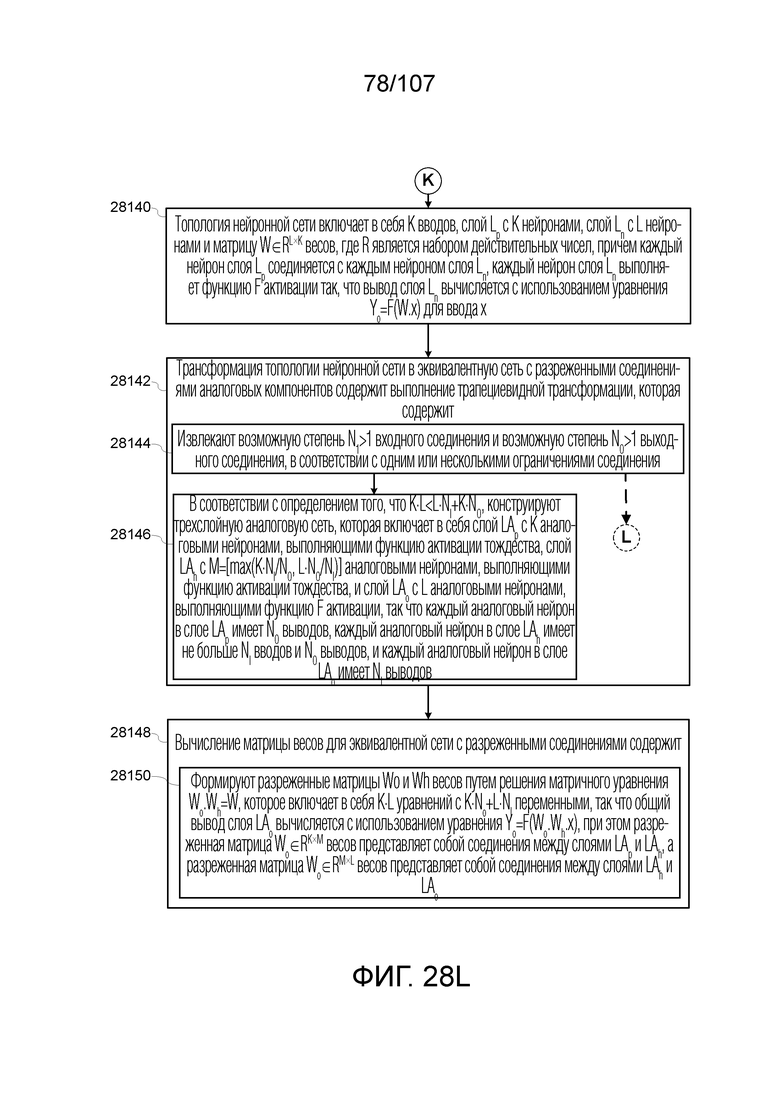

[0040] В некоторых вариантах осуществления, топология нейронной сети включает в себя  вводов, слой

вводов, слой  с

с  нейронами, слой

нейронами, слой  с

с  нейронами и матрицу

нейронами и матрицу  весов, где

весов, где  является набором действительных чисел, причем каждый нейрон слоя

является набором действительных чисел, причем каждый нейрон слоя  соединяется с каждым нейроном слоя

соединяется с каждым нейроном слоя  , причем каждый нейрон слоя

, причем каждый нейрон слоя  выполняет функцию

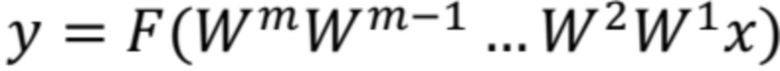

выполняет функцию  активации так, что вывод слоя

активации так, что вывод слоя  вычисляется с использованием уравнения

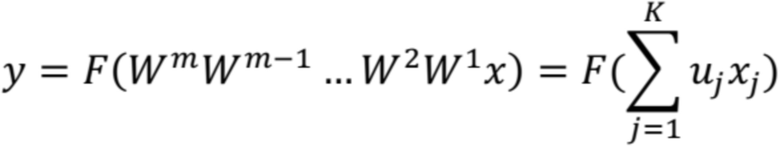

вычисляется с использованием уравнения  для ввода

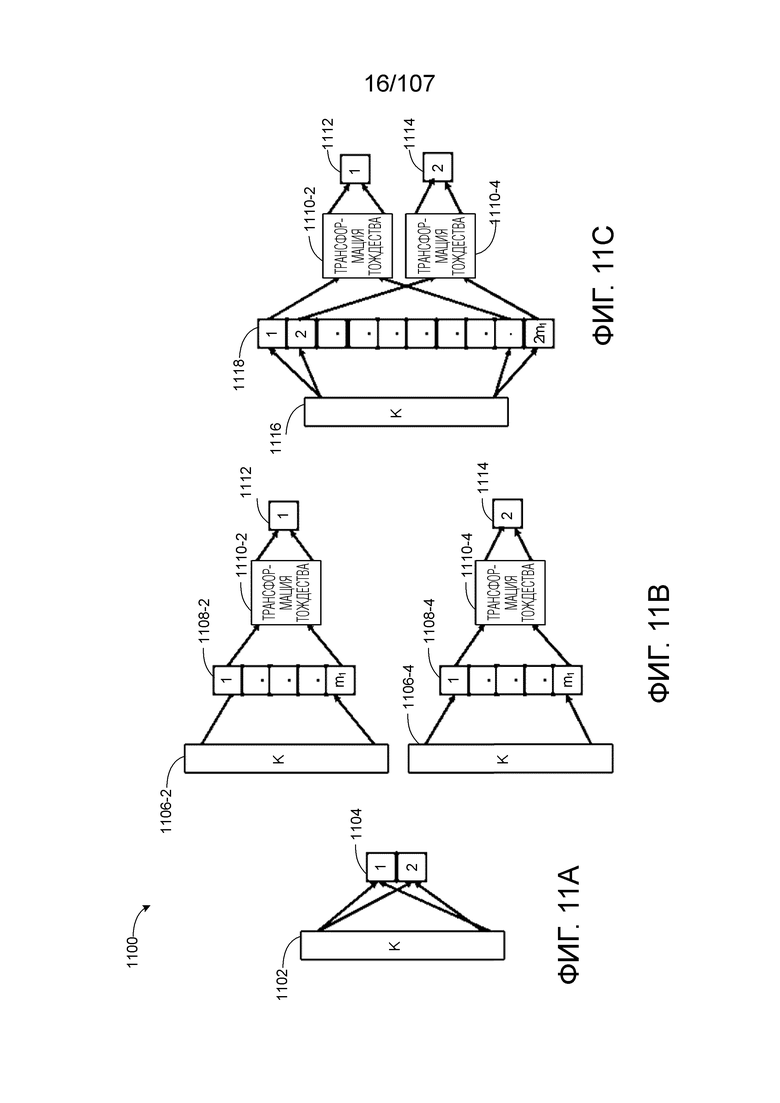

для ввода  . В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором выполняют трапециевидную трансформацию, которая включает в себя: (i) извлечение возможной степени

. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором выполняют трапециевидную трансформацию, которая включает в себя: (i) извлечение возможной степени  входного соединения и возможной степени

входного соединения и возможной степени  выходного соединения, в соответствии с одним или несколькими ограничениями соединения; (ii) в соответствии с определением того, что

выходного соединения, в соответствии с одним или несколькими ограничениями соединения; (ii) в соответствии с определением того, что  , конструирование трехслойной аналоговой сети, которая включает в себя слой

, конструирование трехслойной аналоговой сети, которая включает в себя слой  с

с  аналоговыми нейронами, выполняющими тождественную функцию активации, слой

аналоговыми нейронами, выполняющими тождественную функцию активации, слой  с

с  аналоговыми нейронами, выполняющими тождественную функцию активации, и слой

аналоговыми нейронами, выполняющими тождественную функцию активации, и слой  с

с  аналоговыми нейронами, выполняющими функцию

аналоговыми нейронами, выполняющими функцию  активации, так что каждый аналоговый нейрон в слое

активации, так что каждый аналоговый нейрон в слое  имеет

имеет  выводов, каждый аналоговый нейрон в слое

выводов, каждый аналоговый нейрон в слое  имеет не больше

имеет не больше  вводов и

вводов и  выводов, и каждый аналоговый нейрон в слое

выводов, и каждый аналоговый нейрон в слое  имеет

имеет  выводов. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этап, на котором формируют разреженные матрицы

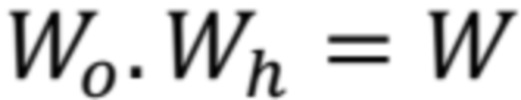

выводов. Также, в таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этап, на котором формируют разреженные матрицы  и

и  весов путем решения матричного уравнения

весов путем решения матричного уравнения  , которое включает в себя

, которое включает в себя  уравнений с

уравнений с  переменными, так что общий вывод слоя

переменными, так что общий вывод слоя  вычисляется с использованием уравнения

вычисляется с использованием уравнения  . Разреженная матрица

. Разреженная матрица  весов представляет собой соединения между слоями

весов представляет собой соединения между слоями  и

и  , а разреженная матрица

, а разреженная матрица  весов представляет собой соединения между слоями

весов представляет собой соединения между слоями  и

и  .

.

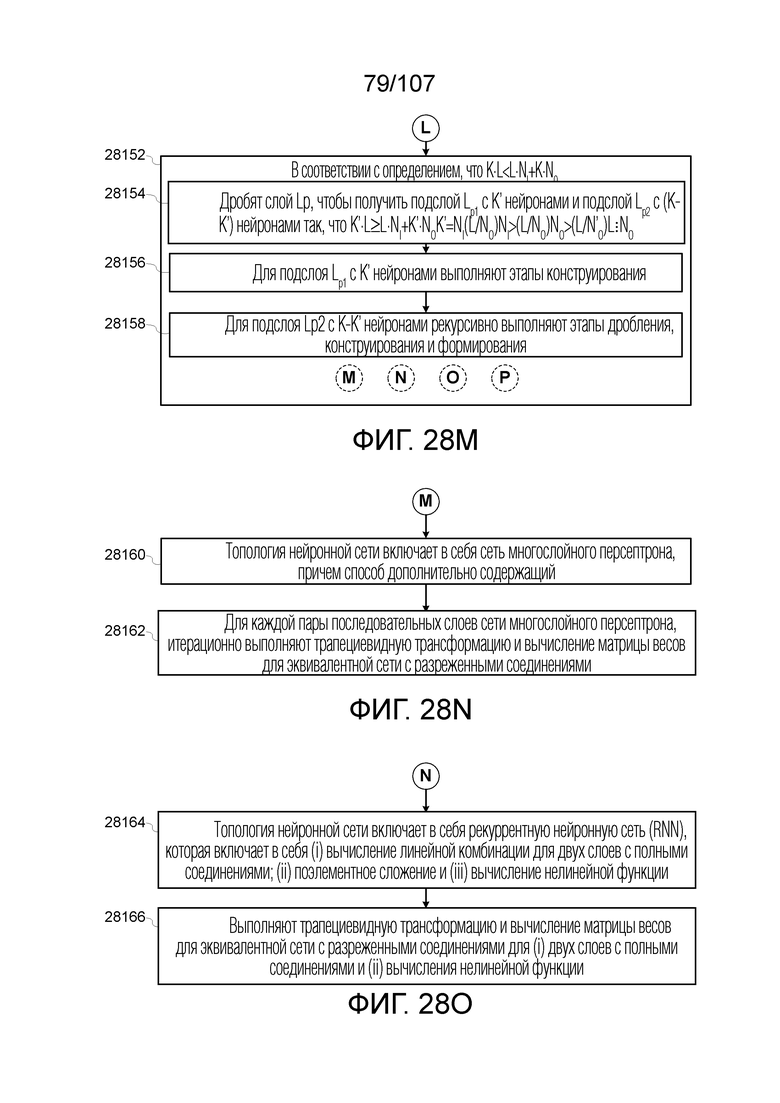

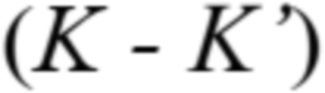

[0041] В некоторых вариантах осуществления, этап, на котором выполняют трапециевидную трансформацию, дополнительно включает в себя этапы, на которых: в соответствии с определением того, что  : (i) дробят слой

: (i) дробят слой  , чтобы получить подслой

, чтобы получить подслой  с

с  нейронами и подслой

нейронами и подслой  с

с  нейронами так, что

нейронами так, что  ; (ii) для подслоя

; (ii) для подслоя  с

с  нейронами, выполняют этапы конструирования и формирования; и (iii) для подслоя

нейронами, выполняют этапы конструирования и формирования; и (iii) для подслоя  с

с  нейронами, рекурсивно выполняют этапы дробления, конструирования и формирования.

нейронами, рекурсивно выполняют этапы дробления, конструирования и формирования.

[0042] В некоторых вариантах осуществления, топология нейронной сети включает в себя сеть многослойного персептрона. В таких случаях, способ дополнительно включает в себя этап, на котором, для каждой пары последовательных слоев сети многослойного персептрона, итерационно выполняют трапециевидную трансформацию и вычисление матрицы весов для эквивалентной сети с разреженными соединениями.

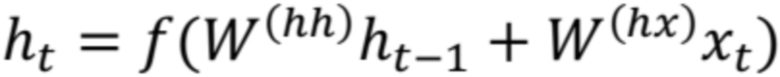

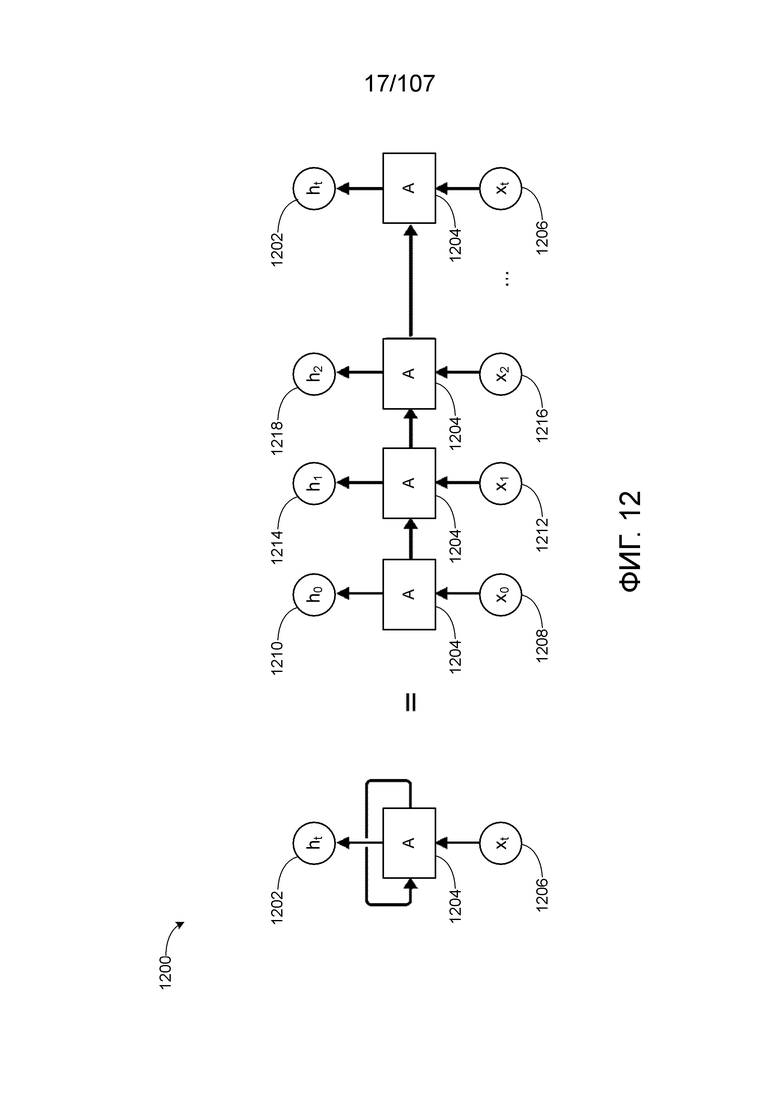

[0043] В некоторых вариантах осуществления, топология нейронной сети включает в себя рекуррентную нейронную сеть (RNN), которая включает в себя (i) вычисление линейной комбинации для двух слоев с полными соединениями; (ii) поэлементное сложение; и (iii) вычисление нелинейной функции. В таких случаях, способ дополнительно включает в себя этап, на котором выполняют трапециевидную трансформацию и вычисление матрицы весов для эквивалентной сети с разреженными соединениями для (i) двух слоев с полными соединениями и (ii) вычисления нелинейной функции.

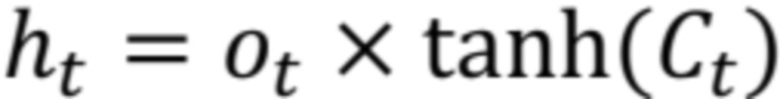

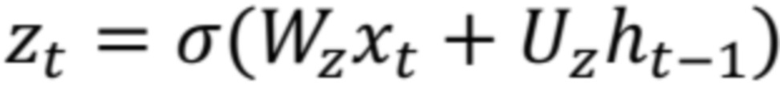

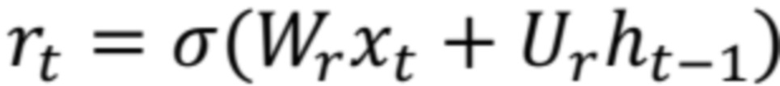

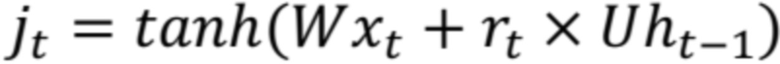

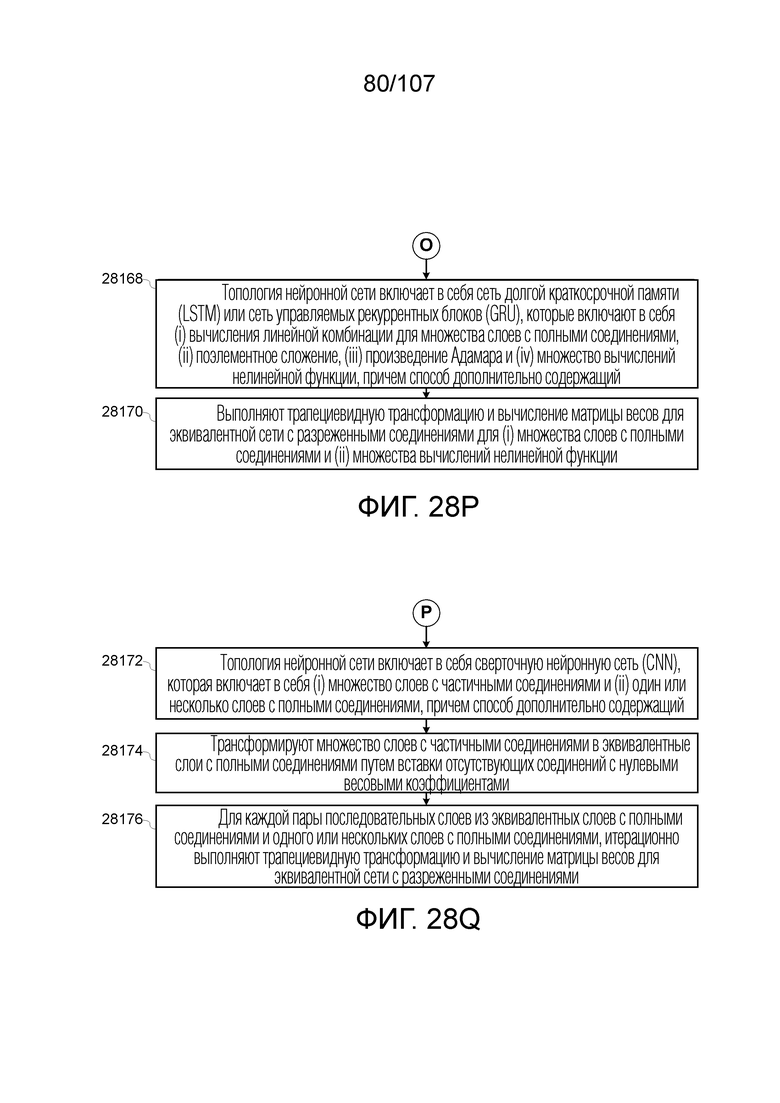

[0044] В некоторых вариантах осуществления, топология нейронной сети включает в себя сеть долгой краткосрочной памяти (LSTM) или сеть управляемых рекуррентных блоков (GRU), которые включают в себя (i) вычисления линейной комбинации для множества слоев с полными соединениями, (ii) поэлементное сложение, (iii) произведение Адамара и (iv) множество вычислений нелинейной функции. В таких случаях, способ дополнительно включает в себя этап, на котором выполняют трапециевидную трансформацию и вычисление матрицы весов для эквивалентной сети с разреженными соединениями для (i) множества слоев с полными соединениями и (ii) множества вычислений нелинейной функции.

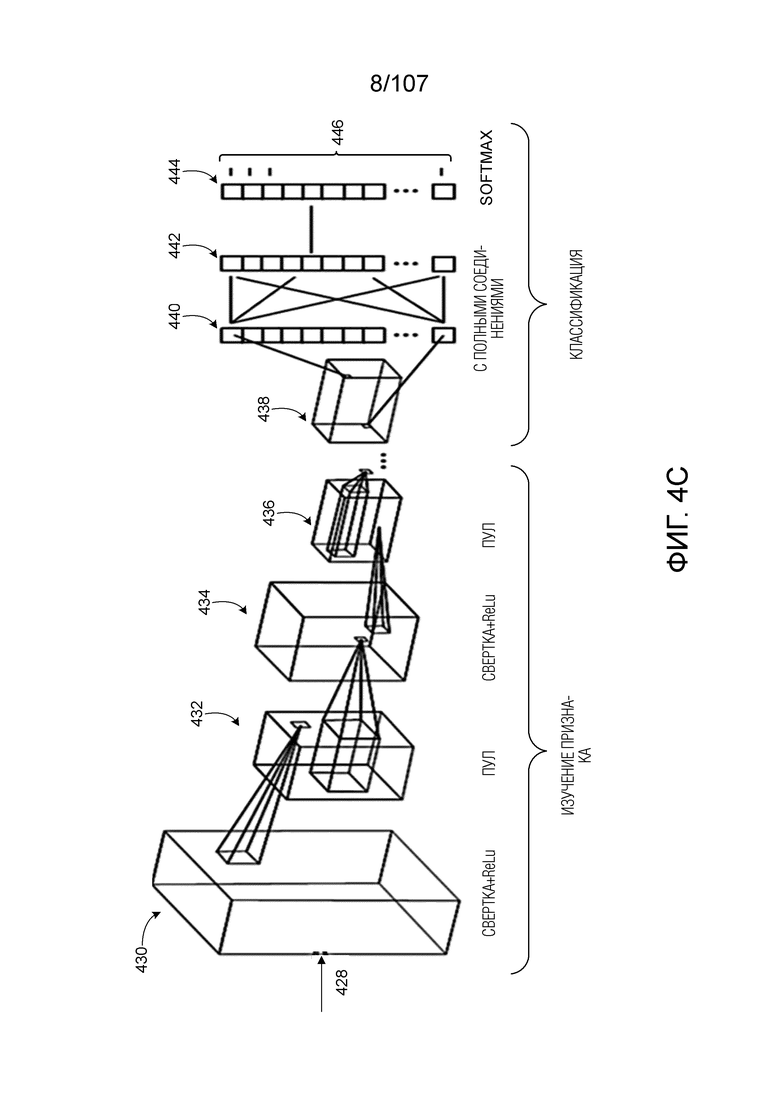

[0045] В некоторых вариантах осуществления, топология нейронной сети включает в себя сверточную нейронную сеть (CNN), которая включает в себя (i) множество слоев с частичными соединениями и (ii) один или несколько слоев с полными соединениями. В таких случаях, способ дополнительно включает в себя этапы, на которых: (i) трансформируют множество слоев с частичными соединениями в эквивалентные слои с полными соединениями путем вставки отсутствующих соединений с нулевыми весовыми коэффициентами; и (ii) для каждой пары последовательных слоев из эквивалентных слоев с полными соединениями и одного или нескольких слоев с полными соединениями, итерационно выполняют трапециевидную трансформацию и вычисление матрицы весов для эквивалентной сети с разреженными соединениями.

[0046] В некоторых вариантах осуществления, топология нейронной сети включает в себя  вводов,

вводов,  выходных нейронов и матрицу

выходных нейронов и матрицу  весов, где

весов, где  является набором действительных чисел, причем каждый выходной нейрон выполняет функцию

является набором действительных чисел, причем каждый выходной нейрон выполняет функцию  активации. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором выполняют трансформацию аппроксимации, который включает в себя этапы, на которых: (i) извлекают возможную степень

активации. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этап, на котором выполняют трансформацию аппроксимации, который включает в себя этапы, на которых: (i) извлекают возможную степень  входного соединения и возможную степень

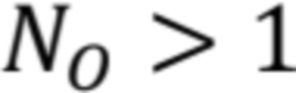

входного соединения и возможную степень  выходного соединения, в соответствии с одним или несколькими ограничениями соединения; (ii) выбирают параметр

выходного соединения, в соответствии с одним или несколькими ограничениями соединения; (ii) выбирают параметр  из набора

из набора  ; (iii) в соответствии с определением того, что

; (iii) в соответствии с определением того, что  , конструируют пирамидальную нейронную сеть, которая формирует первые

, конструируют пирамидальную нейронную сеть, которая формирует первые  слоев эквивалентной сети с разреженными соединениями, так что пирамидальная нейронная сеть имеет

слоев эквивалентной сети с разреженными соединениями, так что пирамидальная нейронная сеть имеет  нейронов в ее выходном слое. Каждый нейрон в пирамидальной нейронной сети выполняет тождественную функцию; и (iv) конструируют трапециевидную нейронную сеть с

нейронов в ее выходном слое. Каждый нейрон в пирамидальной нейронной сети выполняет тождественную функцию; и (iv) конструируют трапециевидную нейронную сеть с  вводами и

вводами и  выводами. Каждый нейрон в последнем слое трапециевидной нейронной сети выполняет функцию

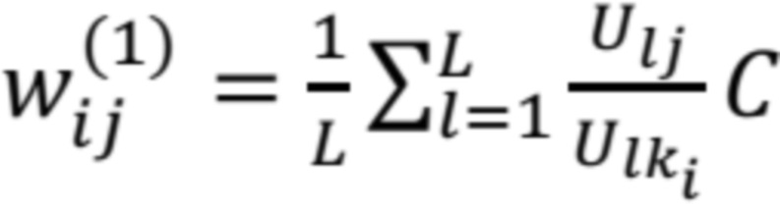

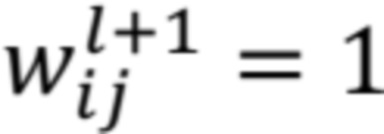

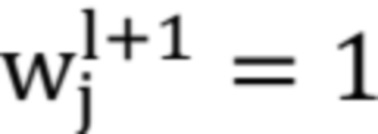

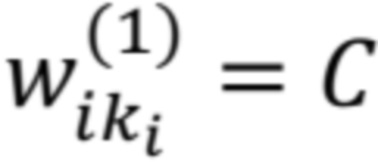

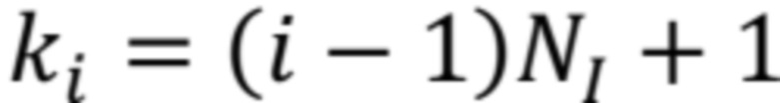

выводами. Каждый нейрон в последнем слое трапециевидной нейронной сети выполняет функцию  активации, а все другие нейроны выполняют тождественную функцию. В таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этапы, на которых: (i) формируют весовые коэффициенты для пирамидальной нейронной сети, включая (a) установку весовых коэффициентов каждого нейрона i первого слоя пирамидальной нейронной сети в соответствии со следующим правилом: (a)

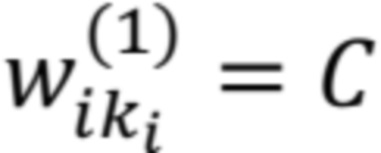

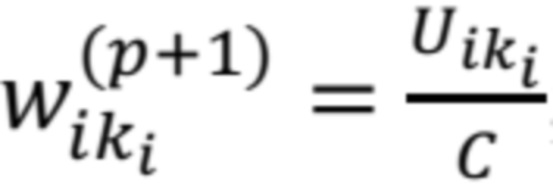

активации, а все другие нейроны выполняют тождественную функцию. В таких случаях, этап, на котором вычисляют матрицу весов для эквивалентной сети с разреженными соединениями, включает в себя этапы, на которых: (i) формируют весовые коэффициенты для пирамидальной нейронной сети, включая (a) установку весовых коэффициентов каждого нейрона i первого слоя пирамидальной нейронной сети в соответствии со следующим правилом: (a)  .

.  является ненулевой константой, а

является ненулевой константой, а  ; и (b)

; и (b)  , для всех весовых коэффициентов j нейрона за исключением

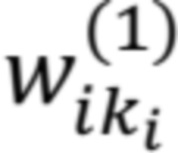

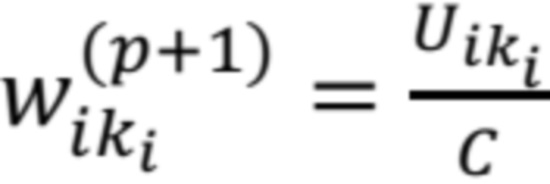

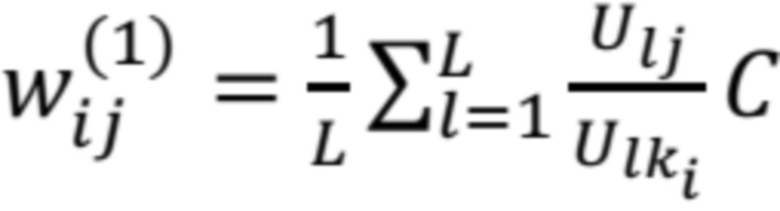

, для всех весовых коэффициентов j нейрона за исключением  ; и (b) установку всех других весовых коэффициентов пирамидальной нейронной сети в 1; и (ii) формируют весовые коэффициенты для трапециевидной нейронной сети, включая (a) установку весовых коэффициентов каждого нейрона i первого слоя трапециевидной нейронной сети в соответствии с уравнением

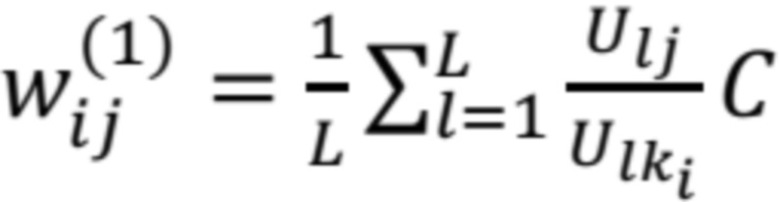

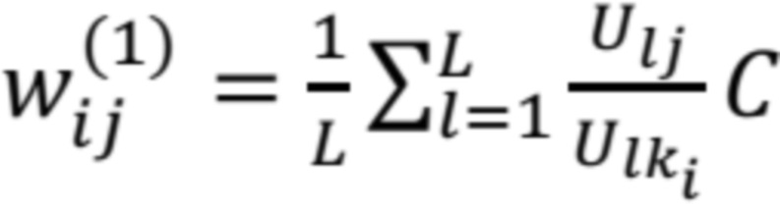

; и (b) установку всех других весовых коэффициентов пирамидальной нейронной сети в 1; и (ii) формируют весовые коэффициенты для трапециевидной нейронной сети, включая (a) установку весовых коэффициентов каждого нейрона i первого слоя трапециевидной нейронной сети в соответствии с уравнением  и (b) установку других весовых коэффициентов трапециевидной нейронной сети в 1.

и (b) установку других весовых коэффициентов трапециевидной нейронной сети в 1.

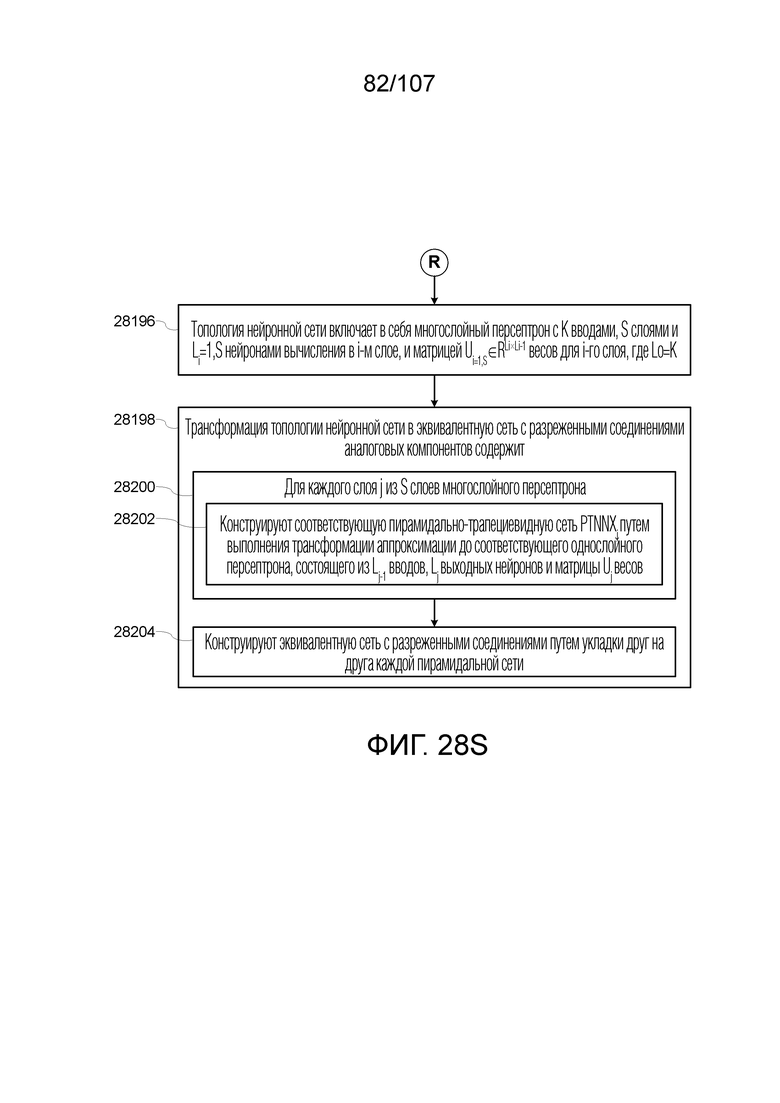

[0047] В некоторых вариантах осуществления, топология нейронной сети включает в себя многослойный персептрон с  вводами,

вводами,  слоями и

слоями и  нейронами вычисления в i-м слое, и матрицей

нейронами вычисления в i-м слое, и матрицей  весов для i-го слоя, где

весов для i-го слоя, где  . В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: для каждого слоя

. В таких случаях, этап, на котором трансформируют топологию нейронной сети в эквивалентную сеть с разреженными соединениями аналоговых компонентов, включает в себя этапы, на которых: для каждого слоя  из

из  слоев многослойного персептрона: (i) конструируют соответствующую пирамидально-трапециевидную сеть PTNNXj путем выполнения трансформации аппроксимации до соответствующего однослойного персептрона, состоящего из

слоев многослойного персептрона: (i) конструируют соответствующую пирамидально-трапециевидную сеть PTNNXj путем выполнения трансформации аппроксимации до соответствующего однослойного персептрона, состоящего из  вводов,

вводов,  выходных нейронов и матрицы

выходных нейронов и матрицы  весов; и (ii) конструируют эквивалентную сеть с разреженными соединениями путем укладки друг на друга каждой пирамидальной трапециевидной сети.

весов; и (ii) конструируют эквивалентную сеть с разреженными соединениями путем укладки друг на друга каждой пирамидальной трапециевидной сети.

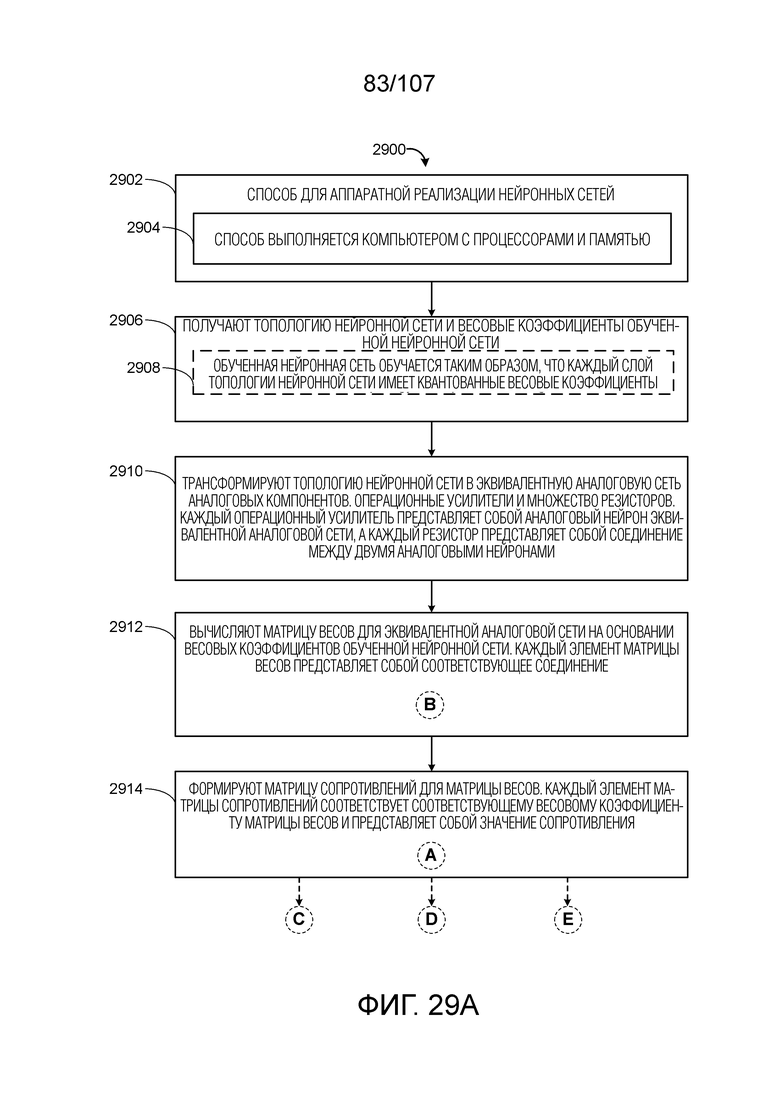

[0048] В другом аспекте, предоставляется способ для аппаратной реализации нейронных сетей, в соответствии с некоторыми вариантами осуществления. Способ включает в себя этап, на котором получат топологию нейронной сети и весовые коэффициенты обученной нейронной сети. Способ также включает в себя этап, на котором трансформируют топологию нейронной сети в эквивалентную аналоговую сеть аналоговых компонентов, включающих в себя множество операционных усилителей и множество резисторов. Каждый операционный усилитель представляет собой аналоговый нейрон эквивалентной аналоговой сети, а каждый резистор представляет собой соединение между двумя аналоговыми нейронами. Способ также включает в себя этап, на котором вычисляют матрицу весов для эквивалентной аналоговой сети на основе весовых коэффициентов обученной нейронной сети. Каждый элемент матрицы весов представляет собой соответствующее соединение. Способ также включает в себя этап, на котором формируют матрицу сопротивлений для матрицы весов. Каждый элемент матрицы сопротивлений соответствует соответствующему весовому коэффициенту матрицы весов и представляет собой значение сопротивления.

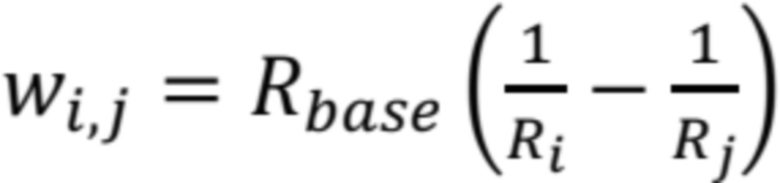

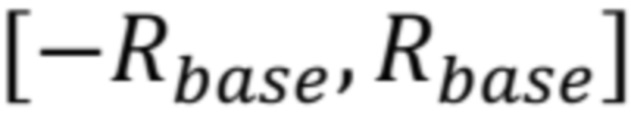

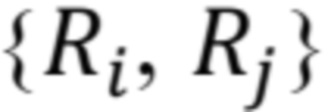

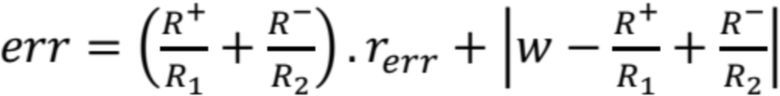

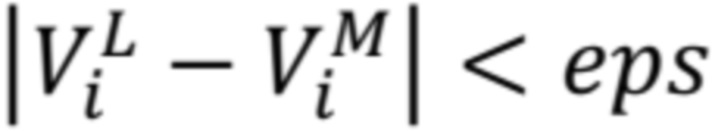

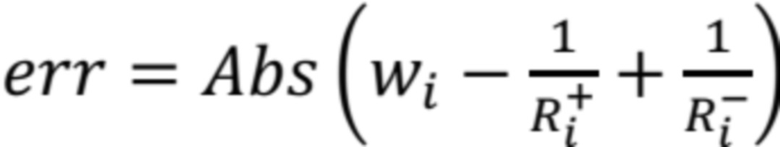

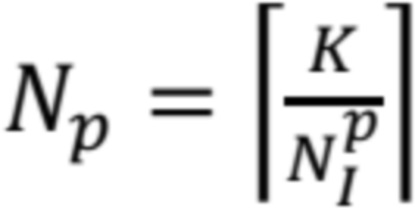

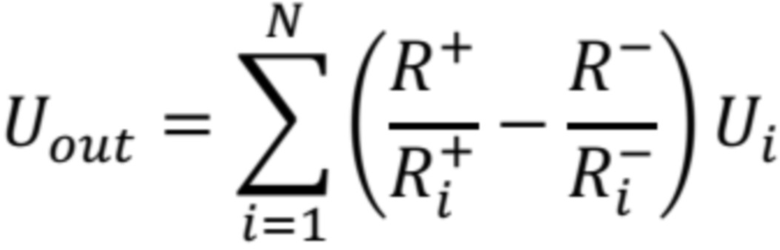

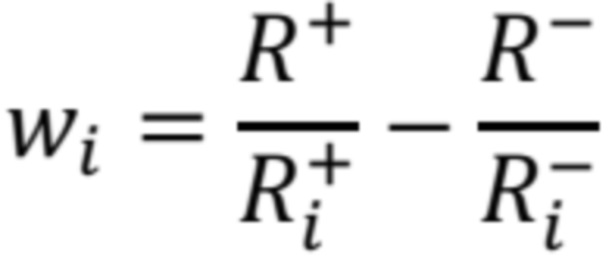

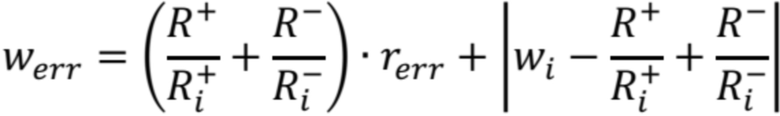

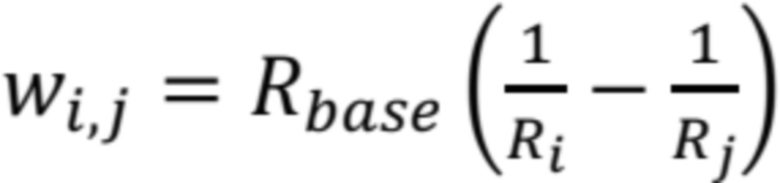

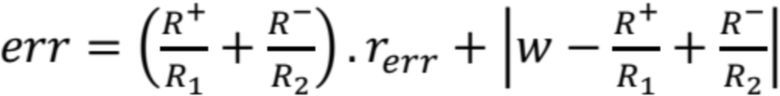

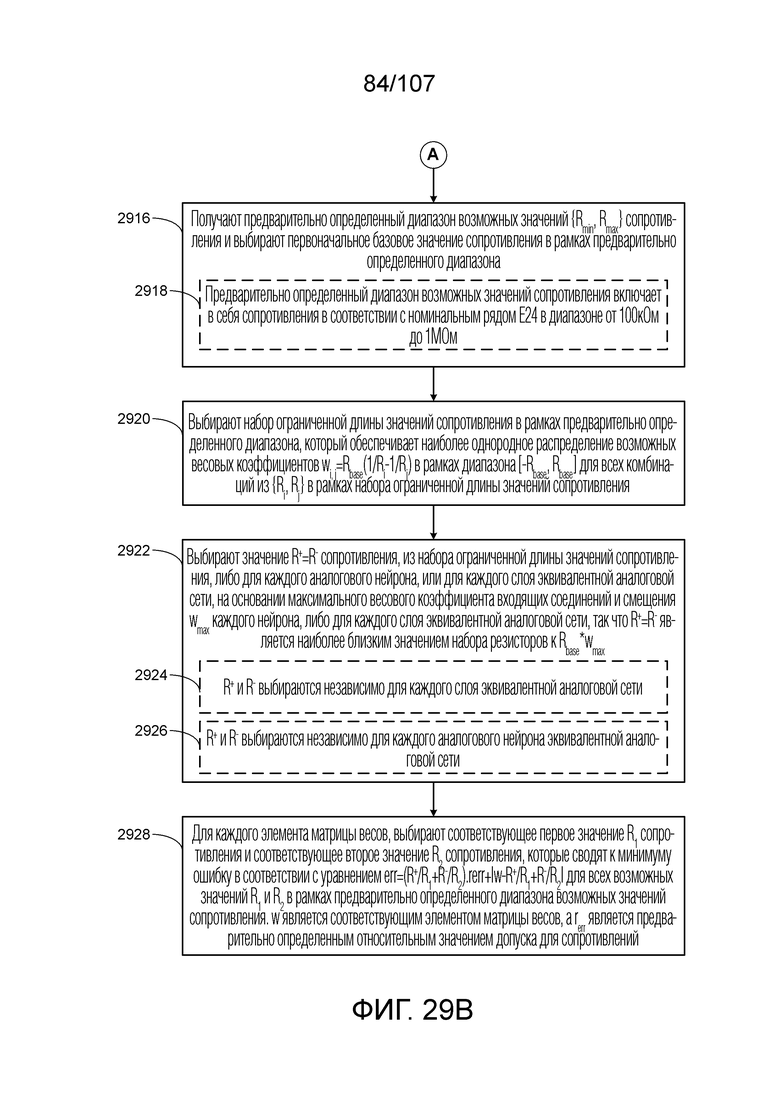

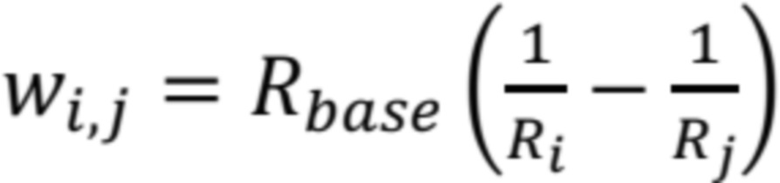

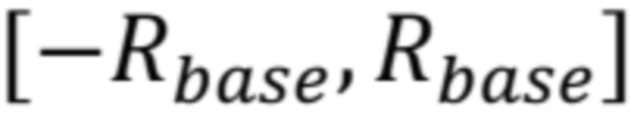

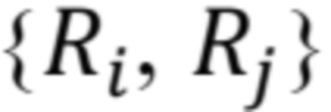

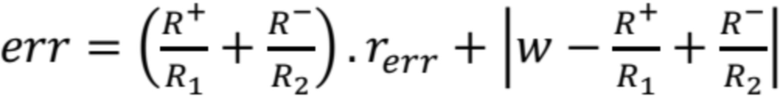

[0049] В некоторых вариантах осуществления, этап, на котором формируют матрицу сопротивлений для матрицы весов, включает в себя этапы, на которых: (i) получают предварительно определенный диапазон  возможных значений сопротивления и выбирают первоначальное базовое значение

возможных значений сопротивления и выбирают первоначальное базовое значение  сопротивления в рамках предварительно определенного диапазона; (ii) выбирают набор ограниченной длины значений сопротивления, в рамках предварительно определенного диапазона, который обеспечивает наиболее однородное распределение возможных весовых коэффициентов

сопротивления в рамках предварительно определенного диапазона; (ii) выбирают набор ограниченной длины значений сопротивления, в рамках предварительно определенного диапазона, который обеспечивает наиболее однородное распределение возможных весовых коэффициентов  в рамках диапазона

в рамках диапазона  для всех комбинаций из

для всех комбинаций из  в рамках набора ограниченной длины значений сопротивления; (iii) выбирают значение

в рамках набора ограниченной длины значений сопротивления; (iii) выбирают значение  сопротивления, из набора ограниченной длины значений сопротивления, либо для каждого аналогового нейрона, или для каждого слоя эквивалентной аналоговой сети, на основе максимального весового коэффициента входящих соединений и смещения

сопротивления, из набора ограниченной длины значений сопротивления, либо для каждого аналогового нейрона, или для каждого слоя эквивалентной аналоговой сети, на основе максимального весового коэффициента входящих соединений и смещения  каждого нейрона, либо для каждого слоя эквивалентной аналоговой сети, так что

каждого нейрона, либо для каждого слоя эквивалентной аналоговой сети, так что  является наиболее близким значением набора резисторов к

является наиболее близким значением набора резисторов к  ; и (iv) для каждого элемента матрицы весов, выбирают соответствующее первое значение

; и (iv) для каждого элемента матрицы весов, выбирают соответствующее первое значение  сопротивления и соответствующее второе значение

сопротивления и соответствующее второе значение  сопротивления, которые сводят к минимуму ошибку в соответствии с уравнением

сопротивления, которые сводят к минимуму ошибку в соответствии с уравнением  для всех возможных значений

для всех возможных значений  и

и  в рамках предварительно определенного диапазона возможных значений сопротивления.

в рамках предварительно определенного диапазона возможных значений сопротивления.  является соответствующим элементом матрицы весов, а

является соответствующим элементом матрицы весов, а  является предварительно определенным относительным значением допуска для сопротивлений.

является предварительно определенным относительным значением допуска для сопротивлений.

[0050] В некоторых вариантах осуществления, предварительно определенный диапазон возможных значений сопротивления включает в себя сопротивления в соответствии с номинальным рядом E24 в диапазоне от 100кОм до 1МОм.

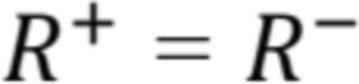

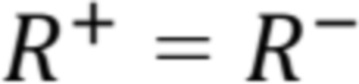

[0051] В некоторых вариантах осуществления,  и

и  выбираются независимо для каждого слоя эквивалентной аналоговой сети.

выбираются независимо для каждого слоя эквивалентной аналоговой сети.

[0052] В некоторых вариантах осуществления,  и

и  выбираются независимо для каждого аналогового нейрона эквивалентной аналоговой сети.

выбираются независимо для каждого аналогового нейрона эквивалентной аналоговой сети.

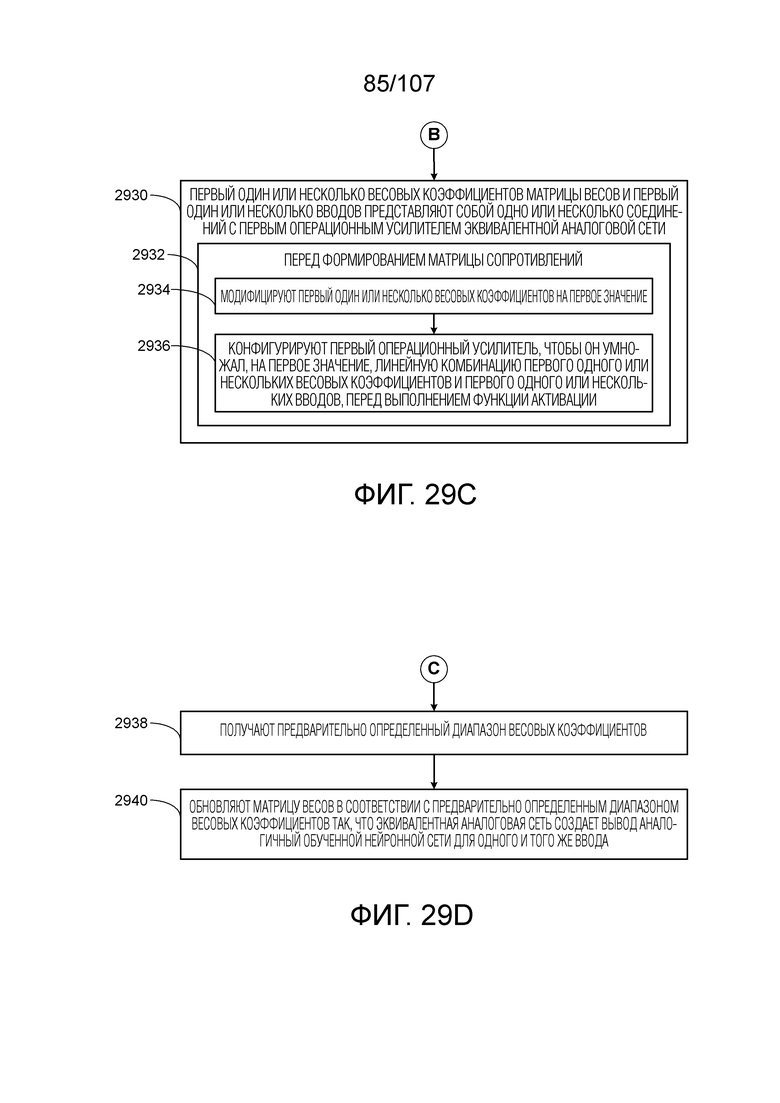

[0053] В некоторых вариантах осуществления, первый один или несколько весовых коэффициентов матрицы весов и первый один или несколько вводов представляют собой одно или несколько соединений с первым операционным усилителем эквивалентной аналоговой сети. В таких случаях, способ дополнительно включает в себя этапы, на которых перед этапом, на котором формируют матрицу сопротивлений: (i) модифицируют первый один или несколько весовых коэффициентов на первое значение; и (ii) конфигурируют первый операционный усилитель, чтобы он умножал, на первое значение, линейную комбинацию первого одного или нескольких весовых коэффициентов и первого одного или нескольких вводов, перед выполнением функции активации.

[0054] В некоторых вариантах осуществления, способ дополнительно включает в себя этапы, на которых: (i) получают предварительно определенный диапазон весовых коэффициентов; и (ii) обновляют матрицу весов в соответствии с предварительно определенным диапазоном весовых коэффициентов так, что эквивалентная аналоговая сеть создает вывод аналогичный обученной нейронной сети для одного и того же ввода.

[0055] В некоторых вариантах осуществления, обученная нейронная сеть обучается так, что каждый слой топологии нейронной сети имеет квантованные весовые коэффициенты.

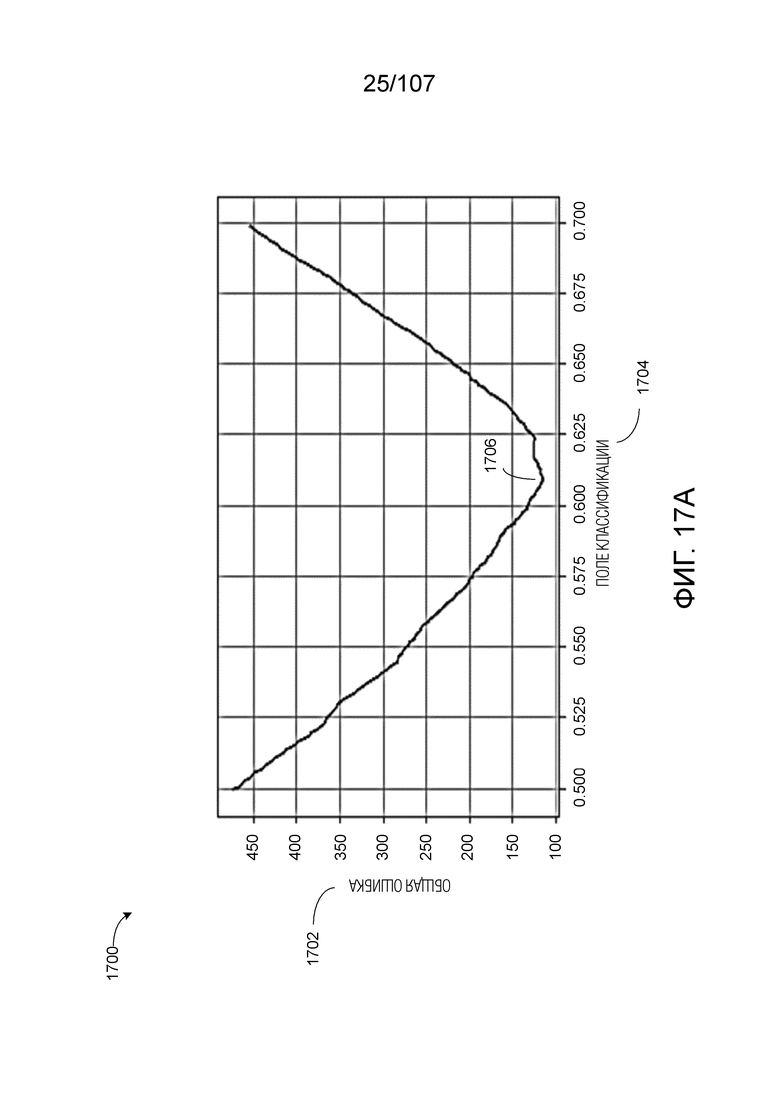

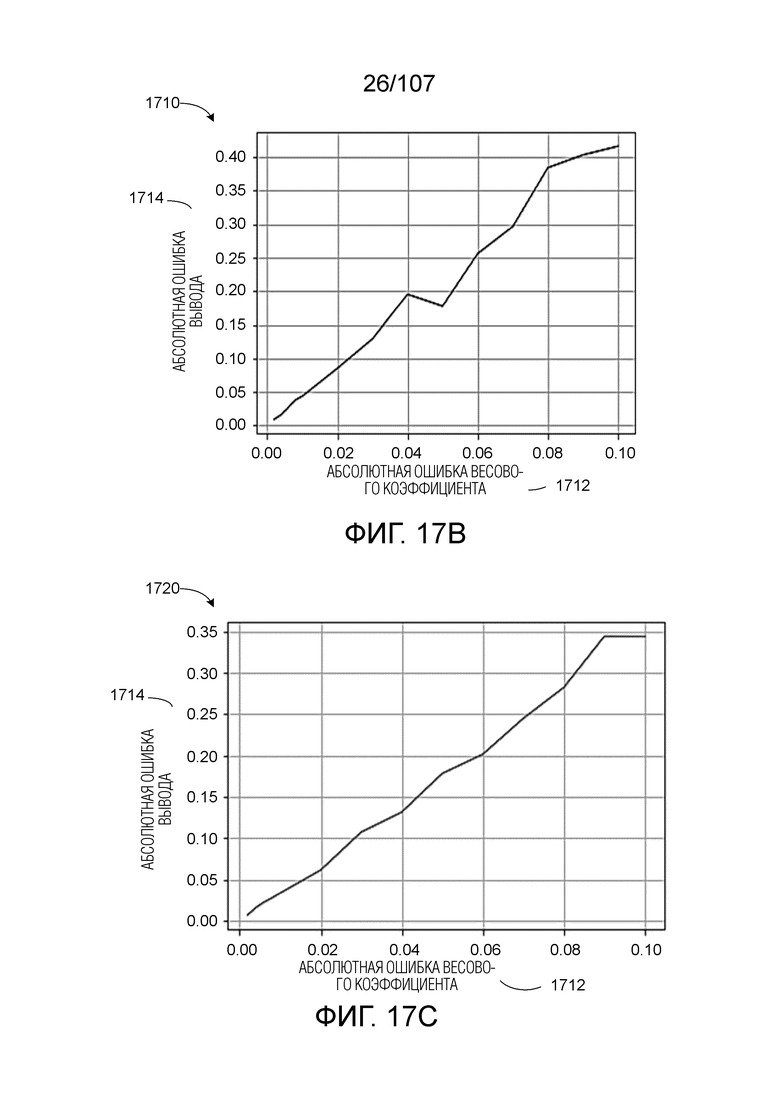

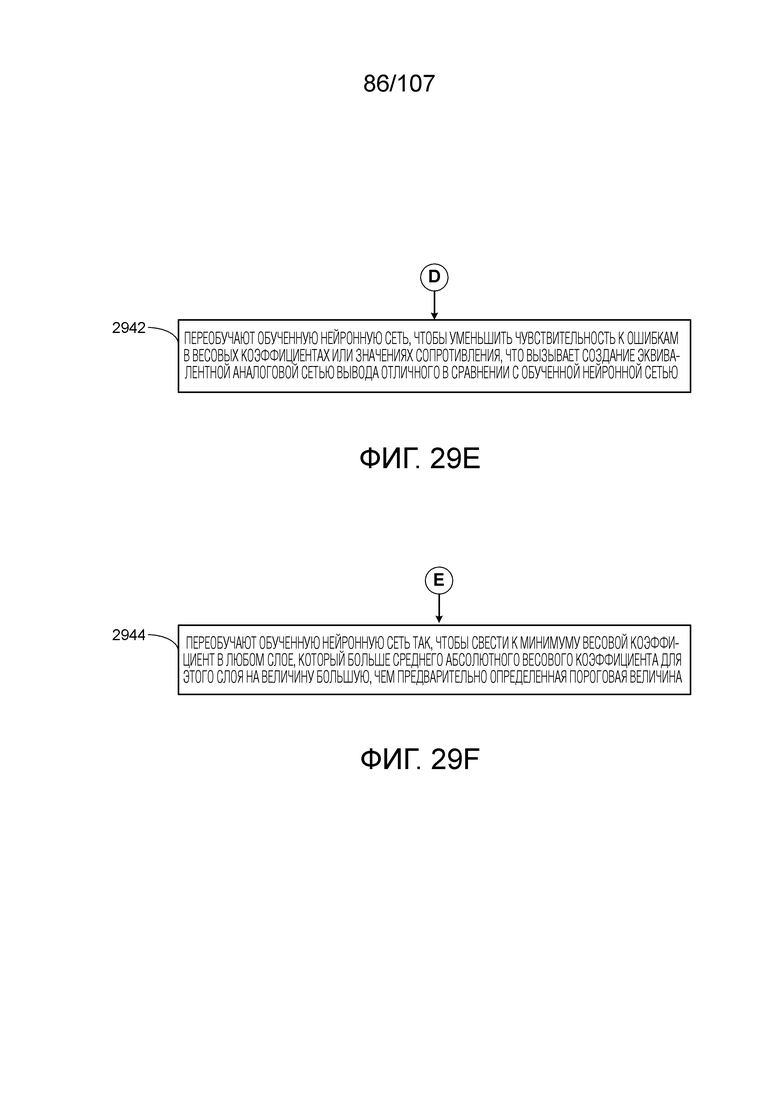

[0056] В некоторых вариантах осуществления, способ дополнительно включает в себя этап, на котором переобучают обученную нейронную сеть, чтобы уменьшить чувствительность к ошибкам в весовых коэффициентах или значениях сопротивления, что вызывает создание эквивалентной аналоговой сетью вывода отличного в сравнении с обученной нейронной сетью.

[0057] В некоторых вариантах осуществления, способ дополнительно включает в себя этап, на котором переобучают обученную нейронную сеть так, чтобы свести к минимуму весовой коэффициент в любом слое, который больше среднего абсолютного весового коэффициента для этого слоя на величину большую, чем предварительно определенная пороговая величина.

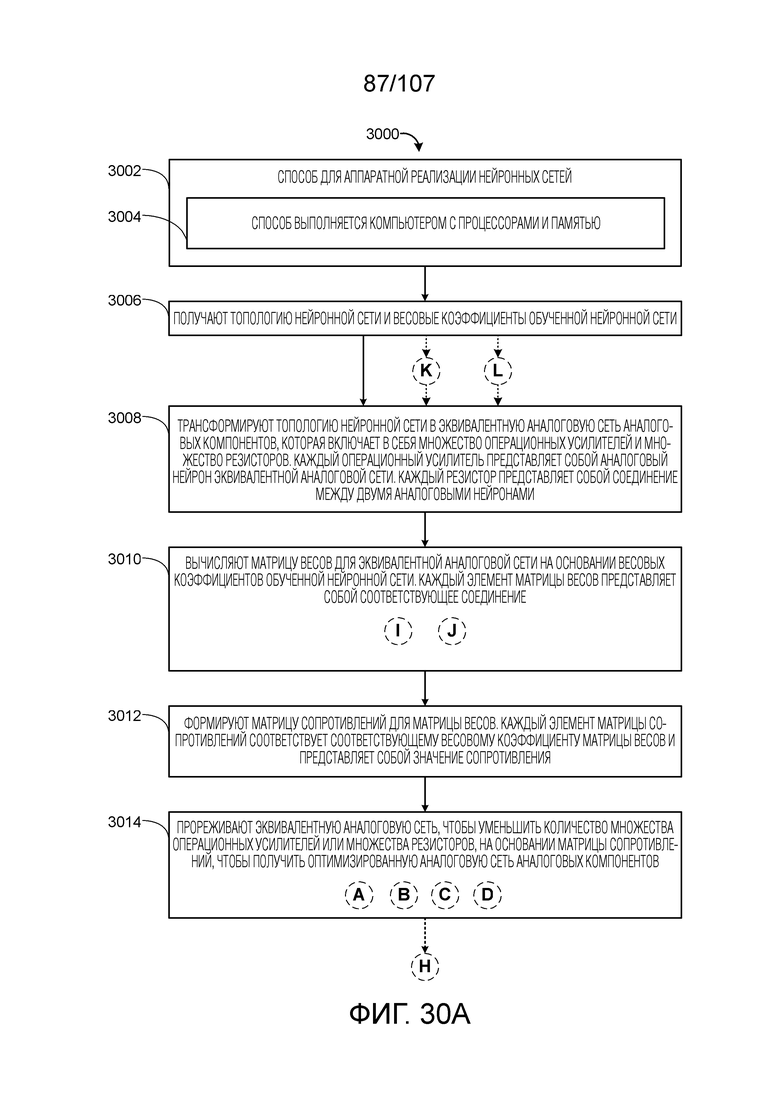

[0058] В другом аспекте, предоставляется способ для аппаратной реализации нейронных сетей, в соответствии с некоторыми вариантами осуществления. Способ включает в себя этап, на котором получают топологию нейронной сети и весовые коэффициенты обученной нейронной сети. Способ также включает в себя этап, на котором трансформируют топологию нейронной сети в эквивалентную аналоговую сеть аналоговых компонентов, включающих в себя множество операционных усилителей и множество резисторов. Каждый операционный усилитель представляет собой аналоговый нейрон эквивалентной аналоговой сети, а каждый резистор представляет собой соединение между двумя аналоговыми нейронами. Способ также включает в себя этап, на котором вычисляют матрицу весов для эквивалентной аналоговой сети на основе весовых коэффициентов обученной нейронной сети. Каждый элемент матрицы весов представляет собой соответствующее соединение. Способ также включает в себя этап, на котором формируют матрицу сопротивлений для матрицы весов. Каждый элемент матрицы сопротивлений соответствует соответствующему весовому коэффициенту матрицы весов. Способ также включает в себя этап, на котором прореживают эквивалентную аналоговую сеть, чтобы уменьшить количество множества операционных усилителей или множества резисторов, на основе матрицы сопротивлений, чтобы получить оптимизированную аналоговую сеть аналоговых компонентов.

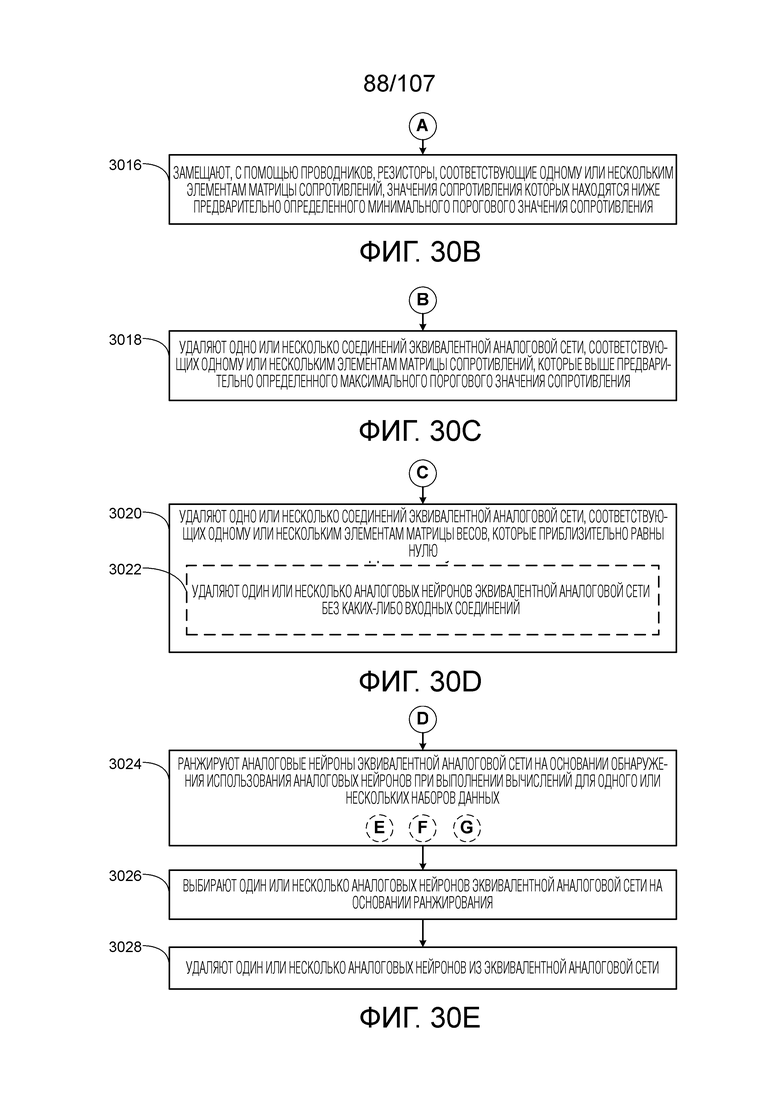

[0059] В некоторых вариантах осуществления, этап, на котором прореживают эквивалентную аналоговую сеть, включает в себя этап, на котором замещают, с помощью проводников, резисторы, соответствующие одному или нескольким элементам матрицы сопротивлений, значения сопротивления которых находятся ниже предварительно определенного минимального порогового значения сопротивления.

[0060] В некоторых вариантах осуществления, этап, на котором прореживают эквивалентную аналоговую сеть, включает в себя этап, на котором удаляют одно или несколько соединений эквивалентной аналоговой сети, соответствующих одному или нескольким элементам матрицы сопротивлений, которые выше предварительно определенного максимального порогового значения сопротивления.

[0061] В некоторых вариантах осуществления, этап, на котором прореживают эквивалентную аналоговую сеть, включает в себя этап, на котором удаляют одно или несколько соединений эквивалентной аналоговой сети, соответствующих одному или нескольким элементам матрицы весов, которые приблизительно равны нулю.

[0062] В некоторых вариантах осуществления, этап, на котором прореживают эквивалентную аналоговую сеть, дополнительно включает в себя этап, на котором удаляют один или несколько аналоговых нейронов эквивалентной аналоговой сети без каких-либо входных соединений.

[0063] В некоторых вариантах осуществления, этап, на котором прореживают эквивалентную аналоговую сеть, включает в себя этапы, на которых: (i) ранжируют аналоговые нейроны эквивалентной аналоговой сети на основе обнаружения использования аналоговых нейронов при выполнении вычислений для одного или нескольких наборов данных; (ii) выбирают один или несколько аналоговых нейронов эквивалентной аналоговой сети на основе ранжирования; и (iii) удаляют один или несколько аналоговых нейронов из эквивалентной аналоговой сети.

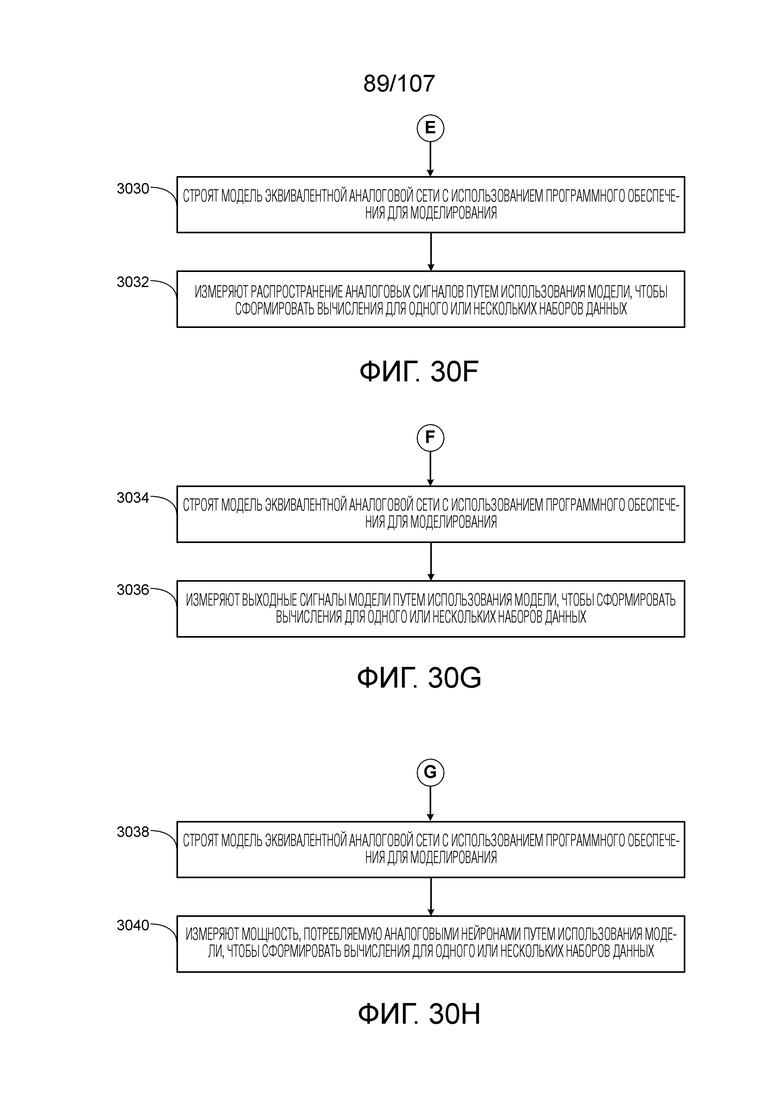

[0064] В некоторых вариантах осуществления, этап, на котором обнаруживают использование аналогового нейрона, включает в себя этапы, на которых: (i) строят модель эквивалентной аналоговой сети с использованием программного обеспечения для моделирования; и (ii) измеряют распространение аналоговых сигналов путем использования модели, чтобы сформировать вычисления для одного или нескольких наборов данных.

[0065] В некоторых вариантах осуществления, этап, на котором обнаруживают использование аналогового нейрона, включает в себя этапы, на которых: (i) строят модель эквивалентной аналоговой сети с использованием программного обеспечения для моделирования; и (ii) измеряют выходные сигналы модели путем использования модели, чтобы сформировать вычисления для одного или нескольких наборов данных.

[0066] В некоторых вариантах осуществления, этап, на котором обнаруживают использование аналоговых нейронов, включает в себя этапы, на которых: (i) строят модель эквивалентной аналоговой сети с использованием программного обеспечения для моделирования; и (ii) измеряют мощность, потребляемую аналоговыми нейронами, путем использования модели, чтобы сформировать вычисления для одного или нескольких наборов данных.

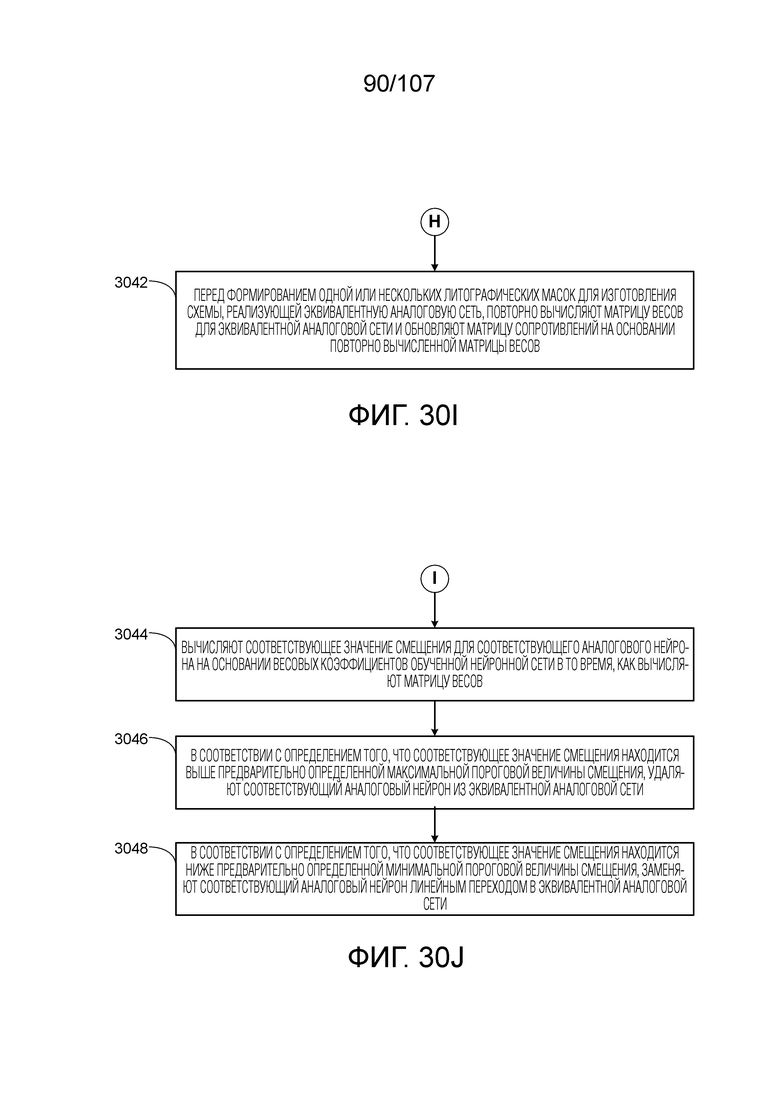

[0067] В некоторых вариантах осуществления, способ дополнительно включает в себя вслед за этапом, на котором прореживают эквивалентную аналоговую сеть, и перед этапом, на котором формируют одну или несколько литографических масок для изготовления схемы, реализующей эквивалентную аналоговую сеть, этап, на котором повторно вычисляют матрицу весов для эквивалентной аналоговой сети и обновляют матрицу сопротивлений на основе повторно вычисленной матрицы весов.

[0068] В некоторых вариантах осуществления, способ дополнительно включает в себя этапы, на которых, для каждого аналогового нейрона эквивалентной аналоговой сети: (i) вычисляют соответствующее значение смещения для соответствующего аналогового нейрона на основе весовых коэффициентов обученной нейронной сети в то время, как вычисляют матрицу весов; (ii) в соответствии с определением того, что соответствующее значение смещения находится выше предварительно определенной максимальной пороговой величины смещения, удаляют соответствующий аналоговый нейрон из эквивалентной аналоговой сети; и (iii) в соответствии с определением того, что соответствующее значение смещения находится ниже предварительно определенной минимальной пороговой величины смещения, заменяют соответствующий аналоговый нейрон линейным переходом в эквивалентной аналоговой сети.

[0069] В некоторых вариантах осуществления, способ дополнительно включает в себя этап, на котором уменьшают количество нейронов эквивалентной аналоговой сети, перед этапом, на котором формируют матрицу весов, путем увеличения количества соединений от одного или нескольких аналоговых нейронов эквивалентной аналоговой сети.

[0070] В некоторых вариантах осуществления, способ дополнительно включает в себя этап, на котором прореживают обученную нейронную сеть, чтобы обновить топологию нейронной сети и весовые коэффициенты обученной нейронной сети, перед этапом, на котором трансформируют топологию нейронной сети, с использованием методик прореживания для нейронных сетей, так что эквивалентная аналоговая сеть включает в себя меньше предварительно определенного количества аналоговых компонентов.

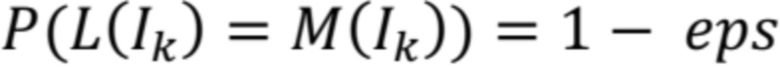

[0071] В некоторых вариантах осуществления, этап, на котором прореживают, выполняется итерационно с учетом точности или уровня совпадения вывода между обученной нейронной сетью и эквивалентной аналоговой сетью.

[0072] В некоторых вариантах осуществления, способ дополнительно включает в себя этап, на котором, перед этапом, на котором трансформируют топологию нейронной сети в эквивалентную аналоговую сеть, выполняют выделение знаний сети.

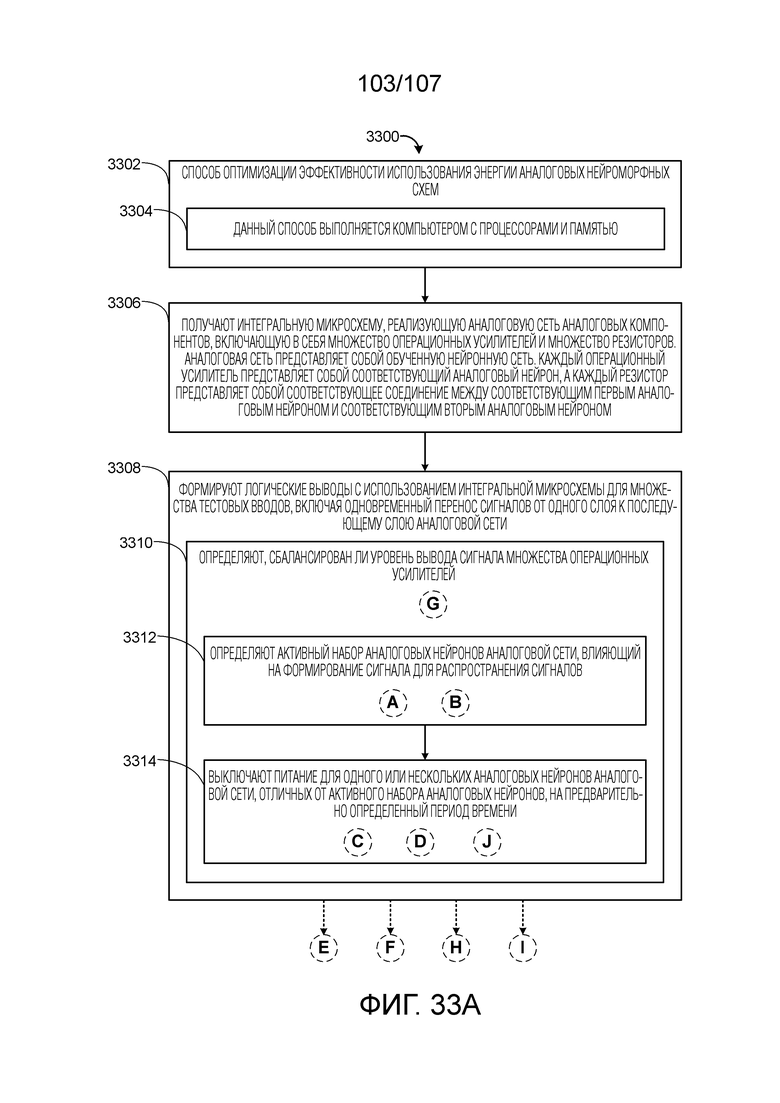

[0073] В другом аспекте, предоставляется интегральная микросхема, в соответствии с некоторыми вариантами осуществления. Интегральная микросхема включает в себя аналоговую сеть аналоговых компонентов, изготовленную способом, который включает в себя этапы, на которых: (i) получают топологию нейронной сети и весовые коэффициенты обученной нейронной сети; (ii) трансформируют топологию нейронной сети в эквивалентную аналоговую сеть аналоговых компонентов, включающих в себя множество операционных усилителей и множество резисторов. Каждый операционный усилитель представляет собой соответствующий аналоговый нейрон, а каждый резистор представляет собой соответствующее соединение между соответствующим первым аналоговым нейроном и соответствующим вторым аналоговым нейроном; (iii) вычисляют матрицу весов для эквивалентной аналоговой сети на основе весовых коэффициентов обученной нейронной сети. Каждый элемент матрицы весов представляет собой соответствующее соединение; (iv) формируют матрицу сопротивлений для матрицы весов. Каждый элемент матрицы сопротивлений соответствует соответствующему весовому коэффициенту матрицы весов; (v) формируют одну или несколько литографических масок для изготовления схемы, реализующей эквивалентную аналоговую сеть аналоговых компонентов на основе матрицы сопротивлений; и (vi) изготавливают схему на основе одной или нескольких литографических масок с использованием литографического процесса.

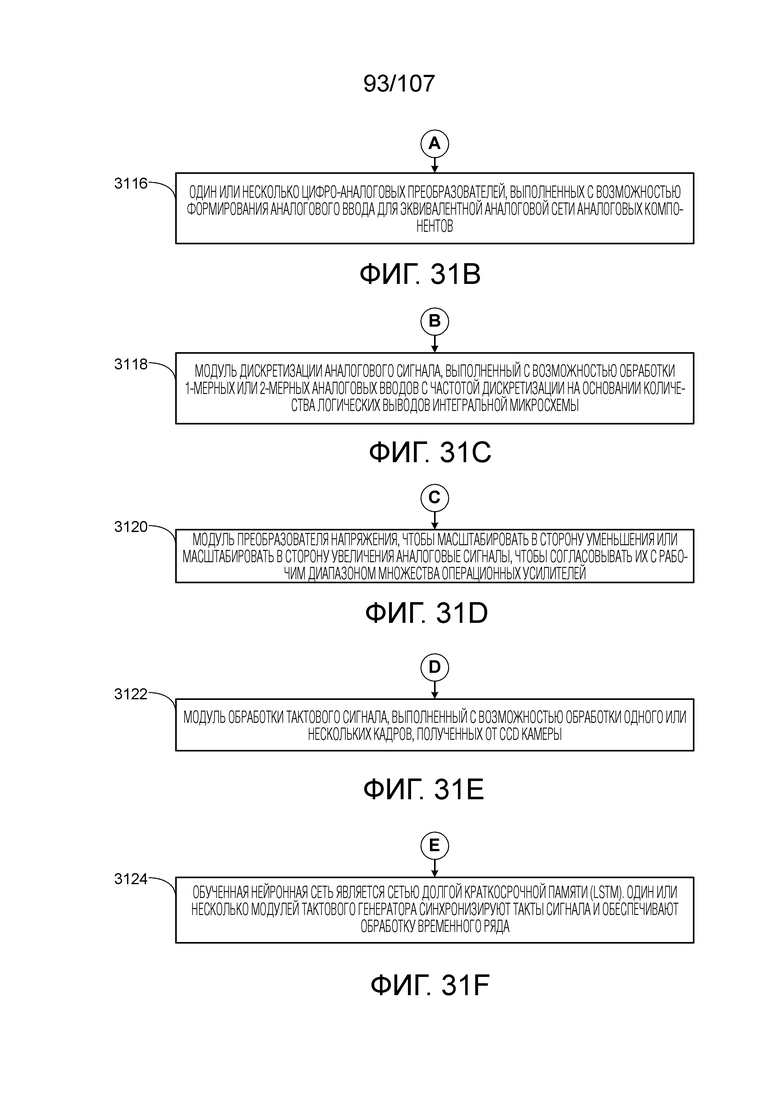

[0074] В некоторых вариантах осуществления, интегральная микросхема дополнительно включает в себя один или несколько цифро-аналоговых преобразователей, выполненных с возможностью формирования аналогового ввода для эквивалентной аналоговой сети аналоговых компонентов на основе одного или нескольких цифровых сигналов.

[0075] В некоторых вариантах осуществления, интегральная микросхема дополнительно включает в себя модуль дискретизации аналогового сигнала, выполненный с возможностью обработки 1-мерных или 2-мерных аналоговых вводов с частотой дискретизации на основе количества логических выводов интегральной микросхемы.

[0076] В некоторых вариантах осуществления, интегральная микросхема дополнительно включает в себя модуль преобразователя напряжения, чтобы масштабировать в сторону уменьшения или масштабировать в сторону увеличения аналоговые сигналы, чтобы согласовывать их с рабочим диапазоном множества операционных усилителей.

[0077] В некоторых вариантах осуществления, интегральная микросхема дополнительно включает в себя модуль обработки тактового сигнала, выполненный с возможностью обработки одного или нескольких кадров, полученных от CCD камеры.

[0078] В некоторых вариантах осуществления, обученная нейронная сеть является сетью долгой краткосрочной памяти (LSTM). В таких случаях, интегральная микросхема дополнительно включает в себя один или несколько модулей тактового генератора, чтобы синхронизировать такты сигнала и для обеспечения обработки временного ряда.

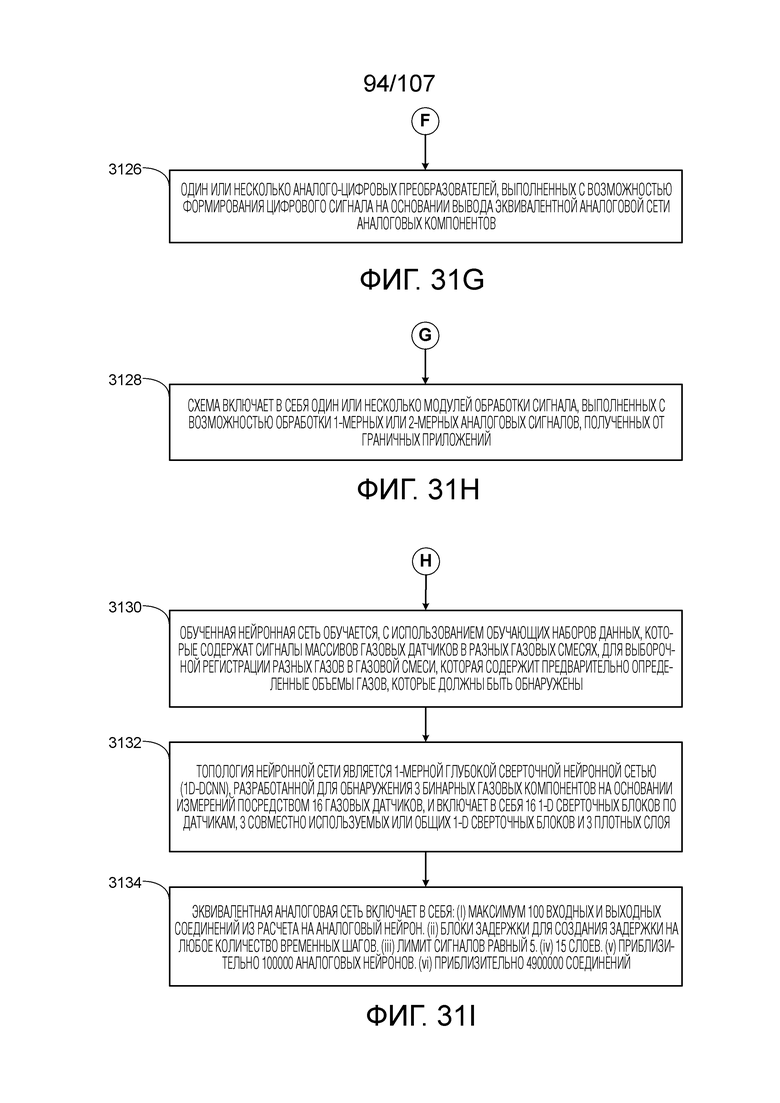

[0079] В некоторых вариантах осуществления, интегральная микросхема дополнительно включает в себя один или несколько аналого-цифровых преобразователей, выполненных с возможностью формирования цифрового сигнала на основе вывода эквивалентной аналоговой сети аналоговых компонентов.

[0080] В некоторых вариантах осуществления, интегральная микросхема дополнительно включает в себя один или несколько модулей обработки сигнала, выполненных с возможностью обработки 1-мерных или 2-мерных аналоговых сигналов, полученных от граничных приложений.

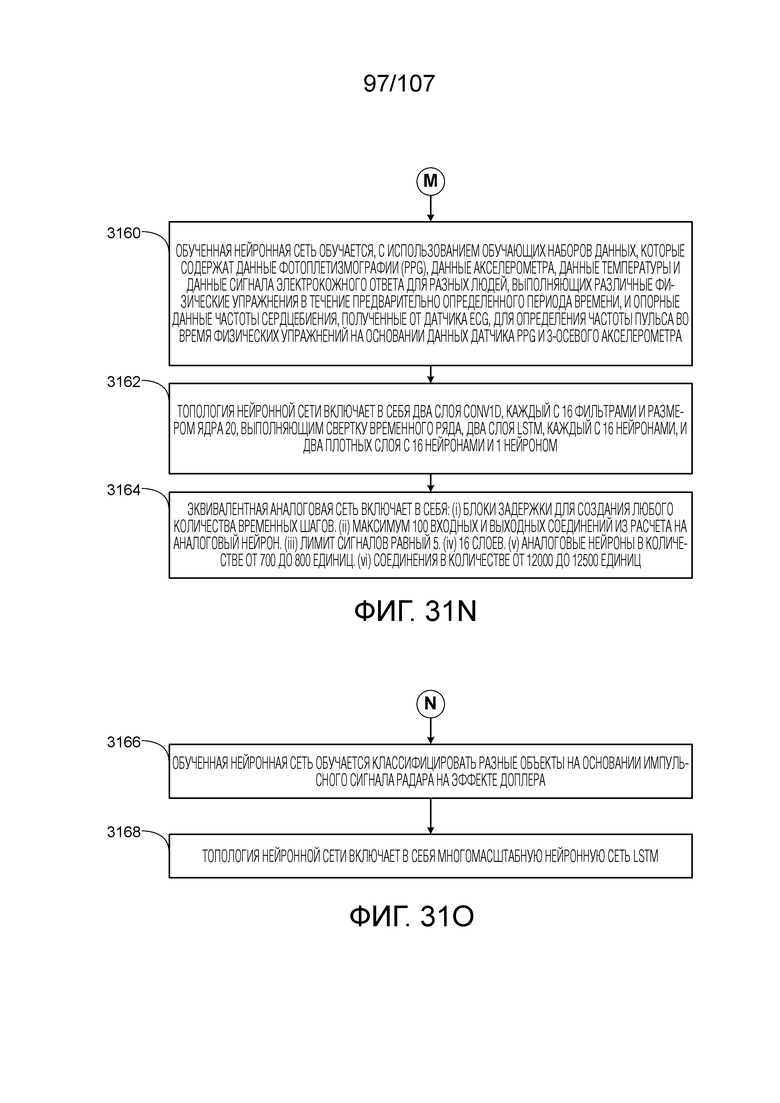

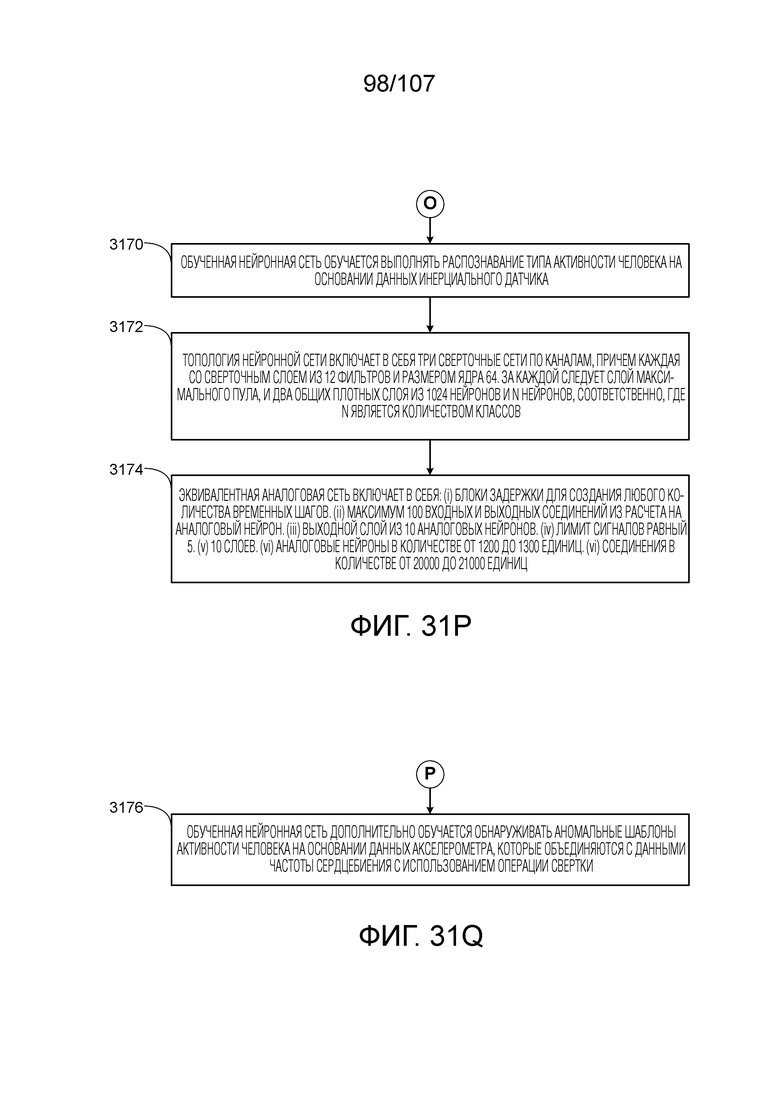

[0081] В некоторых вариантах осуществления, обученная нейронная сеть обучается с использованием обучающих наборов данных, содержащих сигналы массивов газовых датчиков в разных газовых смесях, для выборочной регистрации разных газов в газовой смеси, содержащей предварительно определенные объемы газов, которые должны быть обнаружены. В таких случаях, топология нейронной сети является 1-Мерной Глубокой Сверточной Нейронной сетью (1D-DCNN), разработанной для обнаружения 3 бинарных газовых компонентов на основе измерений посредством 16 газовых датчиков, и включает в себя 16 1-D сверточных блоков по датчикам, 3 совместно используемых или общих 1-D сверточных блоков и 3 плотных слоя. В таких случаях, эквивалентная аналоговая сеть включает в себя: (i) максимум 100 входных и выходных соединений из расчета на аналоговый нейрон, (ii) блоки задержки для создания задержки на любое количество временных шагов, (iii) лимит сигналов равный 5, (iv) 15 слоев, (v) приблизительно 100000 аналоговых нейронов и (vi) приблизительно 4900000 соединений.

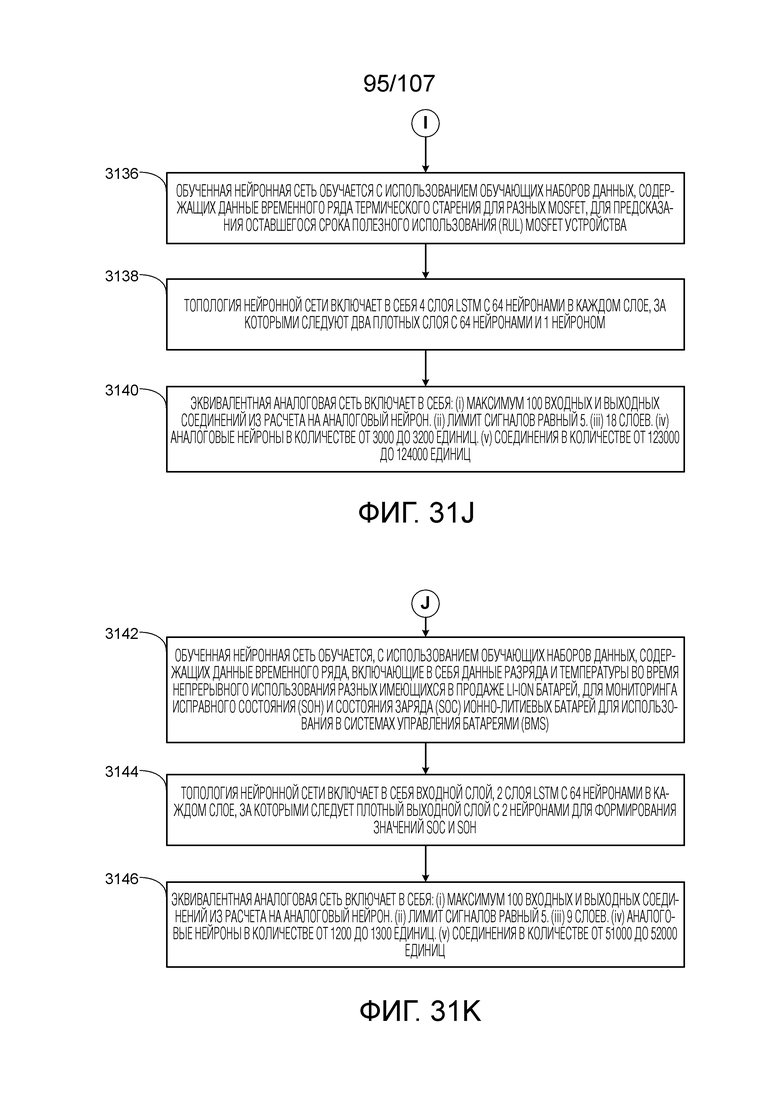

[0082] В некоторых вариантах осуществления, обученная нейронная сеть обучается с использованием обучающих наборов данных, содержащих данные временного ряда термического старения для разных MOSFET, для предсказания оставшегося срока полезного использования (RUL) MOSFET устройства. В таких случаях, топология нейронной сети включает в себя 4 слоя LSTM с 64 нейронами в каждом слое, за которыми следуют два плотных слоя с 64 нейронами и 1 нейроном, соответственно. В таких случаях, эквивалентная аналоговая сеть включает в себя: (i) максимум 100 входных и выходных соединений из расчета на аналоговый нейрон, (ii) лимит сигналов равный 5, (iii) 18 слоев, (iv) аналоговые нейроны в количестве от 3000 до 3200 единиц, и (v) соединения в количестве от 123000 до 124000 единиц.

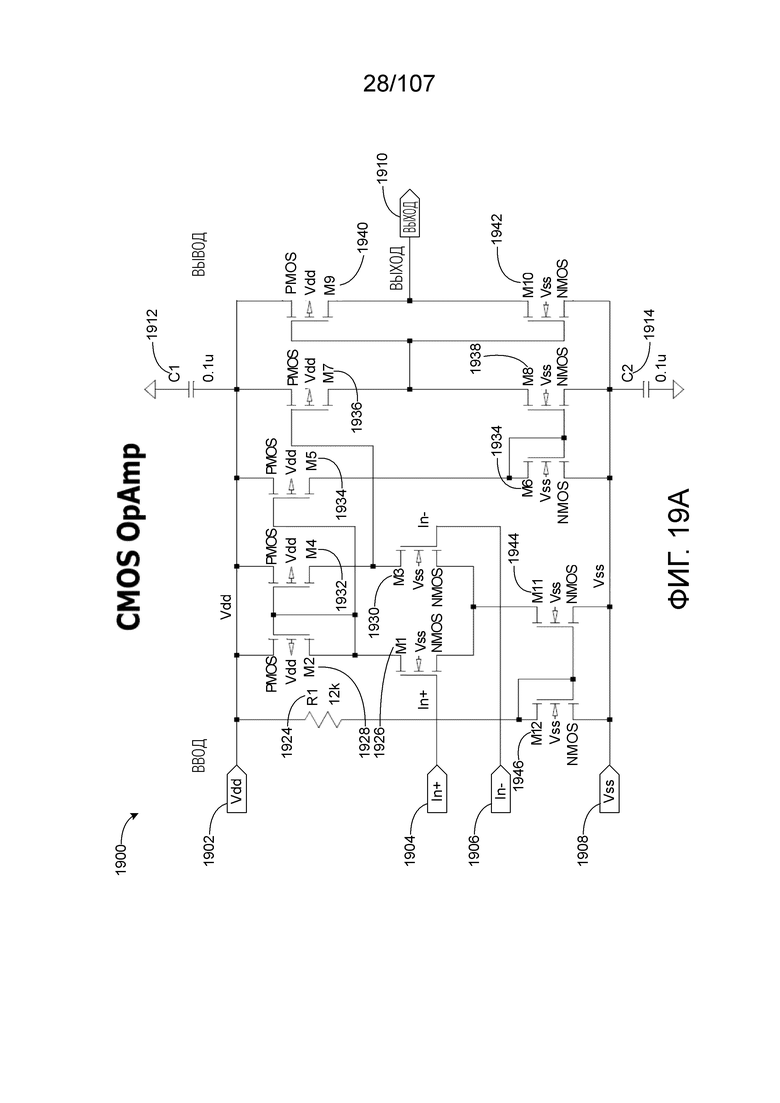

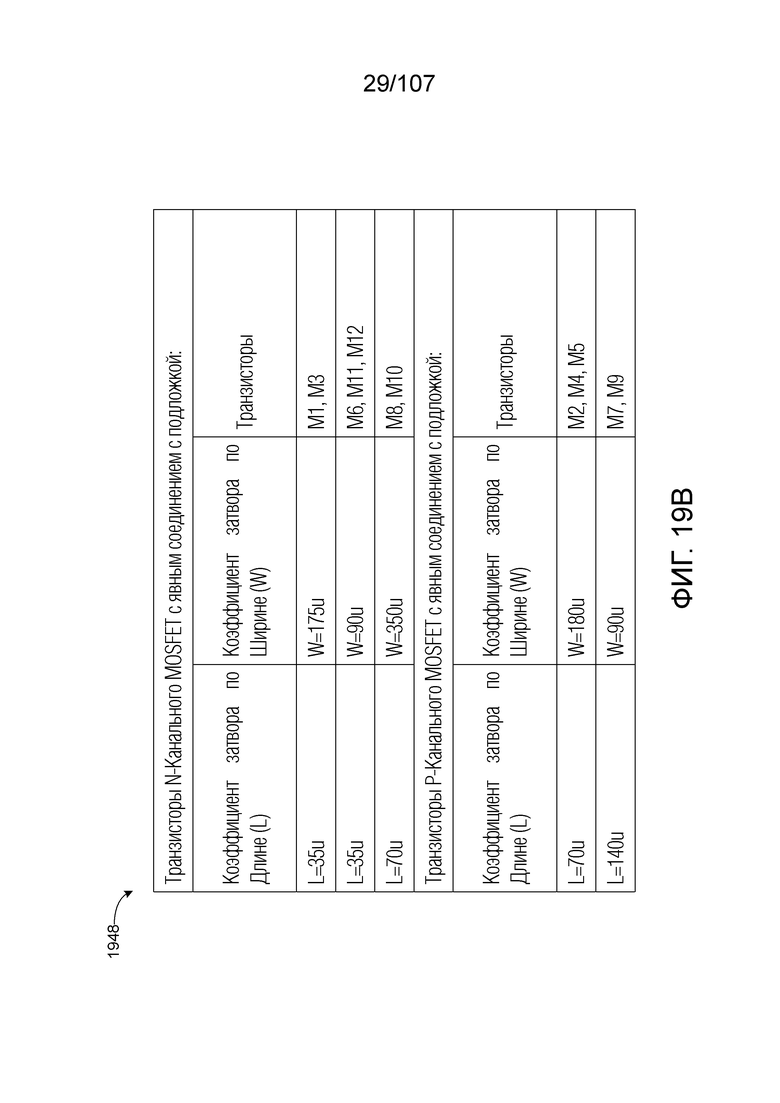

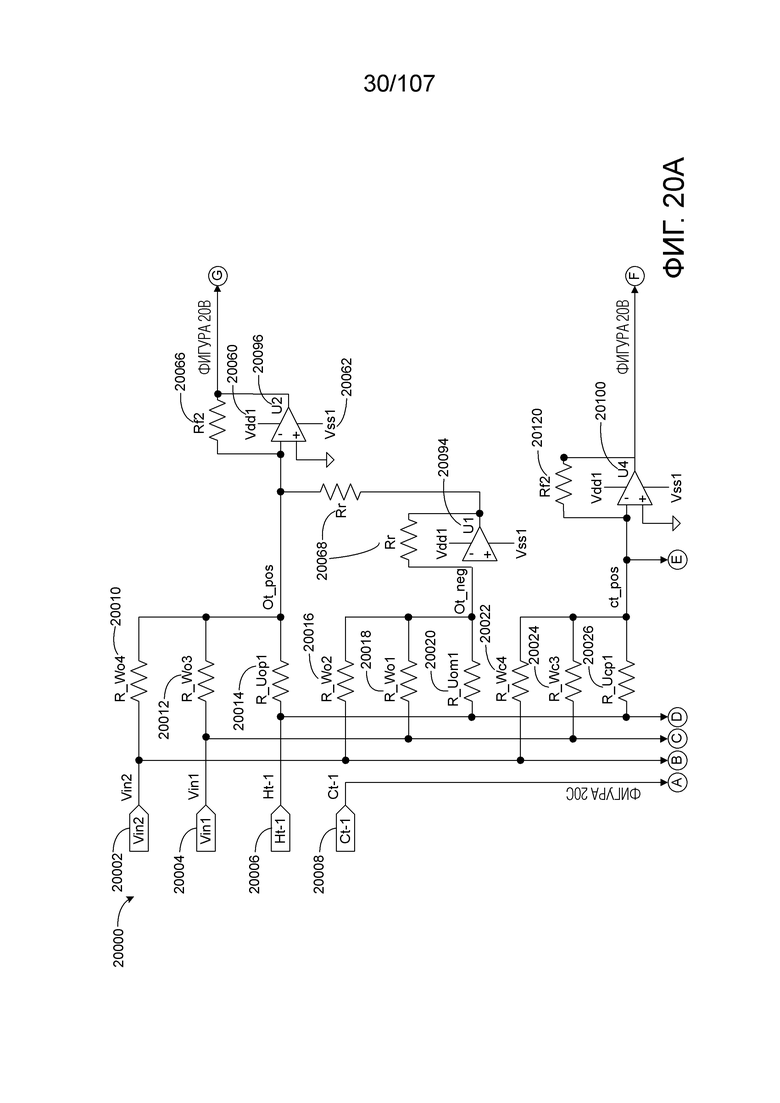

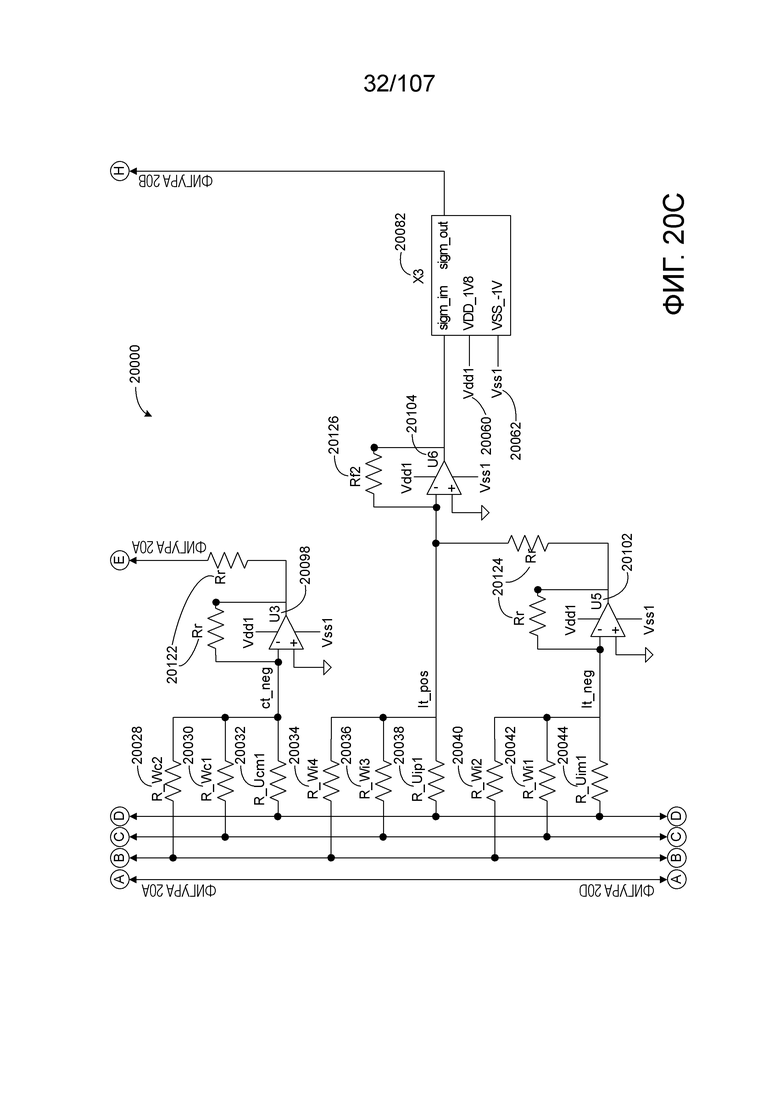

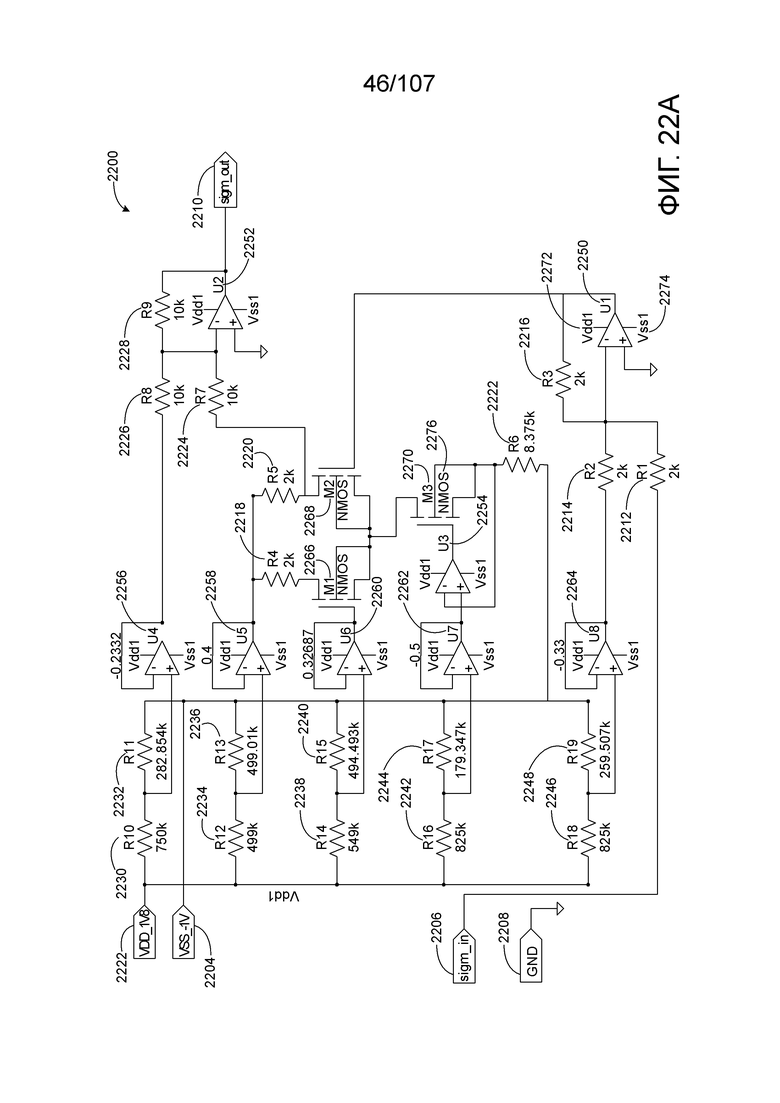

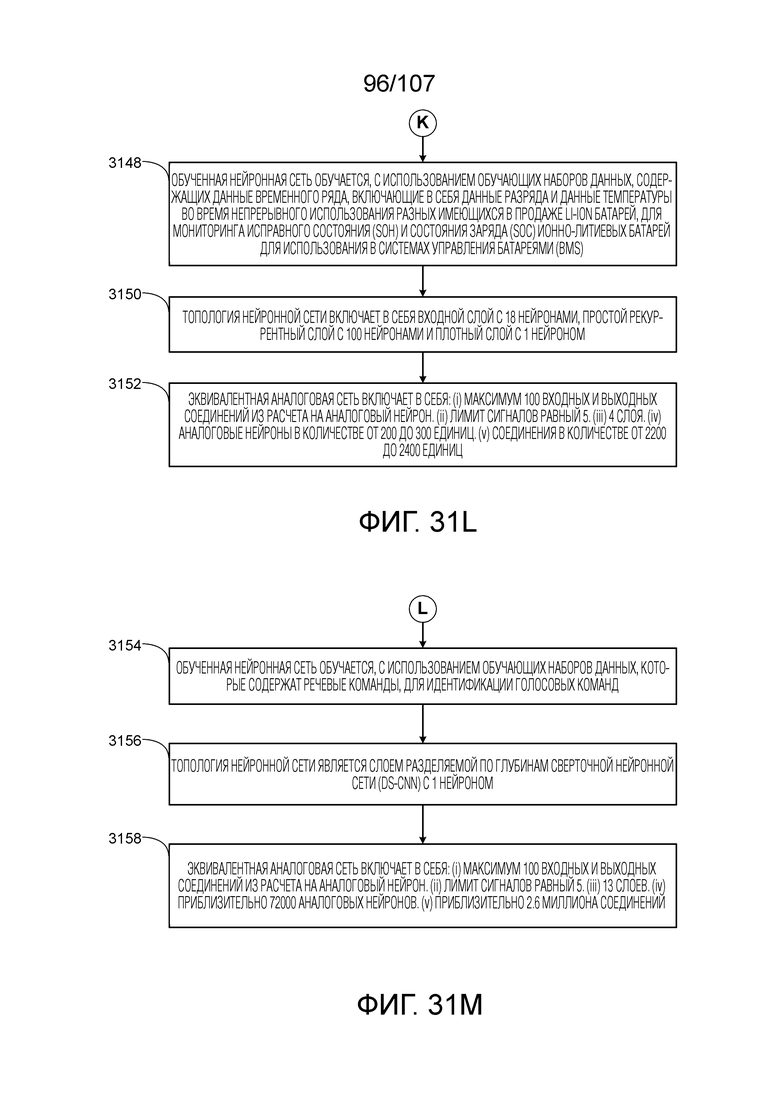

[0083] В некоторых вариантах осуществления, обученная нейронная сеть обучается с использованием обучающих наборов данных, содержащих данные временного ряда, включающие в себя данные разряда и температуры во время непрерывного использования разных имеющихся в продаже Li-Ion батарей, для мониторинга исправного состояния (SOH) и состояния заряда (SOC) ионно-литиевых батарей для использования в системах управления батареями (BMS). В таких случаях, топология нейронной сети включает в себя входной слой, 2 слоя LSTM с 64 нейронами в каждом слое, за которыми следует плотный выходной слой с 2 нейронами для формирования значений SOC и SOH. В таких случаях, эквивалентная аналоговая сеть включает в себя: (i) максимум 100 входных и выходных соединений из расчета на аналоговый нейрон, (ii) лимит сигналов равный 5, (iii) 9 слоев, (iv) аналоговые нейроны в количестве от 1200 до 1300 единиц, и (v) соединения в количестве от 51000 до 52000 единиц.