Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано для построения функциональных узлов высоконадежных систем автоматического регулирования и управления, например, для построения резервированных систем, работающих в космосе, которые проектируют на количество отказов более одного.

В настоящее время в системах автоматики для обеспечения резервирования требуется выявлять один сигнал из нескольких входных сигналов по его рангу. Ранг сигнала определяется его величиной (амплитудой) в упорядоченном списке сигналов. Например, сигнал может занимать минимальное, медианное, максимальное или любое другое положение среди всех входных сигналов, упорядоченных по величине (амплитуде). При этом к таким устройствам в системах автоматики часто предъявляют дополнительные требования: высокое быстродействие выбора любого из сигналов; возможность выполнения устройства на микросхемах с высокой степенью интеграции, например, на ПЛИС (программируемые логические интегральные схемы); наличие вспомогательного сигнала о ложном срабатывании устройства, который необходим для диагностики самого устройства или системы.

Из уровня техники известно техническое решение: «Устройство для передачи на нагрузку медианного сигнала из трех входных сигналов» (Аналог 1- Fu M., Zhang D., Li T. New electrical power supply system for all-electric propulsion spacecraft //IEEE Transactions on Aerospace and Electronic Systems. – 2017. – Т. 53. – №. 5. – С. 2157-2166, (Fig.7).

Аналог 1 представляет собой устройство, передающее на нагрузку, подключенную к его выходу, один из входных сигналов, величина которого имеет медианное значение среди трех входных сигналов. В качестве нагрузки выступает нагрузочный резистор. Устройство по аналогу 1 содержит три входа для подключения аналоговых сигналов и выход. Устройство состоит из трех мажоритарных элементов (majority voter) номер NO1, NO2, NO3 и нагрузочного резистора, каждый мажоритарный элемент имеет два входа и выход, причем выходы мажоритарных элементов и первый вывод нагрузочного резистора объединены и образуют выход устройства, второй вывод нагрузочного резистора подключен к общей точке. Первые и вторые входы элементов с номером NO1, NO2, NO3 объединены по закону неповторяющихся сочетаний, например, 1.1 (первый вход первого элемента NО1) с 2.2 (вторым входом второго элемента NО2); 1.2 (первый вход второго элемента NО2) с 1.3 (первым входом третьего элемента NО3); 2.1 (второй вход первого элемента NО1) с 2.3 (вторым входом третьего элемента NО3). Объединенные входы мажоритарных элементов образуют три входа устройства выбора медианного сигнала, на которые подаются входные сигналы, из которых осуществляется выбор медианного сигнала. Этот сигнал, в свою очередь, передается на выход устройства выбора. Каждый мажоритарный элемент состоит из двух каскадов. Первый каскад состоит из четырех резервированных диодных ключей, объединенных анодами. Выходы первых двух диодных ключей образуют первый и второй входы мажоритарного элемента, а выходы двух остальных диодных ключей образуют выходы первого каскада, которые подключены к двум входам второго каскада, образованного двумя последовательно включенными биполярными транзисторами. Базы этих транзисторов образуют входы второго каскада, причем коллектор верхнего по схеме транзистора, подключен к положительному полюсу источника питания. Аноды резервированных диодных ключей соединены также с положительным полюсом источника питания через резервированный резистор (два последовательно включенных резистора). Отрицательный полюс источника питания соединен с общей точкой (землей) и общей точкой (землей) нагрузочного резистора (нагрузки), второй вывод которого соединен с эмиттером нижнего по схеме транзистора, являющимся выходом мажоритарного элемента.

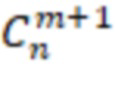

Устройство по аналогу 1 можно применить для выбора медианного сигнала из N входных сигналов. Однако, в этом случае, необходимое количество мажоритарных элементов в составе устройства будет определяться следующей формулой:

где N – количество входных сигналов, n – количество мажоритарных элементов в составе устройства, k – количество входов у каждого мажоритарного элемента,  – количество неповторяющихся сочетаний из N элементов по k элементов в каждом сочетании. Исходя из формулы (1), при увеличении количества входов аналога 1 до 25, для создания устройства потребуется более 5 млн. мажоритарных элементов, что, в свою очередь, потребует значительного количества логических ячеек при реализации устройства на ПЛИС. Кроме того, аналог 1 не позволяет формировать и выдавать вспомогательный сигнал о ложном срабатывании устройства. Эта функция необходима для диагностики устройства и выявления ошибок при вычислении медианного сигнала.

– количество неповторяющихся сочетаний из N элементов по k элементов в каждом сочетании. Исходя из формулы (1), при увеличении количества входов аналога 1 до 25, для создания устройства потребуется более 5 млн. мажоритарных элементов, что, в свою очередь, потребует значительного количества логических ячеек при реализации устройства на ПЛИС. Кроме того, аналог 1 не позволяет формировать и выдавать вспомогательный сигнал о ложном срабатывании устройства. Эта функция необходима для диагностики устройства и выявления ошибок при вычислении медианного сигнала.

Из уровня техники известен «Медианный идентификатор» (Патент РФ №2204164, дата публикации 10.05.2003, Бюл. № 13, МПК G06G 7/25) – аналог 2. Устройство по аналогу 2 представляет собой медианный идентификатор, определяющий медианный сигнал из трех входных аналоговых сигналов путем их сравнения при помощи трех компараторов с линейно изменяющимся опорным сигналом. Аналог 2 содержит три информационных входа x1, x2, x3, три идентифицирующих входа у1, у2, у3, настроечный вход f, вход для подключения линейно возрастающего напряжения u(t) и выходы z1, z2, z3. Аналог 2 состоит из трех компараторов, двух регистров, мажоритарного логического элемента, логического элемента И, двух логических элементов ИЛИ, трех логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и трех замыкающих ключей.

Недостатком аналога 2 является его низкое быстродействие, связанное с использованием линейно изменяющегося опорного сигнала. Данный недостаток определяется принципом действия аналога 2, так как он позволяет определять сигнал, занимающий медианное положение, только один раз за период изменения опорного сигнала. Кроме того, аналог 2 имеет функциональные ограничения, заключающиеся в том, что он предоставляет возможность обработки только трех аналоговых сигналов. Кроме того, аналог 2, также, как и аналог 1, не позволяет формировать и выдавать вспомогательный сигнал о ложном срабатывании устройства.

Из уровня техники известен «Ранговый фильтр» (Аналог 3: Патент РФ на изобретение № 2172516, опубликован 20.08.2001, Бюл. № 23, МПК G06G 7/52). Данное устройство, в зависимости от комбинации управляющих сигналов, позволяет осуществлять выбор сигналов, которые имеют различные ранги: ранг минимального, ранг максимального или ранг медианного сигнала.

Устройство по аналогу 3 содержит n информационных входов {x1, x2, …, xn} (n – нечетное число), 2 управляющих входа f1 и f2 и выход Z. Кроме того, аналог 3 содержит N+1 селекторов. Селекторы {1, 2, …, N} содержат m+1 информационных входов, управляющий вход и выход. Селектор (N+1) содержит N информационных входов, управляющий вход и выход. Величины N и m определяются следующими выражениями:

где n – количество информационных входов, N – количество селекторов, m – количество реляторов в составе каждого из селекторов {1, 2, …, N},  – количество неповторяющихся сочетаний из n элементов по m+1 элементов в каждом сочетании.

– количество неповторяющихся сочетаний из n элементов по m+1 элементов в каждом сочетании.

Недостаток аналога 3 заключается в том, что с увеличением количества информационных входов значительно увеличивается количество селекторов, необходимых для реализации устройства. Например, для 7-канального рангового фильтра с использованием цифровой схемотехники необходимо 35 селекторов, каждый из которых содержит 3 компаратора и 3 двухканальных многоразрядных мультиплексора. Реализация такого рангового фильтра на ПЛИС занимает более 4 тыс. логических ячеек и это число значительно увеличивается с ростом количества каналов. Для создания рангового фильтра, содержащего 25 каналов, потребуется более 5 млн. селекторов, из-за чего его реализация в ПЛИС не представляется возможной, т.к. устройств с таким количеством логических ячеек в данное время не существует. Кроме того, аналог 3, как и аналоги 1, 2, не позволяет формировать и выдавать вспомогательный сигнал о ложном срабатывании устройства.

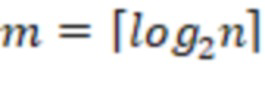

Из уровня техники известно техническое решение: «Ранговый фильтр» (Аналог 4: РФ Патент №2205449, дата публикации 27.05.2003, Бюл. № 15 06.05.2003, МПК G06G 7/25). Аналог 4 является наиболее близким по технической сути и достигаемому техническому результату к заявляемому изобретению и взят за прототип. Прототип представляет собой ранговый фильтр, который осуществляет выбор сигнала любого заданного ранга r  {1, 2, …, n} из n входных аналоговых сигналов x1, …, xn, путем их сравнения при помощи n компараторов с линейно возрастающим опорным сигналом. Прототип содержит n информационных входов для подключения аналоговых сигналов x1, …, xn, m+1 настроечных входов f1, …, fm+1, где

{1, 2, …, n} из n входных аналоговых сигналов x1, …, xn, путем их сравнения при помощи n компараторов с линейно возрастающим опорным сигналом. Прототип содержит n информационных входов для подключения аналоговых сигналов x1, …, xn, m+1 настроечных входов f1, …, fm+1, где  , вход для подключения линейно возрастающего опорного сигнала u(t) и выход z.

, вход для подключения линейно возрастающего опорного сигнала u(t) и выход z.

Прототип состоит из n компараторов (в заявляемом объекте названы блоком компараторов), двух регистров, двух сумматоров единиц, двух блоков сравнения (блок компараторов, сумматор единиц и блок сравнения в заявляемом объекте образуют канал сравнения), двух логических элементов И-НЕ, n логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и n замыкающих ключей (в заявляемом объекте названных управляемым переключателем). Неинвертирующие входы компараторов объединены и подключены к входу u(t), инвертирующие входы подключены к информационным входам x1, …, xn. Выходы компараторов подключены к объединенным i-ым входам первого и второго регистров. Выход i j-го регистра (j  {1, 2}) соединен с j-ым входом i-ого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и i-ым входом j-ого сумматора единиц, подключенного k-ым выходом (k

{1, 2}) соединен с j-ым входом i-ого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и i-ым входом j-ого сумматора единиц, подключенного k-ым выходом (k  {1, 2, …, m} к k-му входу j-ого блока сравнения, выход которого соединен с первым входом j-ого логического элемента И-НЕ, выход которого соединен с входом разрешения записи j-ого регистра. Вторые входы логических элементов И-НЕ объединены и образуют настроечный вход fm+1 рангового фильтра. Вход, управляющий вход и выход i-ого замыкающего ключа соединены соответственно с инвертирующим входом i-ого компаратора, выходом i-ого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом рангового фильтра. Настроечные входы f1, …, fk подключены соответственно к объединенным (m+k)-ым входам блоков сравнения. Блок компараторов, регистры, сумматоры единиц, блоки сравнения и логические элементы И-НЕ и ИСКЛЮЧАЮЩИЕ ИЛИ образуют блок управления замыкающими ключами, названный в заявляемом объекте блоком обработки входных сигналов. Этот блок имеет n входов для подачи входных сигналов, m+1 входов для подачи управляющих сигналов и n выходов, образованных выходами логических элементов ИСКЛЮЧАЮЩИЕ ИЛИ, для управления замыкающими ключами (управляемым переключателем). Данное устройство (прототип) позволяет осуществлять выбор сигнала любого ранга в зависимости от комбинации управляющих сигналов.

{1, 2, …, m} к k-му входу j-ого блока сравнения, выход которого соединен с первым входом j-ого логического элемента И-НЕ, выход которого соединен с входом разрешения записи j-ого регистра. Вторые входы логических элементов И-НЕ объединены и образуют настроечный вход fm+1 рангового фильтра. Вход, управляющий вход и выход i-ого замыкающего ключа соединены соответственно с инвертирующим входом i-ого компаратора, выходом i-ого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом рангового фильтра. Настроечные входы f1, …, fk подключены соответственно к объединенным (m+k)-ым входам блоков сравнения. Блок компараторов, регистры, сумматоры единиц, блоки сравнения и логические элементы И-НЕ и ИСКЛЮЧАЮЩИЕ ИЛИ образуют блок управления замыкающими ключами, названный в заявляемом объекте блоком обработки входных сигналов. Этот блок имеет n входов для подачи входных сигналов, m+1 входов для подачи управляющих сигналов и n выходов, образованных выходами логических элементов ИСКЛЮЧАЮЩИЕ ИЛИ, для управления замыкающими ключами (управляемым переключателем). Данное устройство (прототип) позволяет осуществлять выбор сигнала любого ранга в зависимости от комбинации управляющих сигналов.

Устройство по прототипу позволяет определять сигнал, занимающий медианное положение (или имеющего любой другой ранг r  {1, 2, …, n}), но выполнить это может только один раз за период линейно возрастающего опорного сигнала, что снижает его быстродействие, причем с увеличением разрядности входных сигналов быстродействие снижается еще более. Период опорного сигнала зависит от разрядности входных сигналов следующим образом. При реализации медианного идентификатора для цифровых M-битных входных сигналов, период опорного сигнала (а следовательно, и время вычисления медианного сигнала) составит 2M тактов работы тактового генератора. Таким образом, при частоте тактирования медианного идентификатора, равной 200 МГц и разрядности входных данных, равной 14 бит, период опорного сигнала составит 82 мкс. Эта величина времени, необходимая для определения выбранного сигнала, не отвечает требованиям, предъявляемым при создании быстродействующих систем. Кроме того, прототип, как и аналоги 1, 2, 3 не позволяет формировать и выдавать вспомогательный сигнал о ложном срабатывании устройства.

{1, 2, …, n}), но выполнить это может только один раз за период линейно возрастающего опорного сигнала, что снижает его быстродействие, причем с увеличением разрядности входных сигналов быстродействие снижается еще более. Период опорного сигнала зависит от разрядности входных сигналов следующим образом. При реализации медианного идентификатора для цифровых M-битных входных сигналов, период опорного сигнала (а следовательно, и время вычисления медианного сигнала) составит 2M тактов работы тактового генератора. Таким образом, при частоте тактирования медианного идентификатора, равной 200 МГц и разрядности входных данных, равной 14 бит, период опорного сигнала составит 82 мкс. Эта величина времени, необходимая для определения выбранного сигнала, не отвечает требованиям, предъявляемым при создании быстродействующих систем. Кроме того, прототип, как и аналоги 1, 2, 3 не позволяет формировать и выдавать вспомогательный сигнал о ложном срабатывании устройства.

Указанные недостатки не позволяют использовать устройство по прототипу для построения функциональных узлов высоконадежных, быстродействующих систем автоматического регулирования и управления, например, для построения резервированных систем, работающих в космосе, которые проектируют на количество отказов более одного.

Таким образом, указанные выше недостатки позволяют сформулировать техническую проблему, связанную с необходимостью создания быстродействующего многоканального элемента выбора одного сигнала с заданным рангом из набора входных сигналов с функцией выявления ошибочных результатов вычисления.

Технический результат, достигаемый при решении указанной выше технической проблемы, заключается в создании быстродействующего N-канального элемента выбора одного из входных сигналов, осуществляющего выбор входного сигнала по его заданному рангу из набора входных сигналов, реализуемого с использованием цифровой схемотехники высокой степени интеграции, в том числе на ПЛИС, и выполняющего функцию выявления ошибочных результатов выбора входного сигнала.

Для решения технической проблемы и достижения технического результата многоканальный элемент выбора одного из входных сигналов, как и прототип, содержит управляемый переключатель с N входами и одним выходом. Входы управляемого переключателя являются информационными входами многоканального элемента выбора одного из входных сигналов. Они соединены с N информационными входами блока обработки входных сигналов. Выход управляемого переключателя образует выход многоканального элемента выбора одного из входных сигналов. Управляющий вход управляемого переключателя соединен с выходом блока обработки входных сигналов. Данный блок имеет управляющий вход и канал сравнения, который включает блок компараторов. Компараторы данного блока имеют неинвертирующие входы, которые объединены и образуют его опорный вход. Инвертирующие входы компараторов образуют входы сравнения блока компараторов. Кроме того, канал сравнения заявляемого объекта, как и у прототипа, содержит сумматор единиц и блок сравнения.

В отличие от прототипа блок обработки входных сигналов дополнительно снабжен N-канальным модулем ранжирования, N-1 каналами сравнения, каждый из которых имеет N входов и один выход, блоком задания ранга выбираемого сигнала, и шифратором с N входами и двумя выходами. Первый выход шифратора образует основной выход блока обработки входных сигналов, а второй выход шифратора, предназначенный для выдачи сигнала ошибки, является дополнительным выходом блока обработки входных сигналов. Выход каждого канала сравнения соединен с соответствующим входом шифратора. Каждый из каналов модуля ранжирования содержит усилитель, блок задания сигнала ранжирования и сумматор модуля ранжирования. При этом вход усилителя образует соответствующий вход модуля ранжирования и соединен с соответствующим входом многоканального элемента выбора. Выход усилителя подключен к первому входу сумматора модуля ранжирования, второй вход которого соединен с блоком задания сигнала ранжирования. Выход сумматора модуля ранжирования образует соответствующий выход модуля ранжирования. Каждый из каналов сравнения содержит блок компараторов, состоящий из

N-1 компараторов, сумматор единиц с N-1 входами и одним выходом, а также блок сравнения с двумя входами и одним выходом. При этом выходы N-1 компараторов подключены к соответствующим входам сумматора единиц. Выход сумматора единиц подключен к первому входу блока сравнения, выход которого является выходом соответствующего канала сравнения. Вторые входы блоков сравнения каждого канала сравнения объединены и образуют управляющий вход многоканального элемента выбора одного из входных сигналов. К управляющему входу подключен блок задания ранга выбираемого сигнала. Входы блока компараторов являются одноименными входами канала сравнения. Каждый выход модуля ранжирования соединен со входами каждого канала сравнения таким образом, что первый выход модуля ранжирования подключен к опорному входу первого канала сравнения, второй выход модуля ранжирования подключен к опорному входу второго канала сравнения и далее соответственно, то есть i-тый выход модуля ранжирования подключен к опорному входу i-того канала сравнения. К остальным входам каждого из каналов сравнения подключены все оставшиеся выходы модуля ранжирования за исключением выхода, который подключен к опорному входу соответствующего канала сравнения.

В частном случае управляемый переключатель многоканального элемента выбора одного из входных сигналов выполнен в виде мультиплексора.

В частном случае все блоки многоканального элемента выбора одного из входных сигналов реализованы с использованием цифровой схемотехники высокой степени интеграции, например, на ПЛИС.

В известных авторам источниках научно-технической и патентной информации не обнаружены быстродействующие устройства, позволяющие выбрать один входной сигнал из нескольких входных сигналов за минимальное время, которое ограничено только временем прохождения сигнала через блоки комбинационной логики, и выполняющие функцию выявления ошибочных результатов выбора входного сигнала с выдачей соответствующего сигнала на дополнительный выход многоканального элемента выбора одного из входных сигналов.

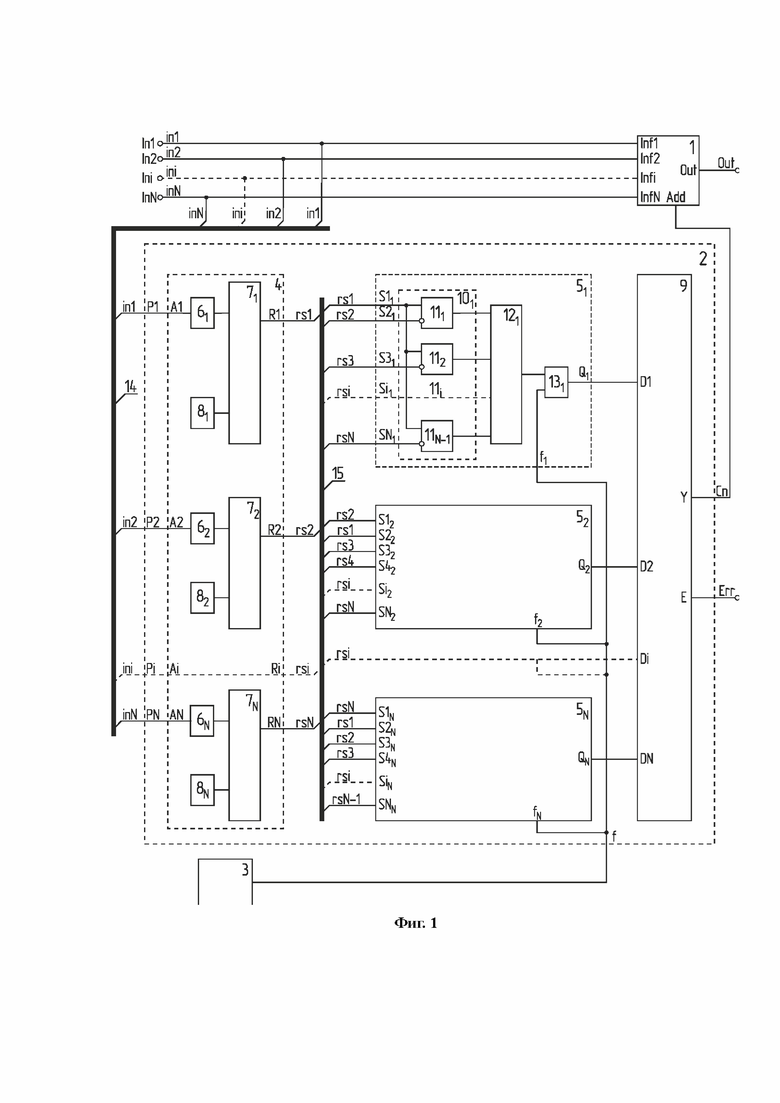

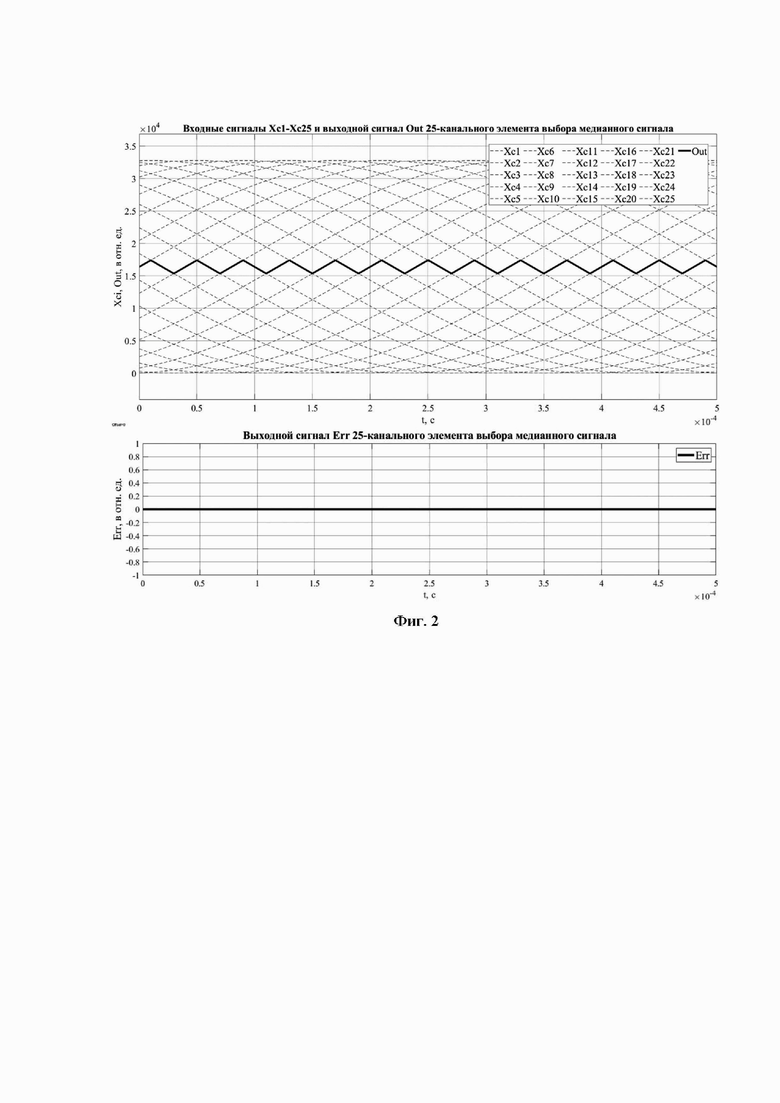

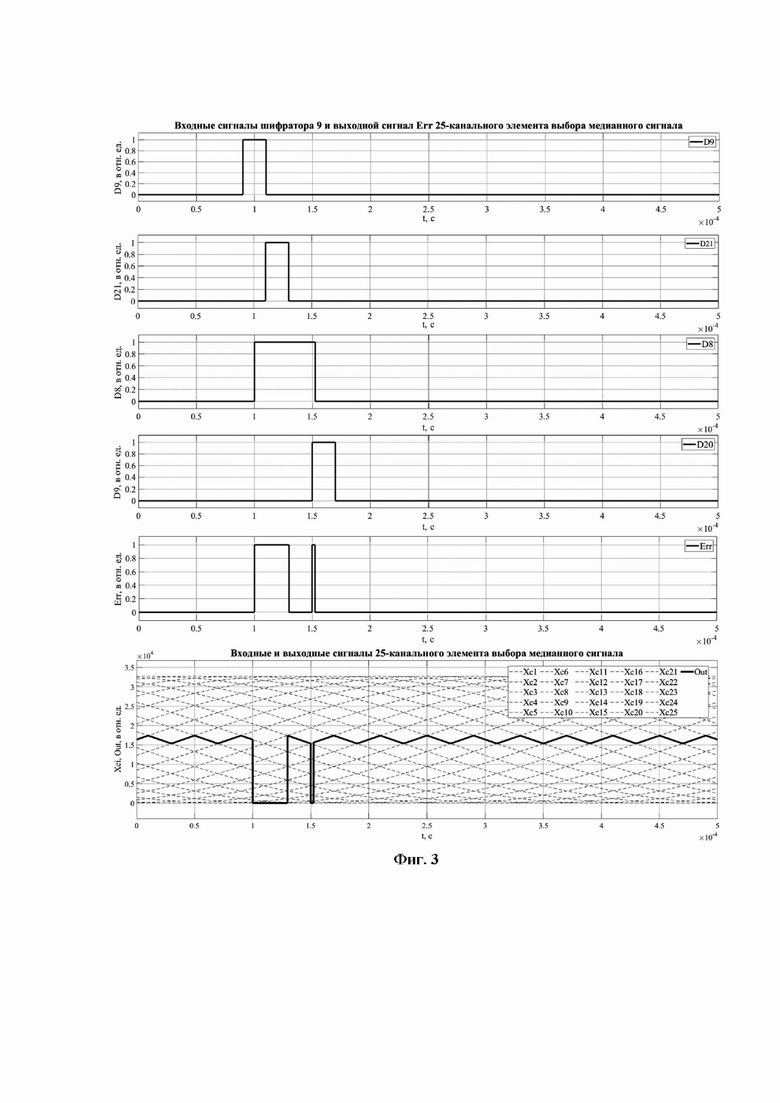

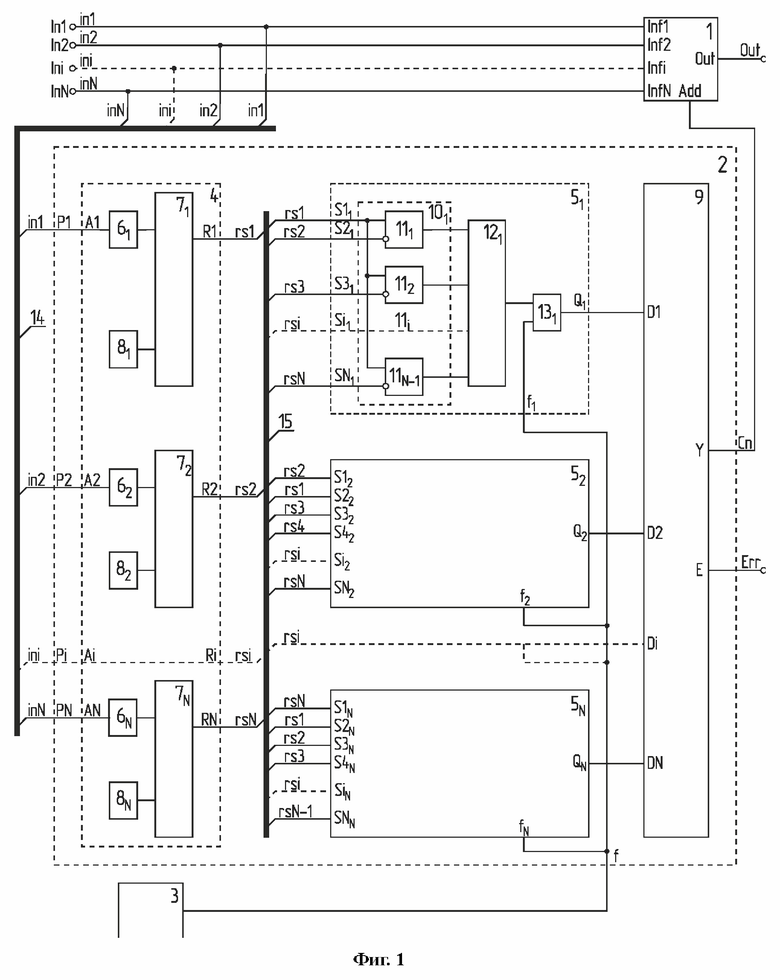

Техническая суть заявляемого изобретения поясняется чертежами, где на фиг. 1 показана функциональная схема многоканального элемента выбора одного из входных сигналов. На фиг. 2 показаны диаграммы входных и выходных сигналов 25-канального элемента выбора медианного сигнала поясняющие его работу в штатном режиме, без ошибочной комбинации выходных сигналов каналов сравнения, поступающих на входы шифратора. На фиг. 3 показаны диаграммы входных и выходных сигналов 25-канального элемента выбора медианного сигнала, поясняющие его работу в режиме имитации ошибочной комбинации выходных сигналов каналов сравнения, поступающих на входы шифратора.

На представленных фигурах приняты следующие обозначения:

На фиг. 1 приняты следующие обозначения:

1 – управляемый переключатель;

2 – блок обработки входных сигналов;

3 – блок задания ранга сигнала;

4 – модуль ранжирования;

51, 52, …, 5i, …, 5N – каналы сравнения;

61, 62, …, 6i, …, 6N – усилители модуля ранжирования;

71, 72, …, 7i, …, 7N – сумматоры модуля ранжирования;

81, 82, …, 8i, …, 8N – блоки задания сигналов ранжирования;

9 - шифратор с функцией выявления ошибочной комбинации;

101, 102, …, 10i, …, 10N – блоки компараторов (102, …, 10i, …, 10N на фиг.1 не показаны) в соответствующих каналах сравнения 51, 52, …, 5i, …, 5N;

111, 112, …, 11i, …, 11N-1 – компараторы блоков компараторов 101, 102, …,10i, …, 10N;

121, 122, …, 12i, …, 12N – сумматоры единиц (122, …, 12i, …, 12N на фиг.1 не показаны) каналов сравнения 51, 52, …, 5i, …, 5N;

131, 132, …, 13i, …, 13N – блоки сравнения (132, …, 13i, …, 13N на фиг.1 не показаны) каналов сравнения 51, 52, …5i, …, 5N;

14 – шина, образованная сигнальными линиями in1, in2, …, ini,…, inN;

15 – шина, образованная сигнальными линиями rs1, rs2, …, rsi, …, rsN;

In1, In2, …, Ini,…, InN – информационные входы многоканального элемента выбора одного из входных сигналов, на которые подаются соответственно входные сигналы Xc1, Xc2, …, Xci,…, XcN (Входные сигналы на чертеже не показаны);

Err – дополнительный выход многоканального элемента выбора одного из входных сигналов и блока обработки входных сигналов 2, на котором формируется сигнал об обнаружении ошибочных результатов вычисления;

Inf1, Inf2, …, Infi, …, InfN – информационные входы управляемого переключателя 1;

Add – управляющий (адресный) вход управляемого переключателя 1;

Out – выход управляемого переключателя 1 и информационный выход многоканального элемента выбора одного из входных сигналов;

P1, P2, …, Pi, …, PN – входы блока обработки входных сигналов 2;

in1, in2, …, ini,…, inN – обозначения сигнальных линий, образующих шину 14, для соединения информационных входов In1, In2, …, Ini,…, InN и входов P1, P2, …, Pi, …, PN блока обработки входных сигналов 2;

Cn – информационный (адресный) выход блока обработки входных сигналов 2 и многоканального элемента выбора одного из входных сигналов;

A1, A2, …, Ai, …, AN – входы модуля ранжирования 4;

R1, R2, …, Ri, …, RN – выходы модуля ранжирования 4;

rs1, rs2, …, rsi, …, rsN – сигнальные линии, образующие шину 15 для соединения выходов модуля ранжирования 4 с соответствующими входами каналов сравнения 51, 52, …5i, … , 5N;

Xсrs1, Xсrs2, …, Xсrsi, …, XсrsN – сигналы, проходящие через соответствующие сигнальные линии rs1, rs2, …, rsi, …, rsN (на фиг. 1 не обозначены);

Xсin1, Xсin2, …, Xсini, …, XсinN – сигналы, проходящие через соответствующие сигнальные линии in1, in2, …, ini, …, inN (на фиг. 1 не обозначены);

S1i (i  {1, 2, …, N}) – опорные входы i-ого канала сравнения 51, 52, …5i, …, 5N;

{1, 2, …, N}) – опорные входы i-ого канала сравнения 51, 52, …5i, …, 5N;

S2i, S3i, …, SNi (i  {1, 2, …, N}) – входы сравнения i-ого канала сравнения 51, 52, …5i, …, 5N;

{1, 2, …, N}) – входы сравнения i-ого канала сравнения 51, 52, …5i, …, 5N;

fi (i  {1, 2, …, N}) – управляющие входы f1, f2, …, fi, …, fN, i-ого канала сравнения 51, 52, …5i, …, 5N;

{1, 2, …, N}) – управляющие входы f1, f2, …, fi, …, fN, i-ого канала сравнения 51, 52, …5i, …, 5N;

f – управляющий вход блока 2 обработки входных сигналов;

Qi (i  {1, 2, …, N}) – выход i-ого канала сравнения 51, 52, …5i, …, 5N;

{1, 2, …, N}) – выход i-ого канала сравнения 51, 52, …5i, …, 5N;

D1, D2, …, Di, …, DN – входы шифратора 9 с функцией выявления ошибочной комбинации;

Y – информационный выход шифратора 9 с функцией выявления ошибочной комбинации;

E – выход ошибки шифратора 9 с функцией выявления ошибочной комбинации.

На Фиг. 2 и Фиг. 3 приняты следующие обозначения:

На первой (сверху) диаграмме фиг. 2 приведены входные сигналы Xc1-Xc25 элемента выбора и выходной сигнал Out. На второй диаграмме фиг. 2 приведен выходной сигнал Err.

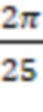

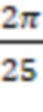

Xc1, Xc2, …, Xci, …, Xc25 – входные синусоидальные сигналы 25-канального элемента выбора медианного сигнала с фазовым сдвигом друг относительно друга, равным  рад и постоянной составляющей. Сигналы показаны прерывистыми линиями.

рад и постоянной составляющей. Сигналы показаны прерывистыми линиями.

Out – выходной сигнал 25-канального элемента выбора медианного сигнала на выходе Out управляемого переключателя 1 (фиг. 1); Сигнал выделен жирной линией.

Err – выходной сигнал ошибки 25-канального элемента выбора медианного сигнала; Сигнал выделен жирной линией.

На диаграммах с первой по четвертую (при нумерации сверху вниз) фиг. 3 приведены входные сигналы D8, D9, D20, D21 шифратора 9 в режиме имитации ошибочных (неверных) комбинаций выходных сигналов каналов сравнения.

На нижней диаграмме фиг.3 приведены входные сигналы Xc1-Xc25 элемента выбора и выходной сигнал Out при имитации ошибочных (неверных) комбинаций. По оси абсцисс показано текущее время в секундах. По оси ординат показана величина соответствующих входных и выходных сигналов (относительные единицы).

Многоканальный элемент выбора одного из входных сигналов, представленный на фиг.1, имеет N информационных входов In1, In2, …, Ini, …, InN, основной Out и дополнительный Err выходы. Он содержит управляемый переключатель 1, блок 2 для обработки входных сигналов, блок 3 для задания ранга выбираемого входного сигнала. Управляемый переключатель 1 также имеет N информационных входов Inf1, Inf2, …, Infi, …, InfN, управляющий (адресный) вход Add и один выход Out, являющийся основным выходом многоканального элемента выбора одного из входных сигналов.

Блок 2 для обработки входных сигналов имеет основной выход Cn, соединенный с управляющим (адресным) входом Add управляемого переключателя 1, и дополнительный выход Err, являющийся дополнительным выходом многоканального элемента выбора одного из входных сигналов. Блок 2 для обработки входных сигналов имеет один управляющий вход f, соединенный с выходом блока 3 для задания ранга выбираемого входного сигнала, и N информационных входов P1, P2, …, Pi,… , PN, соединенных с N одноименными информационными входами In1, In2, …, Ini,…,InN многоканального элемента выбора одного из входных сигналов сигнальными линиями in1, in2, …, ini, …, inN, образующими шину 14, и N информационными входами Inf1, Inf2, …, Infi, …, InfN управляемого переключателя 1. Блок 2 для обработки входных сигналов содержит: N-канальный модуль ранжирования 4 с N входами А1, А2, …, Аi, …, АN и N выходами R1, R2, …, Ri, …, RN; N каналов сравнения 51, 52,…, 5i,…, 5N, каждый из которых имеет N входов S1i, S2i,…, Sii,…,SNi, один выход Qi (i=1, 2, …, N) и управляющий вход fi, причем индекс i соответствует индексу номера каналов сравнения 51, 52, …, 5i,…, 5N; шифратор 9 с функцией выявления ошибочной комбинации с N входами D1, D2,…, Di,…,DN и двумя выходами Yи E. При этом выход Y шифратора 9 соединен с основным выходом Cn блока 2 для обработки входных сигналов, а выход E шифратора 9 подключен к дополнительному выходу Err многоканального элемента выбора одного из входных сигналов. Управляющие входы fi всех каналов сравнения 51, 52, …, 5i, …, 5N объединены и образуют управляющий вход f блока 2 для обработки входных сигналов. Входы N-канального модуля ранжирования 4 - А1, А2, …, Аi, …, АN соединены с соответствующими входами P1, P2, …, Pi, …, PN блока 2 для обработки входных сигналов и подключены к входу соответствующего усилителя 61, 62, …, 6i, …, 6N модуля ранжирования 4. Выходы усилителей 61, 62, …, 6i, …, 6N соединены с первым входом соответствующего сумматора 71, 72, …, 7i, …, 7N модуля ранжирования 4. Вторые входы сумматоров 71, 72, …, 7i, …, 7N соединены с выходом соответствующего блока задания сигнала ранжирования 81, 82, …, 8i, …, 8N. Выходы сумматоров 71, 72, …, 7i, …, 7N образуют N выходов R1, R2, …, Ri, …, RN модуля ранжирования 4. Каждый из N каналов сравнения 51, 52,…, 5i, …, 5N содержит блок компараторов 10i, каждый из которых состоит из (N-1)-го компаратора 111, 112, ,…, 11i,…, 11N-1, неинвертирующие входы которых объединены и образуют опорный вход S1i канала сравнения 5i. Инвертирующие входы компараторов 111, 112, …, 11i, …, 11N-1 образуют N-1 входов сравнения S2i, …, Sii, …, SNi канала сравнения 5i. Выходы компараторов 111, 112, …, 11i, …, 11N-1 соединены с N-1 входами сумматора единиц 12i, выход которого подключен к первому входу блока сравнения 13i, выход которого, в свою очередь, образует выход Qi канала сравнения 5i. Выходы Q1, …, Q2, …, Qi, …, QN всех каналов сравнения 51, 52, …, 5i, …, 5N подключены соответственно ко входам D1, D2, …, Di, …, DN шифратора 9 с функцией выявления ошибочной комбинации. Выходы R1, R2, …, Ri, …, RN модуля ранжирования 4 соединены соответственно с опорными входами S11, S12, …, S1i, …, S1N всех каналов сравнения 51, 52, …, 5i, …, 5N сигнальными линиями rs1, rs2, …, rsi, …, rsN. К оставшимся входам S2i, S3i, …, Sii, …, SNi всех каналов сравнения 51, 52, …, 5i, …, 5N присоединены выходы R1, R2, …, Ri, …, RN модуля ранжирования 4, за исключением выходов, соответственно подключенных к опорным входам каждого из каналов сравнения. Например, в канале сравнения 51 к входам сравнения S21, S31, …, Si1, …, SN1 подключаются выходы R2, …, Ri, …, RN модуля ранжирования 4. В канале сравнения 52 подключаются выходы R1, R3 …, Ri, …, RN, в канале сравнения 53 подключаются выходы R1, R2, R4, …, Ri, …, RN и так далее – в канале сравнения 5N подключаются выходы R1, R3 …, Ri, …, RN-1.

Работа многоканального элемента выбора одного из входных сигналов рассмотрена на примере конкретного выполнения 25-канального элемента выбора медианного сигнала из 25 входных сигналов - Xc1, Xc2, …, Xci, …, Xc25. Все блоки функциональной схемы многоканального элемента фиг. 1 реализованы на программируемой логической интегральной схеме (ПЛИС) типа Altera Cyclone IV EP4CE115F29C7.

Работа заявляемого устройства заключается в следующем.

Входные сигналы Xc1, Xc2, …, Xci, …, Xc25, поступающие на информационные входы In1, In2, …, Ini, …, InN многоканального элемента выбора одного из входных сигналов, одновременно поступают на информационные входы Inf1, Inf2, …, Infi, …, InfN управляемого переключателя 1 и на входы P1, P2, …, Pi, …, PN блока обработки входных сигналов 2. Блок 2, в соответствии со значением сигнала на его управляющем входе f выбирает из входных сигналов тот сигнал, ранг которого совпадает с рангом, заданным с помощью блока 3 (блока задания ранга сигнала), и формирует на информационном (адресном) выходе Cn сигнал, который поступает на управляющий вход Add управляемого переключателя 1. Управляемый переключатель 1 обеспечивает подключение к своему выходу Out того входного сигнала, ранг которого совпадает с рангом, заданным на выходе блока 3. Перед началом работы устройства необходимо задать ранг выбираемого сигнала с помощью блока 3 и произвести настройку модуля ранжирования 4. Ранг сигнала в упорядоченной по величине выборке из N сигналов определяется числом сигналов выборки, меньших этого сигнала по величине. Таким образом, для минимального сигнала ранг rmin = 0, для максимального rmax = N-1. Ранг медианного сигнала для N-канального элемента выбора рассчитывается по следующей формуле:

где  – искомый ранг медианного сигнала, N – количество входных сигналов элемента выбора,

– искомый ранг медианного сигнала, N – количество входных сигналов элемента выбора,  - операция округления до целого в меньшую сторону. Таким образом, при выборе медианного сигнала из 25 произвольно меняющихся входных сигналов Xc1, Xc2, …, Xci, …, Xc25 ранг медианного сигнала в соответствии с формулой (3) равен rmed = 12. Это значение ранга устанавливается на выходе блока 3.

- операция округления до целого в меньшую сторону. Таким образом, при выборе медианного сигнала из 25 произвольно меняющихся входных сигналов Xc1, Xc2, …, Xci, …, Xc25 ранг медианного сигнала в соответствии с формулой (3) равен rmed = 12. Это значение ранга устанавливается на выходе блока 3.

Настройка модуля ранжирования 4 необходима для корректного определения сигнала, имеющего нужный ранг в случае, если входные сигналы имеют одинаковые величины, так как на входы многоканального элемента поступают произвольно изменяемые сигналы. Для этого необходимо обеспечить, чтобы значения всех сигналов, поступающих на входы S1, S2, …, Si, …, SN каналов сравнения 51, 52, …, 5i, …, 525 отличались друг от друга. Этого можно добиться путем ранжирования. Под ранжированием будем понимать добавление к величине входного сигнала величины  , равной номеру канала, на который поступает этот сигнал. Для того, чтобы данная добавка не влияла на ранг сигнала, необходимо масштабировать сигнал по величине, увеличив его в

, равной номеру канала, на который поступает этот сигнал. Для того, чтобы данная добавка не влияла на ранг сигнала, необходимо масштабировать сигнал по величине, увеличив его в  раз. Ранжирование осуществляется путем выполнения следующих математических операций (4)-(6):

раз. Ранжирование осуществляется путем выполнения следующих математических операций (4)-(6):

где i – номер канала элемента выбора (i=1 .. N), Xcini – i-ый входной сигнал элемента выбора, 2K – коэффициент масштабирования (коэффициент усиления каждого усилителя модуля ранжирования 61, 62, …, 6i, …, 6N), необходимый для обеспечения несущественности вносимой добавки (значения выходного сигнала блока задания сигнала ранжирования 8i)  , обеспечивающей строгое неравенство ранжированных сигналов, не влияя при этом на их ранги, K – количество двоичных разрядов, необходимых для добавления несущественной добавки ко входным сигналам элемента выбора, Xсrsi – i-ый ранжированный сигнал (поступает на соответствующий выход Ri модуля ранжирования 4),

, обеспечивающей строгое неравенство ранжированных сигналов, не влияя при этом на их ранги, K – количество двоичных разрядов, необходимых для добавления несущественной добавки ко входным сигналам элемента выбора, Xсrsi – i-ый ранжированный сигнал (поступает на соответствующий выход Ri модуля ранжирования 4),  – операция округления до целого в большую сторону.

– операция округления до целого в большую сторону.

При N=25 коэффициенты усиления всех усилителей 61, 62, …, 6i, …, 625, в соответствии с формулами (4) и (6), устанавливаются равными 25 = 32. На выходах блоков задания сигналов ранжирования 81, 82, …, 8i, …, 825 устанавливаются значения констант  , рассчитанных по выражению (5) и соответственно равных: 0, 1, 2, …24. Таким образом, в результате настройки модуля ранжирования 4 многоканальный элемент выбора сможет определить медианный сигнал (или сигнал любого другого ранга) даже при равных величинах всех входных сигналов.

, рассчитанных по выражению (5) и соответственно равных: 0, 1, 2, …24. Таким образом, в результате настройки модуля ранжирования 4 многоканальный элемент выбора сможет определить медианный сигнал (или сигнал любого другого ранга) даже при равных величинах всех входных сигналов.

Ранжированные выходные сигналы Xсrsi с выходов R1, R2, …, Ri, …, R25 модуля ранжирования 4 поступают соответственно на опорные входы S1i, каждого i-того из каналов сравнения 51, 52, …, 5i, …, 525, определяя тем самым опорные сигналы каждого из каналов сравнения. На входы сравнения S2i, S3i, …, SNi каждого i-ого канала сравнения 51, 52, …5i, …, 525 поступают соответственно выходные сигналы Xсrsi с тех же выходов R1, R2, …, Ri, …, R25, за исключением выходов, соответственно подключенных к опорному входу каждого из каналов сравнения, определяя тем самым сигналы, которые будут сравниваться с опорным сигналом соответствующего канала сравнения. Благодаря такому подключению в первом канале сравнения 51 ранжированный выходной сигнал Xсrs1 с выхода R1 сравниваются с остальными ранжированными выходными сигналами Xсrsi (кроме сравнения с самим собой при i = 1), которые поступают с выходов R2, …, Ri, …, R25. Во втором канале сравнения 52 ранжированный выходной сигнал Xсrs2 с выхода R2 сравнивается с остальными ранжированными выходными сигналами XCrsi (кроме сравнения с самим собой при i = 2), которые поступают с выходов R1, R3…, Ri, …, R25. И так далее во всех каналах сравнения, реализуя тем самым сравнение каждого из ранжированных сигналов модуля ранжирования 4, с опорным, обеспечивая при этом неповторяющиеся сочетания оставшихся сигналов и реализуя определение ранга сигнала, выступающего в качестве опорного в соответствующем канале сравнения 5i.

Таким образом первый канал сравнения 51 определяет ранг ранжированного сигнала с выхода R1 модуля ранжирования 4, второй канал сравнения 52 определяет ранг ранжированного сигнала с выхода R2 модуля ранжирования 4 и так далее до 25 канала сравнения 525, который определяет ранг ранжированного сигнала с выхода R25 модуля ранжирования 4.

Определение ранга сигнала, который играет роль опорного сигнала в соответствующем i-том канале сравнения 5i реализуется, например, для первого канала сравнения с помощью блока компараторов 101 и компараторов 111, 112, …, 11i, …, 1124. На объединенные неинвертирующие входы данных компараторов поступает соответствующий опорный сигнал с выхода R1 модуля ранжирования 4, а на входы сравнения (инвертирующие входы компараторов 111, 112, …, 11i, …, 1124) – остальные сигналы R2, R3 …, Ri, …, R25 модуля ранжирования 4. На выходе каждого из компараторов 111, 112, …, 11i, …, 1124 формируется сигнал «0», если опорный сигнал меньше соответствующего сравниваемого сигнала, и сигнал «1», если опорный сигнал больше сравниваемого. Сигналы компараторов 111, 112, …, 11i, …, 1124 суммируются с помощью сумматора единиц 121, на выходе которого формируется число, равное числу сигналов, которые меньше опорного сигнала, что равносильно по определению рангу опорного сигнала. Далее это число, определяющее ранг опорного сигнала, сравнивается в блоке сравнения 131 с числом, заданным блоком 3 задания ранга сигнала. Это число поступает через управляющий вход f1 на второй вход блока сравнения 131 канала сравнения 51 и через соответствующие управляющие входы fi на все каналы сравнения 5i. Если ранг опорного сигнала в любом из каналов сравнения равен рангу, заданному блоком 3 задания ранга сигнала, то на соответствующем выходе Qi канала сравнения 5i формируется сигнал «1», а если ранг опорного сигнала не равен рангу, заданному блоком 3 (больше или меньше), то на соответствующем выходе Qi формируется сигнал «0». Число каналов сравнения, равное числу входных сигналов и их «параллельная» работа обеспечивает быстродействие, зависящее только от параметров ПЛИС.

Выходные (цифровые) сигналы «0» или «1» с выходов Q1, Q2, …, Qi, …, Q25 (несущие информацию о соответствии ранга опорного сигнала канала сравнения рангу, заданному с помощью блока 3) каналов сравнения 51, 52, …, 5i, …, 525 поступают на входы D1, D2, … Di, …, D25 шифратора 9 с функцией определения ошибочной комбинации. На информационном выходе Y шифратора 9 с функцией выявления ошибочной комбинации формируется сигнал, несущий информацию о номере канала сравнения 5i, на который поступает сигнал, имеющий заданный ранг. Этот сигнал передается через информационный выход Cn блока обработки входных сигналов 2, на управляющий (адресный) вход Add управляемого переключателя 1. Этот сигнал обеспечивает подключение входа Ini многоканального элемента выбора, соответствующий каналу сравнения 5i, на опорный вход которого поступает сигнал, имеющий заданный ранг, на выход Out многоканального элемента выбора. Кроме того, в случае возникновения ошибок при работе каналов сравнения, например, выявление нескольких сигналов, имеющих заданный ранг, на выходе E шифратора 9 генерируется сигнал ошибки, передаваемый на выход Err элемента выбора. Логика работы шифратора 9 с функцией выявления ошибочной комбинации поясняется таблицей истинности (таблица 1).

Таблица 1 – Таблица истинности шифратора 9 с функцией определения ошибочной комбинации

X - выходной сигнал не имеет значения, т.к. выявлена ошибка при работе устройства

Таблицу истинности шифратора 9 условно можно разделить на две части – верные и неверные комбинации. Верными комбинациями сигналов на входах D1, D2, … Di, …, D25 шифратора 9 с функцией определения ошибочной комбинации назовем такие комбинации, при которых только на одном из названных входов существует сигнал «1», а на остальных входах только сигналы «0». Тогда таблица истинности верных комбинаций шифратора на N входов будет представлять собой единичную матрицу, что будет соответствовать поступлению на i-ый вход шифратора логической единицы, а на все остальные – логических нулей. При этом i-ый номер входа шифратора будет совпадать с i-ым номером комбинации. Неверными комбинациями будут являться все оставшиеся случаи (комбинации), в которых логическая единица будет присутствовать на более, чем одном входе, или отсутствовать вовсе. В соответствии с таблицей истинности при поступлении на входы шифратора верной комбинации, на выходе Y формируется сигнал, представление которого в десятичной системе счисления равно номеру i-того канала сравнения 5i, на который поступил сигнал, имеющий заданный блоком 3 ранг среди всех входных сигналов. Ошибочными являются все комбинации, при которых на входы шифратора приходит не одна логическая единица, что свидетельствует о том, что сигнал заданного ранга не был найден, или было найдено несколько сигналов заданного ранга. Это утверждение является верным для любого набора сигналов, в котором исключены сигналы одного ранга, что обеспечивается введением модуля ранжирования 4 и его настройкой. Поэтому можно утверждать, что существует только один сигнал каждого ранга (даже для равных сигналов), а нахождение нескольких сигналов одного ранга или не нахождение ни одного сигнала искомого ранга свидетельствует об ошибке, возникшей при работе устройства. При поступлении на входы D1, D2, …, Di, …, D25 шифратора 9 неверной комбинации сигналов, на его втором (дополнительном) выходе E формируется логическая единица, информирующая о возникшей ошибке.

В соответствии с таблицей истинности при поступлении на i-ый вход шифратора 9 логической единицы, а на все остальные – логических нулей (верная комбинация, что свидетельствует о том, что сигнал Xсi, поступающий на вход Ini элемента выбора, имеет ранг, соответствующий заданному блоком 3), на выходе Y формируется сигнал, представление которого в десятичной системе счисления соответствует номеру соответствующего i-ого канала сравнения 5i. Сигнал с выхода Y поступает на управляющий вход Add управляемого переключателя, который подключает на свой выход Out, тот из входов Ini, сигнал которого подается на опорный вход канала сравнения 5i, определившего заданный ранг. По выполняемой функции мультиплексор может выполнять роль управляемого переключателя 1 фиг. 1.

Для проверки работоспособности рассмотренного (предлагаемого) 25-канального элемента выбора медианного сигнала при изменяющихся входных сигналах на его информационные входы были поданы 25 входных сигналов Xc1-Xc25 (смотри фиг.2). Входные сигналы 25-канального элемента выбора медианного сигнала представляют собой дискретные (цифровые) синусоиды Xc1, Xc2, …, Xci, …, Xc25(обозначены прерывистыми линиями), с фазовым сдвигом друг относительно друга, равным  рад и постоянной составляющей. Амплитуда синусоиды каждого входного сигнала составляет 214-1, а постоянная составляющая 214=16384 (относительных единиц). Максимальная величина сигнала равна 32767 относительных единицы. Частота входных сигналов составляет 1 кГц (период 1 миллисекунда). При заданном фазовом сдвиге величина, а значит и ранг, каждого из входных сигналов изменяется с частотой 25 раз за период входного сигнала, что явно отражается на временной диаграмме выхода Out управляемого переключателя 1 (фиг. 1). Временная диаграмма выхода Out показана на фиг.2 жирной сплошной линией. Выходной сигнал Err (фиг. 2) дополнительного выхода многоканального элемента выбора Err (фиг.1) при этом постоянен в течение периода входного сигнала и равен «0», что свидетельствует об отсутствии ошибки устройства при определении ранга входного сигнала.

рад и постоянной составляющей. Амплитуда синусоиды каждого входного сигнала составляет 214-1, а постоянная составляющая 214=16384 (относительных единиц). Максимальная величина сигнала равна 32767 относительных единицы. Частота входных сигналов составляет 1 кГц (период 1 миллисекунда). При заданном фазовом сдвиге величина, а значит и ранг, каждого из входных сигналов изменяется с частотой 25 раз за период входного сигнала, что явно отражается на временной диаграмме выхода Out управляемого переключателя 1 (фиг. 1). Временная диаграмма выхода Out показана на фиг.2 жирной сплошной линией. Выходной сигнал Err (фиг. 2) дополнительного выхода многоканального элемента выбора Err (фиг.1) при этом постоянен в течение периода входного сигнала и равен «0», что свидетельствует об отсутствии ошибки устройства при определении ранга входного сигнала.

Для проверки работоспособности многоканального элемента при реализации функции выявления ошибочных комбинаций был проведен дополнительный эксперимент, для которого на вход D8 шифратора 9 подавалась логическая единица с частотой 2 кГц и длительностью импульса 58,5 мкс, что имитировало ложное срабатывание канала сравнения 58. При этом, когда сигнал, имеющий искомый ранг, подается не на вход In8, логическая единица также возникает на выходе другого канала сравнения. Таким образом, имитировалась ситуация, когда на два входа шифратора 9 одновременно поступают логические единицы (четыре временных диаграммы сверху вниз на фиг. 3), что является ошибочной комбинацией и вызывает появление логической единицы на выходе Err элемента выбора (пятая временная диаграмма сверху на фиг. 3). На нижней (шестой сверху диаграмме фиг. 3) приведены входные сигналы Xc1-Xc25 элемента выбора и выходной сигнал Out (жирная линия) при имитации ошибочных (неверных) комбинаций.

Таким образом, многоканальный элемент для выбора одного из входных сигналов, согласно заявляемого изобретения, позволяет решить поставленную техническую проблему и достигнуть технического результата, заключающегося в реализации быстродействующего многоканального элемента выбора одного из входных сигналов с использованием цифровой схемотехники высокой степени интеграции, в том числе на ПЛИС, и выполняющего функцию выявления ошибочных результатов вычисления медианного сигнала. Предложенная реализация элемента выбора с двадцатью пятью входами, предназначенного для определения медианного сигнала, занимает 6555 логических ячеек на ПЛИС Altera Cyclone IV EP4CE115F29C7 (6% от общего числа доступных логических ячеек). Схема собрана на доступных (серийно выпускаемых) комплектующих, с возможностью многократного воспроизведения. Для выбранной ПЛИС была установлена тактовая частота, равная 200 МГц. При этом время вычисления медианного сигнала не превышает одного периода тактового сигнала – 5 нс, что обеспечивает высокое быстродействие заявляемого многоканального элемента выбора медианного сигнала. Задание другой величины ранга на выходе блока 3 задания ранга входного сигнала обеспечит выбор сигнала с этим заданным рангом и диагностику появления ошибки в определении ранга, аналогично рассмотренному.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный элемент выбора медианного сигнала | 2024 |

|

RU2832435C1 |

| ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ АНАЛОГОВЫХ СИГНАЛОВ | 1994 |

|

RU2093888C1 |

| Аналоговый ранговый процессор | 1988 |

|

SU1571627A1 |

| РЕЛЯТОРНЫЙ ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ОБРАБОТКИ КОРТЕЖЕЙ АНАЛОГОВЫХ СИГНАЛОВ | 1995 |

|

RU2120662C1 |

| Устройство для ранжирования аналоговых сигналов | 1988 |

|

SU1541636A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| РЕЛЯТОРНЫЙ ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ИДЕНТИФИКАЦИИ, СЕЛЕКЦИИ И РАНЖИРОВАНИЯ ТРЕХ АНАЛОГОВЫХ СИГНАЛОВ | 1999 |

|

RU2149450C1 |

| Многоканальный различитель максимального сигнала | 1985 |

|

SU1277376A1 |

| Пневматическое многоканальное управляющее устройство | 1972 |

|

SU450132A1 |

| Устройство для передачи командной информации с рассредоточенных пунктов управления | 1990 |

|

SU1795500A1 |

Изобретение относится к автоматике и цифровой вычислительной технике. Техническим результатом является создание быстродействующего N-канального элемента выбора одного из входных сигналов, осуществляющего выбор входного сигнала по его заданному рангу из набора входных сигналов и выполняющего функцию выявления ошибочных результатов операции выбора входного сигнала. Технический результат достигается тем, что устройство реализовано с использованием цифровой схемотехники высокой степени интеграции и содержит управляемый переключатель, блок для обработки входных сигналов, блок для задания ранга выбираемого входного сигнала. Блок для обработки входных сигналов содержит модуль ранжирования, N каналов сравнения, шифратор с основным и дополнительным выходами. Модуль ранжирования содержит N усилителей, N сумматоров, N блоков задания сигналов ранжирования. Каждый канал сравнения включает блок компараторов, сумматор единиц и блок сравнения, соединенные между собой. Неинвертирующие входы N-1 компараторов объединены и образуют опорный вход канала сравнения. Инвертирующие входы этих компараторов образуют входы сравнения каждого из каналов сравнения. 2 з.п. ф-лы, 3 ил., 1 табл.

1. Многоканальный элемент выбора одного из входных сигналов, содержащий управляемый переключатель, имеющий управляющий вход, выход и N информационных входов, которые соединены с N информационными входами блока обработки входных сигналов, а выход управляемого переключателя образует выход многоканального элемента выбора, при этом управляющий вход переключателя подключен к выходу блока обработки входных сигналов, который имеет управляющий вход, а также содержит канал сравнения, включающий блок компараторов, неинвертирующие входы которых объединены и образуют опорный вход блока компараторов, а их инвертирующие входы образуют входы сравнения блока компараторов, кроме того, канал сравнения содержит сумматор единиц и блок сравнения, отличающийся тем, что блок обработки входных сигналов дополнительно снабжен N-канальным модулем ранжирования, N-1 каналами сравнения, каждый из которых имеет N входов, один выход и управляющий вход, блоком задания ранга выбираемого сигнала и шифратором с N входами и двумя выходами, при этом первый выход шифратора образует основной выход блока обработки входных сигналов, а его второй выход, предназначенный для выдачи сигнала ошибки, является дополнительным выходом блока обработки входных сигналов, при этом выход каждого канала сравнения соединен с соответствующим входом шифратора; каждый из каналов модуля ранжирования содержит усилитель, блок для задания сигнала ранжирования и сумматор модуля ранжирования, при этом вход усилителя образует соответствующий вход модуля ранжирования и соединен с соответствующим входом многоканального элемента выбора, а выход усилителя подключен к первому входу сумматора модуля ранжирования, второй вход которого соединен с блоком для задания сигнала ранжирования, а выход сумматора модуля ранжирования образует соответствующий выход модуля ранжирования; каждый из каналов сравнения содержит блок компараторов из N-1 компараторов, сумматор единиц с N-1 входами и одним выходом и блок сравнения с двумя входами и одним выходом, выходы N-1 компараторов подключены к соответствующим входам сумматора единиц, выход сумматора единиц подключен к первому входу блока сравнения, выход которого является выходом соответствующего канала сравнения, соединенного с соответствующим входом шифратора, а вторые входы блоков сравнения каждого канала сравнения, являющиеся управляющими входами канала сравнения, объединены и образуют управляющий вход многоканального элемента выбора, к которому подключен блок задания ранга выбираемого сигнала, а входы блока компараторов являются одноименными входами канала сравнения; кроме того, каждый выход модуля ранжирования соединен со входами каждого канала сравнения таким образом, что i-й выход модуля ранжирования подключен к опорному входу i-го канала сравнения, при этом к входам сравнения каждого из каналов сравнения подключены все выходы модуля ранжирования за исключением выхода, подключенного к опорному входу соответствующего канала сравнения.

2. Многоканальный элемент выбора одного из входных сигналов по п. 1, отличающийся тем, что управляемый переключатель выполнен в виде мультиплексора.

3. Многоканальный элемент выбора одного из входных сигналов по п. 1, отличающийся тем, что все блоки многоканального элемента реализованы с использованием цифровой схемотехники высокой степени интеграции, например, на ПЛИС.

| МЕДИАННЫЙ ИДЕНТИФИКАТОР | 2002 |

|

RU2204164C1 |

| РАНГОВЫЙ ФИЛЬТР | 2002 |

|

RU2205449C1 |

| СПОСОБ ВЫДЕЛЕНИЯ АНТИБИОТИКОВ | 0 |

|

SU169194A1 |

| CA 2000294 A1, 11.04.1990 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

Авторы

Даты

2023-10-02—Публикация

2023-02-10—Подача